Introductory course to VHDL and HLS FPGA programming

Università degli Studi Milano Bicocca

Introduction to FPGA programming

Introduction to FPGA programming

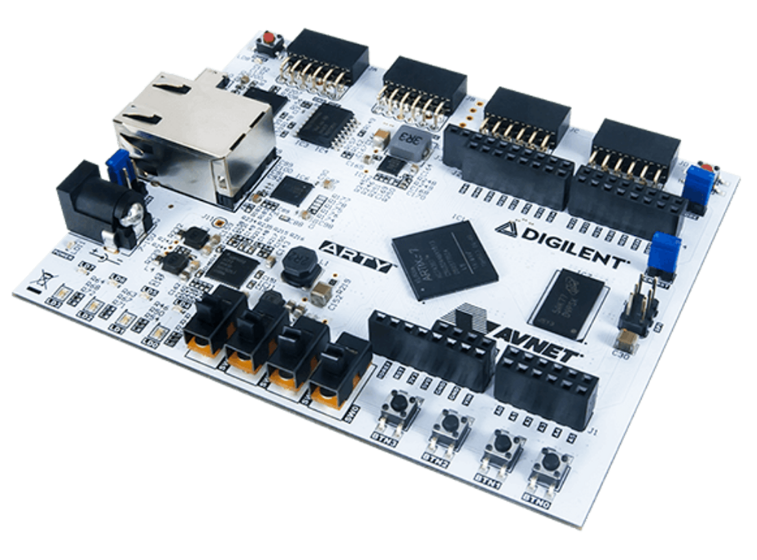

Image taken from: https://https://digilent.com

The course is mainly thought for the new personnel hired by means of the ICSC project to work on projects and research activities in the framework of Spoke 2 ("Fundamental Research And Space Economy") and Spoke3 (Astrophysics & Cosmos Observations), but open to anyone interested within the fundamental physics community.

Lecturers:

- Andrea Triossi (University of Padova)

- Mirko Mariotti (University and INFN of Perugia)

- Sioni Summers (CERN)

Facilitators for the hands-on sessions:

- Giulio Bianchini (INFN of Perugia)

- Francesco Brivio (INFN Milano Bicocca)

Prerequisites:

- Basic notion of digital electronics (combinatorial and sequential circuits)

- basic C++ programming with usage of templates

- basic python programming

- entry level knowledge of machine learning (not really needed, but it may help for the last part of the course)

Target skills and knowledge: The aim of the course is to provide a hands-on programming laboratory of Field-Programmable Gate Arrays (FPGA) through the VHDL hardware description language

Course unit contents:

- Introduction to FPGAs

- FPGA Architecture

- FPGA programming flow

- VHDL language by examples

- Introduction to the Vivado programming framework and the Arty A7 board

- Combinational circuits on FPGA

- Sequential circuits on FPGA

- Arithmetic operations on FPGA

- Case study: UART interface

- High Level Synthesis (HLS)

- Programming flow

- Number representations and arithmetic

- Loops: understanding and optimizing

- HLS case study: Missing transverse energy calculation

Suggested readings:

- Manual for syntax

- The VHDL Golden Reference Guide (DOULOS)

- VHDL handbook (HARDI)

- Books

- Zwolinski,M., Digital System Design with VHDL. Harlow: PRentice Hall Pearson Education

- Tappero F., Mealy B., Free Range VHDL

- Kastner R., Matai J., Neuendorffer S., Parallel Programming for FPGAs

All the participants are requested to have a copy of Vivado installed on a local machine

The Course will be held at Università degli Studi di Milano Bicocca

GitHub pages:

- Day 1: https://github.com/FPGA-course-2025/day1

- Day 2: https://github.com/FPGA-course-2025/day2

- Day 3: https://github.com/FPGA-course-2025/day3

- Day 4: https://github.com/FPGA-course-2025/day4

- Day 5: https://github.com/FPGA-course-2025/day5