### PHASE-1 UPGRADES

RPC MINIWORKSHOP ROMA 26 MARZO 2015

- BARREL SECTOR LOGIC TO MUCTPI INTERFACE BOARD FOR PHASE-I

- THE PAD TRIGGER LOGIC BOARD

- THE BIS78 PROJECT

## BARREL SECTOR LOGIC TO MUCTPI INTERFACE BOARD FOR PHASE-I

R.GIORDANO, V.IZZO, S.PERRELLA, A.SALAMON, R.VARI

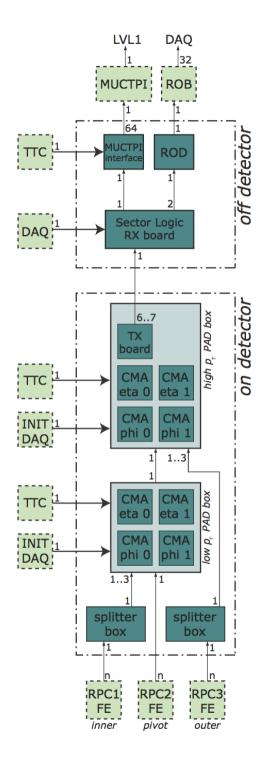

### **RPC** TRIGGER PATH TO MUCTPI

RPC DATA FROM FRONT-END TO COINCIDENCE MATRIX (CM) AND PAD

> THEN TRANSFERRED VIA OPTICAL LINK (G-LINK) TO OFF-DETECTOR

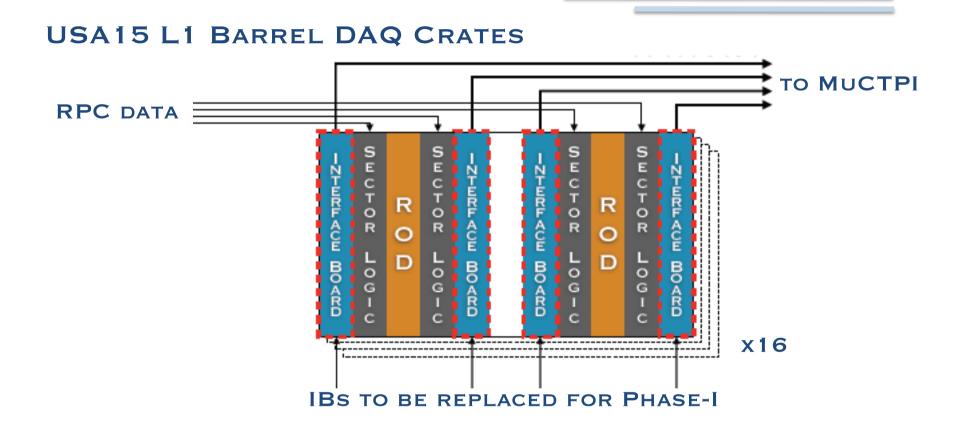

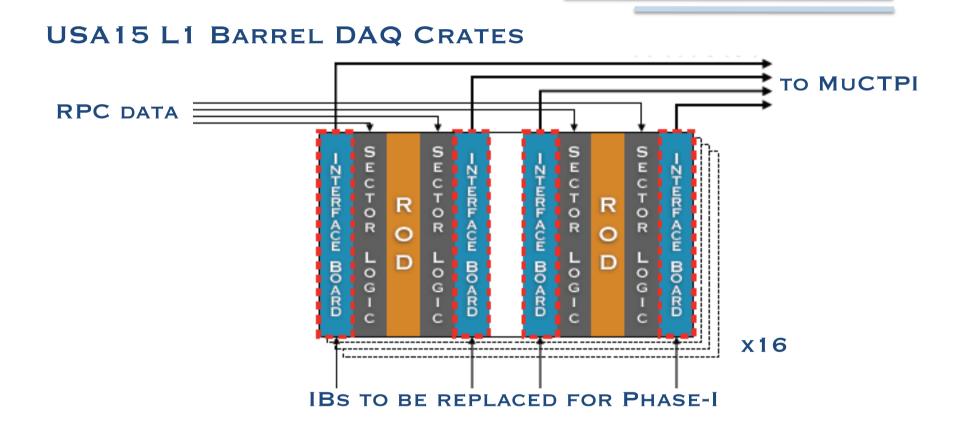

RPC TRIGGER DATA RECEIVED IN USA15 BY SECTOR LOGIC

THEN TRANSFERRED TO MUCTPI VIA MUCTPI INTERFACE BOARD ON COPPER CABLES

### **MOTIVATION OF THE OPTICAL UPGRADE**

NECESSARY SINCE THE NEW MUCTPI FOR PHASE-I WILL ACCEPT OPTICAL INPUT ONLY

THE NEW END-CAP SECTOR LOGIC WILL GO OPTICAL AS WELL.

### **MOTIVATION OF THE OPTICAL UPGRADE**

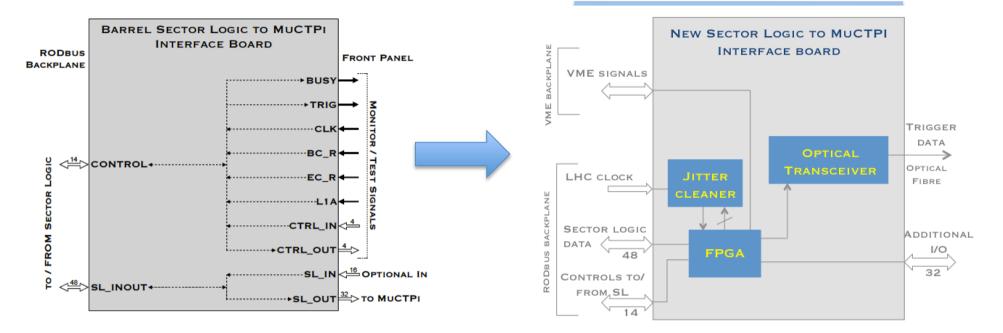

64 SL-MUCTPI VME INTERFACE BOARDS + 64 COPPER CABLES WILL BE REPLACED WITH:

64 NEW INTERFACE BOARDS (SAME VME CRATES) + 64 NEW OPTICAL FIBERS

### **New Interface Board**

- FPGA USED TO CONNECT TO VME AND BACKPLANE AND TO SERIALIZE DATA

- Optical SFP+ transceiver, Data Rate: 6.4 GB/s  $\rightarrow$  160 Bit @ 40 MHz

- ADDITIONAL 32 BIT I/O SIGNALS FORESEEN ON THE IB FRONT PANEL

- SERIALIZER LOGIC MUST BE SYNCHRONIZED WITH THE 40 MHz LHC CLOCK

- UP TO 4 BCS ADDITIONAL L1 LATENCY

### **PRELIMINARY TESTS**

TTC CLOCK SIGNAL CORRECTLY PROPAGATED ON VME BACKPLANE AND RECEIVED BY A JITTER CLEANER

PRESENTLY, WE ARE PERFORMING JITTER MEASUREMENTS ON THE RECEIVED SIGNAL, IN ORDER TO EVALUATE THE IMPACT OF THE PHYSICAL LAYER ON THE SIGNAL INTEGRITY OF THE CLOCK ITSELF

# PLANS

2014.12: INTERFACE BOARD PRELIMINARY IMPLEMENTATION ON FPGA DEMO BOARD

2015.02: PDR

2016.Q1: FIRST PROTOTYPE

2016.Q3: FDR

2017.Q1: PRR

2017.Q2: PRODUCTION

**2018.Q1:** INSTALLATION AND COMMISSIONING

2015-2018: SOFTWARE DEVELOPMENT (TEST SOFTWARE AND INTEGRATION INTO TDAQ FRAMEWORK)

### MANPOWER

#### **INTERESTED INSTITUTES:**

| INFN group       | FTE                           | Work                                                      |

|------------------|-------------------------------|-----------------------------------------------------------|

| INFN Roma        | 0.2 physicist<br>0.1 engineer | Main board schematic, test software, test & commissioning |

| INFN Napoli      | 0.3 physicist                 | Board layout, optical link, DAQ software                  |

| INFN Tor Vergata | 0.1 physicist                 | Main Board schematic, interface<br>with SL board          |

#### TOTAL FTE NUMBER (0.7 FTE/YEAR) FULFILLS THE REQUIREMENTS

DESIGN DONE IN COLLABORATION WITH CERN CTP/MUCTPI GROUP TO DEFINE COMMON PARTS (SAME OPTICAL INTERFACE AND TRANSMISSION PROTOCOL)

## THE NSW PAD TRIGGER LOGIC BOARD

V.IZZO, S.PERRELLA, R.VARI

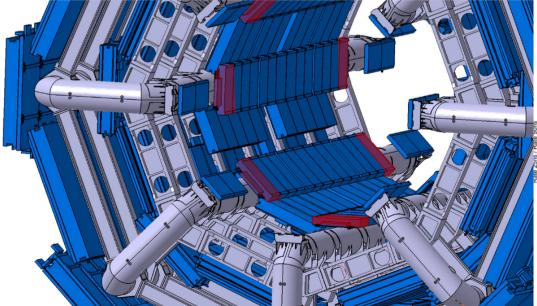

### **STGC SEGMENTATION**

**16 stgc sectors** per **NSW** wheel.

EACH SECTOR IS DIVIDED IN INNER, MIDDLE AND OUTER REGION.

2 stgc quadruplets (pivot + confirm) per sector.

4 LAYERS OF PADS AND 4 LAYERS OF STRIPS PER QUADRUPLET.

PADS ARE **STAGGERED** BY HALF LENGTH IN ETA AND PHI ON THE **4** LAYERS.

A LOGICAL PAD IS DEFINED BY THE PROJECTION OF THE PHYSICAL PADS IN THE DIFFERENT LAYERS (1/4 OF THE PAD AREA).

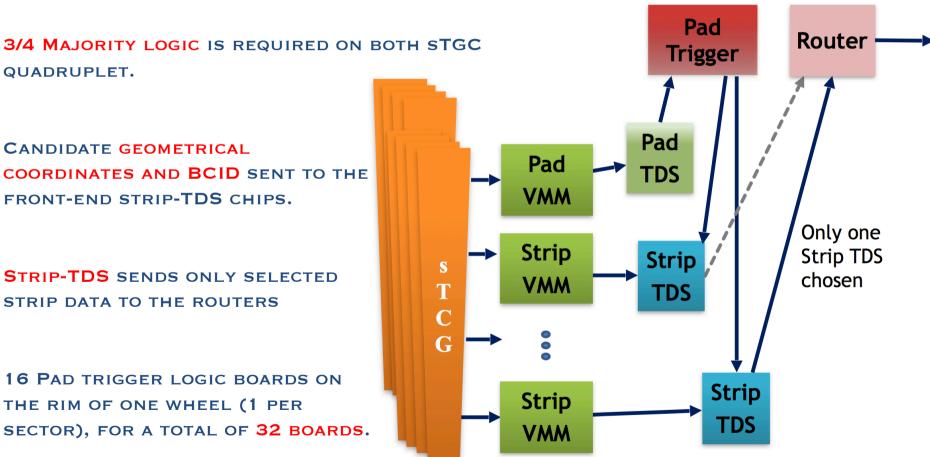

### **STGC TRIGGER LOGIC**

FIND A PAD HIT COINCIDENCE IN A TOWER OF LOGICAL PADS WITHIN ONE BUNCH CROSSING.

**CANDIDATE GEOMETRICAL** COORDINATES AND BCID SENT TO THE FRONT-END STRIP-TDS CHIPS.

STRIP-TDS SENDS ONLY SELECTED STRIP DATA TO THE ROUTERS

QUADRUPLET.

16 PAD TRIGGER LOGIC BOARDS ON THE RIM OF ONE WHEEL (1 PER SECTOR), FOR A TOTAL OF 32 BOARDS.

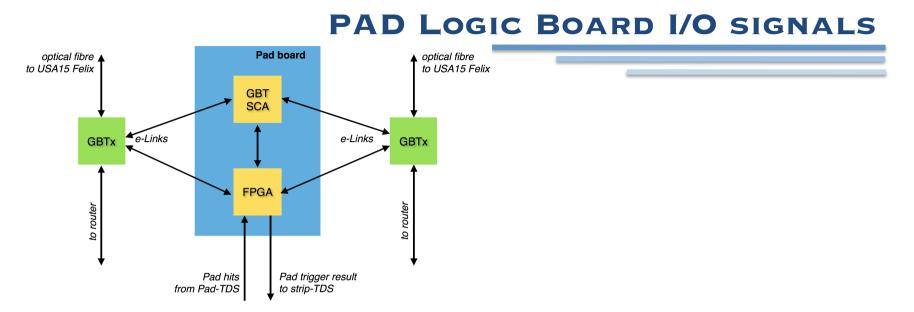

BI-DIRECTIONAL: GBTX E-LINKS FROM 2 GBTX (TOTAL NUMBER OF E-LINKS TO BE DEFINED, MOST PROBABLY 1-2 FOR THE CLOCK(S), 1 FOR THE GBT-SCA, 1-2 FOR THE READOUT, SO UP TO 5 E-LINKS PER GBTX).

INPUT: **STGC PAD HIT** SIGNALS FROM FRONT-END **PAD-TDS** CHIPS (24 SERIAL LINES ON TWINAX CABLES)

OUTPUT: PAD LOGIC TRIGGER RESULT (UP TO 3 TRIGGER CANDIDATES) TO FRONT-END STRIP-TDS CHIPS (5/6 SERIAL LINES ON TWINAX CABLES).

ALL I/O SIGNALS MAKE USE OF DIFFERENTIAL LSVS OR LVDS STANDARDS

EACH BC THE STGC PAD HIT SERIAL DATA IS SAMPLED, DESERIALISED AND BCID TAGGED:

- 4.8 GB/S PER SERIAL LINE = 120 BIT @ 40 MHZ -> 20 BIT @ 240 MHZ FROM EACH GTX

TRIGGER LOGIC BASED ON COINCIDENCE WINDOWS TO LOOK FOR A 3/4 MAJORITY ON EACH OF THE TWO STGC QUADRUPLET

THE TRIGGER LOGIC IS PERFORMED INDEPENDENTLY AND SIMULTANEOUSLY ON THREE **STGC** REGIONS (INNER, MIDDLE, OUTER), SO THAT UP TO THREE INDEPENDENT TRIGGER WORDS CAN BE PRODUCED

THE OUTPUT TRIGGER WORD IS THEN SERIALISED AND SENT TO THE FRONT-END STRIP-TDS CHIPS:

- KINTEX-7 OSERDES SERIALISERS, 640 MB/S (320 MHz DDR) PER LINE (14-BIT WORD)

A LOCAL FAN-OUT ON THE FRONT-END BOARDS MAY BE NEEDED TO TRANSMIT THE TRIGGER DATA TO ALL STRIP-TDS CHIPS

**ROME1** AND NAPLES INFN GROUPS ARE INVOLVED SO FAR

| 2015 Feb. | Preliminary Design Review                    |

|-----------|----------------------------------------------|

| 2015 Dec. | First Pad board prototype                    |

| 2016 May  | Final Design Review                          |

| 2016 Sep. | Second Pad board prototype                   |

| 2017 Apr. | Production Readiness Review                  |

| 2017 Jun. | production of the 32 Pad boards + 4/5 spares |

| 2017 Sep. | installation and commissioning               |

INFN: BOLOGNA, NAPOLI, ROMA1, ROMA2 MPI (MUNICH), U MICHIGAN, USTC

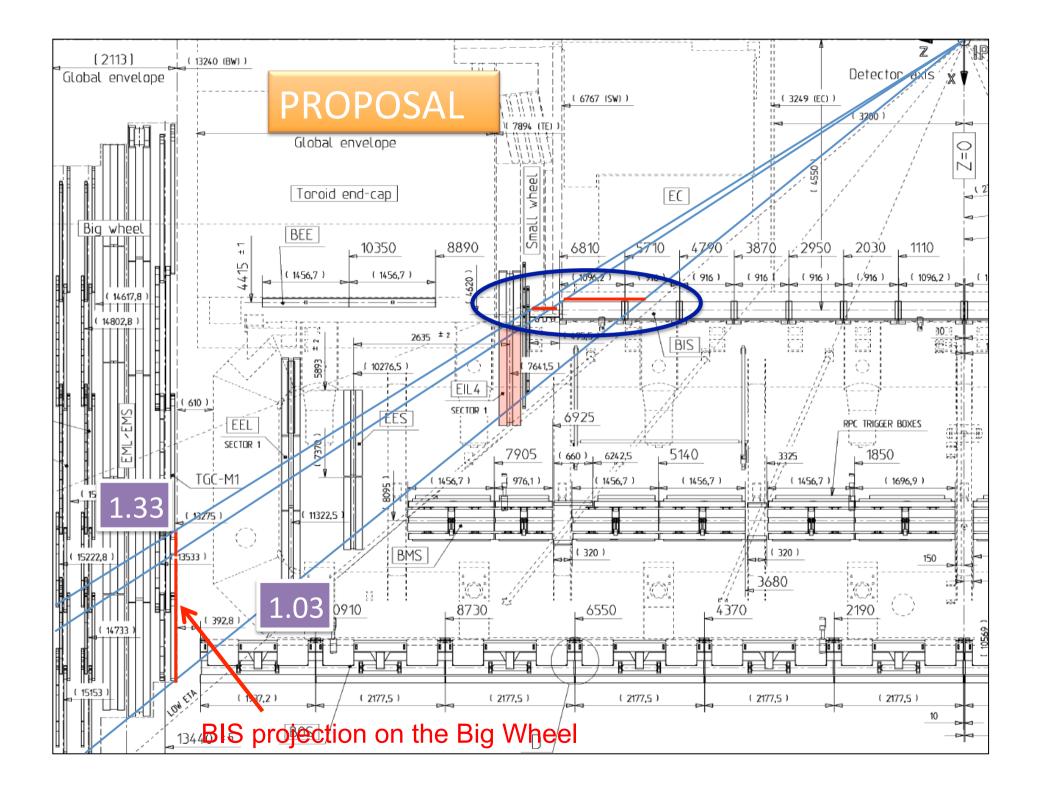

### THE BIS78 PROJECT

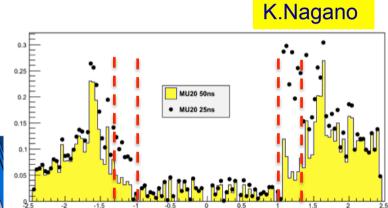

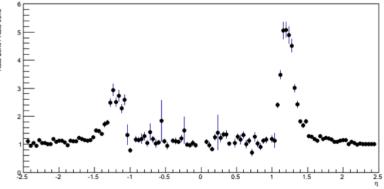

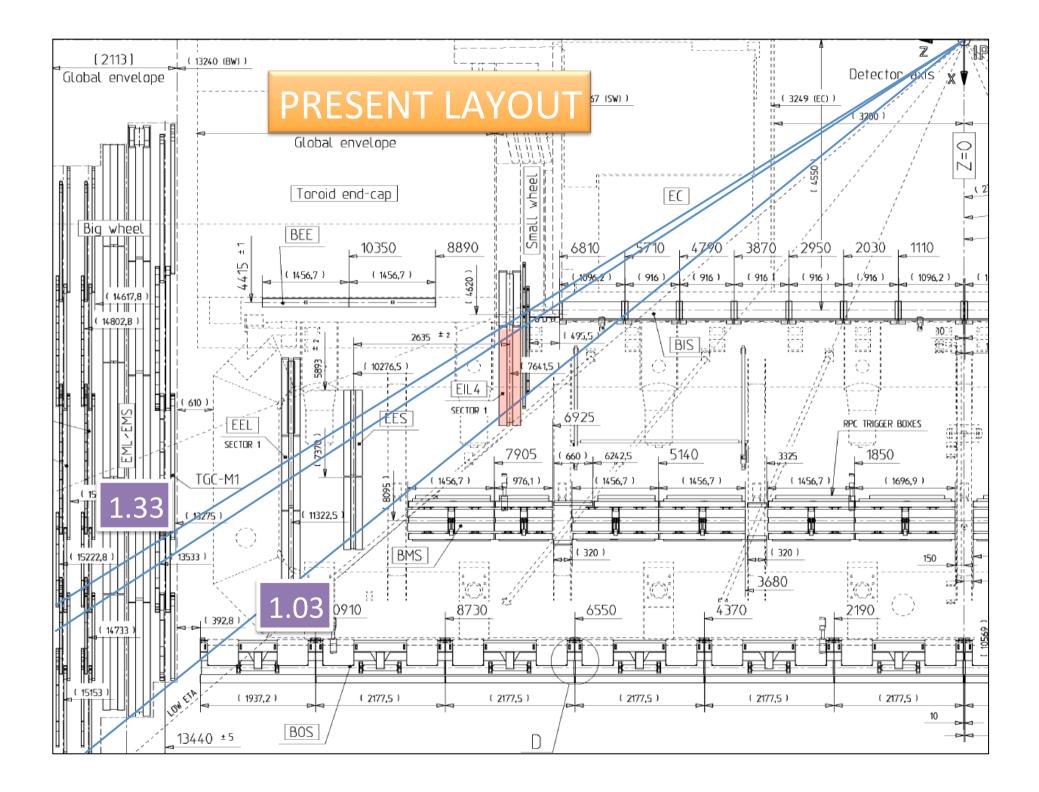

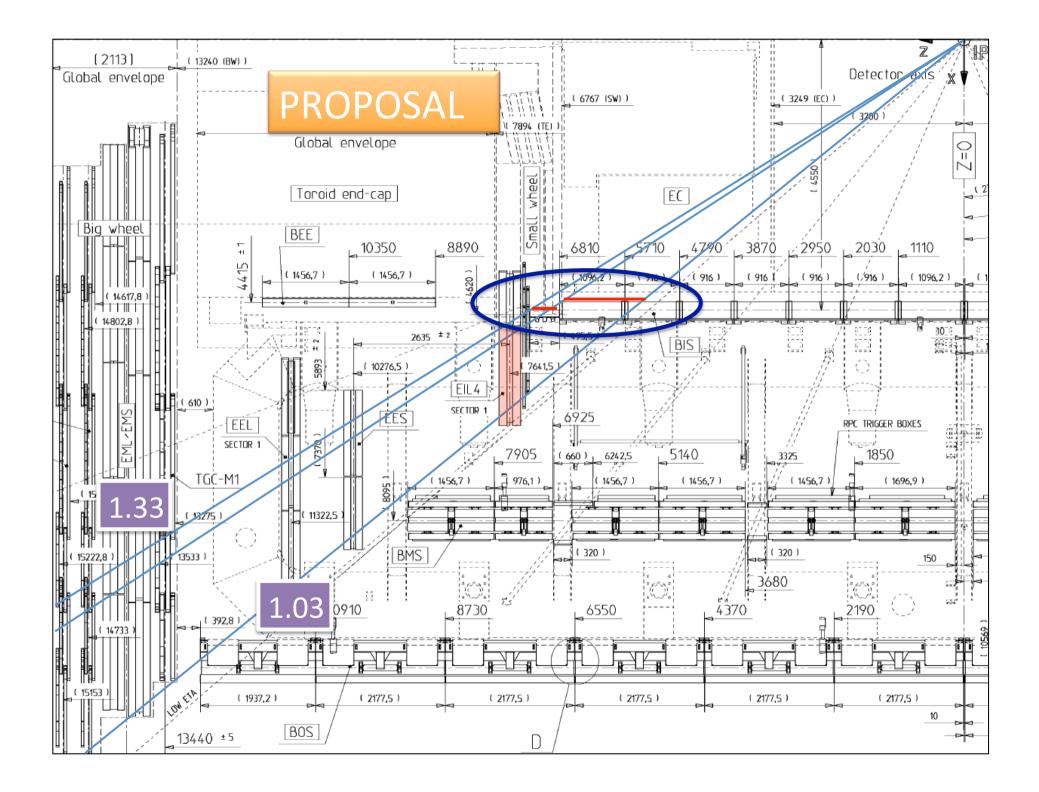

THE BARREL/ENDCAP TRANSITION REGION (1 < ETA < 1.3), NOT COVERED BY THE NSW, WILL SUFFER FROM HIGH TRIGGER FAKE RATE WITH INCREASING LUMINOSITY.

THE PROPOSED ADDITIONAL RPC CHAMBERS IN THE BARREL INNER SMALL REGION (16 NEW STATIONS) CAN SIGNIFICANTLY REDUCE THE FORESEEN FAKE RATE.

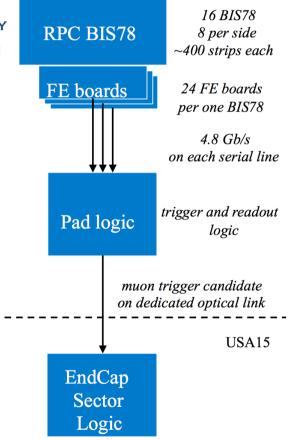

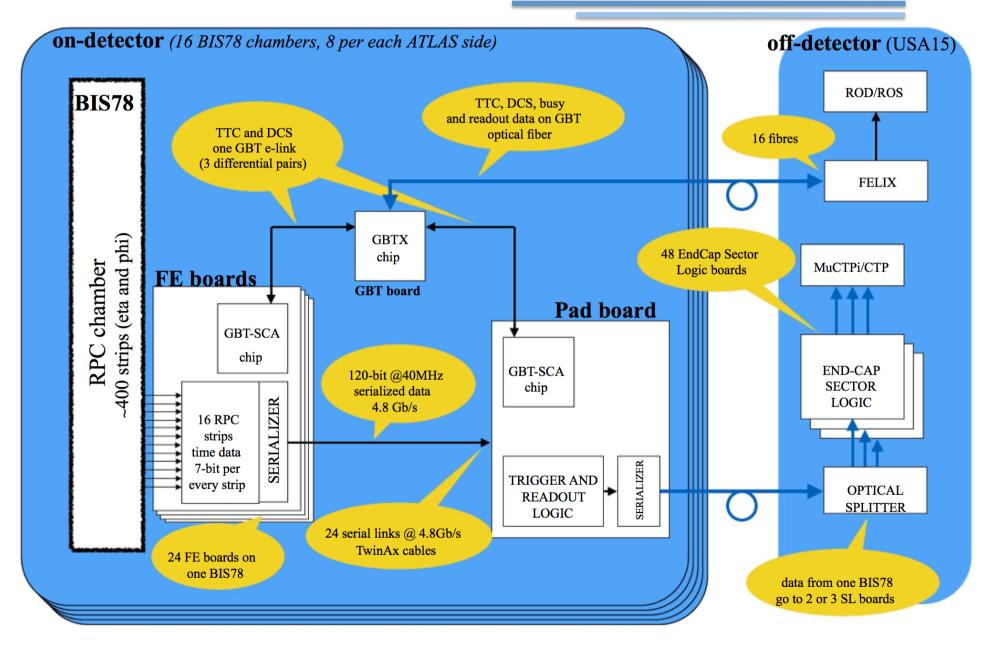

BIS78 ON-DETECTOR ELECTRONICS (16 PADS) WILL RECEIVE RPC HITS AND SEND THE MUON TRIGGER CANDIDATE DATA TO THE END-CAP SECTOR LOGIC BOARDS IN USA15.

### **BIS78 RPC TRIGGER PATH**

EACH BIS78 RPC CHAMBER WILL BE EQUIPPED WITH ABOUT 400 STRIPS (TRIPLET, ETA+PHI).

ONE RPC FRONT-END ELECTRONICS BOARD WILL READ MOST PROBABLY 16 STRIPS AND SAMPLE EACH STRIP HIT WITH 7-BIT TIME INFORMATION (SAMPLED EVERY 25 NS).

DATA COMING FROM 24 FE BOARDS WILL BE SERIALLY SENT TO ONE PAD BOARD ON TWINAX CABLES.

FE\_TO\_PAD SERIAL LINE BANDWIDTH: 4.8 GB/S (UP TO 6.4 GB/S).

NO ZERO-SUPPRESSION TRANSMISSION: **112 GB/S** TOTAL RAW HIT PATTERN DATA TO BE RECEIVED AND PROCESSED BY ONE **PAD BOARD**

TRIGGER RESULT WILL BE SENT TO THE USA15 ENDCAP SECTOR LOGICS ON DEDICATED OPTICAL LINKS.

**OPTICAL FAN-OUT** NEEDED IN **USA15** FOR MATCHING ONE PAD FIBRE TO 2 OR 3 SECTOR LOGIC BOARDS.

UNDER STUDY THE POSSIBILITY TO SEND MORE THAN 7-BIT TIME INFO PER EACH STRIP (EITHER INCREASING THE NUMBER OF PAD INPUTS (UP TO 32) AND/OR INCREASING THE FE\_TO\_PAD BW (UP TO 6.4 GB/S)

### **BIS78 RPC READOUT PATH**

THE PAD BOARD WILL PERFORM THE READOUT LOGIC TOO.

READOUT LATENCY SHOULD BE COMPATIBLE WITH PHASE-II.

TTC, READOUT, BUSY LOGIC AND DCS WILL MAKE USE OF THE GBT SYSTEM.

THE FELIX SYSTEM WILL BE USED TO SEND READOUT DATA TO RODS.

TO BE CHOSEN WHICH ROD TO BE USED

### **PRELIMINARY PROPOSAL:**

### TRIGGER AND READOUT SCHEMA

### CONCLUSIONS

25

STILL VERY PRELIMINARY TRIGGER/READOUT SCHEMA, I/O INTERFACES (FRONT-END AND USA15 LOGIC) HAVE TO BE DEFINED BEFORE THE FINAL SCHEMA.

WE WOULD LIKE TO USE THE **NSW STGC PAD LOGIC** WITH SOME MODIFICATIONS:

- 24 SERIAL INPUTS @ 4.8 GB/S FOR THE NSW PAD LOGIC;

- MICHIGAN SERIALIZER (TO BE USED ON THE FE BOARDS) IS SUPPOSED TO WORK @ 4.8 GB/S (POSSIBLE BANDWIDTH INCREASE UP TO 6.4 GB/S IS UNDER STUDY);

- THE BIS78 PAD FPGA SHOULD HAVE 24 TO ~30 HIGH SPEED SERIAL INPUTS (4.8 TO 6.4 GB/S);

- ONE ADDITIONAL SERIAL OUTPUT FOR THE TRIGGER PATH.

**OPTICAL SPLITTER** OPTIONS FOR THE TRIGGER PATH HAVE TO BE STUDIED.

NO TRIGGER LATENCY ESTIMATE YET (MOST PROBABLY NOT AN ISSUE).

TRIGGER LOGIC PRELIMINARY SIMULATION PERFORMED, DETAILED SIMULATION MUST FOLLOW.

**READOUT SCHEMA** TO BE DEFINED: INDEPENDENT OR BARREL OR ENDCAP (WHICH ROD?).

|                    | NSW sTGC Pad             | <b>BIS78 Pad</b>      |

|--------------------|--------------------------|-----------------------|

| num. serial inputs | 24                       | 24 to 32              |

| input speed        | 4.8 Gb/s (FPGA up to 8)  | (4.8 to 6.4) Gb/s     |

| num. serial output | not defined yet, 3 to 24 | 1                     |

| output speed       | 320 MHz SDR or DDR       | not defined, 4.8 Gb/s |

### THE BIS78 COLLABORATION

**INFN BOLOGNA:** SIMULATIONS; PERFORMANCE STUDY; PRODUCTION DRAWINGS; **DCS**

**INFN ROMA AND NAPOLI:** TRIGGER ELECTRONICS INTEGRATION (PAD)

**INFN ROMA2:** FRONT-END-ELECTRONICS AND GAS VOLUME AND CHAMBER DESIGN

**MPI (MUNICH):** SYSTEM LAYOUT, MECHANICS, INTEGRATION, STATION ASSEMBLY AND TEST

U MICHIGAN: TRIGGER SIMULATION, SERIALIZER, READOUT AND DAQ

U SCIENCE TECHNOLOGY OF CHINA: CHAMBER CONSTRUCTION, COMMISSIONING AND R&D