VI Scuola Nazionale "Rivelatori ed Elettronica per Fisica delle Alte Energie, Astrofisica, Applicazioni Spaziali e Fisica Medica

# Noise performance of 65 nm CMOS transistors exposed to ionizing radiation

26<sup>th</sup> March 2015

**Riceputi Elisa**

Università degli Studi di Bergamo, INFN Pavia

## **Activity overview**

#### Main purpose:

Evaluate ionizing radiation effects on the analog performance of TSMC 65 nm CMOS devices after exposure to a TID of 1Grad

### **Test chip:**

- 1 chip with test devices submitted in June 2014 (delivered in September 2014)

- Test devices bonded in a QFN48 "Open-Pak" package

- 2 bonding diagrams

#### **Measurements:**

#### Static and signal parameters

measured by means of an Agilent E5270B Precision Measurement Mainframe with E5281B SMU Modules

#### Noise in the devices channel current

measured by means of a purposely developed wide-band interface circuit, which allows for noise measurements in the 100 Hz-100 MHz range

# **ATLAS-CMS RD53 Collaboration**

This activity has been carried out in framework of RD53 collaboration and the aim of this project is the design of the next generation of hybrid pixel readout chips to enable the ATLAS and CMS phase 2

Similar/identical requirements, same technology choice and limited availability of rad hard IC design experts in HEP makes this ideal for a close CMS-ATLAS RD collaboration

Institutes: 17

- ATLAS: CERN, Bonn, CPPM, LBNL, LPNHE Paris, NIKHEF, New Mexico, RAL, UC Santa Cruz.

- CMS: Bari, Bergamo-Pavia, CERN, Fermilab, Padova, Perugia, Pisa, PSI, RAL, Torino

- Collaborators: 99, ~50% chip designers

- Collaboration organized by Institute Board (IB) with technical work done in specialized Working Groups (WG)

- Initial work program covers 3 years to make foundation for final pixel chips

#### WG1. Radiation test/qualification

- Qualification of technology to 10 MGy TID, 10 16 n.eq./cm<sup>2</sup>

- Transistor simulation models after irradiation

- Evaluation of logic cell libraries after irradiation

- Expertise on radiation effects in 65nm

# **Ionizing radiation effects in sub-100 nm CMOS**

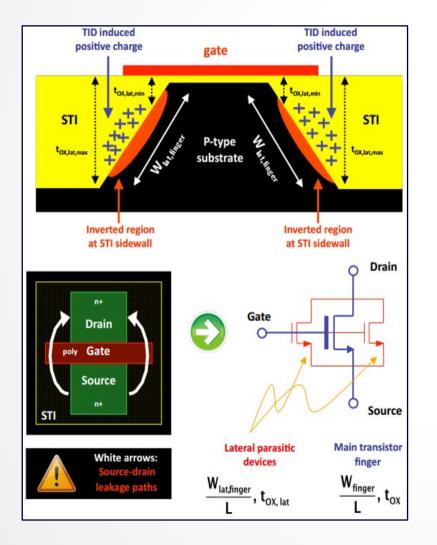

Radiation induced positive charge is removed from thin gate oxides by tunneling (which also prevents the formation of interface states)

- Isolation oxides remain thick (order of 100 nm) also in nanoscale CMOS, and they are radiation soft

- In NMOS, edge effects due to radiation-induced positive charge in the STI oxide generate sidewall leakage paths

- In an interdigitated device, this can be modeled considering that two lateral transistors for each finger are turned on

- The effect of these parasitic devices on the noise and static characteristics must be carefully evaluated

# **Previous measurements**

(September 2013)

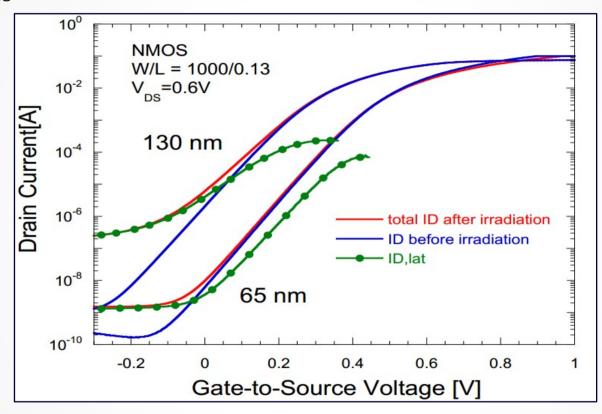

$I_D - V_{GS}$  before and after exposure to a 10 Mrad total dose of  $\gamma$ -rays

A larger amount of lateral leakage takes place in 130 nm devices

The smaller I<sub>D</sub>, lat of 65 nm devices suggests that the sensitivity to positive charge buildup in STI oxides is mitigated by the higher doping of the P-type body with respect to less scaled processes

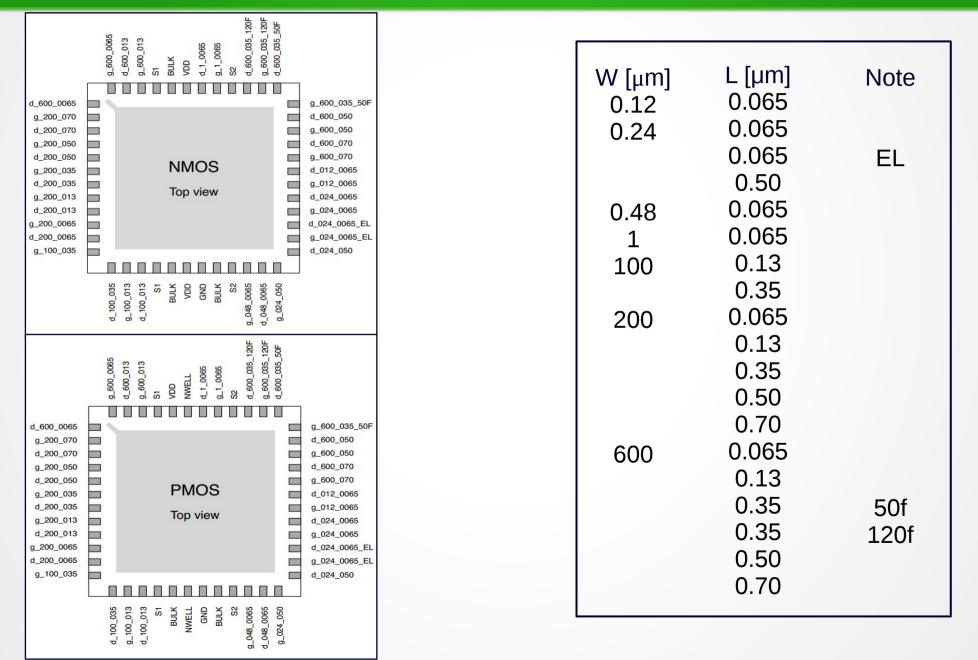

### **Available geometries and bonding diagrams**

6

### **Pre and post-irradiation measurements**

#### **Static measurements**

For all avaliable geometries of NMOS and PMOS

$I_D - V_{GS}$  characteristics

- V<sub>GS</sub> from -0.3 V to 1.2 V with 5 mV steps

- $V_{DS}$  form 0 V to 1.2 V with 0.2 V steps and  $V_{DS}$  = 10 mV

#### $I_D - V_{DS}$ characteristics

- ●V<sub>DS</sub> from 0 V to 1.2 V with 5 mV steps

- V<sub>GS</sub> from 0 V to 1.2 V with 0.2 V steps

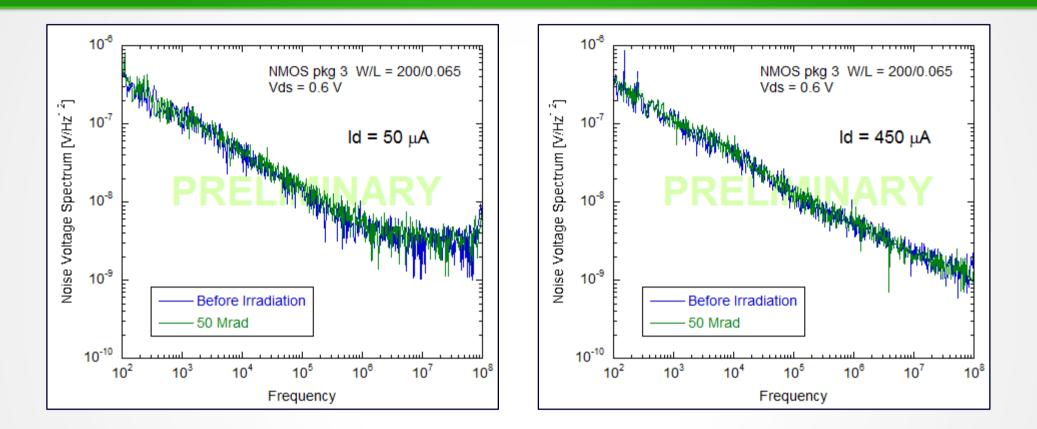

### Noise measurements:

For NMOS and PMOS devices with W = 100, 200 and 600  $\mu m$

Frequency range — 100 Hz - 100 MHz

**Bias conditions**  $\rightarrow$   $|V_{DS}| = 0.6 V$  $\bullet |_{D} = 20, 50, 100, 250 \text{ and } 500 \ \mu\text{A}$

# **Irradiation Procedure and Plans**

**Radiation source** — X-Ray facilities at LNL, Legnaro (PD)

### **Bias conditions during irradiation**

• NMOS with  $V_{GS} = 1.2 \text{ V}$  and  $V_{D} = V_{S} = 0 \text{ V}$

• PMOS with

$$V_{GS} = V_D = V_S = 0 V$$

#### **Temperature**

- Irradiaton and measurements: ambient

- Storage ≈ 0 °C

#### **Irradiaton Plan**

| 1 NMOS Chip |             |      | 1 PMOS Chip |             |      |

|-------------|-------------|------|-------------|-------------|------|

| TID [Mrad]  | Step [Mrad] | Date | TID [Mrad]  | Step [Mrad] | Date |

| 50          | 50          | Feb  |             |             |      |

| 100         | 50          | Mar  | 100         | 100         | Mar  |

| 500         | 400         | Apr  | 500         | 400         | Apr  |

| 1000        | 500         | May  | 1000        | 500         | Мау  |

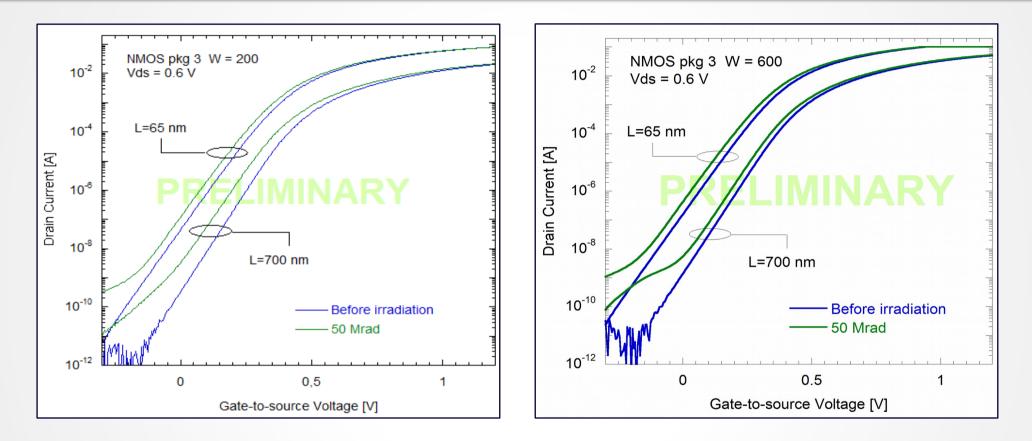

### **Drain Current**

- Devices with L = 65 nm: an increase in the subthreshold current detected for both channel widths W = 200 µm and W = 600 µm

- Devices with L = 700 nm: a more marked increase in the subthreshold current detected for the device with channel widths W = 200 µm

### Noise

No increase in the 1/f noise region detected

No increase in the white noise region detected

Same results for low and high current density

Bg/Pv Group activity mainly concerned with the evaluation of ionizing radiation effects on the analog performance of TSMC 65 nm CMOS devices

#### **Status**

- 1 chip of NMOS devices exposed to a first step of ionizing radiation up to a total dose of 50 Mrad of X-ray

- Static and noise measurements performed before and after irradiation

- Processing of measurement results in progress

### Plan

- Next irradiation steps of NMOS and PMOS chips with X-ray scheduled for March

- Irradiation with 3 MeV proton beam (CN accelerator, INFN-LNL in Padova) scheduled for April