# **A New Front-end ASIC for GEM detectors** with Time and Charge Measurement Capabilities

FRONTIER DETECTORS FOR FRONTIER PHYSICS 13th Pisa Meeting on Advanced Detectors

24-30 May 2015 - La Biodola, Isola d'Elba (Italy)

#### <u>F. Ciciriello<sup>1</sup></u>, F. Corsi<sup>1</sup>, G. De Robertis<sup>2</sup>, G. Felici<sup>3</sup>, F. Loddo<sup>2</sup>, C. Marzocca<sup>1</sup>, G. Matarrese<sup>1</sup>, A. Ranieri<sup>2</sup>

<sup>1</sup>DEI – Politecnico di Bari and INFN – Sezione di Bari, Italy <sup>2</sup>INFN – Sezione di Bari, Italy <sup>3</sup>INFN – Frascati National Laboratories, Italy

# **Motivations and purposes**

### The AMIDERHA project

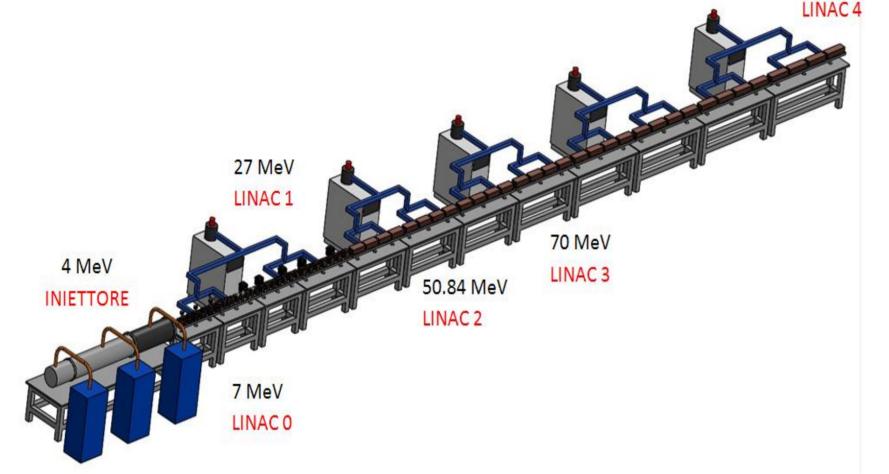

- Construction of a new proton-therapy facility in the Apulia region

- □ Based on multi-stage, cascaded LINAC to obtain different energy levels 150 MeV

#### **Beam monitoring**

- □ Accurate system of beam monitoring needed

- □ Based on Gas Electron Multiplier (GEM) detectors

- Flexibility in size and geometry

- High rate capability (up to 50MHz/cm<sup>2</sup>)

- > Good spatial resolution (down to 50÷100  $\mu$ m) and time resolution (down to 4.5 ns)

- Low mass contribution

- > Large gain with triple GEM structures

#### Front-end ASIC for GEM detectors

- Multichannel ASIC needed for compactness and power consumption

- □ Charge measurement capability, to improve the spatial resolution (charge centroid technique)

- □ Accurate trigger signal, to allow for coincidence analysis among different GEM layers

| ASIC main features            |                     |         |

|-------------------------------|---------------------|---------|

| ASIC Main leatures            | Sensitivity         | 15mV/fC |

| Technology CMOS AMS<br>0.35µm | Dynamic range       | 80fC    |

|                               | Non-linearity error | < 1%    |

> 32 channels

transfer

Integrated 8 bit ADC

> Fast LVDS link for data

Development of the GEM for AMIDERHA: mechanical gas volume

| 52 channels               | Equivalent i |

|---------------------------|--------------|

| Power supply voltage 3.3V |              |

|                           | Datasta      |

nput noise charge < 650e-(ENC) **≅10pF Detector capacitance**

Main specifications for the GEM front-end

# Main building blocks of the ASIC

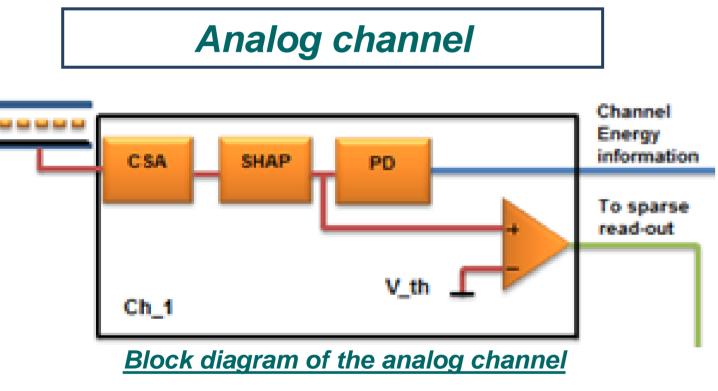

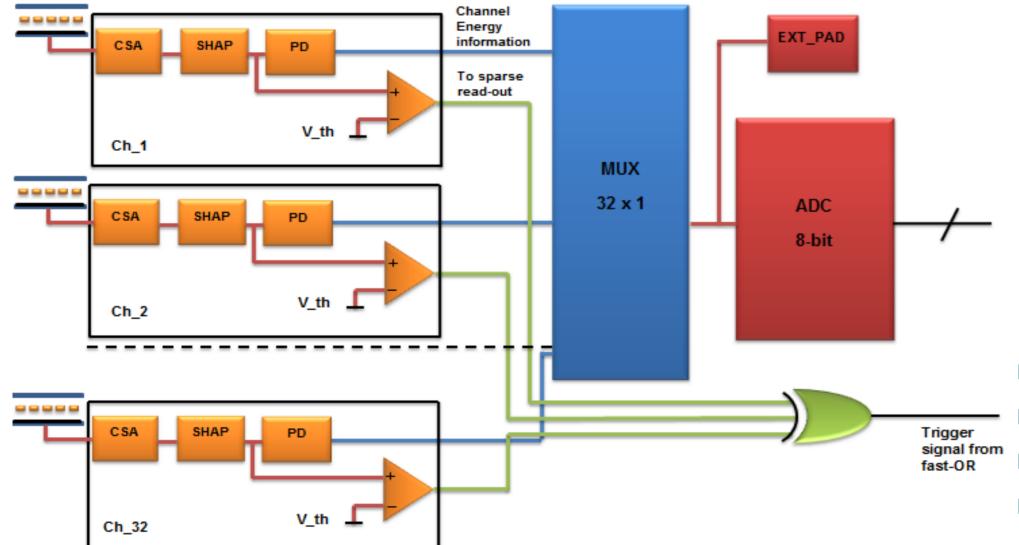

- □ Classic CSA+shaper front-end structure

- **CSA:** straight cascode with active reset of the integration capacitance C<sub>F</sub>=180fF (PMOS with adjustable bias current)

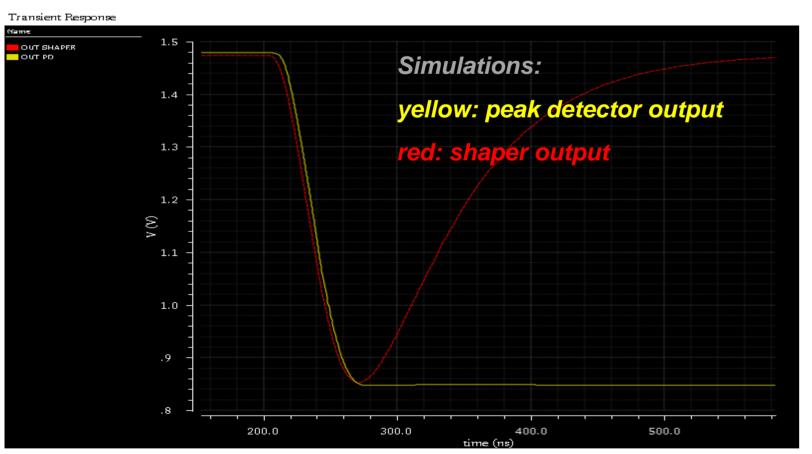

- **Given Second order shaper with adjustable output baseline, peaking** time ≅ 80ns

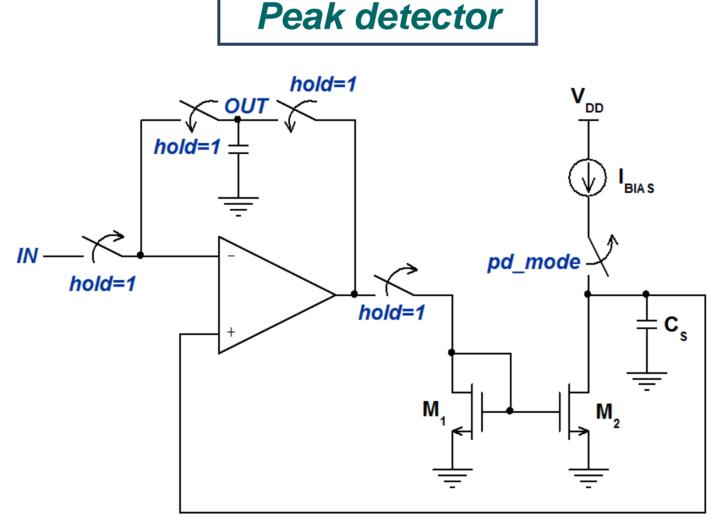

- **D** Peak detector, working as an analog memory, to store the charge information during the read-out

- □ Leading edge comparator with adjustable threshold

Three operating modes:

- > pd\_mode=0, hold=0: voltage follower mode The voltage on C<sub>s</sub> follows the input

- pd\_mode=1, hold=0: peak detection mode The voltage on C<sub>s</sub> tracks the peak of the input

- pd\_mode=1, hold=1: analog memory  $\succ$ The voltage on  $C_s$  is buffered on the output node

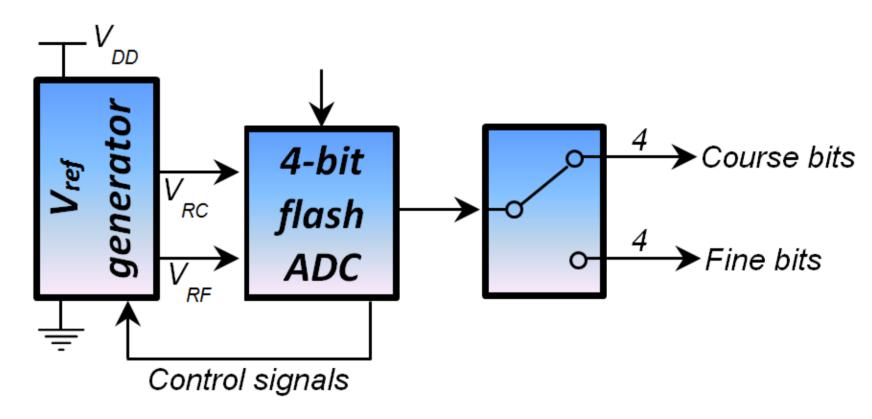

## Two-step flash, subranging 8-bit ADC

- **Two-phase conversion: coarse and fine, exploiting the same** comparators and different references  $V_{RC}$  and  $V_{RF}$

- **Resistor ladder for reference generation**

- **Two ADC modules working in interleaving: one conversion per** clock cycle, maximum conversion rate 20MS/s

- □ Correction logic for "bubble" errors

- Total power consumption 24mW

**Digital part**

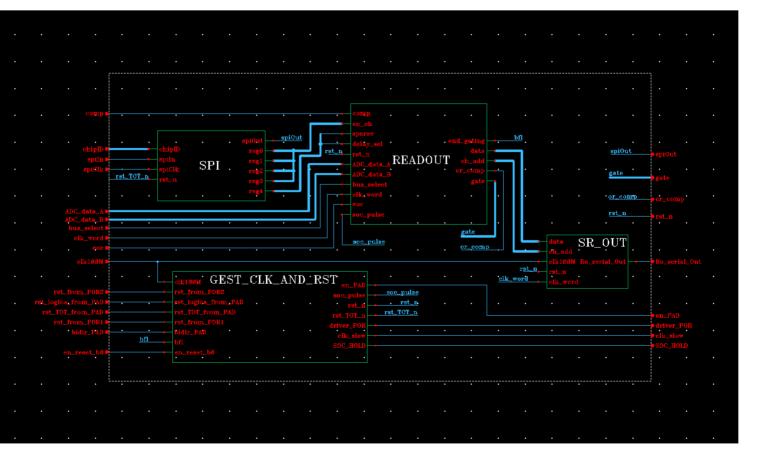

# **Architecture of the ASIC**

- □ READOUT: management of the sparse and serial read-out modes

- □ SPI: configuration interface (two 8-bit DACs, three 10-bit DACs, channel masking, setting of the read-out mode, test mode)

- □ SR\_OUT: data serializer for the 100Mbit/s LVDS output link

- □ GEST\_CLK\_AND\_RST: clock and reset management

- **D PD** outputs multiplexed to the ADC input □ Trigger formation: fast-OR of the comparator outputs Channel maskable through configuration flags

- □ Internal bias generator based on bandgap reference

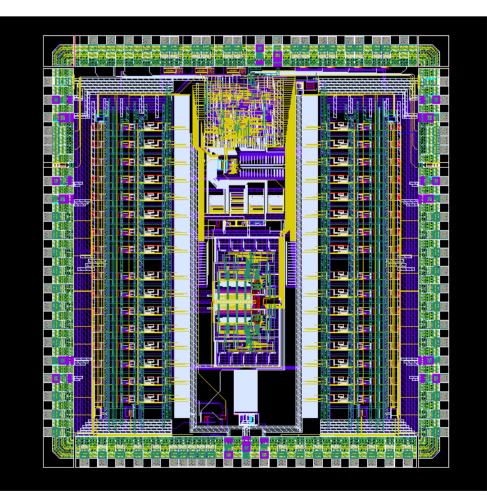

Layout

#### □ 4.6 x 4.9 mm2, package JLCC 84 pins

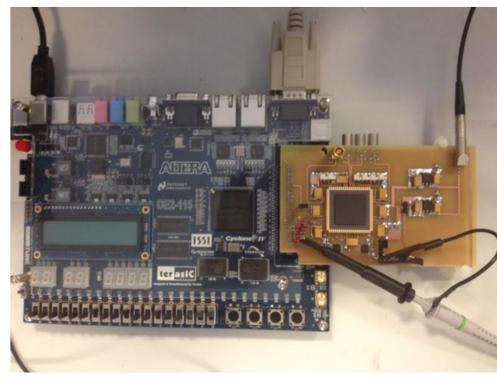

#### □ ASIC assembled on the test board