# A Patter Recognition Mezzanine based on Associative Memory and FPGA technology for L1 track triggering at HL-LHC

L. Alunni<sup>1</sup>, N. Biesuz<sup>4</sup>, G.M. Bilei<sup>1</sup>, S. Citraro<sup>4</sup>, F. Crescioli<sup>5</sup>, L. Fanò<sup>1</sup>, G. Fedi<sup>4</sup>, D. Magalotti<sup>1,2</sup>, G.Magazzù<sup>4</sup>, L.Servoli<sup>1</sup>, L. Storchi<sup>1</sup>, F. Palla<sup>4</sup>, P. Placidi<sup>1,3</sup>, A. Papi<sup>1</sup>, Y. Piadyk<sup>5</sup>, E. Rossi<sup>4</sup>

**1. INFN** – Sezione di Perugia **4. INFN** – Sezione di Pisa

2. UNIMORE – Università di Modena e Reggio Emilia 🚺 🔂 3. DIEI – Università di Perugia LPNHE

## INTRODUCTION

At high luminosity LHC (5·10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>), the number of interactions per bunch crossing will increase to 140 (and up to 200), and the trigger challenges due to the high pileup will be enormous.

- The silicon-based tracking information is the most effective way for pileup mitigation, if it can be made available to L1 trigger within the required latency (~5 microseconds)

- A dedicated hardware processor is hence the proposed solution to be used at L1 trigger to select interesting configurations at the 40 MHz bunchcrossing rate [1]

- The proposed CMS phase II L1 tracking trigger is conceptually organized in 48 trigger towers (6 η x 8 φ)

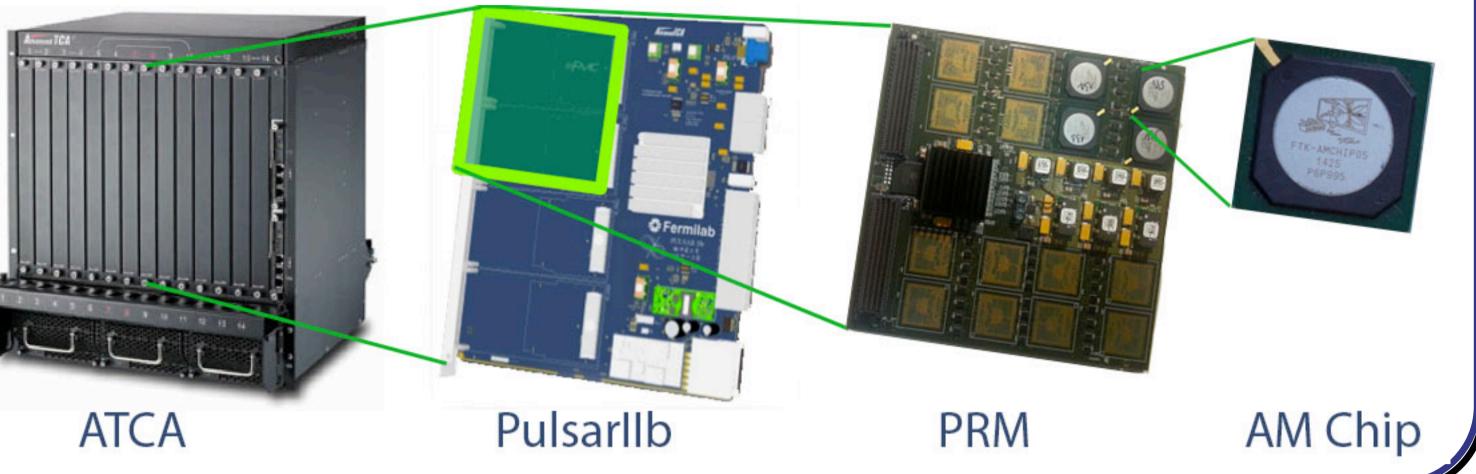

- Each tower is managed by a Advanced Telecom Computing Architecture (ATCA) crate. The basic card slot in each crate is the Pulsar II board [2]

The Pattern Recognition Mezzanine (PRM) based on the Associative Memory and the FPGA technologies

We aim to built a prototype of the system with the state of the art technology to show the feasibility of the project.

## PATTERN RECOGNITION MEZZANINE ARCHITECTURE

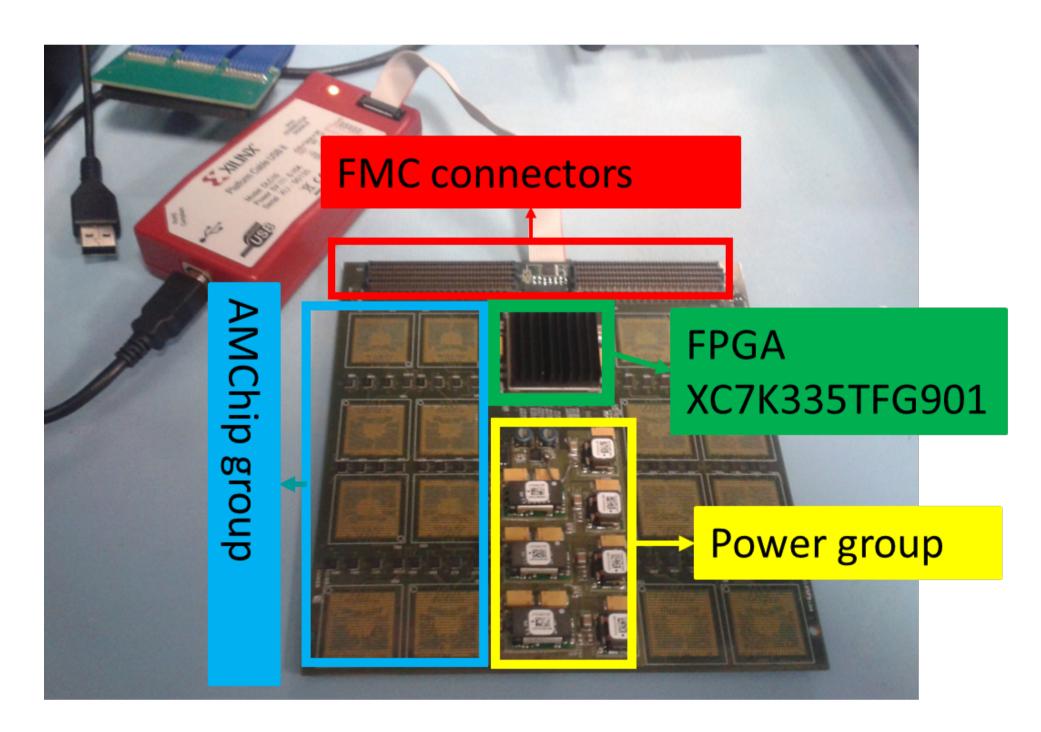

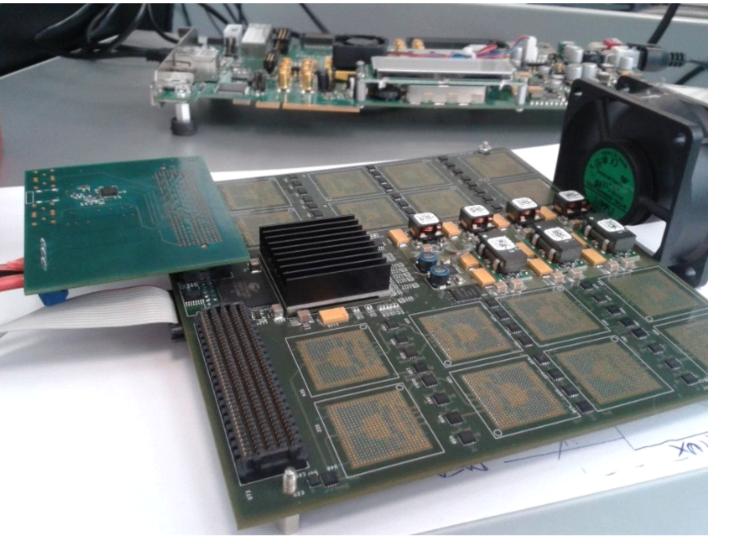

The Pattern Recognition Mezzanine (PRM) is a 14.9 x 14.9 cm<sup>2</sup> card hosting two High Pin Count connectors (FMC), a Xilinx FPGA (XC7355T) and 16 AM chips. The FPGA will have the role of routing the hits coming from the tracker layers, collecting the candidate tracks and performing a track fitting operation.

# **EXPERIMENTAL SETUP**

#### The experimental setup consists of:

**5. LPNHE Paris**

- loopback card providing the power and connects in loop the High Speed Serial I/O of the FMC connectors;

- the PRM board.

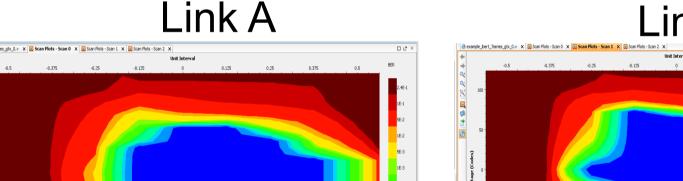

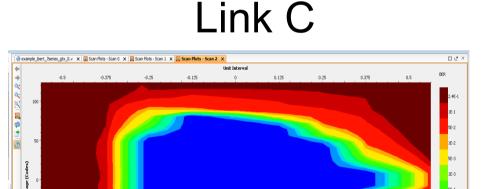

The eye diagram of the High Speed Serial links are tested with the IBERT core of the FPGA and a serial data analyzer.

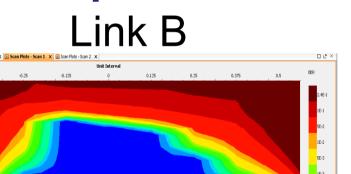

### **FPGA – FMC connector links: 8 Gbps**

#### The logic resources of the Pattern Recognition Mezzanine

- 16 Associative Memory Chips for a total amount of patterns:

- PRM with AM05  $\rightarrow$  2 kpatterns \* 16 AM chips = 32 kpatterns/PRM

- PRM with AM06  $\rightarrow$  128 kpatterns \* 16 AM chips = 2 Mpatterns/PRM

## **EVENT TRACK RECONSTRUCTION**

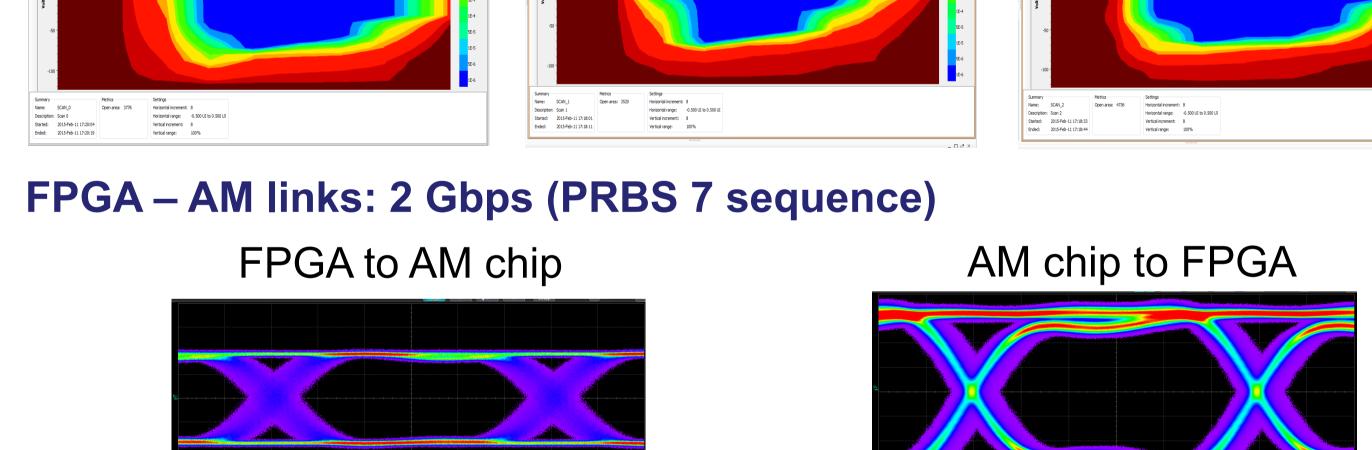

#### Pattern Matching (AM approach)

The Associative Memory has a modular architecture in which each chip includes both the memory required for storing candidate tracks (patterns) and the logic needed for the actual comparison.

- The device compares the SuperStrips ID (SSID) with all the stored patterns.

- The device returns the addresses (Road ID) of the matching locations.

#### Data Organizer (FPGA logic and memories)

The Data Organizer (DO) implements a SmartDB containing the SuperStrip ID and the Road ID value according to the information written in the Associative Memory chip.

**Track Fitting (FPGA logic)** A fit is done computing all combinations of hits across layers.

## CONCLUSION

The proposed processor for the L1 track trigger provides high computation power combining the Associative Memory and the FPGA technologies. It implements also the Data Organizer and Track Fitter stages to minimize the latency of the whole processing chain.

#### REFERENCE

[1] A. Annovi et al., Associative Memory for L1 Track Triggering in LHC environment, Nuclear Science, IEEE Transactions on, vol. 60, no. 5, pp. 3627–3632, Oct 2013

[2] J Olsen et al. A full mesh ATCA-based general purpose data processing board, 2014 JINST 9 C01041

**Contact person:** GIACOMO FEDI, giacomo.fedi@pi.infn.it

13° Pisa Meeting on Advanced Detectors 24-30 May 2015 Isola d'Elba (Italy)

This project has received funding from Progetto PRIN MIUR DM 28.12.2012 n.957

This project has received funding from the European Union's seventh Framework Programme for research, technological development and demonstration under grant agreement n.31744