University of Bergamo Department of Engineering and Applied Sciences

<sup>2</sup> University of Pavia, Department of Electrical, Compute and Riomedical Engineering

# Design and test of clock distribution circuits for the Macro Pixel ASIC

L. Gaioni<sup>1</sup>, F. De Canio<sup>2,3</sup>, M. Manghisoni<sup>1,3</sup>, L. Ratti<sup>2,3</sup>, V. Re<sup>1,3</sup>, G. Traversi<sup>1,3</sup>, A. Marchioro<sup>4</sup>, K. Kloukinas<sup>4</sup>

IINFIN

<sup>3</sup> INFN ne di Pavia Pavia, Italy

CERN

\*\*\*\*\*

\*\*\*\*\*

\*\*\*\*\*

\*\*\*\*\*

## Introduction

The innermost part of the **CMS tracker** at the HL-LHC is based on a combination of pixelated and short strip sensors, the socalled **Pixel-Strip module**. The short strip layer is read out as a classical strip detector by means of the Strip Sensor ASIC, while the pixelated layer is readout by means of the **Macro Pixel ASIC** (MPA), bump bonded to the sensor, as normally done in hybrid pixels. **Clock distribution** circuits account for a significant fraction of the **power dissipation** in the readout chip: the clock signal must indeed be distributed all over the chip with minimum possible skew. While keeping the skew at a minimum, clock distribution networks waste a significant amount of power. A **65nm CMOS test chip**, including the clock distribution

A **65nm CMOS test chip**, including the clock distribution circuits of the MPA, has been fabricated and tested. The prototype chip includes metal structures emulating the long clock lines that will be laid out in the final design of the MPA, and two versions of the drivers and the receivers suitable for operation in the readout chip. A summary of the **simulation and experimental results**, focused on the power and speed performance, will be given in this work.

# The Macro Pixel ASIC

#### **MPA main characteristics**

- 16x120 matrix featuring a pixel size of 1500 μm x 100 μm

- Designed in a 65 nm CMOS

- technology

Limited power budget (~200 mW)

- available to carry out the complex functions integrated in the chip

40 MHz clock operating frequency

In the design phase of the prototype chip, two routing schemes for the clock distribution have been investigated: the **column distribution** (CD) and the **row distribution** (RD)

# Investigated architectures and simulation results

- CD scheme for the MPA consumes a huge amount of power due to the large number of columns

- The integrated solution features an RD architecture where a central buffer column distributes the clock along the matrix and 1 clock line per row distributes the clock to the 120 pixel cells in the row

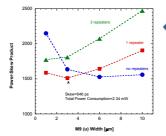

- A study of the optimum number and dimension of repeaters to be placed on the central column (laid out with ultrathick metal M9) has been carried out

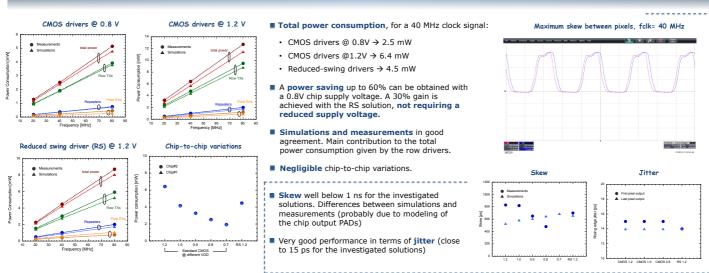

- Two possible implementations have been investigated, based on CMOS buffers supplied with reduced VDD and on reduced swing drivers

- We evaluated each architecture in terms of total power consumption (including the contribution from row drivers, pixel receivers and column repeaters) and the maximum skew between pixels. A comparison with conventional full swing buffers (1.2 V) has been carried out.

Reduced supply voltage

Standard CMOS buffers as TXs and RXs, supplied by VDDL=800  $\rm mV$

## **Reduced-swing driver**

The M3 nMOS transistor is inserted between the pMOS and nMOS transistors of a simple inverter to **decrease the output voltage swing**. An asymmetric inverter involving an LVT nMOS and a HVT pMOS can be used **as the receiver**.

Column distribution

| Simulations carried out for different number |               |  |  |  |  |

|----------------------------------------------|---------------|--|--|--|--|

| of buffers in the central column,            | for different |  |  |  |  |

| column width                                 |               |  |  |  |  |

|                                              |               |  |  |  |  |

|               | Skew @<br>rising edge<br>[ps] | Skew @<br>falling edge<br>[ps] | Average<br>Skew [ps] | Total Power<br>Consumption<br>[mW] | Power-<br>Skew<br>Product<br>[fJ] |

|---------------|-------------------------------|--------------------------------|----------------------|------------------------------------|-----------------------------------|

| 0.8V Solution | 632                           | 660                            | 646                  | 2.34                               | 1512                              |

| Low-swing     | 489                           | 636                            | 562                  | 4.34                               | 2441                              |

| 1.2V Solution | 435                           | 447                            | 441                  | 5.41                               | 2386                              |

**Measurements results**

13th Pisa Meeting on Advanced Detectors, May 24-30 2015, La Biodola, Isola d'Elba (Italy)