# An "artificial retina" processor for track reconstruction at the full LHC crossing rate **Riccardo Cenci** Scuola Normale Superiore and INFN, Pisa

**Problem: trigger efficiently hadronic events at very high luminosity (>10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>)**

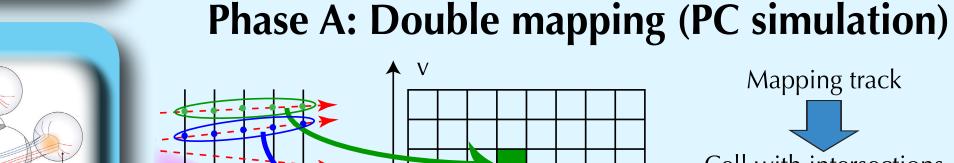

#### The "Artificial Retina" algorithm<sup>[1]</sup>

• Highly-parallel algorithm inspired to quick detection of edges in mammals visual cortex

- Continuous response with limited number of pre-calculated patterns, which allows a coarser grid mapping of parameters

- Reconstruction of charged-particle trajectories (tracks) at LHC collisions frequency with **few** µ**s latency**, which allows to trigger hadronic events

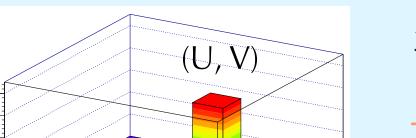

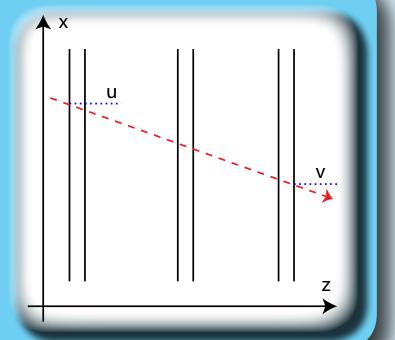

**Detector layers**

Tracks

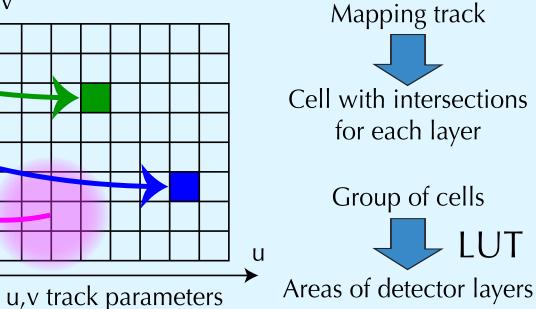

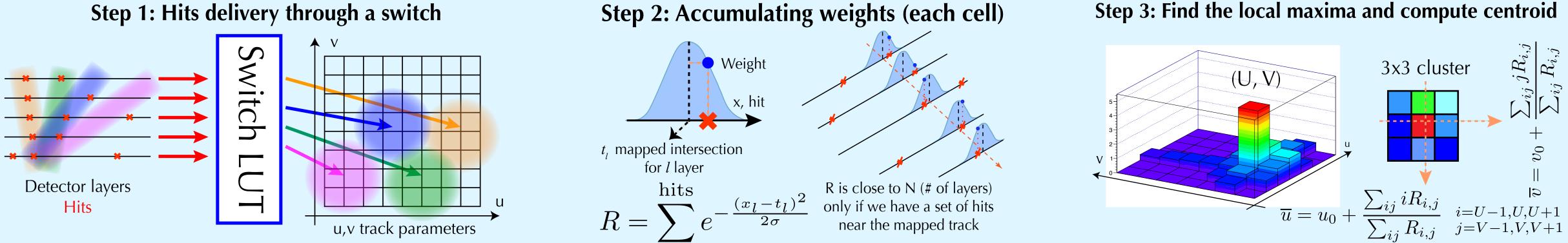

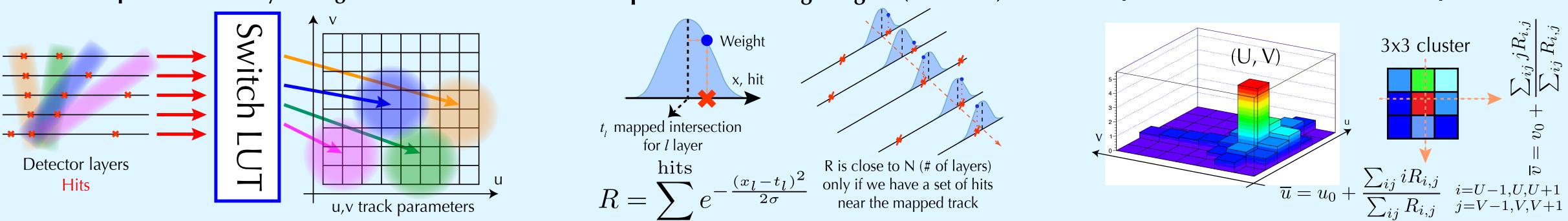

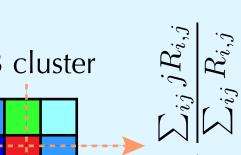

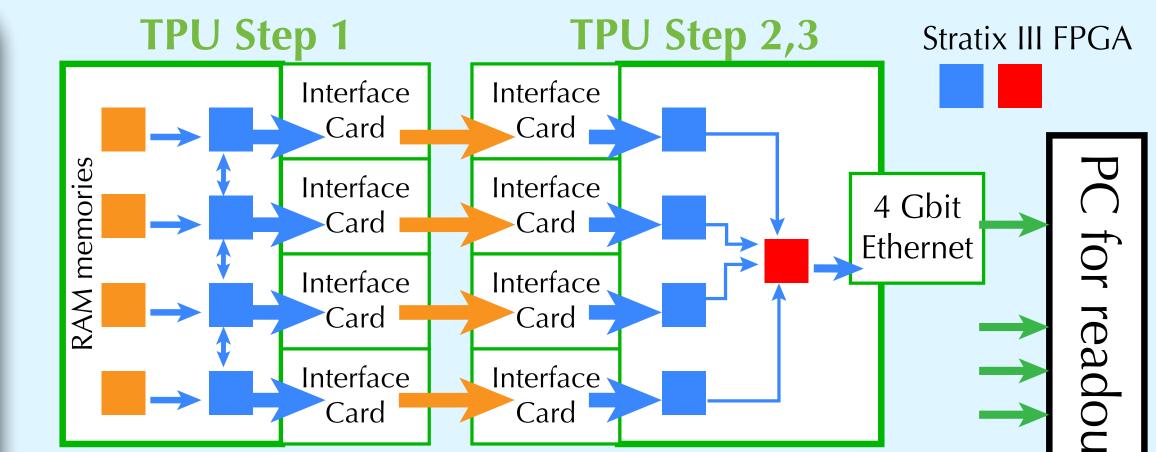

### **Phase B: Reconstruction (FPGA, Track Processing Unit TPU)**

## Goal: reconstruct high quality tracks for events at 40 MHz, lab prototype at 1 MHz

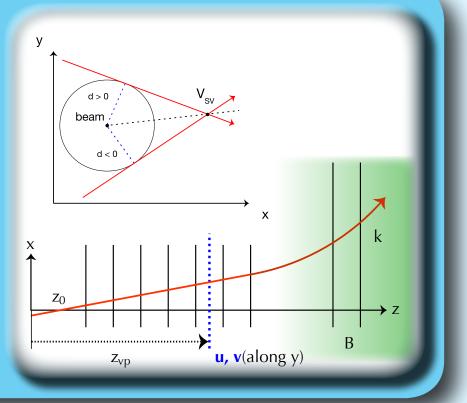

#### **Study for a real-detector application**<sup>[2]</sup>

- Forward spectrometer, **pixel silicon tracker** with fringe magnetic field, independent subset of LHCb tracker in 2020

- Track parameters: intersections u,v with virtual plane at  $z_{vp}$

- Track origin shifts  $(z_0, d)$  and curvature (k) are included as perturbations

- Available testing events: single track, simulated using official LHCb simulation<sup>[3]</sup> with 2020 conditions after the upgrade

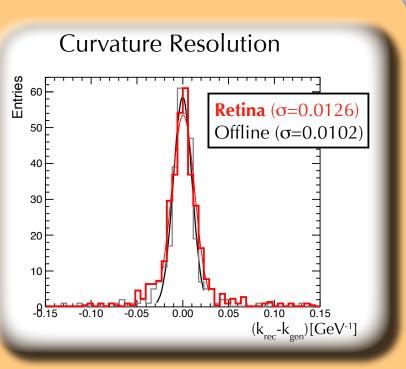

#### **Study results**<sup>[2]</sup>

- Using about 20k cells, reconstruction performances equal to offline algorithms • Basic logic implementation in VHDL on

- Altera Stratix V FPGA, event processing time is about 150 clock cycles (**0.5** µ**s** latency @350MHz)

- 20k cells fit into 32 Stratix V chips

#### **First prototype**<sup>[4]</sup>

- Simplified tracker with 6 single-coordinate layers (x silicon strips)

- Track parameters: first and last layer coordinates (u,v)

- Available testing events: single track, simulated, real data

#### **Prototype Results**

- Good reconstruction efficiency with about 3k cells, fit into 32 Stratix III chips

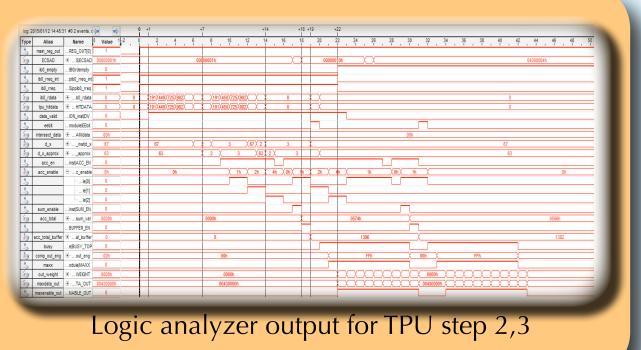

- TPU step 2,3: firmware designed and simulated<sup>[5]</sup>

- TPU step 2,3: firmware **fully working on the real**

- board at 160 MHz, including Ethernet output to PC

- Using detector occupancy from real data and switch simulation, max event rate is 1.8 MHz

#### **Prototype tech details**<sup>[6]</sup>

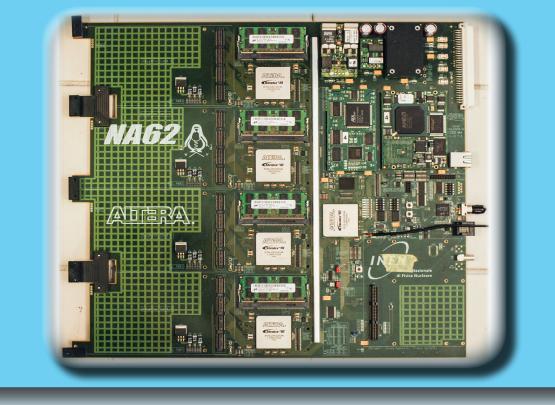

- **Tel62** board developed by INFN for NA62

- FPGA Altera Stratix III: 4 processing unit (PP's) controlled by one master (SL)

- Clock: 40 MHz, 160 MHz inside FPGA's

- Memory: 4x2Gb DDR2, 64bit@640MHz

- I/O rate: 10 Gbit PP to SL, 5 Gbit on generic mezzanine slot (x4), 2.5 Gbit between PP's and SL to Ethernet card

- Slow control interface (embedded PC)

#### x4 (8 Tel62 boards, 3k cells)

Results shown here have been achieved by "Retina", a 3-year project funded by INFN, Division of technological research experiments (CNS5) Participants: A. Abba<sup>4,6</sup>, F. Bedeschi<sup>1</sup>, F. Caponio<sup>4,6</sup>, R. Cenci<sup>1,3</sup>, M. Citterio<sup>4</sup>, A. Cusimano<sup>4,6</sup>, J. Fu<sup>4</sup>, A. Geraci<sup>5</sup>, M. Grizzuti<sup>4,6</sup>, N. Lusardi<sup>4,6</sup>, P. Marino<sup>1,3</sup>, M. J. Morello<sup>1,3</sup>, N. Neri<sup>4</sup>, D. Ninci<sup>1,2</sup>, M. Petruzzo<sup>4,5</sup>, A. Piucci<sup>1,2</sup>, G. Punzi<sup>1,2</sup>, L. Ristori<sup>7</sup>, F. Spinella<sup>1</sup>, S. Stracka<sup>1,3</sup>, D. Tonelli<sup>8</sup>, J. Walsh<sup>1</sup> <sup>1</sup>INFN Pisa, <sup>2</sup>Università di Pisa, <sup>3</sup>Scuola Normale Superiore di Pisa, <sup>4</sup>INFN Milano, <sup>5</sup>Università di Milano, <sup>6</sup>Politecnico di Milano, <sup>7</sup>Fermilab, <sup>8</sup>CERN

#### **References:**

[1] L. Ristori, An artificial retina for fast track finding, NIM A453 (2000) 425.

[2] A. Abba et al., A specialized track processor for the LHCb upgrade, CERNa-LHCb-PUB-2014-026.

[3] M. Clemencic et al., The LHCb simulation application, Gauss: Design, evolution and experience, J. Phys. Conf. Ser. 331, 032023 (2011).

[4] A. Piucci, *Reconstruction of tracks in real time at high luminosity environment at LHC*, Master thesis, https://etd.adm. unipi.it/theses/available/etd-06242014-055001/. [5] D. Ninci, Real-time track reconstruction with FPGA at LHC, https://etd.adm.unipi.it/theses/available/etd-11302014-212637/. [6] F. Spinella *et al.*, The TEL62: A real-time board for the NA62 Trigger and Data Acquisition. Data flow and firmware design, IEEE Nucl. Sci. Symp. Conf. Rec., 1 (2014).

Additional material can be found at: https://web2.infn.it/RETINA/index.php/en/

13th Pisa Meeting on Advanced Detectors, La Biodola (Italy), May 24-30, 2015