Development of arrays of Silicon Drift Detectors and readout ASICs for the SIDDHARTA experiment

R. Quaglia<sup>(1)</sup>, <u>F. Schembari</u><sup>(1)</sup>, G. Bellotti<sup>(1)</sup>, A. D. Butt<sup>(1)</sup>, C. Fiorini<sup>(1)</sup>, L. Bombelli<sup>(2)</sup>, G. Giacomini<sup>(3)</sup>, F. Ficorella<sup>(3)</sup>, C. Piemonte<sup>(3)</sup>, N. Zorzi<sup>(3)</sup>

<sup>1</sup> Politecnico di Milano, DEIB & INFN, Sezione di Milano, Milano, Italy <sup>2</sup> XGLab srl, Milano, Italy <sup>3</sup> Fondazione Bruno Kessler FBK, Trento, Italy

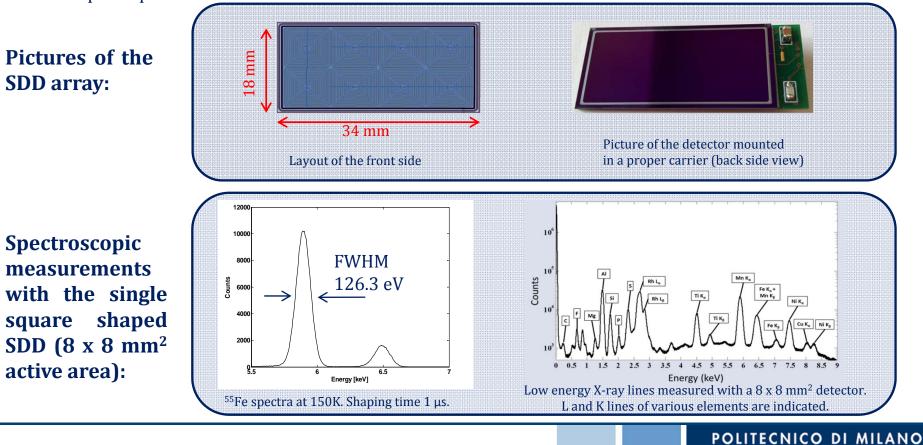

In the framework of the INFN-SIDDHARTA experiment a new SDD array has been developed. This array is characterized by eight independent elements organized in a 4 x 2 format (square SDD). Each channel is connected to a CUBE preamplifier.

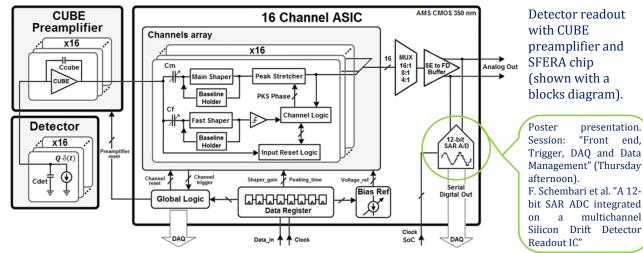

## **Readout ASIC – SFERA chip**

The output of the CUBE preamplifiers are connected to a common ASIC called SFERA (SDDs Front-End Readout ASIC) that is a 16 channels Integrated Circuit that performs analog shaping and peak detection of the signals.

- Technology: AMS 0.35 μm;

- Area 25 mm<sup>2</sup>;

- 16 channels;

- 9<sup>th</sup> order semi-gaussian filter;

- Peaking times: 0.5, 1, 2, 3, 4, 6 μs;

- Gains: 10, 16, 36, 50 keV and 20 ke<sup>-</sup>;

- Pile-up rejector;

- Multiplexer Output: 16:1, 8:2, 4:1;

- Polling or "sparse" multiplexer readout;

- 256-bit internal configuration register;

- 12 bit SAR ADC;

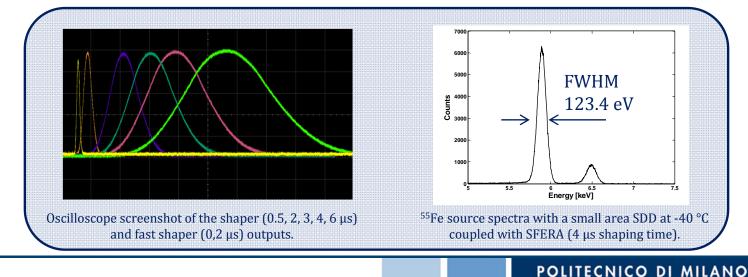

## Experimental results: