# Trigger-less DAQ How to transform a detector in a PC peripheral

Umberto Marconi

INFN Bologna

Catania, Novembre 2014

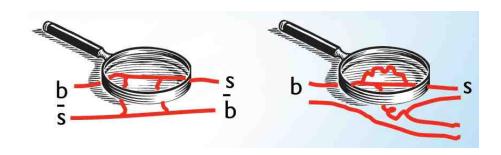

#### The LHCb experiment

- LHCb is a **high-precision experiment** devoted to the search for New Physics beyond the Standard Model:

- By studying CP violation and rare decays in the b and c-quark sectors.

- Searching for deviations from the SM due to virtual contributions of new heavy particles in loop diagrams.

- Past and running experiments have shown that:

- Flavour changing processes are consistent with the CKM mechanism.

- Large sources of flavour symmetry breaking are excluded at the TeV scale.

- The flavour structure of the NP, if it exists, would be very peculiar at the TeV scale.

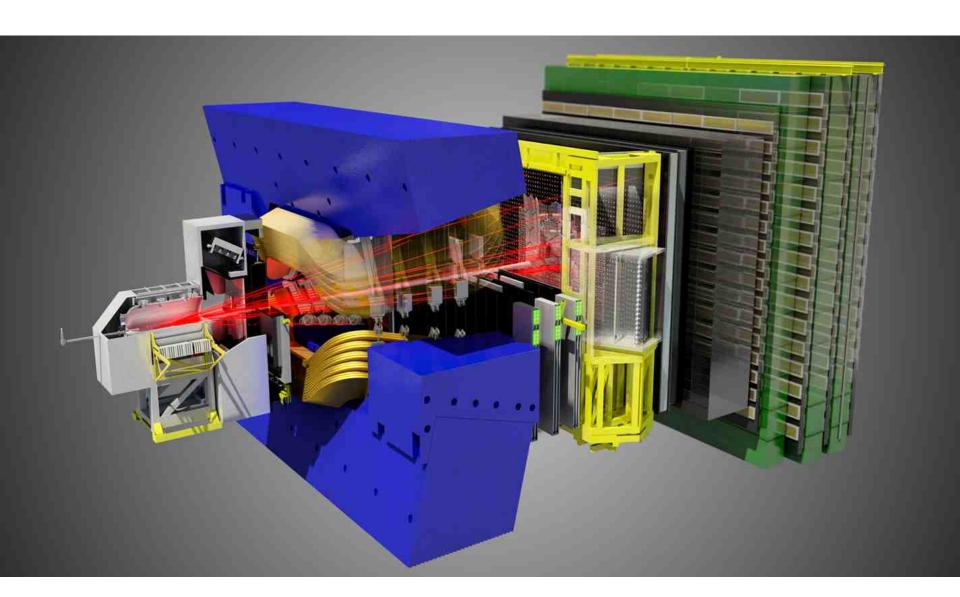

#### The LHCb Detector

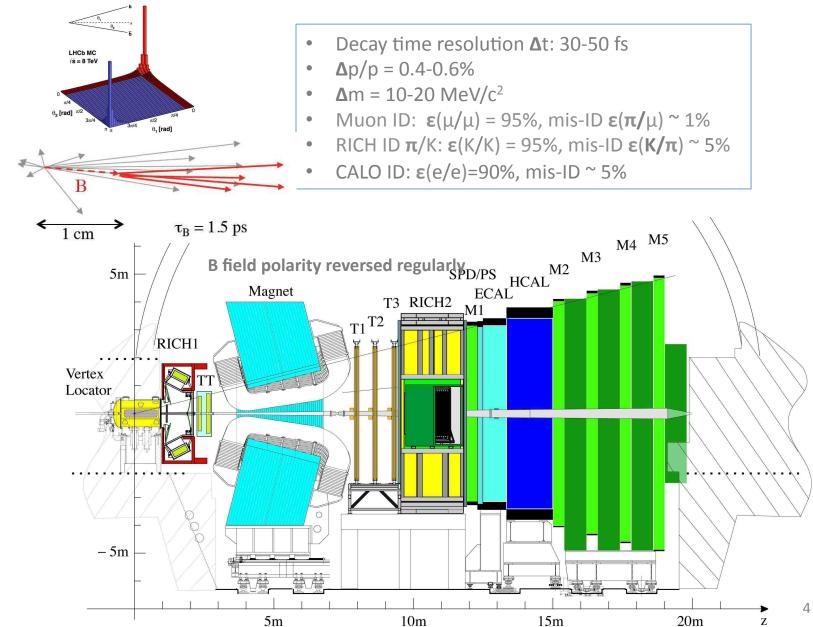

#### The LHCb detector

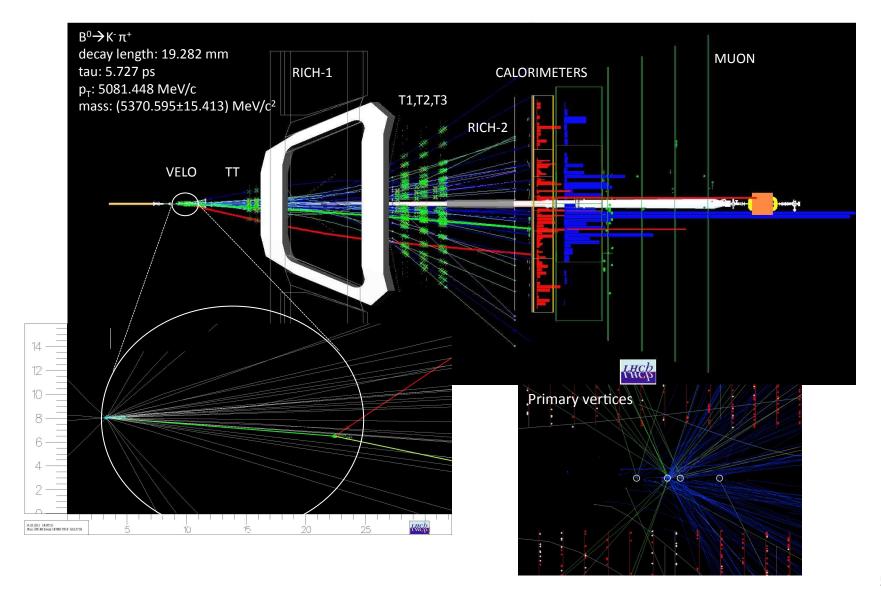

#### LHCb events

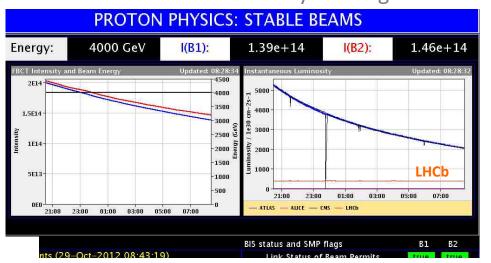

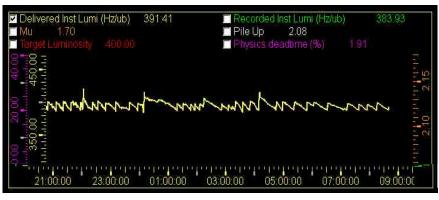

#### Instantaneous Luminosity

• Instantaneous luminosity leveling at  $4 \times 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup>, ±3% around the target value

- LHCb was designed to operate with a single collision per bunch crossing, running at a instantaneous luminosity of  $2 \times 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup> (assuming about 2700 circulating bunches).

- At the time of design there were worries about possible ambiguities in assigning the B decay vertex to the proper primary vertex among many.

- Soon LHCb realized that running at higher multiplicities would have been possible. In 2012 we run at  $4 \times 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup> with only 1262 colliding bunches.

- 50 ns separation between bunches while the nominal 25 ns (will available by 2015).

- 4 times more collisions per crossing than planned in the design.

- The average number of visible collisions per crossing in 2012 raised up to  $\mu > 2.5$  ( $\mu$ : average n. of visible interactions)

## Heavy flavour signatures

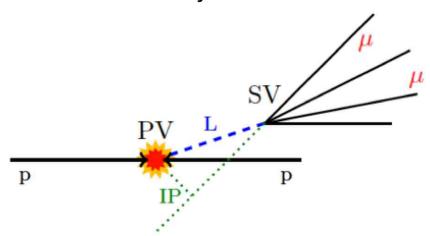

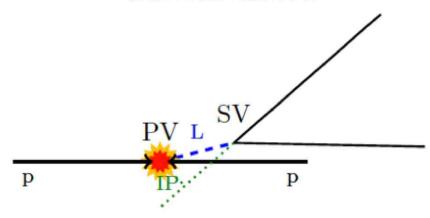

#### Beauty hadrons

- $B^+$  mass 5.28 GeV, daughter  $p_T$   $\mathcal{O}(1 \, \text{GeV})$

- lifetime ≈ 1.6 ps ⇒ flight distance

≈ 1 cm

- common signature: detached μμ

#### Charmed hadrons

- $D^0$  mass 1.86 GeV, sizeable daughter  $p_T$

- lifetime ≈ 0.4 ps ⇒ flight distance

≈ 4 mm

- can be produced in B decays

## The present LHCb Trigger

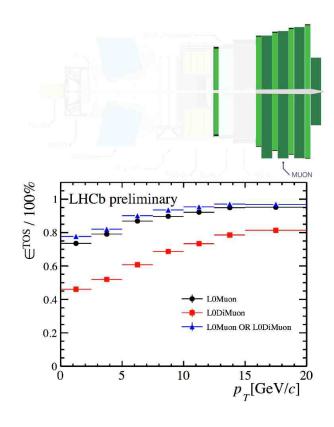

#### Muon Based L0 Triggers

#### Reconstructs muon track segments

•  $\Delta p/p \approx 20\%$

#### Two L0 muon triggers:

- single muon,  $p_T > 1.76 \,\text{GeV}$

- dimuon,  $p_{T1} \times p_{T2} > (1.6 \,\text{GeV})^2$

- total rate ≈ 400 kHz

Typically over 90% efficiency (wrt offline selected  $B \rightarrow J/\psi K$ )

## The present LHCb Trigger (2)

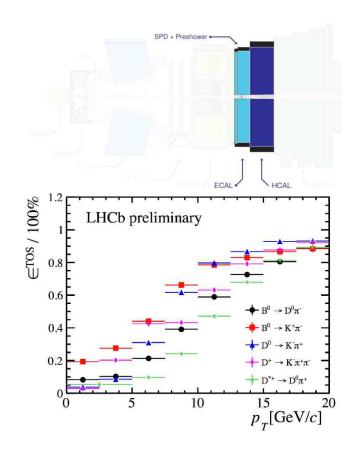

#### Calorimeter Based LO Triggers

Select high  $E_T$  hadrons, electrons and photons

Preshower and SPD discriminate between electrons and photons

#### L0 hadron trigger:

- threshold 3.6 GeV

- rate ≈ 490 kHz

L0 electron, photon:

- threshold 3 GeV

- rate ≈ 150 kHz

- $\approx 80\%$  efficient for  $B \rightarrow X\gamma$  (wrt offline selection)

**Total LO rate** ≈ 1 MHz

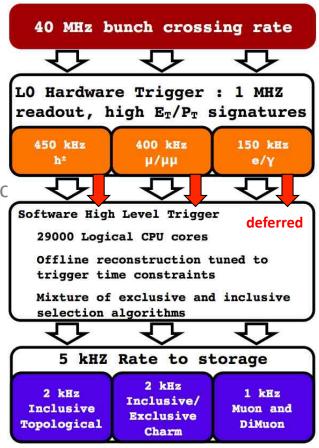

## The present LHCb Trigger

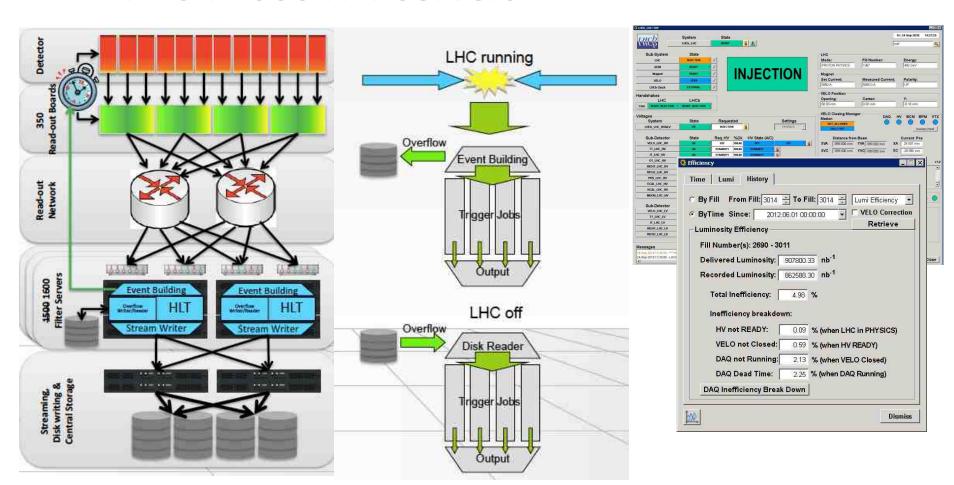

- The Level-0 trigger operates at 40 MHz, with a maximum output rate limited to 1.1 MHz.

- Custom electronics, fully pipelined,

constant latency of about 4 μs.

- Bandwidth to the HLT ~ 1.5 Tb/s,

through GOL serializers ~1 Gb/s and optical links.

- 25% of the events are deferred: temporarily stored c disk and processed with the HLT farm during the inter-fills.

- The HLT is a software trigger.

- Reconstruct VELO tracks and primary vertices

- Select events with at least one track matching  $p, p_T$ , impact parameter and track quality cuts.

- At around 50 kHz performs inclusive or exclusive selections of the events.

- Full track reconstruction, without particleidentification.

- Total accept rate to disk for offline analysis is 5 kHz.

# farm-nodes

# core-routers

# edge routers

max. input bw / farm-node

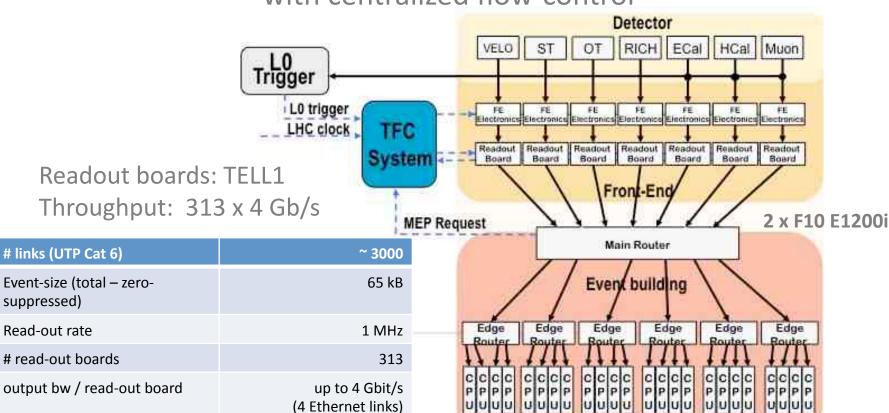

#### LHCb DAQ today

Switched packed network, push protocol, with centralized flow-control

1 Gbit/s Fast Control Signals

2

56

1500 (up to 2000)

**HLT farm**

#### Deferred trigger

2 TB on 1000 HLT servers

#### Push based event building

- Run at > 90% link load.

- Multi Event Packets: aggregate O(10) event fragments and just drop them onto the wire.

- IP Datagrams: no resend, no explicit flow control.

- Rely on network hardware with large buffers to handle traffic flow pattern.

- Link aggregation load balancing is not 100% fair nor standardized.

- 1 Gb/s ≠ 1 Gb/s: there is a small ± which can cause trouble at very high link loads.

- Commercial network stuff most of the time does not work off the shelf.

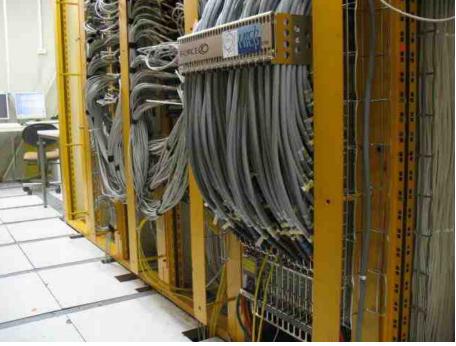

#### The core router

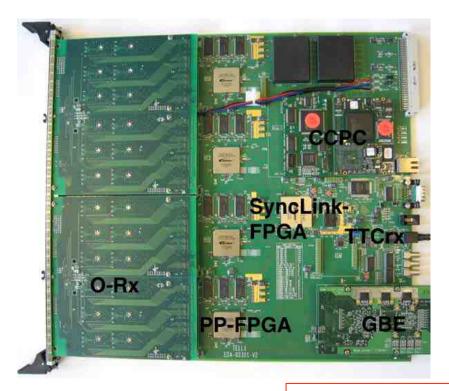

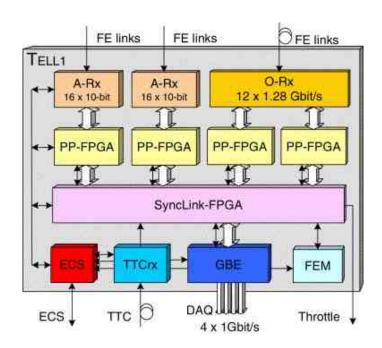

#### The readout-board TELL1

TTC in Throttle out

4 x 1 GbE (UTP)

Central FPGA pushing data via UDP

#### The 1MHz LO rate limitation

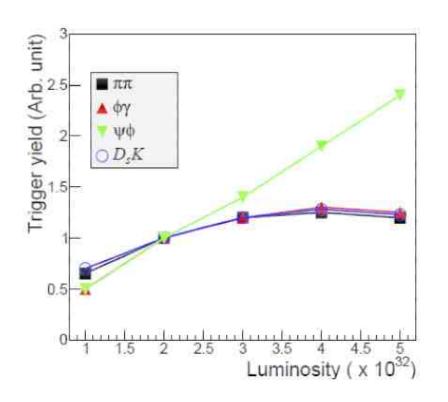

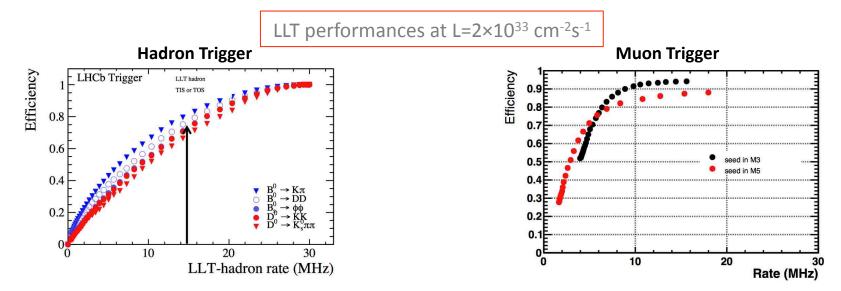

- Due to the available bandwidth and the limited discrimination power of the hadronic L0 trigger, LHCb experiences the saturation of the trigger yield on the hadronic channels around  $4 \times 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup>

- Increasing the first level trigger rate considerably increases the efficiency on the hadronic channels.

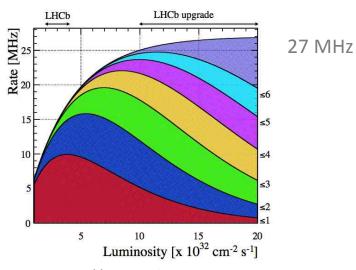

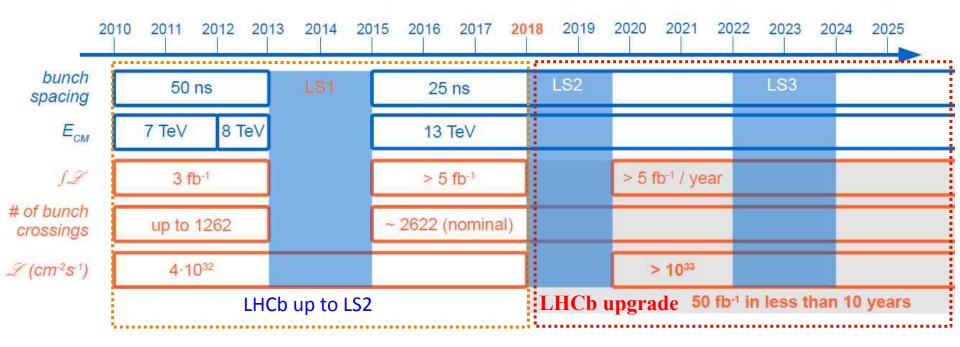

## The LHCb upgrade

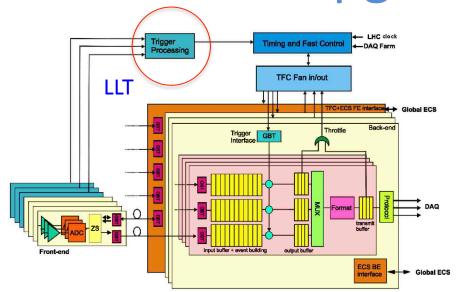

- Readout the whole detector at 40 MHz.

- Use a Low Level Trigger as a throttle mechanism.

- Trigger-less data acquisition system

running at the highest possible frequency.

- We have foreseen to reach 20 × 10<sup>32</sup>

cm<sup>-2</sup>s<sup>-1</sup> and therefore to prepare the subdetectors on this purpose.

- pp interaction rate 27 MHz

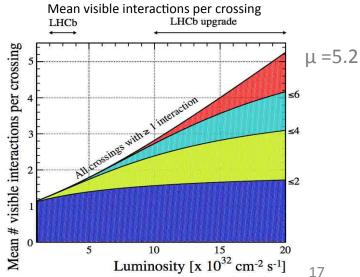

- At 20. ×  $10^{32}$  cm<sup>-2</sup> s<sup>-1</sup>pile up μ ≅ 5.2

- Increase the yield in the decays with muons by a factor five and the yield of the hadronic channels by a factor ten.

- Collect 50 fb<sup>-1</sup> of data over ten years.

- 8 fb<sup>-1</sup> is the integrated luminosity target,

to reach by 2018 with the present detector;

3.2 fb<sup>-1</sup> collected so far.

- The upgrade shall take place during the Long Shutdown 2 (LS2) in 2018/19.

#### **Running Conditions**

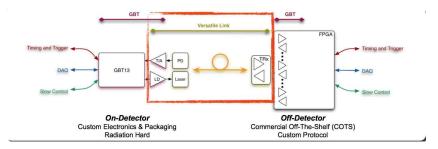

## Istituto Nazionale di Fisica Nucleare LHCb upgrade: consequences

- The detector front-end electronics has to be entirely rebuilt, because of the current readout speed is limited to 1 MHz.

- Synchronous readout, no trigger.

- No more buffering in the front-end electronics boards.

- Zero suppression and data formatting before transmission to optimize the number of required links.

- Average event size 100 kB

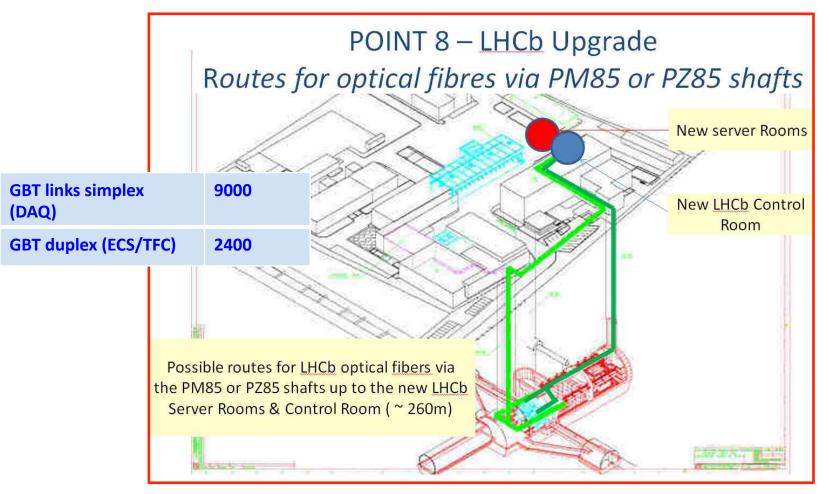

- Three times the optical links as currently to get the required bandwidth, needed to transfer data from the front-end to the read-out boards at 40 MHz.

- GBT links simplex (DAQ) 9000, GBT duplex (ECS/TFC) 2400

- New HLT farm and network to be built by exploiting new LAN technologies and powerful many-core processors.

- Rebuild the current sub-detectors equipped with embedded frontend chips.

- Silicon strip detectors: VELO, TT, IT

- RICH photo-detectors: front-end chip inside the HPD.

- Consolidate sub-detectors to let them stand the foreseen luminosity of 20.  $\times$  10<sup>32</sup> cm<sup>-2</sup> s<sup>-1</sup>

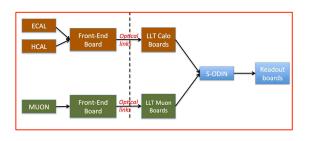

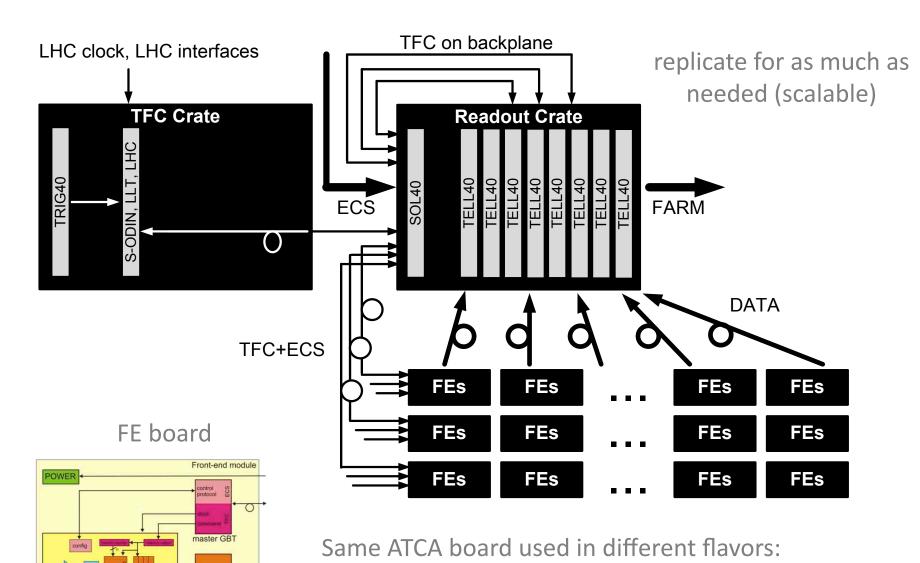

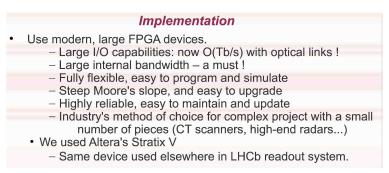

#### DAQ upgrade: First idea

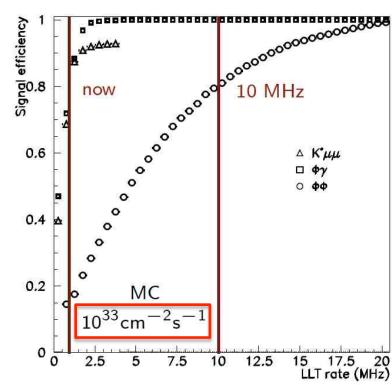

Hardware LLT to provide a reduction in the rate of input events to be processed by the Event Filter Farm (EFF),

At 15 MHz, efficiency between 65% and 80% for hadronic channels, 85%-95% for muons

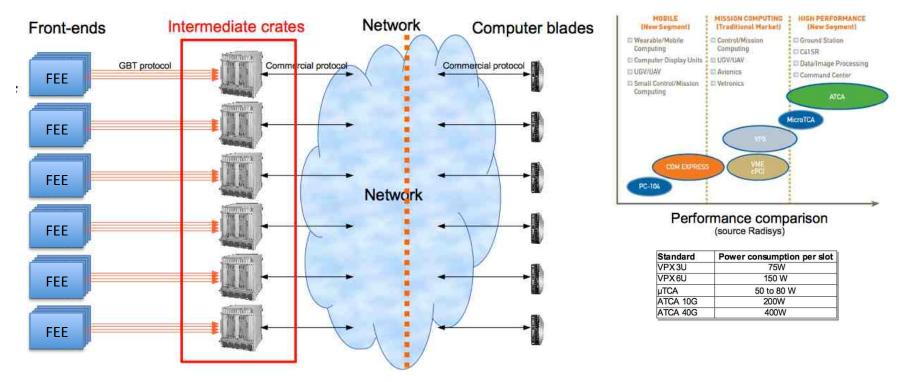

## DAQ upgrade: First idea (2)

- Intermediate layer of electronics boards arranged in crates to decouple FEE and PC farm: for buffering and data format conversion.

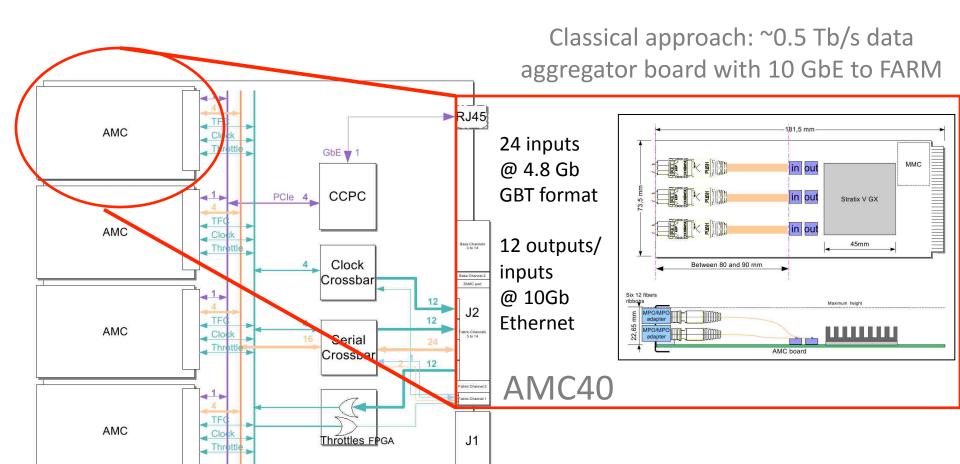

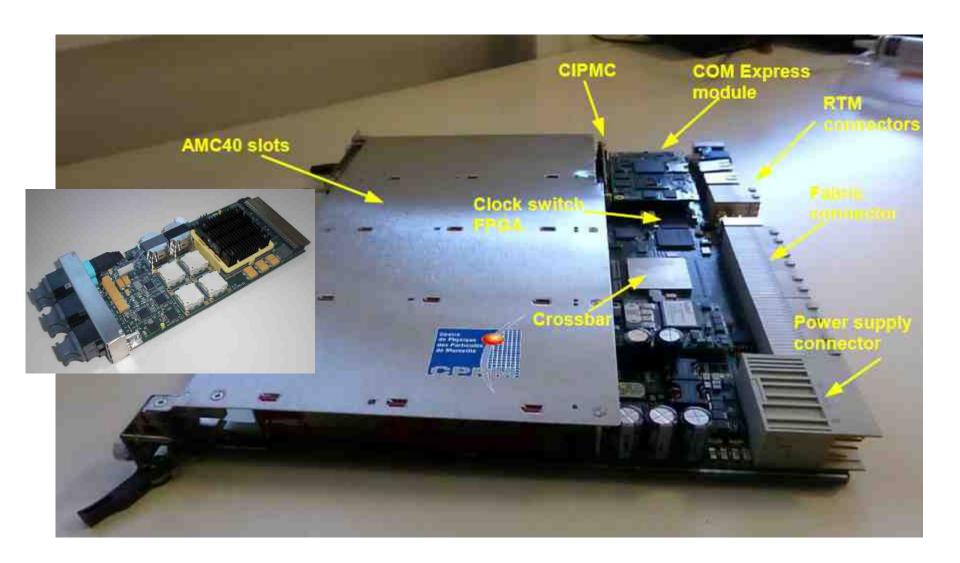

- The optimal solution with this approach: ATCA, μTCA crates, ATCA carrier board hosting AMC standard mezzanine boards.

- AMC boards equipped with FPGAs to de-serialize the input streams and transmit eventfragments to the farm, using a standard network protocol, using 10 GbEthernet.

## DAQ upgrade: First idea (3)

same generic hardware, different firmware

21

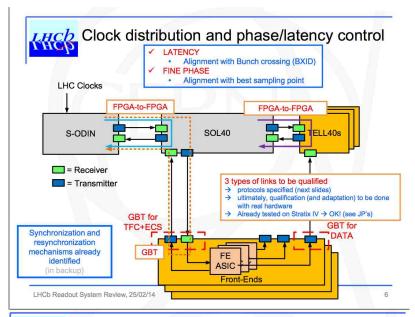

#### TELL40

**AMC40 Input**: 24 inputs @ 4.8 Gb GBT format, **Output**: 12 outputs/inputs @ 10GbE **TELL40** 96 inputs @ 4.8 Gb  $\rightarrow$  processing in FPGA  $\rightarrow$  48 x 10 Gb Ethernet ports

#### TELL40

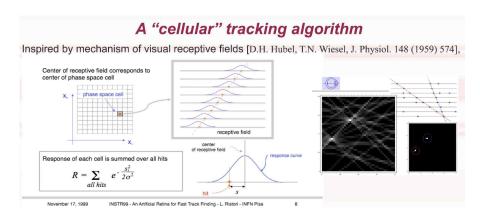

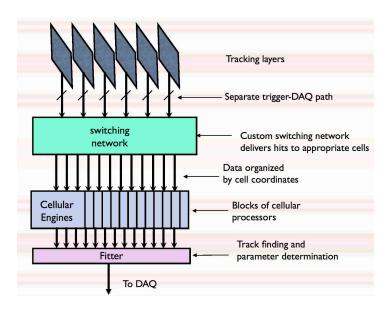

## TPU: HLT assisted tracking

- "A specialized processor for track reconstruction at the LHC crossing rate".

<a href="https://indico.inp.nsk.su/contributionDisplay.pycontribld=129&sessionId=6&confld=0">https://indico.inp.nsk.su/contributionDisplay.pycontribld=129&sessionId=6&confld=0</a>

- "We have shown with a realistic detector arrangement that it is possible to reconstruct tracks and measure their parameters very well with a "brain inspired" cell-matrix method."

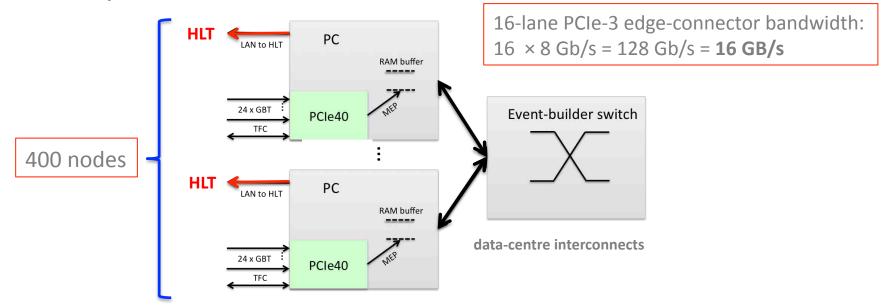

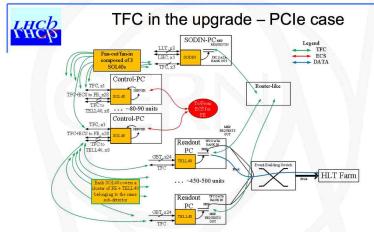

#### DAQ present view

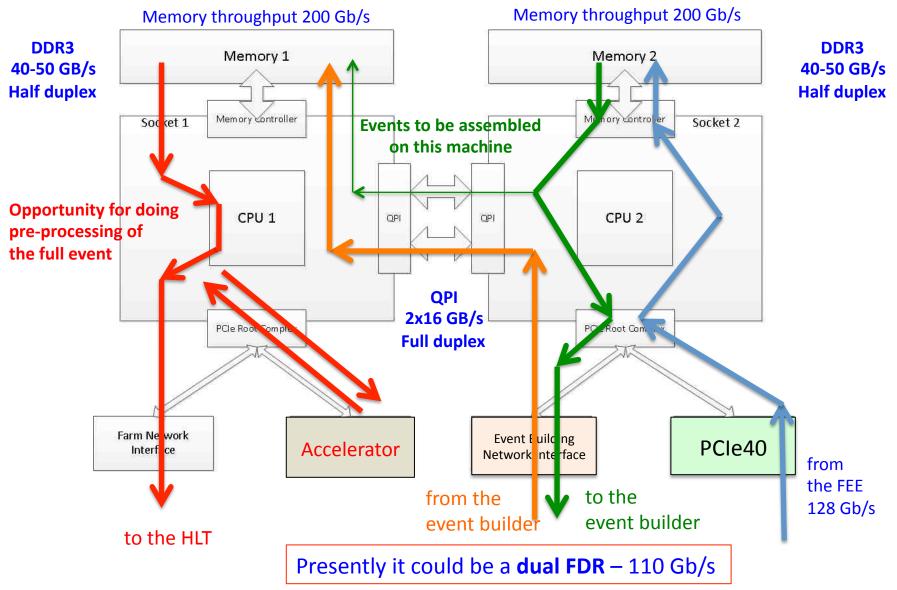

Use PCIe Generation 3 as communication protocol to inject data from the FEE directly into the event-builder PC ...

- A much cheaper event-builder network because data-centre interconnects can be used on the PC, which are not realistically implementable on an FPGA (large software stack, lack of soft IP cores,...)

- Moreover PC provides: huge memory for buffering, OS and libraries.

Up to date network adapter cards and drivers available as pluggable modules.

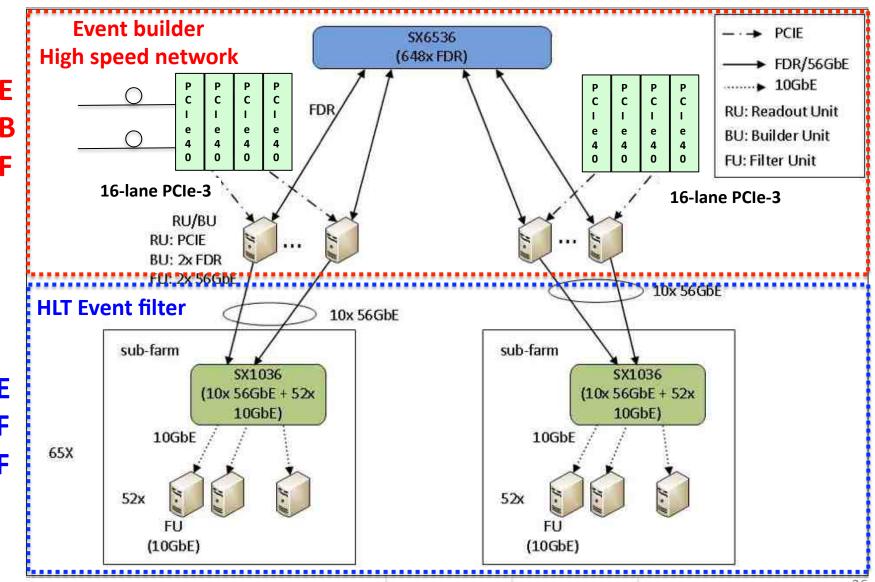

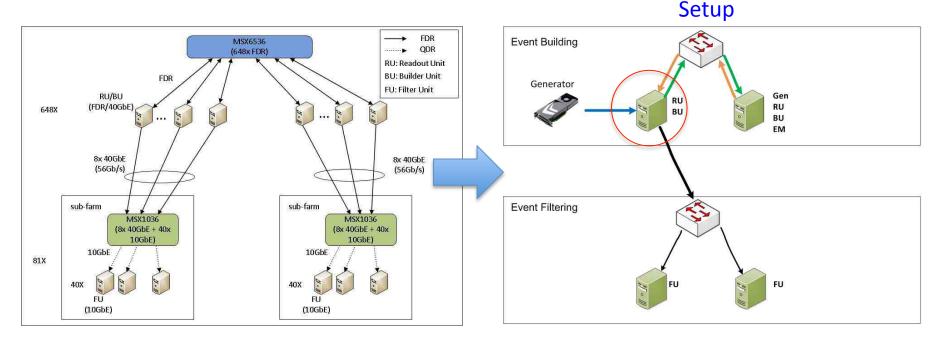

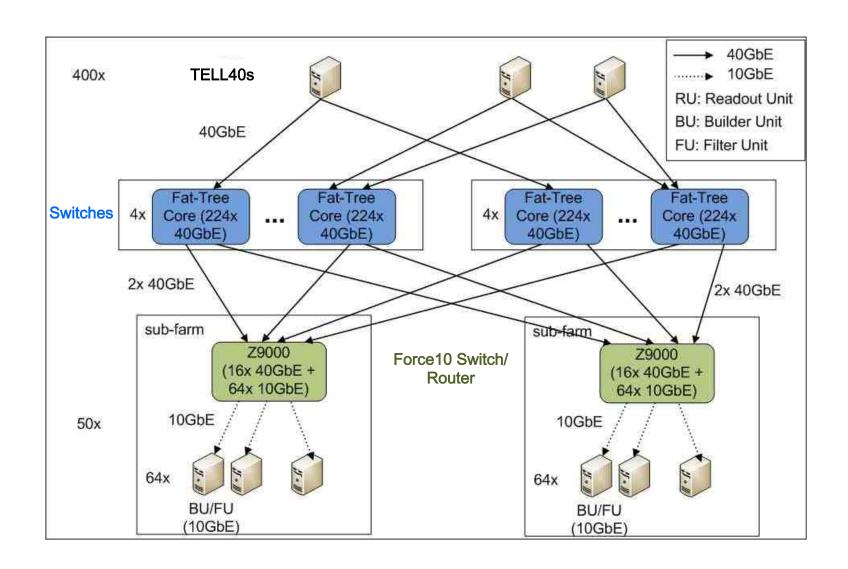

#### DAQ network

26

## **EB Network Topology**

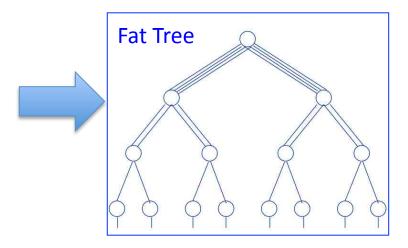

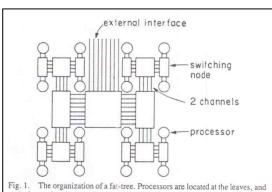

- Fat-Tree (Constant Bisectional Bandwidth).

- The fat tree topology maintains identical bandwidth at each level of the network.

- The Fat Tree topologies do not scale linearly with the cluster size. Cabling and switching become increasingly difficult and

expensive as cluster size grows, with very large core switches required for larger clusters

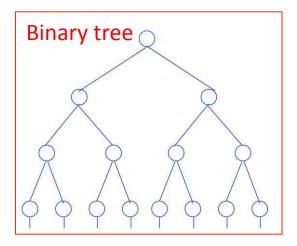

- In the simple **binary tree**, the number of links and thus the aggregate bandwidth is reduced by half at each stage of the network.

Fig. 1. The organization of a fal-tree. Processors are located at the leaves, and the internal nodes contain concentrator switches. The capacities of channels increase as we go up the tree.

Fat-Trees: Universal Networks for Hardware-Efficient Supercomputing, C.E. Leiserson. IEEE Transactions on Computers, Vol 34, October 1985, pp 892-901

Note that the links are bidirectional so the notion of upstream and downstream describes the direction of the interconnect topology towards or away from the shortest path to an end node, rather than the actual data flow.

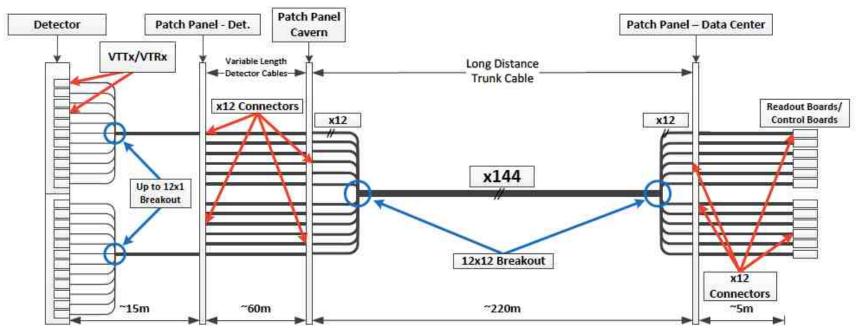

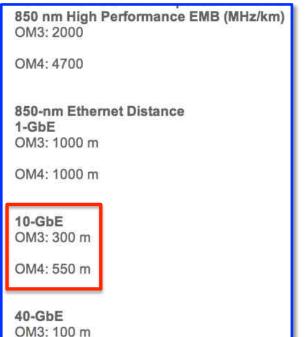

## Long distance fibres

Locate the **Event Builder Farm** and the **Event Filter Farm** for the HLT **outside** the cavern.

The distance to cover with 850 nm OM multimode optical cables, from underground to the surface, is **300 m**.

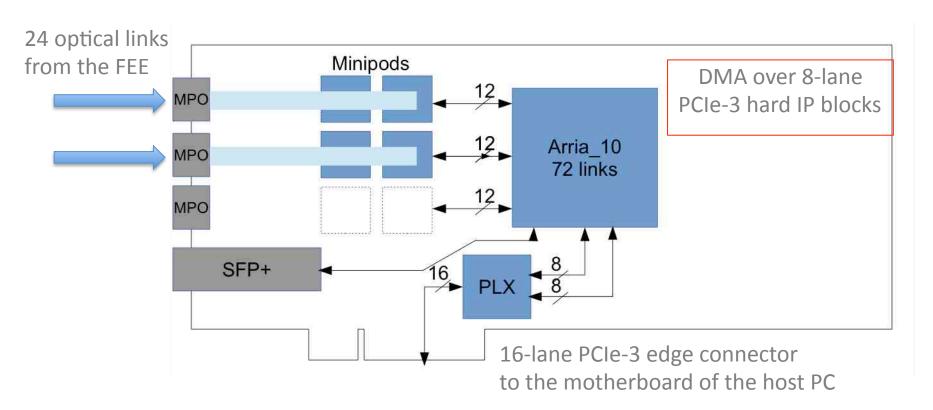

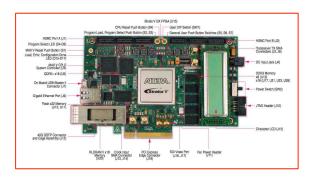

#### PCIe Gen3 based readout

- A main FPGA manages the input streams and transmits data to the event-builder PC by using DMA over PCIe Gen3.

- The readout version of the board uses two de-serializers.

- The same board can be used to clock and control distribution.

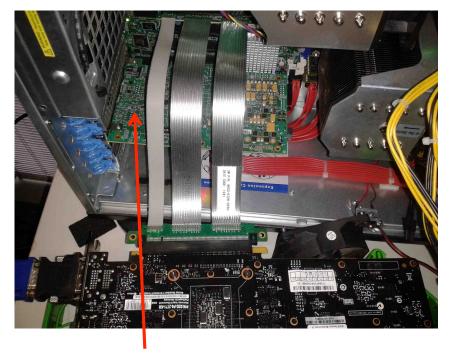

#### The PCIe-3 test setup

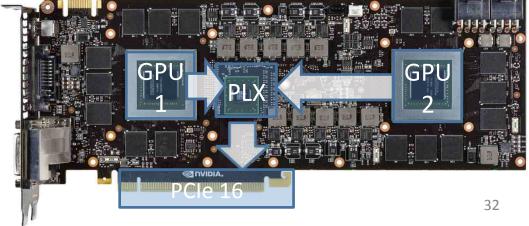

GPU used to test 16-lane PCIe-3 data transfer between the device and the host memory

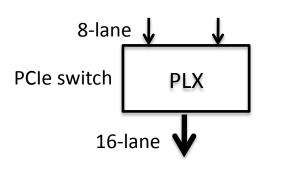

The FPGA provides 8-lane PCIe-3 hard IP blocks and DMA engines.

ALTERA development board, Stratix V GX FPGA, model 5SGXEA7K2F40C2N

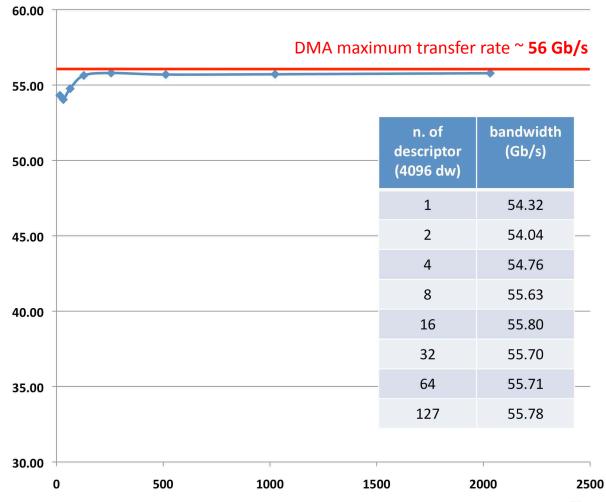

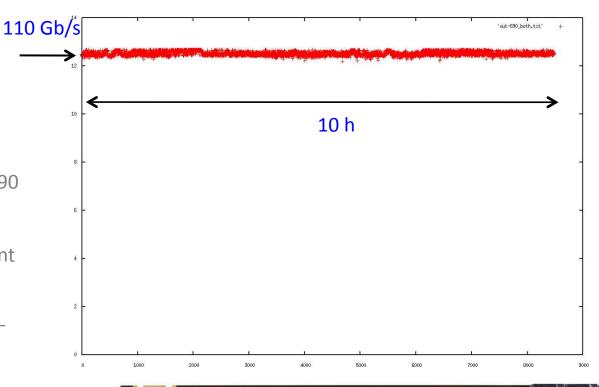

## DMA PCIe-3 effective bandwidth

Throghput[Gb/s]

DMA over 8-lane PCIe-3 hard IP blocks ALTERA Stratix V

#### Test of PLX bridge

- Long-term test using GTX690 card / PLX 8747 bridge.

- Zero impact of using a bridge and two independent PCIe targets pushing data into a PC. Consistently around 110 Gb/s over longterm.

- No load balancing issues between the two competing links observed.

- Details at:

https://

lbonupgrade.cern.ch/wiki/

index.php/I/

O\_performance\_of\_PC\_serv

ers#Upgrade\_to\_GTX690

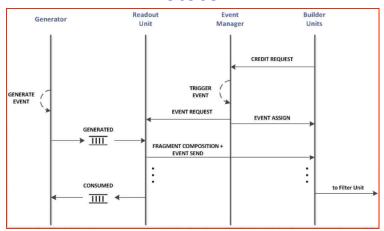

## Event builder fluxes: 400 Gb/s

#### PC event-builder tests

#### **Protocol**

- Test with a Ivy Bridge Intel dual CPU, 12 cores, PC.

- InfiniBand FDR connections

- OpenMPI-based application

#### **EVB** performance

At about 400 Gb/s more than 80% of the CPU resources are free

The CPUs used in the test are Intel E5-2670 v2 with a C610 chipset. The servers are equipped with 1866 MHz DDR3 memory in optimal configuration. Hyper-threading has been enabled.

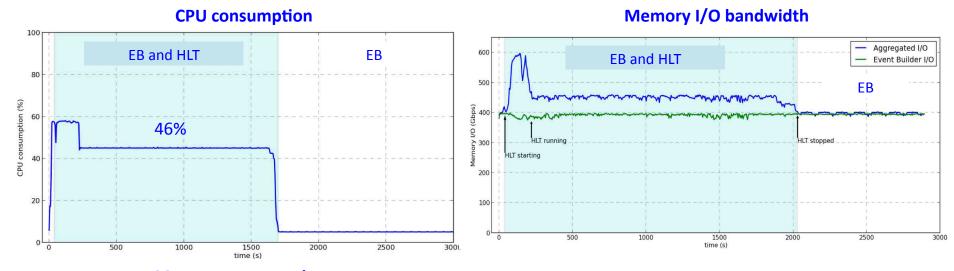

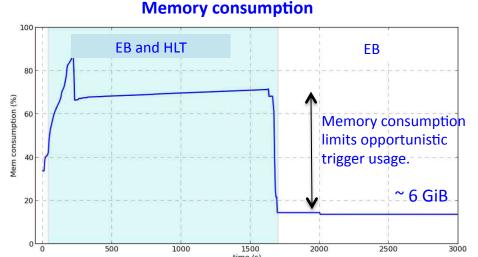

#### PC sustains the event building at 100 Gb/s today.

- The Event Builder performs stably at 400 Gb/s

- Aggregated CPU utilization of EB application and trigger 46%

- We currently observe **50% free resources for opportunistic triggering on EB nodes**: event builder execution requires about 6 logical core. Additional 18 instances of the HLT software running simultaneously.

#### Software LLT

- The LLT algorithms can be executed in the event builder PC after the event building.

- Preliminary studies show that the LLT runs in less than 1 ms, if the CALO clusters are built in the FEE.

- Assuming 400 servers, 20 LLT processes running per PC, and a factor 8 for the CPU power from the Moore Law, the time budget available turns out to be safely greater then 1ms:

$$\frac{1}{40MHz} \times 400 \times 20 \times 8 \approx 3.2 \, ms$$

processing time budget =

$$\frac{1}{\text{event rate}} \times \text{nodes} \times \text{cores per node} \times \text{task per node}$$

#### DAQs Upgrade

#### Future LHC DAQs in numbers

|       | Event-size [kB] | Rate [kHz] | Bandwidth [Gb/s] | Year [CE] |

|-------|-----------------|------------|------------------|-----------|

| ALICE | 20000           | 50         | 8000             | 2019      |

| ATLAS | 4000            | 200        | 6400             | 2022      |

| CMS   | 2000            | 200        | 3200             | 2022      |

| LHCb  | 100             | 40000      | 32000            | 2019      |

- Some overlapping trends across experiments, at least conceptually

- o custom-made Readout Boards with fast optical links and big&powerful FPGAs

- ✓ ideally with fast interface to PCs (PCIe Gen3 or future...)

- ✓ ideally with some co-processing (Xeon, GPUs...)

- o commercial network technologies following market trends in terms of BW & costs

- ✓ distributed vs data-center-like network.

- ✓ network technologies: Ethernet vs InfiniBand.

### LHCb upgrade: HLT farm

- Trigger-less system at 40 MHz:

A selective, efficient and adaptable software trigger.

- Average event size: 100 kB

- Expected data flux: 4 TB/s

- Total HLT trigger process latency: ~15 ms

- Tracking time budget (VELO + Tracking + PV searches): 50%

- Tracking finds 99% of offline tracks with  $p_T > 500 \text{ MeV/c}$

- Number of running trigger process required: 4×10<sup>5</sup>

- Number of core/CPU available in 2018: ~ 200

- Intel tick-tock plan: 7nm technology available by 2018-19, the number of core accordingly scales as  $12 \times (32 \text{ nm}/7 \text{ nm})^2 = 250$ , equivalent 2010 cores.

- Number of computing nodes required: ~ 1000

The most powerful CPU ever built: IBM Power8 CPU, http://www.extremetech.com/computing/181102-ibm-power8-openpower-x86-server-monopoly

# DAQ numbers

| GBT links simplex (DAQ)                        | 9000        |

|------------------------------------------------|-------------|

| GBT duplex (ECS/TFC)                           | 2400        |

| PCIe40 (DAQ)                                   | 400         |

| SOL40 (ECS/TFC)                                | 66          |

| Estimated total mean event-<br>size            | 100 kB      |

| 100G links for event-building network @ 40 MHz | 400         |

| Dual-socket servers for High<br>Level Trigger  | 2000 – 4000 |

### Conclusions

- The concept of the LHCb experiment has been definitely proved: exploiting a forward spectrometer at a hadron collider to perform a dedicated experiment for heavy flavour physics.

- Many world leading results and many more to come with the 3.2 fb<sup>-1</sup> full data set collected.

- LHCb plans the upgrade, to be installed in 2018: the upgrade is an essential next step forward for flavour physics.

- The DAQ system we envisage for the upgrade will allow us to feed the HLT trigger and exploit its capabilities at 40 MHz.

- TDRs are all ready.

# Spare material

# **Prospects**

|             | LHC era             |                      | HL-LHC era           |                     |                       |

|-------------|---------------------|----------------------|----------------------|---------------------|-----------------------|

|             | 2010-2012           | 2015-2017            | 2019-2021            | 2024-2026           | 2028-2030+            |

| ATLAS & CMS | 25 fb <sup>-1</sup> | 100 fb <sup>-1</sup> | 300 fb <sup>-1</sup> | $\rightarrow$       | 3000 fb <sup>-1</sup> |

| LHCb        | 3 fb <sup>-1</sup>  | 8 fb <sup>-1</sup>   | 23 fb <sup>-1</sup>  | 46 fb <sup>-1</sup> | 100 fb <sup>-1</sup>  |

| Belle II    | <b>%</b> ■          | 0.5 ab <sup>-1</sup> | 25 ab <sup>-1</sup>  | 50 ab <sup>-1</sup> | -                     |

## Prospects (II)

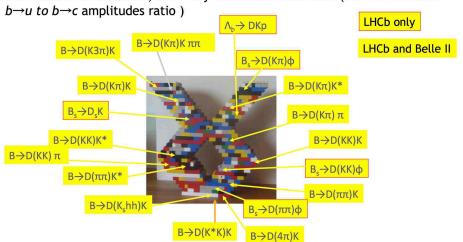

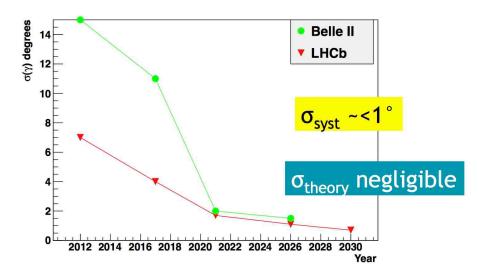

The "ultimate"  $\gamma$ -from tree-decays precision will be reached through many individual measurements, with very different sensitivities (due to different

#### Expected precision on $\gamma$ from tree decays

## **Evolution of LHC luminosity**

#### LHCb up to 2018 $\rightarrow$ ~ 8-10 fb<sup>-1</sup>:

find or rule-out large sources of flavour symmetry breaking at the TeV scale

#### LHCb upgrade $\rightarrow$ ≥ 50 fb<sup>-1</sup>:

- increase precision on quark flavour physics observables

- aim at experimental sensitivities comparable to theoretical uncertainties

- reinforce LHCb as a general purpose forward detector

# Long distance fibres (II)

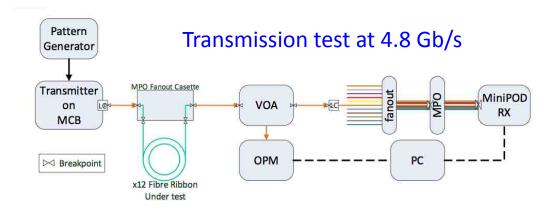

- 4.8 Gbit/s signal produced on the detector by Versatile Link transmitters.

- VTTx to MiniPod for data acquisition.

- MiniPod to VTRx for control, configuration.

- 144 fibres per cable. A total of 120 such cables.

- 3 patch panels (breakpoints) foreseen: expected attenuation ~ 3dB

**MiniPod**

OM4: 150 m

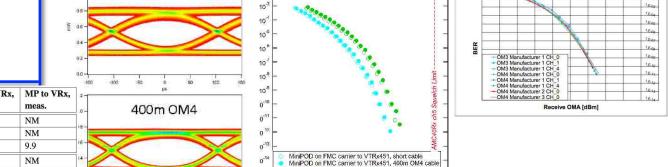

## Optical fibres studies

400m OM3

Figure 3: Schematic of Setup B, used for measuring BER vs. OMA for the DAQ direction.

Measurement of BER vs. receive OMA(\*) on different OM3 and OM4 fibres. (\*) optical modulation amplitude

MiniPOD on AMC40 ch5 to VTRx451, 400m OM4

MiniPOD on AMC40 ch5 to VTRx451, short cable

OMA [dBm]

10"

| Description               | Unit | VTTx to<br>MP, spec. | VTTx to MP, meas. | MP to VRx, spec. | MP to VRx,<br>meas. |

|---------------------------|------|----------------------|-------------------|------------------|---------------------|

| Transmitter OMA           | dBm  | -5.2                 | NM                | -3.2             | NM                  |

| Receiver sensitivity      | dBm  | -11.1                | -14.2             | -13.1            | NM                  |

| Power budget              | dB   | 5.9                  | 9.0               | 9.9              | 9.9                 |

| Fibre loss (2.3 dB/km)    | dB   | 0.9                  | NM                | 0.9              | NM                  |

| Connectors (0.5 dB/pair)  | dB   | 1.5                  | NM                | 1.5              | NM                  |

| Disp. (400 m, 4.8 Gbit/s) | dB   | 2.4                  | 0.5               | 2.4              | 0.5                 |

| TX Radiation penalty      | dB   | 0                    | NM                | 20 <del>5</del>  |                     |

| RX Radiation penalty      | dB   | -                    | -                 | 2.5              | NM                  |

| Fibre Radiation penalty   | dB   | 0.1                  | NM                | 0.1              | NM                  |

| Margin                    | dB   | 1.0                  | 6.0               | 2.5              | 4.4                 |

Comparison, 400m OM3, OM4 - OMA

### **Fast Control**

#### General considerations and conclusions

#### From TFC point of view:

- the choice of PCIe does not pose any problems in terms of hardware, functional and firmware implementation (of TFC). ATCA was already demonstrated to be adequate.

- Additional number of cards in PCle and additional number of fibers.

- No crates. Distributed system + scalability at its best.

- · No need to test backplane if going for PCle. One solution fits all.

- · No need of a motherboard if going for PCIe. Commercial PCs.

- Output bus is flexible and bigger bandwidth for ECS to FE in PCle.

- · PCle seems more flexible in terms of future development and optimizations.

- ✓ Fully 40 MHz streamlined system (data center-like).

#### My personal point of view:

- ✓ ATCA is a more compact solution, perfect for a triggered system (with LLT)

- ✓ PCle is a more distributed and streamlined solution, perfect for a trigger-less system.

- Technology at the service of development (and efficiency)!

Common electronics board for upgraded readout system: PCle-Gen3 card fitted on a host PC

- S-ODIN & SOL40 → PCle card

- TELL40 → PCle card

- LHC Interfaces → specific PCIe card (or might simply be Ethernet WhiteRabbit)

- ECS goes via PCle, TFC to TELL40 goes via fibers

#### Numbers: ATCA vs PCle

Most of the numbers from TDRs ...

(in parenthesis is the # of additional SOL40 in PCIe vs ATCA)

|        | # of<br>Master<br>GBTs | # of TELL40s<br>for data<br>(24 input) | # SOL40s<br>(24 input) | # SOL40s<br>(36 input) |

|--------|------------------------|----------------------------------------|------------------------|------------------------|

| VELO   | 156                    | 104<br>(16 input)                      | 11 (+4)                | 8 (+3)                 |

| UT     | 168                    | 55                                     | 10 (+3)                | 7 (+1)                 |

| RICH   | 1030                   | 77                                     | 47 (+4)                | 31 (+2)                |

| Sci-Fi | 678                    | 113                                    | 33 (+4)                | 22 (+3)                |

| CALO   | 72                     | 53                                     | 6 (+3)                 | 4 (+1)                 |

| MUON   | 140                    | 24                                     | 7 (+1)                 | 5 (+1)                 |

| TOTAL  | 2244                   | 426                                    | 114 (+19)              | 77 (+11)               |

Only additional complication is the ACTIVE fan-in/fan-out of TFC and throttle information to TELL40s and FE (> 3 boards needed of 36 input/output)

→ While maintaining partitioning and logical separations

#### DAQ event-builder

# The LHCb upgrade: physics

LHCb upgrade: statistical sensitivity to key observables

| Туре                      | Observable                                                             | Current precision         | LHCb 2018             | Upgrade<br>(50 fb <sup>-1</sup> ) | Theory<br>uncertainty |

|---------------------------|------------------------------------------------------------------------|---------------------------|-----------------------|-----------------------------------|-----------------------|

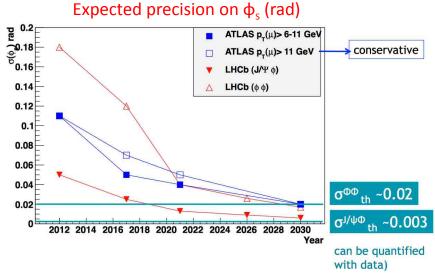

| $B_s^0$ mixing            | $2\beta_s(B_s^0 \to J/\psi \phi)$                                      | 0.10 [139]                | 0.025                 | 0.008                             | ~0.003                |

|                           | $2\beta_s(B_s^0 \to J/\psi f_0(980))$                                  | 0.17 [219]                | 0.045                 | 0.014                             | ~0.01                 |

|                           | $a_{ m sl}^{ m s}$                                                     | $6.4 \times 10^{-3}$ [44] | $0.6 \times 10^{-3}$  | $0.2\times10^{-3}$                | $0.03 \times 10^{-3}$ |

| Gluonic penguins          | $2\beta_s^{ m eff}(B_s^0 	o \phi\phi)$                                 | =                         | 0.17                  | 0.03                              | 0.02                  |

|                           | $2\beta_s^{\text{eff}}(B_s^0 \to K^{*0}\overline{K}^{*0})$             | -                         | 0.13                  | 0.02                              | < 0.02                |

|                           | $2\beta^{\rm eff}(B^0 \to \phi K_S^0)$                                 | 0.17 [44]                 | 0.30                  | 0.05                              | 0.02                  |

| Right-handed currents     | $2\beta_s^{\rm eff}(B_s^0 \to \phi \gamma)$                            | -                         | 0.09                  | 0.02                              | < 0.01                |

|                           | $	au^{ m eff}(B^0_s	o\phi\gamma)/	au_{B^0_s}$                          | -                         | 5 %                   | 1 %                               | 0.2 %                 |

| Electroweak penguins      | $S_3(B^0 \to K^{*0} \mu^+ \mu^-; 1 < q^2 < 6 \text{ GeV}^2/c^4)$       | 0.08 [68]                 | 0.025                 | 0.008                             | 0.02                  |

|                           | $s_0 A_{\rm FB}(B^0 \to K^{*0} \mu^+ \mu^-)$                           | 25 % [68]                 | 6 %                   | 2 %                               | 7 %                   |

|                           | $A_{\rm I}(K\mu^+\mu^-; 1 < q^2 < 6 {\rm GeV^2/c^4})$                  | 0.25 [77]                 | 0.08                  | 0.025                             | ~0.02                 |

|                           | $\mathcal{B}(B^+\to\pi^+\mu^+\mu^-)/\mathcal{B}(B^+\to K^+\mu^+\mu^-)$ | 25 % [86]                 | 8 %                   | 2.5 %                             | ~10 %                 |

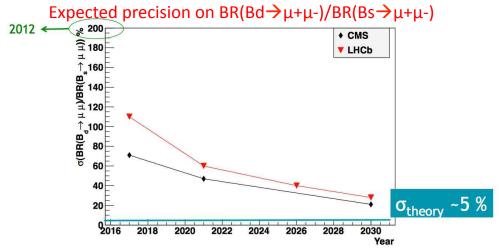

| Higgs penguins            | $\mathcal{B}(B_s^0 	o \mu^+\mu^-)$                                     | $1.5 \times 10^{-9}$ [13] | $0.5 \times 10^{-9}$  | $0.15 \times 10^{-9}$             | $0.3 \times 10^{-9}$  |

|                           | $\mathcal{B}(B^0\to\mu^+\mu^-)/\mathcal{B}(B^0_s\to\mu^+\mu^-)$        | =                         | ~100 %                | ~35 %                             | ~5 %                  |

| Unitarity triangle angles | $\gamma(B\to D^{(*)}K^{(*)})$                                          | ~10-12° [252, 266]        | 4°                    | 0.9°                              | negligible            |

|                           | $\gamma(B_s^0 \to D_s K)$                                              | -                         | 11°                   | 2.0°                              | negligible            |

|                           | $\beta(B^0 \to J/\psi K_{\rm S}^0)$                                    | 0.8° [44]                 | 0.6°                  | 0.2°                              | negligible            |

| Charm CP violation        | $A_{arGamma}$                                                          | $2.3 \times 10^{-3}$ [44] | $0.40\times10^{-3}$   | $0.07\times10^{-3}$               | -                     |

|                           | $\Delta \mathcal{A}_{CP}$                                              | $2.1 \times 10^{-3}$ [18] | $0.65 \times 10^{-3}$ | $0.12 \times 10^{-3}$             | _                     |

### LHCb upgrade: TDRs

- Letter of Intent for the LHCb Upgrade. CERN-LHCC-2011-001; LHCC-I-018. 2011.

- Framework TDR for the LHCb Upgrade : Technical Design Report

- CERN-LHCC-2012-007; LHCb-TDR-12. 2012.

- LHCb VELO Upgrade Technical Design Report CERN-LHCC-2013-021; LHCB-TDR-013. 2013.

- LHCb PID Upgrade Technical Design Report CERN-LHCC-2013-022; LHCB-TDR-014. 2013.

- LHCb Tracker Upgrade Technical Design Report

CERN-LHCC-2014-001; LHCB-TDR-015. 2014

- LHCb Trigger and Online Upgrade Technical Design Report CERN-LHCC-2014-016; LHCB-TDR-016. 2014.