# Silicon Vertex Detector Upgrade for the Belle II **Experiment**

# S. Stanič, University of Nova Gorica, Slovenia

# for the Belle SVD Group

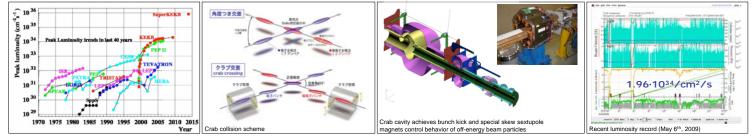

Extreme Luminosity Experiment at Y(4S) Resonance: End of 2008 the international Belle II Collaboration was inaugurated with the purpose to extend the physics reach of the present Belle experiment. The improvement is based on the SuperKEKB accelerator upgrade with a target luminosity of 8.10<sup>35</sup>/cm<sup>2</sup>/s. Belle detector will be upgraded accordingly so that efficient measurements will be possible at the highest luminosity. Thanks to functional crab crossing scheme in KEKB, which allows for head-on collisions, a record breaking 1.96·10<sup>34</sup>/cm<sup>2</sup>/s was already achieved in May 2008 (a factor of two higher than KEKB design).

### Physics at a Super B factory:

Precision measurements of CPV in B decays

•Study of time dependence of Bº - anti-Bº decays

•Study of rare decay modes of beauty and charm hadrons and  $\boldsymbol{\tau}$

#### Silicon tracker upgrade plan:

•PXD - Pixel Detector (2 inner layers) - high precision •SVD - Strip Detector (4 outer layers) - larger acceptance

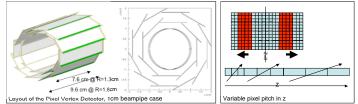

PXD Layout (based on DEPFET):

•Small radius, as close as possible to the beampipe (for 1.0cm BP case 1.3cm IL [8 modules] and 1.8cm OL [10 modules]) depending on IR

- High granularity sensors, pixel size about 50x75µm<sup>2</sup>

- •Detector should be small, 20-24 single sensor modules in two layers

•Total of ~6Mpixel, frame readout rate <10μs Possibility of variable pixel in z pitch to optimize charge sharing at large

z and improve resolution in the central part

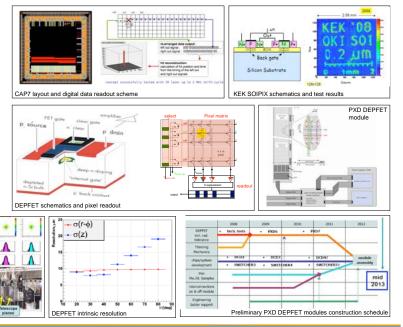

•Sensor R&D (DEPFET, CAP, SOI), all technologically promising

### PXD Sensor R&D Status - 3 variants pursued:

# CAP (Continuous Acquisition Pixels) V1-7

From basic technology studies to working pixel arrays

-Testing of digital readout CAP7 in 0.2μm OKI SOI (35x50 μm<sup>2</sup> pixel cell, 60k pixels, 3x3mm<sup>2</sup> active area) •KEK SOIPIX

-Latest prototype in 0.2μm OKI SOI, successful tests with x-rays

-Works, but problems due to back-gate-effect, plans to reduce it -LBNL beam tests - best S/N (15) at U=10V, gets worse at higher U (no full depletion)

Both offer very promising concepts for the future, however still at basic R&D

#### •DFPFFT

-Each pixel is a p-channel FET on a completely depleted bulk, deep n-implant creates a potential minimum for electrons under the gate;  $50 \times (75-115) \text{ mm}^2 \text{ pixels}$ -Signal electrons accumulate in the internal gate and modulate the transistor current  $(g_q\sim400~pA/e^{-}),$  accumulated charge removed by a clear contact ("reset") -Frame readout time <10  $\mu s$ , sequential readout of pixels or rows (line readout time 80ns, 2x4 lines per readout step)

-Low power (only few pixels active), ASICs at the periphery Most promising candidate - Evolving from basic R&D to production for Belle II ! DEPFET testing, plans and open questions:

1

Beam test of DEPFET with ILC pixel size (24 x 24 µm<sup>2</sup>)

Λ

-Beam tests at DESY (<6 GeV) and CERN (180 GeV) -Latest setup: 6 DEPFET array acting as telescope & DUT (20 M events taken)

-Radiation hardness: DEPFET works after 80kGy with low noise, large (operation mode dependent) threshold

voltage shift & dispersion, annealing helps -GEANT4 simulation started, tuned to beam test data Solve radiation related issues (try thinner oxides,

optimization of nitride/oxide thicknesses)

Start considering mechanics/cooling design, which strongly depends on IR design (fixed at latest mid 2010) -DAQ interface (PXD may deliver up to 70Gbit/s)

Pisa Meeting, May 24-31, 2009

Design requirements for the Silicon Vertex Detector:

·Good resolution in the beam direction

·Small amount of material inside the acceptance region Operation at high radiation background rates and high track density (40 x present)

Two beam-beam collision variants under investigation: High beam current and nano-beam size at IP. Silicon tracker details will depend upon that choice.

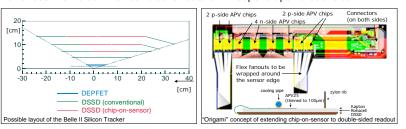

# SVD Layout:

•System size 3-4 of the present Belle SVD2 (4 layers from ~3.8 to 14cm) •Use of DSSD sensors from 6" wafer, well established technology •Additional use of alternative "chip-on-sensor" sensor types (Lower number of readout chips, less material and power dissipation in acceptance region) •Readout with APV25 (~ 50ns shaping time, sensitive window ~160ns)+ FADC+COPPER (Full DAQ chain already successfully tested in a beam test at KEK)

Conceptually proven, after finalizing the geometry ready for production.

**Belle SVD Group**