# Progetti Futuri: HV-CMOS

G. Darbo – INFN / Genova ATLAS Italia – Upgrade Phase II

Indico agenda:

https://agenda.infn.it/conferenceDisplay.py?confld=7290

## INFN \_\_\_\_

### **HV-CMOS**

### Che cos'è?

- Evoluzione delle MAPS (Monolitic Active Pixel Sensor) con l'aggiunta di un campo elettrico per la raccolta di carica

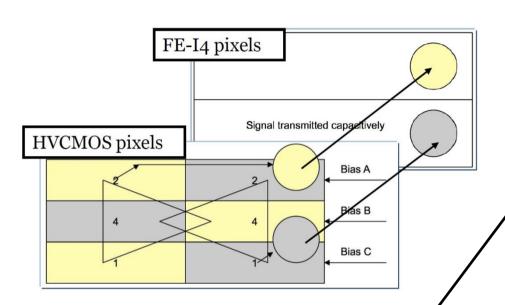

- Possibile averli in forma monolitica (ALICE) o in forma ibrida (accoppiamento con FE-I4) in modo capacitivo, tramite i pad di bump-bonding – incollaggio dell'HV-CMOS su FE-I4 (al posto del bumpbonding). Per ATLAS si punta su pixel ibridi, anche se c'è interesse a guardare quelli monolitici (sforzo enorme e tempi lunghi)

### Vantaggi

- Permette di avere dei pixel molto piccoli (~1/3 di quelli del chip di R/O) e depletion molto sottile (~10÷20 µm). → alta risoluzione spaziale

- Permette di evitare un processo costoso (bump-bonding) e sostituirlo con uno stimato più facile (incollaggio di precisione)

### Svantaggi

- Segnale molto piccolo (MIP rilascia 800 e in 10µm)

- Tecnologia ancora non matura molte cose ancora da comprendere

- Interconnessioni al mondo esterno: FE-I4 e HV-CMOS hanno wirebonds da parti opposte!

#### Stato attuale

- 2 versioni AMS in 180 nm (irraggiate e misurate su test/beam), versione GLOBALFOUNDRIES

150 nm (Irraggiata), altre sottomesse o in programma.

- Capito: indicazioni che regge 1 Grad e danno NIEL. Segnale con sorgenti e fascio visti, S/N buono

- Non capito: efficienza 90÷95%, risoluzione temporale non sufficiente (50% degli hits in-time)

### HV-CMOS & CCPD (\*)

Combine 3 pixels together to fit one FE-I4 pixel (50×250µm²), with HVCMOS pixels encoded by pulse height.

Pixel readout chip (FE-chip) Pixel electronics based on CSA Coupling Bump-bond pad capacitance Glue Summing line **Transmitting** 33x 125 µm Pixel CMOS sensor

Capacitive coupling OK: gluing! (perspective to avoid bump-bonding?)

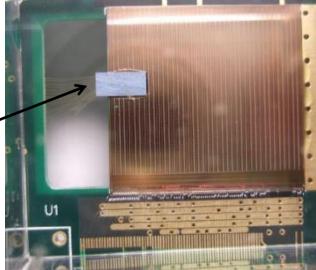

> The tiny HV2FEI4p1 prototype glued on the large FE-I4

Aix\*Marseille

Marlon Barbero, Genova visit to CPPM, Dec. 16th 2013

(\*) CCPD - Capacitive Coupled Pixel Detector

### **HV-CMOS**

- Crescente interesse in ATLAS per la tecnologia HV-CMOS

- Accoppiamento capacitivo di un sensore "attivo" utilizzante una HV di drift con il FE-I4.

- Primi sviluppi fatti in tecnologia AMS (180µm) da Ivan Peric (Heidelberg) dal 2007.

- In mialparazione un documento per un R&D ATLAS, meeting tutti i Martedì (>25 partecipanti questa settimana)

- https://indico.cern.ch/conferenceDisplay.py?confld=260703

- Proposal di R&D in preparazione, 15 d'istituti hanno espresso interesse in qualche forma (in crescita) – Vedi link sopra.

- Bonn, CERN, CPPM, DESY, Geneva, Genova, Glasgow, Göttingen, Heidelberg, LBNL, Liverpool, LPNHE, Lubiana, Santa Cruz.

- Possibili contributi italiani:

- Genova: accoppiamento HV-CMOS/FE-I4, integrazione moduli, test in lab e test-beam, R/O Visita di Genovesi a Marsiglia (Lunedì) Pianificati test a Genova su HV-CMOS con stimolazione laser insieme a colleghi di Marsiglia a Gennaio

- Milano, Bologna: valutando possibile contributo al disegno del HV-CMOS

#### *♀ Costi*

Qualche riduzione del programma ACTIVE nel 2014 e la possibile disponibilità dei fondi accantonati per CHIPIX65 (finanziato nella call di Gr.V) permettono di espandere l'R&D verso HV-CMOS (strategico per ATLAS e quindi INFN)

G. Darbo – INFN / Genova 20 December 2013 4

### Conclusioni

#### HV-CMOS

- Nuova tecnologia dalle molte promesse

- Largo interesse della collaborazione ATLAS Interesse di Genova consolidato

- Si sta valutando il possibile interesse di Milano e Bologna

#### Finanziamenti

Non saturando con ACTIVE i fondi "messi da parte" dalla CSN1 si apre la possibilità di richiedere finanziamenti per HV-CMOS