# IAPP SCHOOL - VHDL DESIGN: CHIPSCOPE AND DEBUGGING

DANIEL MAGALOTTI

#### **SUMMARY**

- Introduction of debugging problem

- Testing and debugging

- Why debugging is important?

- Description of ChipScope™ Pro software

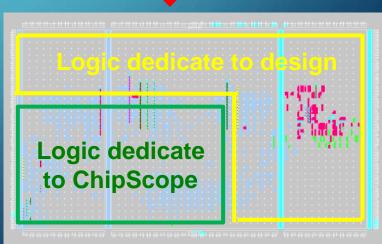

- Minimal impact to FPGA design

- Optimized cores consume minimal FPGA resources

- How to add ChipScope Pro software into design

- Describe the ChipScope Pro cores and how to allow you to focus on solving problems

- Integrated Logic Analyzer (ILA) for viewing results

- IBERT for high speed serial link

#### **TEST & DEBUG**

Do you know the difference between testing and debugging problems?

#### **TEST & DEBUG**

Do you know the difference between testing and debugging problems?

➤ In testing, the goal is to determine as quickly as possible whether the chip is working correctly, with high, but not absolute, certainty.

#### **TEST & DEBUG**

- Do you know the difference between testing and debugging problems?

- In testing, the goal is to determine as quickly as possible whether the chip is working correctly, with high, but not absolute, certainty.

- In debugging, the goal is not simply to determine that the chip is not working, but to find out why it is not working. It is not automatic, but requires the participation of the chip-design team. And it occurs at place discrete points in the design cycle.

#### WHY DEBUGGING IS IMPORTANT?

- FPGA designs are becoming more complex

- Designs are becoming faster

- Design times are becoming shorter

- Debugging and verification are more challenging

- Debugging and verification consume a significant portion of FPGA design time

- An FPGA design survey conducted by Xilinx indicates that FPGA debugging and verification accounts for nearly 40% of the FPGA design time

- Debugging and verification need to be easier and integrated into the FPGA design flow

#### **DEBUG AND VERIFICATION IS CRITICAL**

- Debug and verification can account for over40% of an FPGA design time

- Serial nature of debug and verification can make it difficult to optimize

- Inefficient strategy may result in product launch delay

- Loss in market share

- Loss of first-to-market advantages

#### **LOGIC OF DEBUGGING**

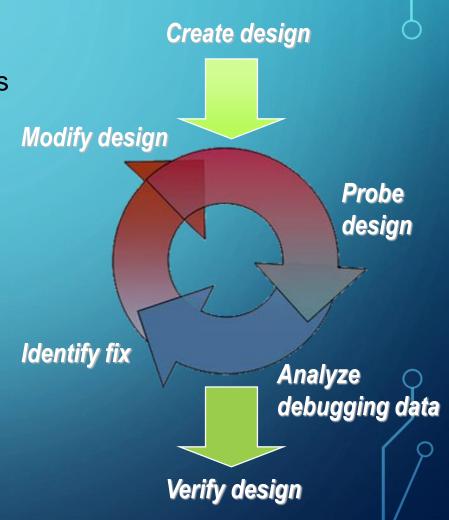

- Debugging is problem solving

- Break a problem into basic parts

- Remove or reduce variables and variation

- Predict and verify

- Debugging is an iterative process

- Verification is a component of debugging

- Confirming no problems remain

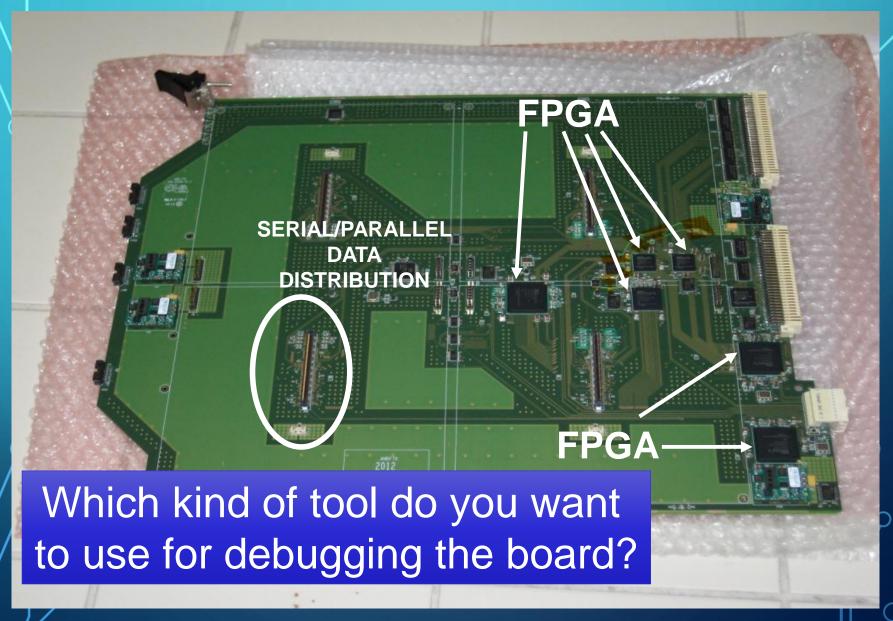

- In order to understand typical debugging problem I show you a "RANDOM" board

- > Who guess? I give you three options

**LAMB**

**AMB**

AM

- In order to understand typical debugging problem I show you a "RANDOM" board

- > Who guess? I give you three options

LAMB

AMB

AM

Page 11

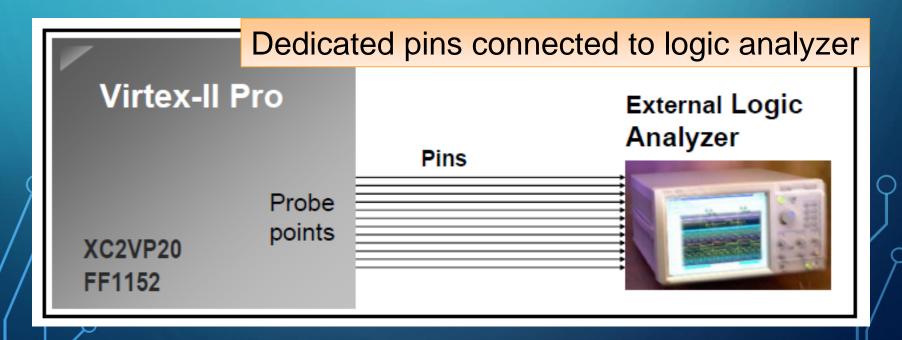

## LOGIC ANALYZER

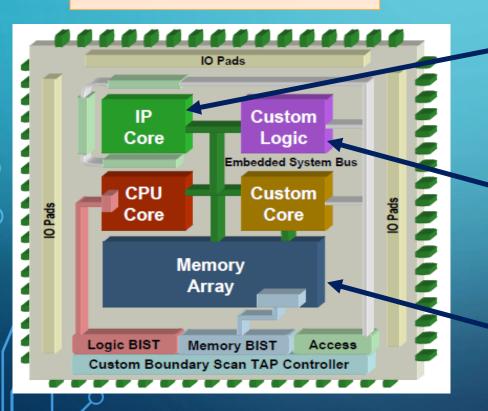

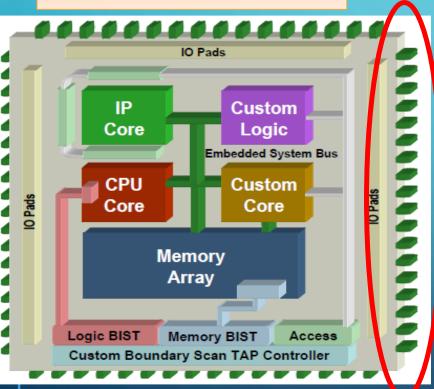

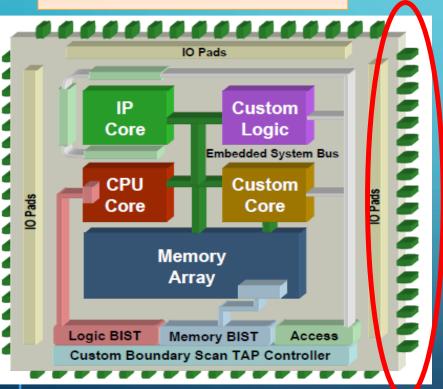

**FPGA**

>We focalize to debug a single FPGA

Internal Block of FPGA

**FIFO**

COUNTER or MULTIPLEXER or FLIP FLOP D

**RAM**

> We focalize to debug a single FPGA

**Internal Block of FPGA**

The point that you can use to access to you FPGA is the lopin

> We focalize to debug a single FPGA

**Internal Block of FPGA**

The point that you can use to access to you FPGA is the lopin

A typical package for the FPGA is a BGA

- Which the step in which we can divide the design of the FPGA

- ▶ 1° STEP: definition of the specification and architecture design by VHDL code

```

--library UNISIM:

--use UNISIM.VComponents.all;

entity babyFTK_TOP_v2 is

Port ( HIT_A_IN : in STD_LOGIC_VECTOR (15 downto 0);

DataValid_A : in STD_LOGIC;

HIT_B_IN : in STD_LOGIC_VECTOR (15 downto 0);

DataValid B : in STD LOGIC:

RESET : in STD_LOGIC:

CLK : in STD LOGIC;

MUXSEL: in STD LOGIC;

ERROR_n : out STD_LOGIC;

HOLD_A : out STD_LOGIC;

HOLD_B : out STD_LOGIC;

DATA_TO_LAMBO : out STD_LOGIC_VECTOR (15 downto 0);

DATA_TO_LAMB1 : out STD_LOGIC_VECTOR (15 downto 0);

DATA TO LAMB2 : out STD LOGIC VECTOR (15 downto 0);

DATA TO LAMB3 : out STD LOGIC VECTOR (15 downto 0)

end babyFTK_TOP_v2;

architecture Behavioral of babyFTK_TOP_v2 is

----- components declaration -----

component COMP_EQUAL is

Port ( INPUT1 : in STD_LOGIC_VECTOR (7 downto 0);

INPUT2 : in STD LOGIC VECTOR (7 downto 0);

72

EQUAL : out STD LOGIC

72

×

Design Summary

```

- Which the step in which we can divide the design of the FPGA

- 2° STEP: synthetize the code and perform a behavioral simulation of your code

- Which the step in which we can divide the design of the FPGA

- 3° STEP: implementation of your code and timing simulation of your code

- Which the step in which we can divide the design of the FPGA

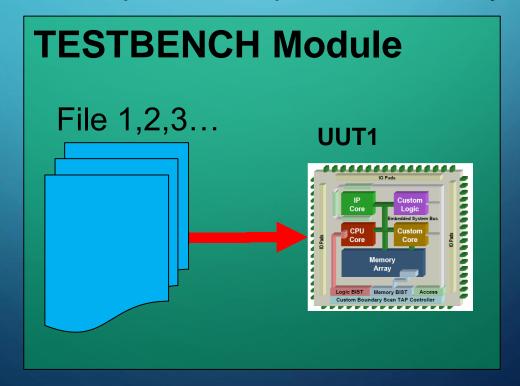

- ▶ 4° STEP: modify you testbench file in order to consider all the possible input stimulus to your design

Page 21

- Which the step in which we can divide the design of the FPGA

- ▶5° STEP: insert more than a FPGA into testbench to simulate the protocol between them

- >Which the step in which we can divide the design of the FPGA

- To STEP: definition of the specification and architecture design by VHDL code

- >2° STEP: synthetize the code and perform a behavioral simulation of your code

- 3° STEP: implementation of your code and timing simulation of your code

- 34° STEP: modify you testbench file in order to consider all the possible input stimulus to your design

- >5° STEP: insert more than a FPGA into testbench to simulate the protocol between them

- > Which the step in which we can divide the design of the **FPGA**

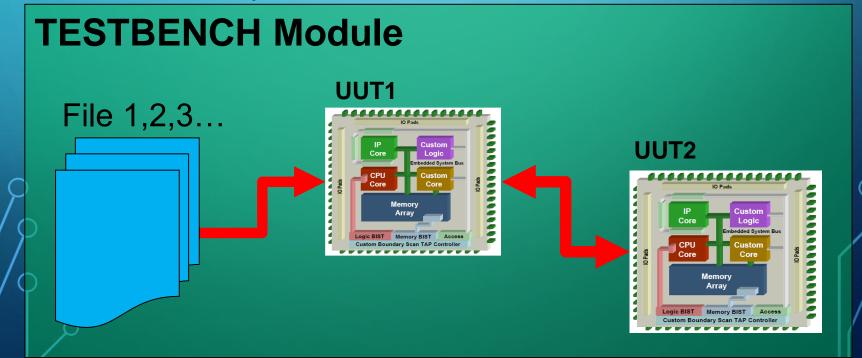

- ▶6° STEP: Programming the FPGA

```

--library UNISIM:

--use UNISIM.VComponents.all;

entity babyFTK_TOP_v2 is

Port ( HIT_A_IN : in STD_LOGIC_VECTOR (15 downto 0);

DataValid_A : in STD_LOGIC;

HIT_B_IN : in STD_LOGIC_VECTOR (15 downto 0);

DataValid_B : in STD_LOGIC;

CLK : in STD_LOGIC;

MUXSEL: in STD_LOGIC;

ERROR_n : out STD_LOGIC;

HOLD_A : out STD_LOGIC;

HOLD B : out STD LOGIC;

DATA_TO_LAMB0 : out STD_LOGIC_VECTOR (15 downto 0);

DATA_TO_LAMB1 : out STD_LOGIC_VECTOR (15 downto 0);

DATA_TO_LAMB2 : out STD_LOGIC_VECTOR (15 downto 0);

DATA_TO_LAMBS : out STD_LOGIC_VECTOR (15 downto 0)

end babyFTK_TOP_v2;

architecture Behavioral of babyFTK TOP v2 is

component COMP_EQUAL is

Port ( INPUT1 : in STD_LOGIC_VECTOR (7 downto 0);

INPUT2 : in STD_LOGIC_VECTOR (7 downto 0);

EQUAL : out STD LOGIC

Design Summary

```

- >Which the step in which we can divide the design of the FPGA

- ▶6° STEP: Programming the FPGA

```

--library UNISIM;

--use UNISIM.VComponents.all;

entity babyFTK_TOP_v2 is

Port ( HIT_A_IN : in STD_LOGIC_VECTOR (15 downto 0);

DataValid_A : in STD_LOGIC;

HIT B IN : in STD LOGIC VECTOR (15 downto 0);

DataValid_B : in STD_LOGIC;

CLK : in STD_LOGIC;

MUXSEL: in STD_LOGIC;

ERROR_n : out STD_LOGIC:

HOLD_A : out STD_LOGIC;

DATA_TO_LAMB0 : out STD_LOGIC_VECTOR (15 downto 0);

DATA_TO_LAMB1 : out STD_LOGIC_VECTOR (15 downto 0);

DATA_TO_LAMB2 : out STD_LOGIC_VECTOR (15 downto 0);

end babyFTK_TOP_v2:

architecture Behavioral of babyFTK TOP v2 is

component COMP_EQUAL is

Port ( INPUT1 : in STD_LOGIC_VECTOR (7 downto 0);

INPUT2 : in STD_LOGIC_VECTOR (7 downto 0);

EQUAL : out STD LOGIC

Design Summary

```

New parameter into the real design that you cannot considering into simulation

- Error in the board design

- Temperature variation

•

.bit file

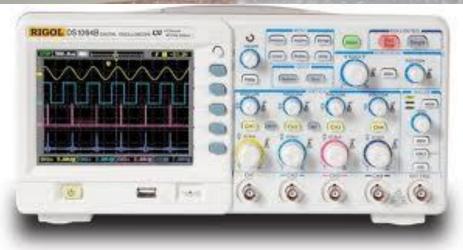

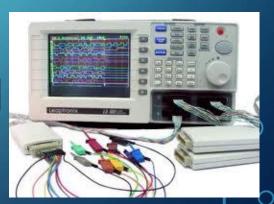

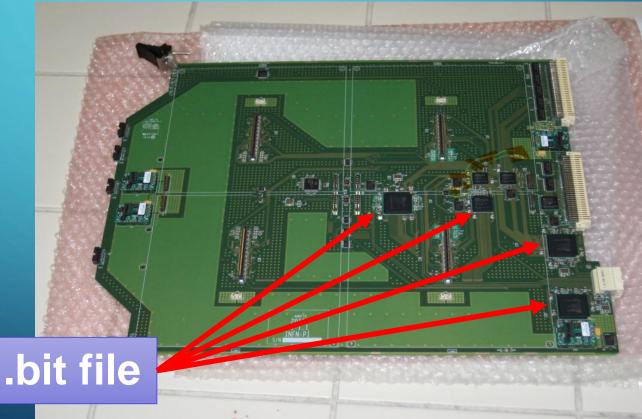

#### TRADITIONAL LOGIC ANALYSIS METHOD

- Requires Extensive Dedicated I/O for Debug

- Driving signals to external I/O introduces additional problems

- Inflexible solution

- Difficult or impossible to add additional debug pins if needed

- Limited visibility to on-chip activity

#### WHAT DO WE WANT

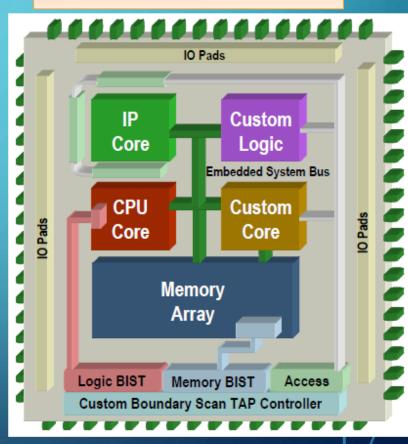

- ➤ FPGA Enables Full Internal Visibility

- Complete on-chip access

- Access Processor System Busses

- Integrated Bus Analyzer

- > Flexible On-Chip Debug

- Small, efficient cores access any node or signal and can be removed at any time

- > Enable Complete System Verification

- Debug systems in real-time

#### **Internal Block of FPGA**

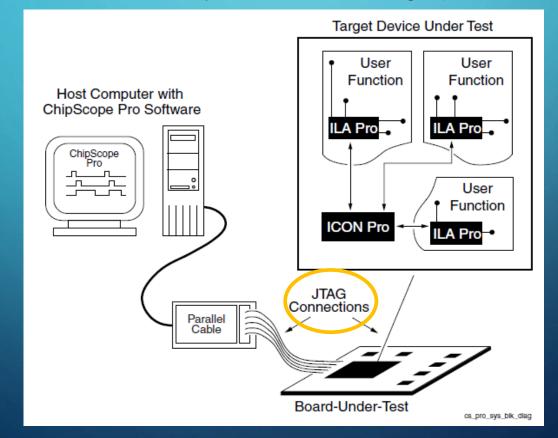

#### CHIPSCOPE PRO ON-CHIP DEBUG

- No I/O pins required for debug

- Access via the JTAG Port

- On-Chip access to every signal and node in the FPGA design

- >Add and remove cores at any time in the design process

#### CHIPSCOPE PRO ON-CHIP DEBUG

- Use the ChipScope Pro software for

- Verification and debug

- Injecting short signal sequences

- Capturing data for post-bench analysis

- Do not use the ChipScope Pro software for

- A replacement for a simulation tool

- Accessing the System Monitor

- Testing high-speed I/O

- Remote diagnostics/monitoring

#### **OPTIMIZED DEBUGGING CORES**

There are 5 CORE integrated into ChipScope

#### Virtual Input Output Core (VIO)

- · Virtual Inputs and Outputs

- Stimulate logic with pulse trains

#### Integrated Bus Analysis Core (IBA)

- PLB and OPB specific Bus analysis cores

- Protocol detection

- Debug and verify control, address, and data buses

### Integrated Bit Error Ratio (IBERT)

monitor the functionality of transceivers (GTP, GTH, GTX)

# Integrated Logic Analysis Core (ILA)

- Access internal nodes and signals

- Debug and verify signal behavior

- Define detailed trigger conditions

#### Agilent Trace Core 2 (ATC2)

Agilent created core enabling

On-chip debug of Xilinx FPGAs using

Agilent FPGA Dynamic Probing

#### **CORE RESOURCES**

- ChipScope™ Pro software cores utilize FPGA resources

- For what?

- Block RAM: trigger and data storage

- Slice logic: trigger comparisons

- > You must leave room for the ChipScope Pro software cores in the FPGA

- This may require using a larger part in the same package as you will use in production

- The CORE Generator and Core Inserter tools can estimate block RAM usage, but the design may still end up with too many block RAMs

- If MAP issues an error, reduce the number of observed signals or the sample data depth to reduce block RAM usage

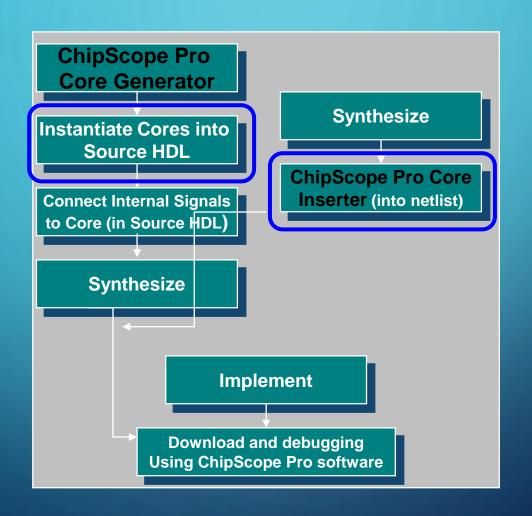

# ADD CHIPSCOPE IN THE DESIGN

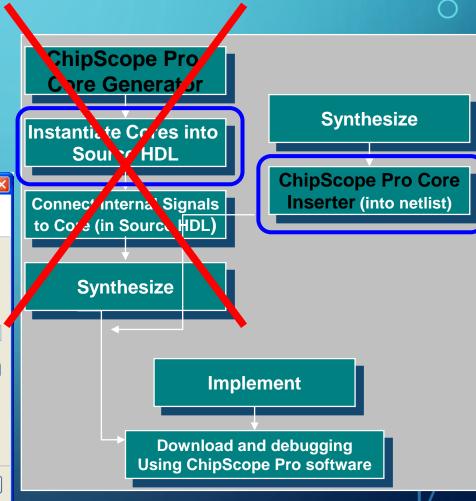

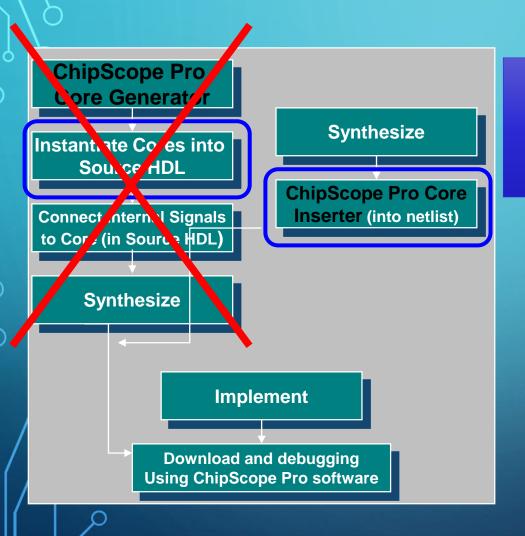

> Two way to insert the ChipScope: into HDL source or with Core Insert

> Two way to insert the ChipScope: into HDL source or with Core Insert

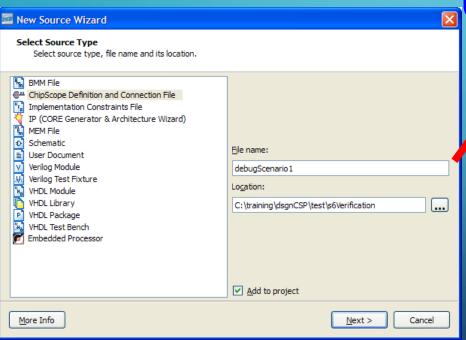

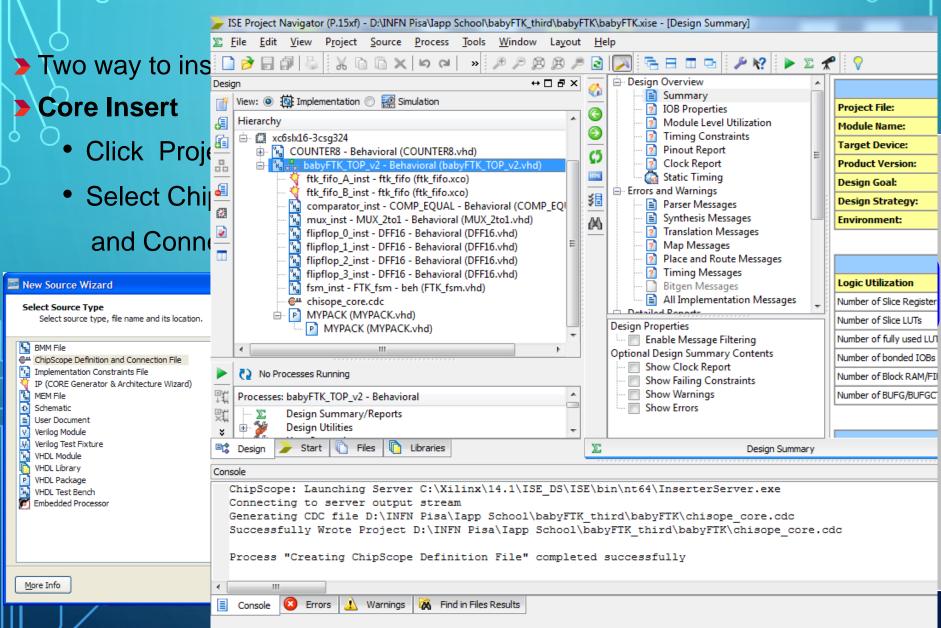

Core Insert

Click Project -> New Source

Select ChipScope Definition and Connection File (CDC)

Two way to insert the ChipScope: into HDL source or with Core Insert

A source VHDL for the design

A different source for the ChipScope

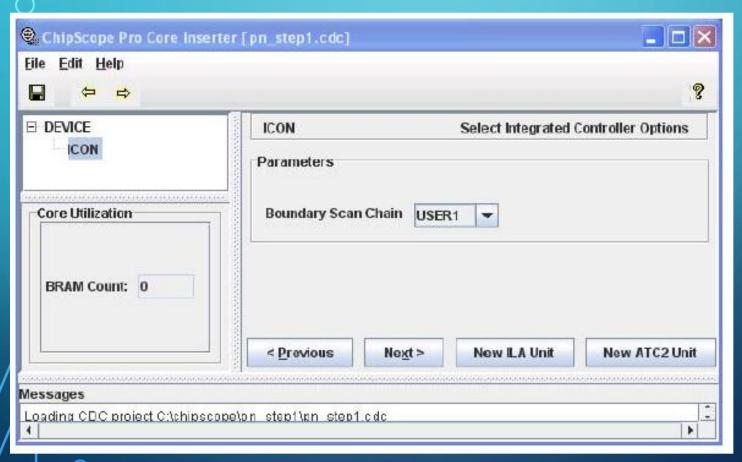

#### THE ICON CORE

- ICON (Integrated Control) core: This core controls up to 15 capture cores

- The ICON core interfaces between the JTAG interface and the capture cores

- Capture cores: Customizable cores for creating triggers and data storage

- Customizable number, width, and storage of trigger ports

- ILA (Integrated Logic Analyzer) core: Capture core for HDL designs

- IBERT core: High speed monitoring

- ATC2 (Integrated Logic Analyzer with Agilent Trace) core: similar to the ILA core, except data is captured off-chip by the Agilent Trace Port Analyzer

- IBA/OPB (Integrated Bus Analyzer for CoreConnect On-Chip Peripheral Bus) core:

Capture core for debugging CoreConnect OPB

- IBA/PLB (Integrated Bus Analyzer for CoreConnect Processor Local Bus) core:

Similar to the IBA/OPB core, except for the PLB bus

- VIO (Virtual Input/Output core): Define and generate virtual I/O ports

## THE ILA CORE

- Integrated Logic Analyzer (ILA) cores can be added with either the CORE Generator or Core Inserter tools or PlanAhead tool

- ➤ A design can contain up to 15 ILA cores

- Maximum speed of the ILA core varies according to device family and selected features

- Turning on more "features" generally slows down the performance of the core and causes it to consume additional fabric resources

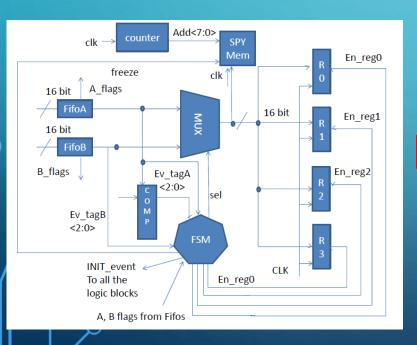

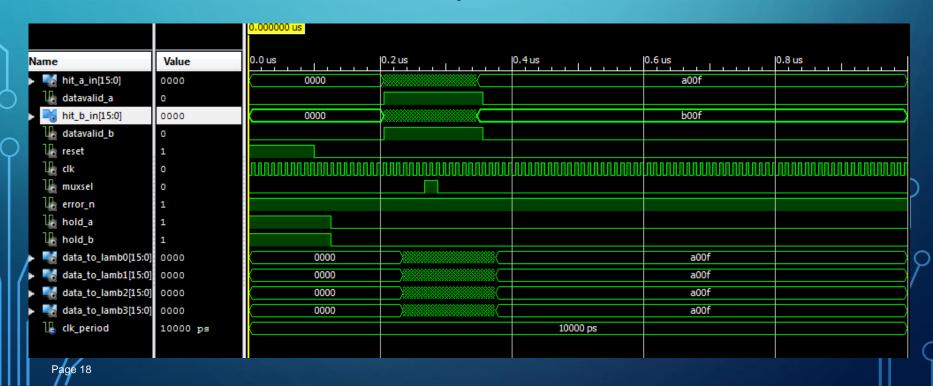

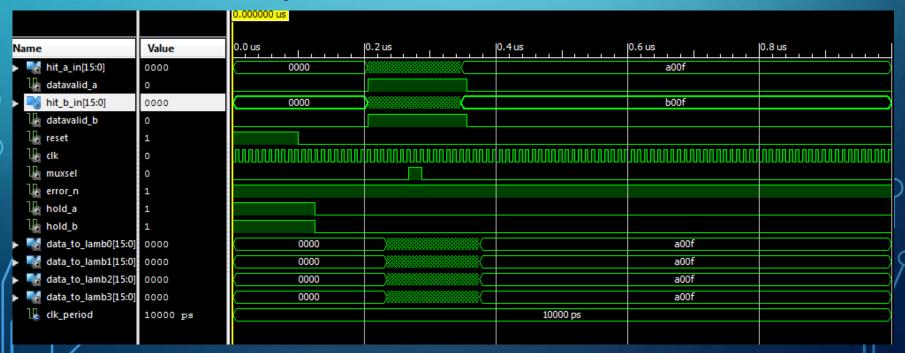

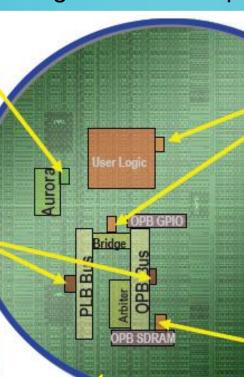

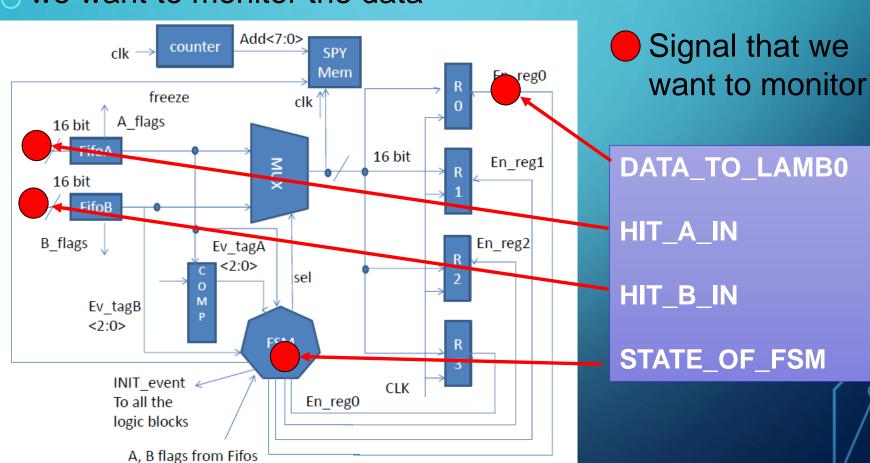

### THE BABY FTK PROJECT

Considering the baby FTK project we select the point that we want to monitor the data

## **ILA CORE**

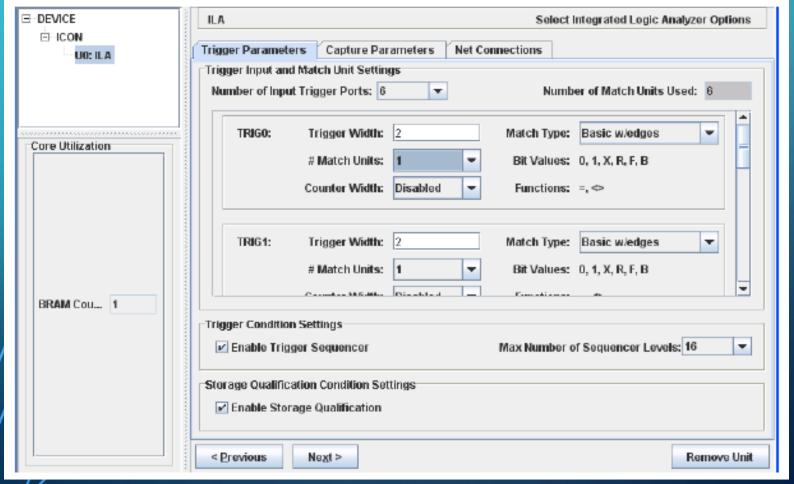

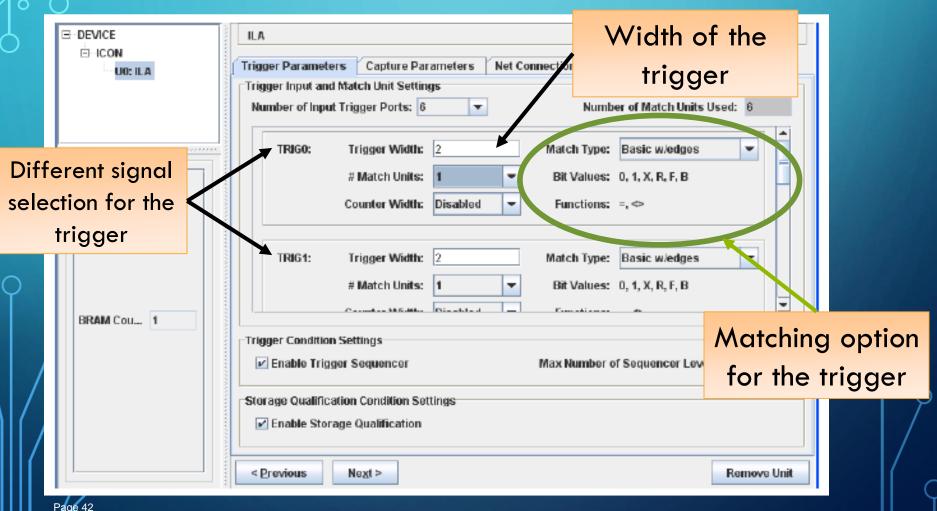

> The wizard after the inserting chipscope core

The wizard to define the option of the ILA core

The trigger parameters and capture parameters

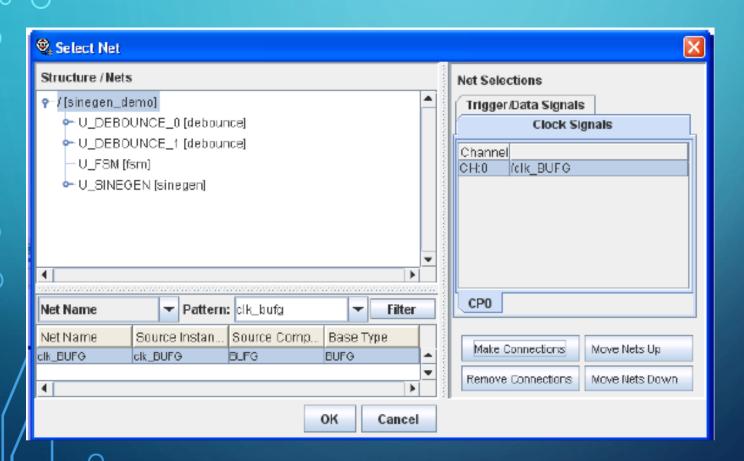

> The net selection wizard: the clock selection to sample the data

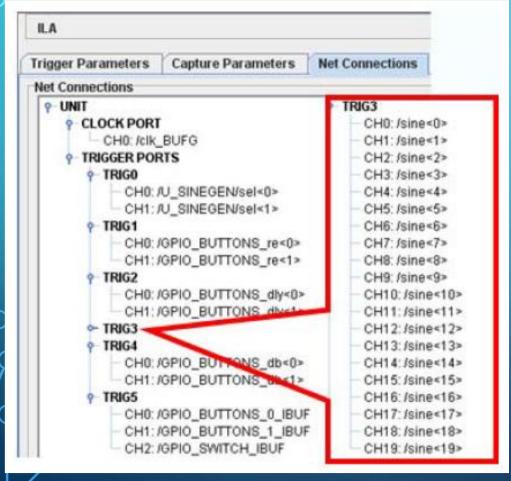

The net selection wizard: the data signals selection

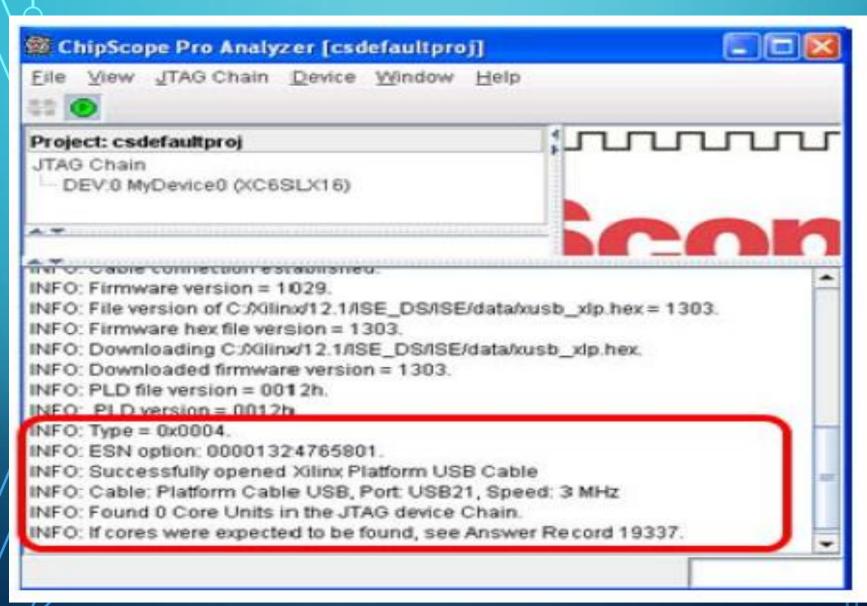

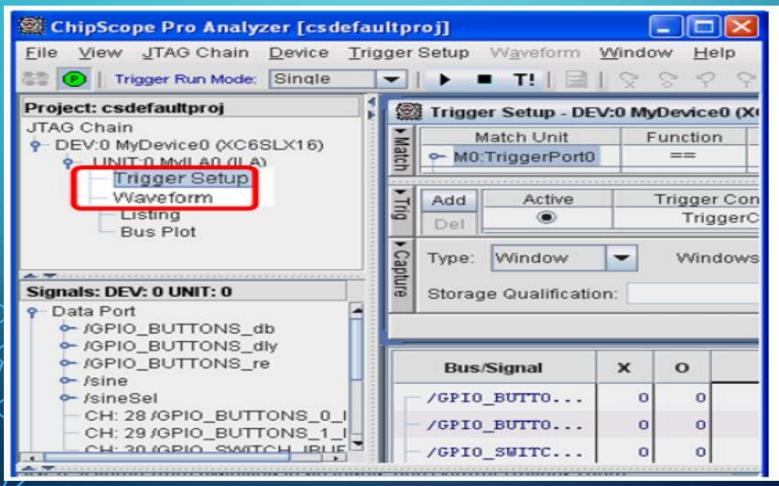

The Chipscope software: selection of the ILA unit: trigger and waveform

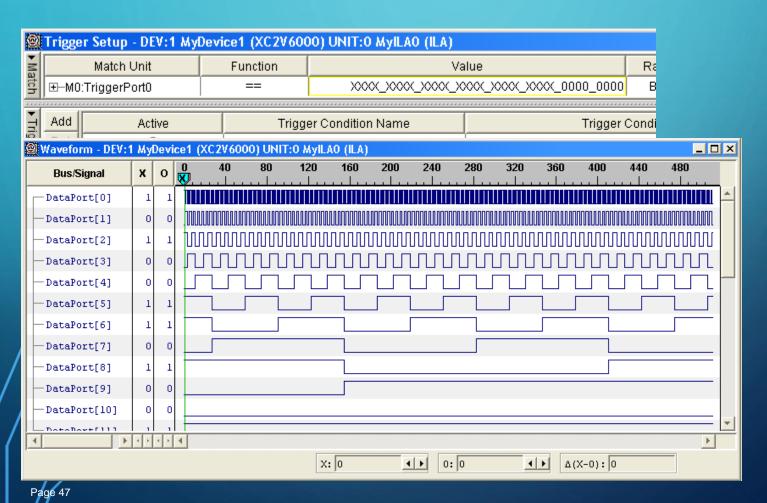

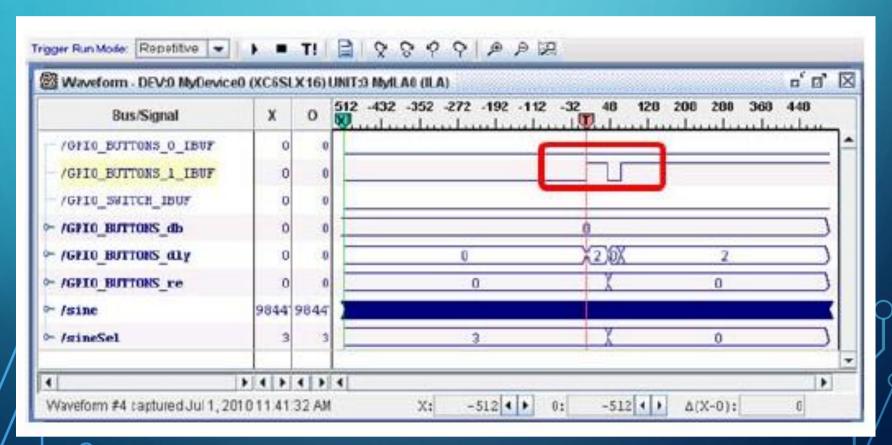

The Chipscope software: selection of the trigger sequence and monitor of the data selected

The Chipscope software: selection of the trigger sequence and monitor of the data selected

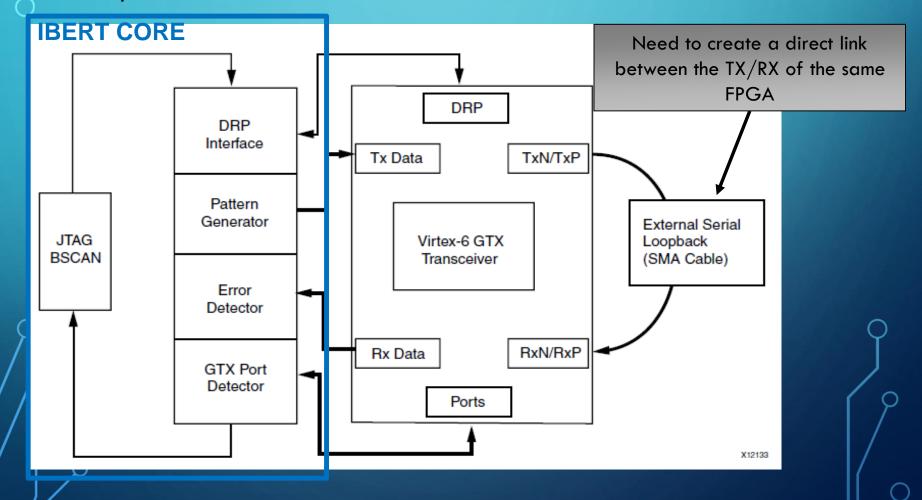

### THE IBERT CORE

- The IBERT core is used to evaluate and monitor the functionality of transceivers for a variety of Xilinx devices, (for example the Spartan®-6 GTP transceiver, Virtex®-6 GTX transceivers).

- ➤ The design includes pattern generators and checkers implemented in FPGA logic, as well as access to the ports and dynamic reconfiguration port (DRP) attributes of the GTX transceivers.

- ➤ The IBERT core is a self-contained design. When generated, it runs through the entire implementation flow, including bitstream generation.

# **IBERT DESIGN FLOW (2/1)**

Description of interface between the IBERT core and the transceiver

# **IBERT DESIGN FLOW (2/2)**

- DRP Interface and GTX Port Registers: IBERT provides you with the flexibility to change GTX transceiver ports and attributes. Dynamic reconfiguration port (DRP) logic is included, which allows the runtime software to monitor and change any attribute in any of the GTX transceivers included in the IBERT core.

- ▶ Pattern Generator: Each GTX transceiver enabled in the IBERT design has both a pattern generator and a pattern checker. The pattern generator sends data out through the transmitter.

- Error Detector: Each GTX transceiver enabled in the IBERT design has both a pattern generator and a pattern checker. The pattern checker takes the data coming in through the receiver and checks it against an internally generated pattern.

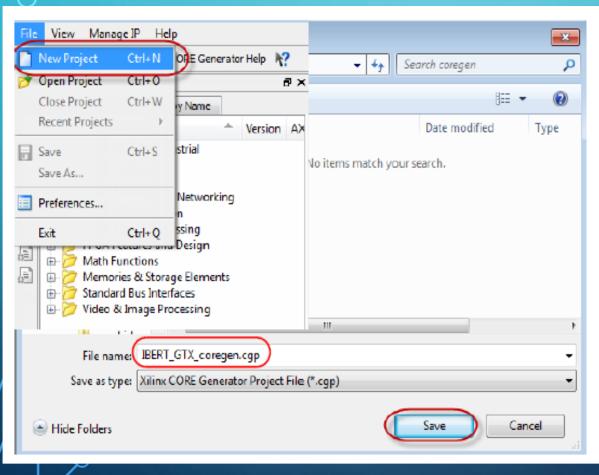

Create a new project with only the IBERT core

The core create a standalone project.

A bit programming file is generated with the purpose to test only the quality of link

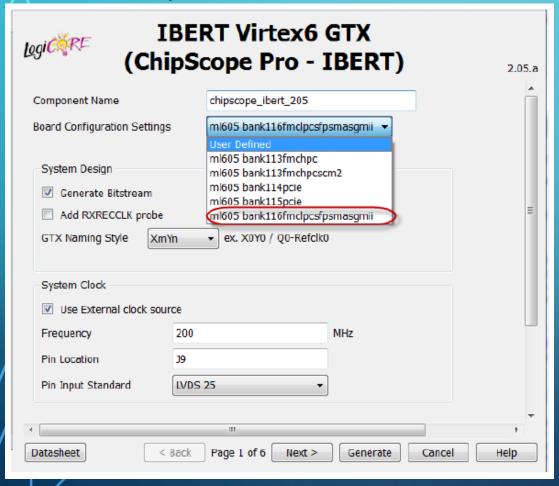

Define the parameter of the IBERT core

With the core generator interface we can select a series of parameter of the link, for example the speed of the link and the clock reference.

The graphic interface of the IBERT

| MGT/BERT Settings DRP 9                | Settings Port Settings Swe | ep Test Settings |                              |                  |

|----------------------------------------|----------------------------|------------------|------------------------------|------------------|

|                                        | GTX_X0Y16                  | GTX_X0Y17        | GTX_X0Y18                    | GTX_X0Y19        |

| MGT Settings                           |                            |                  |                              |                  |

| - MGT Alias                            | GTX0_116                   | GTX1_118         | GTX2_116                     | GTX3_116         |

| - Tile Location                        | GTX_X0Y16                  | GTX_X0Y17        | GTX_X0Y18                    | GTX_X0Y19        |

| - MGT Link Status                      | No Link                    | No Link          | 5.0 Gbps                     | No Link          |

| <ul> <li>MGT Edit Line Rate</li> </ul> | 5.0 Gbps                   | 5.0 Gbps         | 5.0 Gbps                     | 1.25 Gbps        |

| - TX PLL Status                        | LOCKED                     | LOCKED           | LOCKED                       | LOCKED           |

| - RX PLL Status                        | LOCKED                     | LOCKED           | LOCKED                       | LOCKED           |

| Loopback Mode                          | None -                     | None             | None                         | None             |

| - Channel Reset                        | Reset                      | Reset            | None                         | Reset            |

| - TX Polarity Invert                   |                            |                  | Near-End PCS<br>Near-End PMA |                  |

| - TX Error Inject                      | Inject                     | Inject           | Far-End PMA                  | Inject           |

| - TX Diff Output Swing                 | 590 mV (0110) 🔻            | 590 mV (0110)    | Far-End PCS                  | 590 mV (0110)    |

| TX Pre-Emphasis                        | 0.000 dB (0000)            | 0.000 dB (0000)  | 0.000 dB (0000)              | 0.000 dB (0000)  |

| - TX Post-Emphasis                     | 0.000 dB (00000)           | 0.000 dB (00000) | 0.000 dB (00000)             | 0.000 dB (00000) |

| - RX Polarity Invert                   |                            |                  |                              |                  |

| - RX AC Coupling Enable                | <b>V</b>                   | P                | <b>V</b>                     | <b>*</b>         |

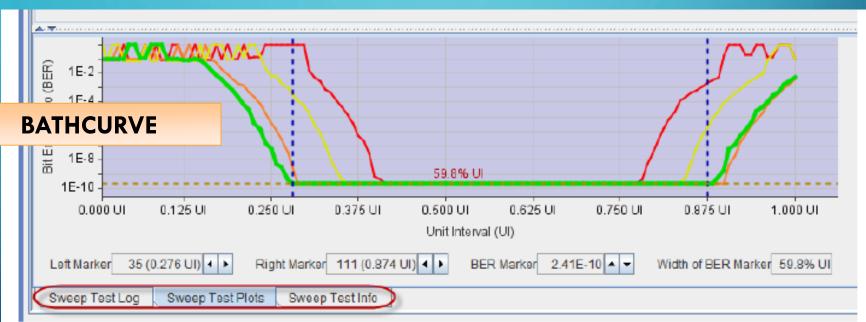

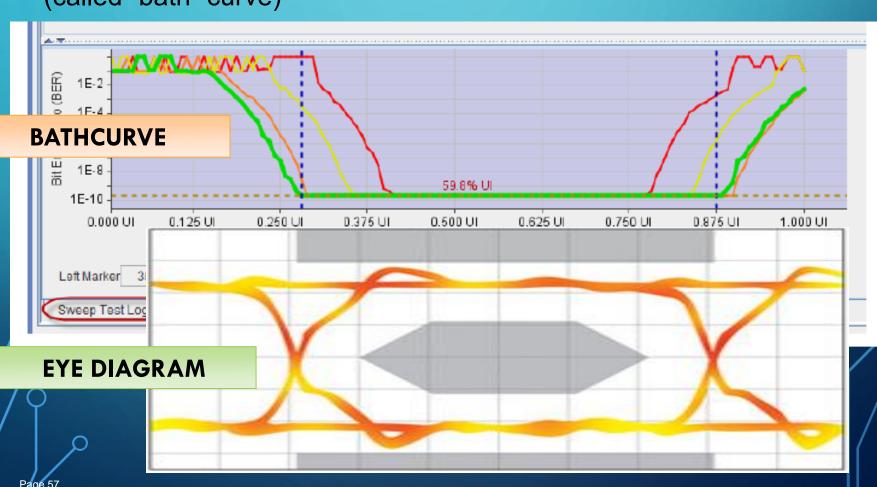

In order to characterize the link the Bit Error Rate (BER) is plotted (called "bath" curve)

In order to characterize the link the Bit Error Rate (BER) is plotted (called "bath" curve)

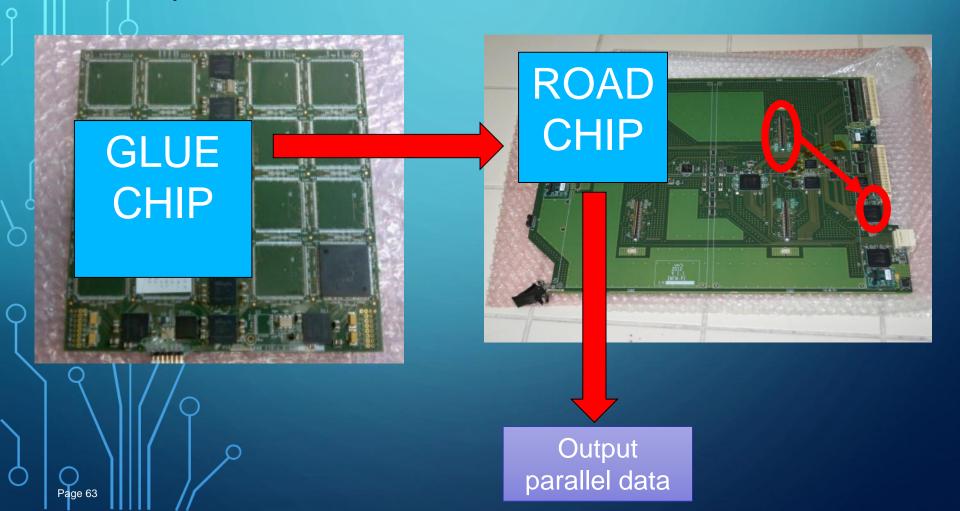

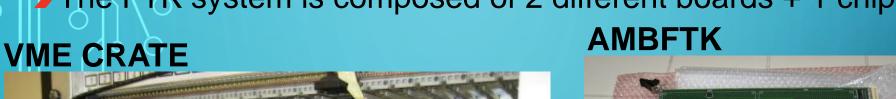

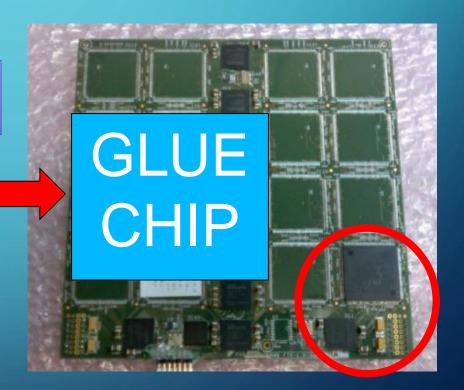

> The FTK system is composed of 2 different boards + 1 chip

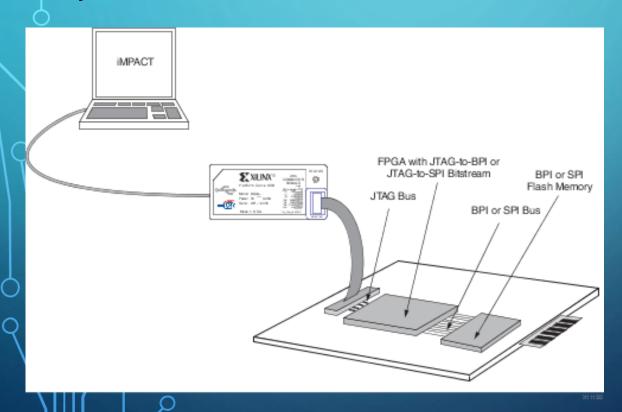

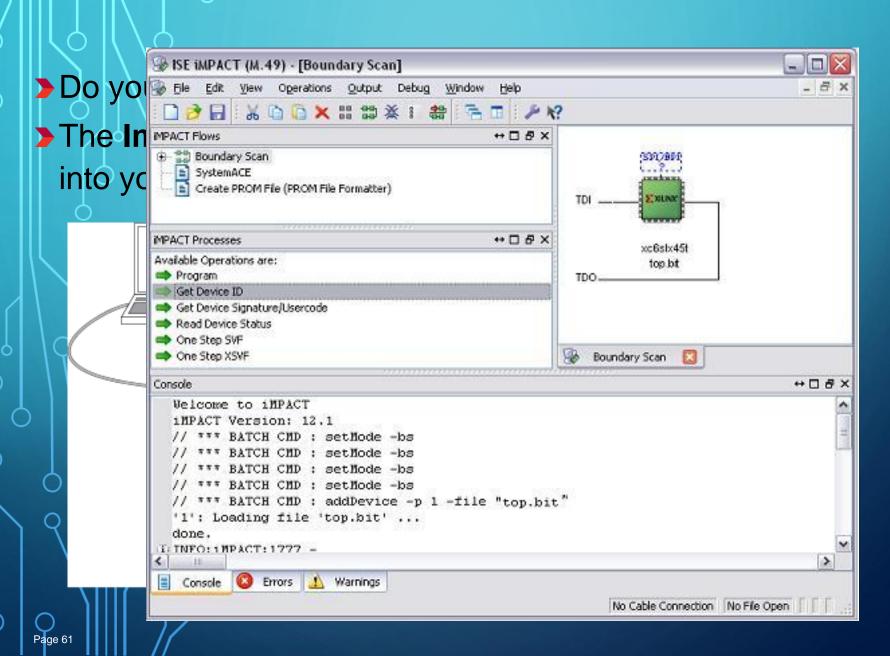

- ➤ Do you remember the 6° STEP?

- The Impact software help us to load the program bit file into your FPGA

➤ We test whit ChipScope the data chain of the output of the Amchip to LAMB and to AMB

Output parallel data

Input Stimulus

➤ We test whit ChipScope the data chain of the output of the Amchip to LAMB and to AMB