# FTK: HW status

Marco Piendibene for the FTK team

Atlas Italia – Pisa - April 12, 2013

### OUTLINE

- For each board: Status future schedule for 2015

- Summary of timescales

- Milestones & Conclusions

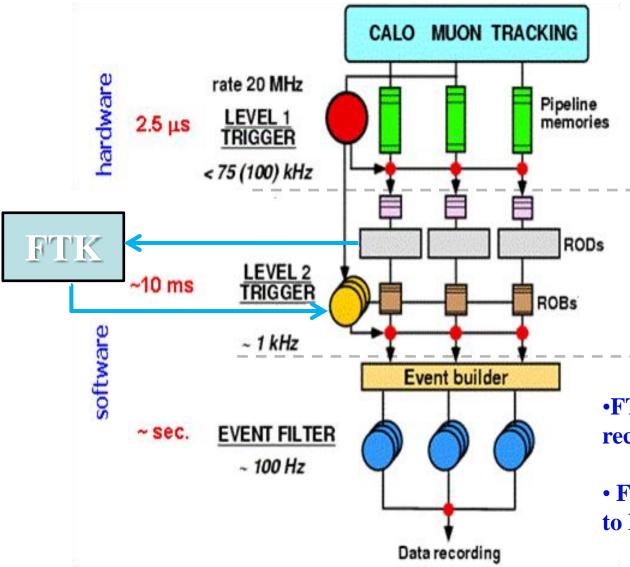

# **Atlas trigger system: where is FTK?**

•We need to reduce the amount of data

•Atlas 3 levels trigger

•FTK is an hardware system to reconstruct the particles tracks

• FTK gives tracks information to Level2 trigger.

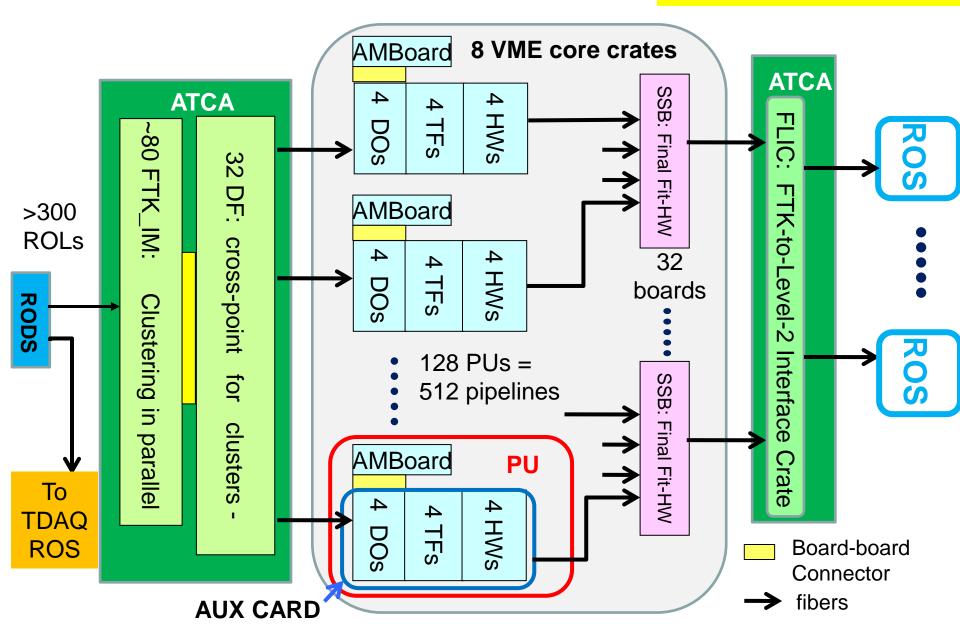

# FTK global view

16400 AMchips ~2000 FPGAs Thousands of serial links

# **Dual-output HOLA (U. of Chicago)**

- Sends SCT & pixel data to DAQ & FTK.

- All required boards produced and tested.

- 32 boards installed at P1.

- More SCT RODs  $\rightarrow$  produce 40 more HOLAs. s

- IBL RODs have it built in.

We will pay for ½ of the QSFPs.

Schedule:

**Production** of additional DO-HOLAs:

*Spring. '13* Installation of DO-HOLAs/fibers:

when fibers from all ROD-BOCs will be disconnected for new RODs installation

Test of installation

when ROS will be available

S

П

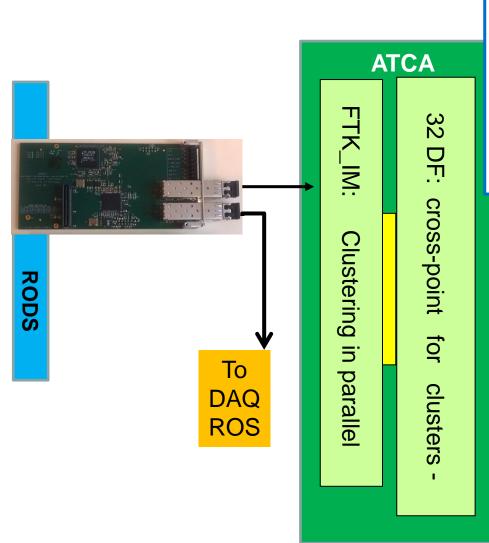

# **FTK** input mezzanine (FTK\_IM Frascati Waseda)

- Receive ROD's data and do cluster finding.

- Prototypes produced, tested, and used @P1. •

- Few changes needed for DF compatibility. •

- New prototype: now under stand-alone test

# **Data Formatter (DF, Fermilab, UofC)**

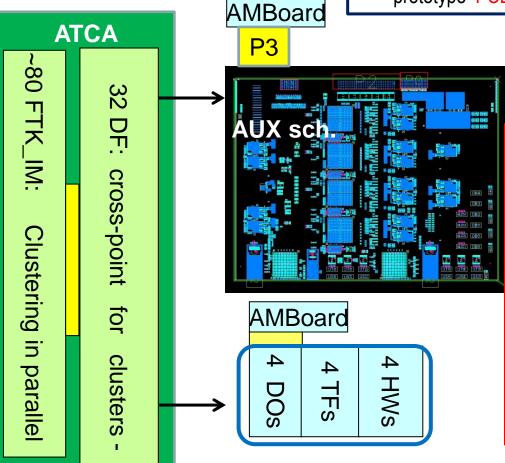

**ATCA Distributes found clusters to 64 FTK**  $\eta$ - $\phi$  towers. **ATCA** 32 for complex fiber-to-tower mapping. P PCBs delivered, parts assembly is on-going First task (summer '13): test high speed serial data FTK\_IM: Clustering in ross-point transfer & ATCA control functionality. Firmware test. RODS б clusters >300 paralle **ROLs**

#### Schedule:

Test FTK\_IM-IBL BOC: Sum. '13 Integrated tests w DF: Aut. '13 **Global Integration** Spr.-Sum. '14 Production FTK\_IM: Sum. '14 **DF Production** Sum. '14 **DF-FTK\_IM Installation** Aut, '14

S

S

U

S

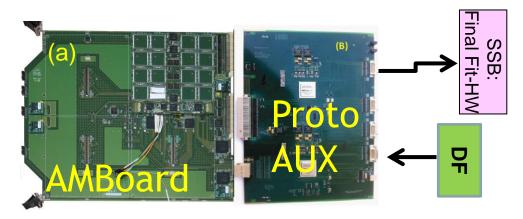

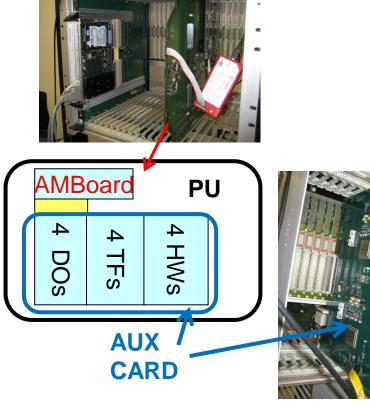

# FTK Processor Unit (PU) - Status

- 128 PUs do pattern matching and the 1<sup>st</sup> stage track fitting.

- A PU consists of an

a large *Auxiliary Card* (b) (AUX-UoChicago) behind it.

We tested them successfully together in the Pisa test stand for Data Transfer & VME functions 7

# The final AUX (U. of Chicago)

- Receives DF data, sends coarse hits to AMB, receives back roads, and does the 1<sup>st</sup>-stage fitting (8 layers).

- Final board design completed

- Firmware ready for data processing (under optimization), but error handling, monitoring tasks to be added.

- Engineering review in March successful

- prototype PCB ordered

#### Schedule:

Standalone test: *Summer '13* Integrated Test DF/AUX : *Aut. '13* Integrated Test AMB/AUX : *next Winter* Integrated 1<sup>st</sup> stage: *Spring '14* Global Integration: *Spr.-Sum '14* AUX Production *Sum-Aut. '14* AUX Installation *Aut. '14-Winter '15*

П

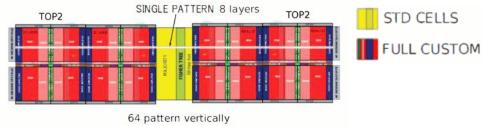

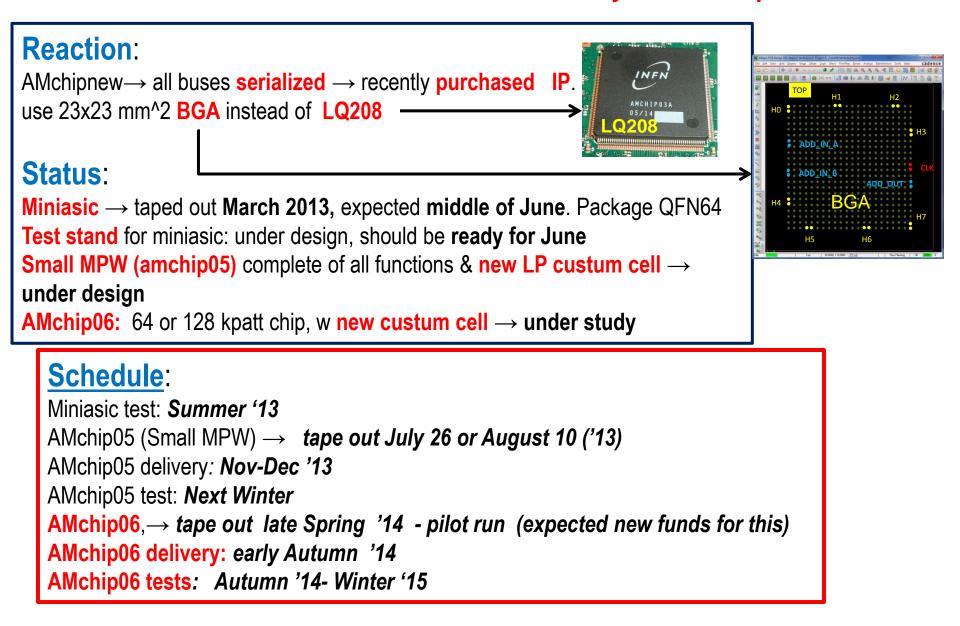

## AM System (1): - Status DOI:10.1109/ANIMMA.2011.6172856 AM chip04: TMSC 65 nm with Variable Resolution

custom cell to reduce pattern size: 8k patterns in 14 mm<sup>2</sup>.

- Yield>80% tests successful

- 64kpatt power consumption lower than AMchip03

AMchip03 (5 kpat, 180 nm):  $1 A \rightarrow 1,8 W$ AMchipnew (64 kpatt): 1,45 A  $\rightarrow 1,7 W$ p03 expected 1,6 W

**EXTREMELY GOOD RESUSLTS, BUT:** we need Serialized I/O whose consumption is high (many SL fanouts).

TWO possibilities:

(1) Dilute boards in more crates

(2) *Reduce further* AMchipnew core consumption: down from 1.2 v to Q.6 v: *new LP custom cell.*

#### AM System (2): Why Serialized I/O TSMC-65 nm: Too many GND/VCC pads needed

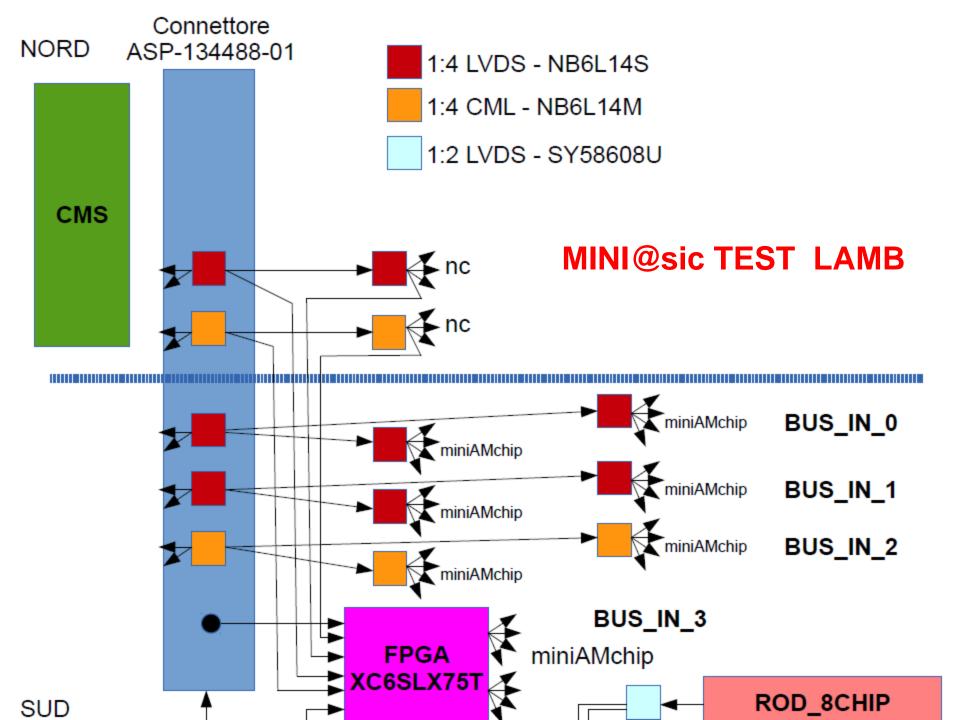

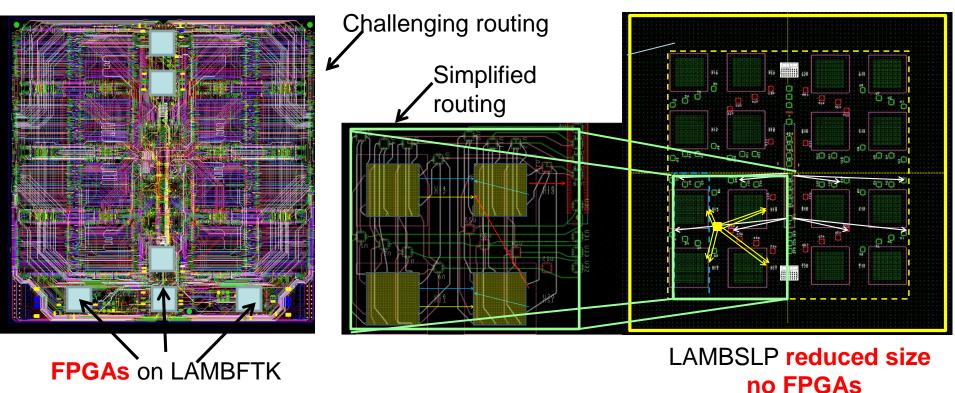

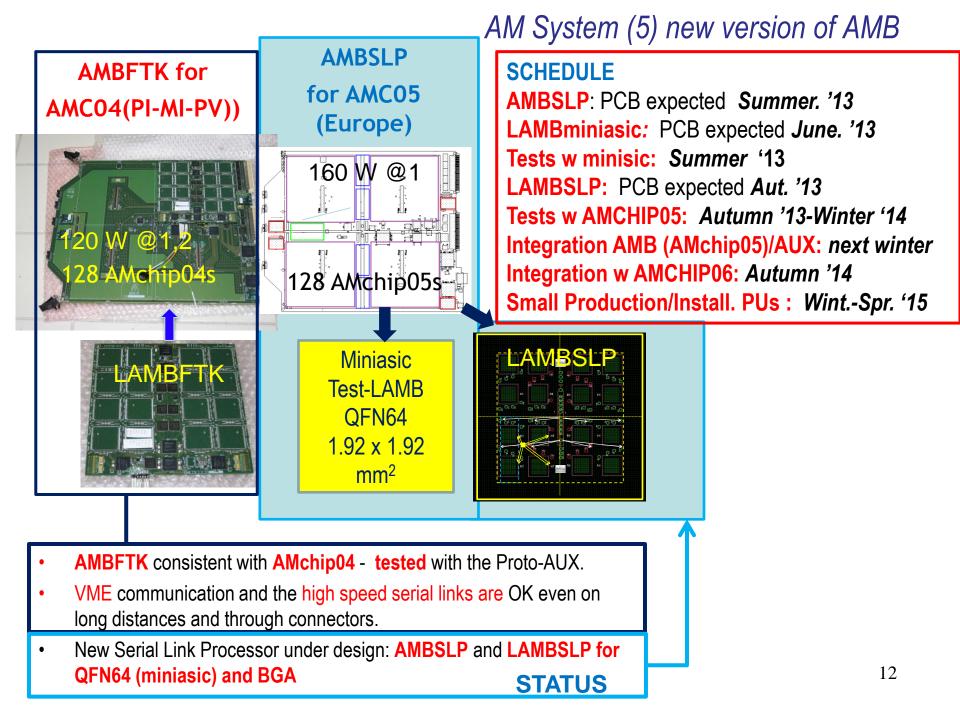

## AM System (3): A new LAMB for AM chip05: all buses on serial links

#### BGA with Flip chip technique:

- (1) high frequency solution for 2.5 Gb/s links

- (2) Caps included in the package to be able to solder BGA on both sides (32 BGA/LAMB)

- (3) Possibility of multi-packaging

- (4) **AMchip05 more expensive** than expected (IP, flip chip BGA, multipackaging) INFN budget insufficient  $\rightarrow$  the **AM system** try to become **EUROPEAN** 11

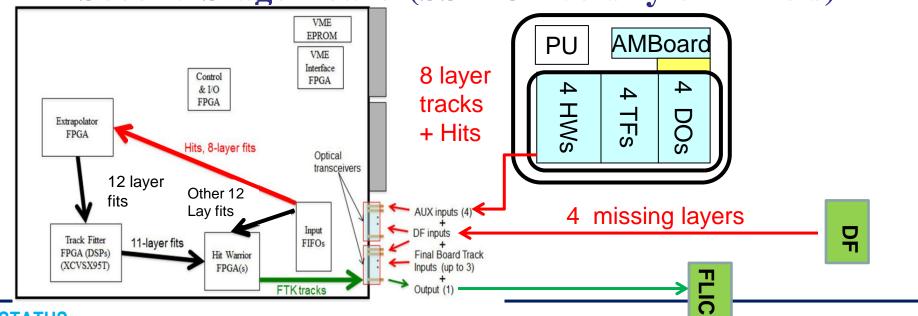

### Second Stage Board (SSB-University of Illinois)

#### **STATUS**

- SSB: full 12-layer fit: (a) receives 8-layer good tracks from the PU (b) find hits in the missing 4 silicon layers, (c) fit tracks with 12 lay, (d) removes duplicates.

- basic firmware functions written, testing in progress.

- After that, board design will be finalized.

- An engineering review is planned for April, with a prototype to be built shortly after.

#### SCHEDULE

- Stand-alone test Summer '13

- Integration with FLIC Autumn '13

- Integration with AUX Autumn '13

Global Integration: Spring –Summer '14 Small Production: Summer '14 Installation: Autumn '14 13

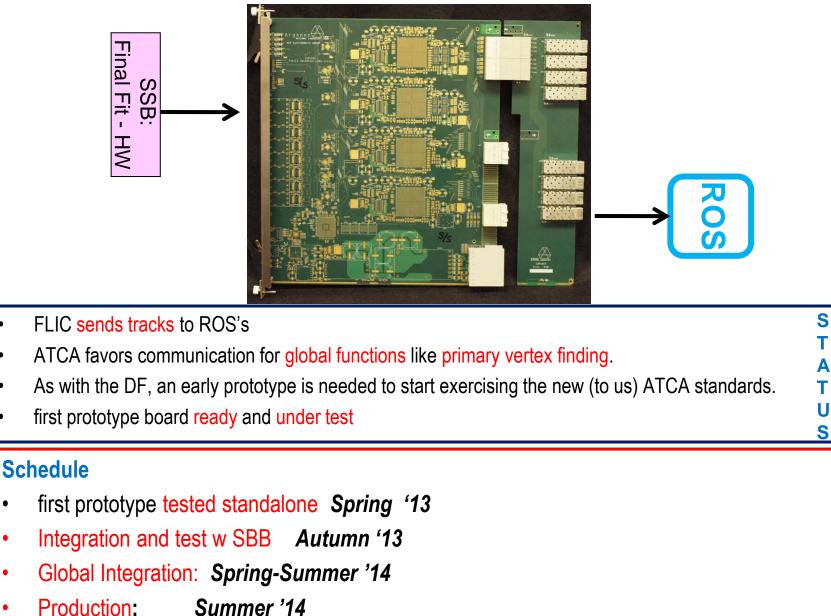

## FTK-to-Level-2 Interface Crate (FLIC-Argonne)

Installation: Autumn '14

٠

•

٠

| Schedule<br>Summary<br>for 2015<br>a-16 PUS<br>8-16 PUS |       |      |   |           | 300<br>OLs<br>To<br>DAQ<br>OS |                 | ~80 FTK_IM: Clustering in parallel |     | 32 DF: cross-point for clusters - |             |             | MBO<br>4 DOs<br>MBO<br>4 DOs<br>MBO<br>4 DOs | 4 TFs<br>ard<br>4 TFs<br>128<br>512 |   |   |      | <b>^ ^ ^</b> | tes<br>SSB: Final Fit-HW 32 a SSB: Final Fit-HW | ds   |      |     | ard-be |   |   |

|---------------------------------------------------------|-------|------|---|-----------|-------------------------------|-----------------|------------------------------------|-----|-----------------------------------|-------------|-------------|----------------------------------------------|-------------------------------------|---|---|------|--------------|-------------------------------------------------|------|------|-----|--------|---|---|

| Months                                                  | 7     | 8    | 9 | 10        | 11                            | <mark>12</mark> | 1                                  | 2   | 3                                 | 4           | 5           | 6                                            | 7                                   | 8 | 9 | 10   | 11           | 12                                              | 1    | 2    | 2 3 | 3 4    | 5 | 6 |

| Tasks                                                   | 2013  |      |   | .3        | 3                             |                 |                                    |     |                                   |             | 2014        |                                              |                                     |   |   |      |              |                                                 |      | 2015 |     |        |   |   |

| Dual Output HOLA                                        |       |      |   |           |                               |                 |                                    |     |                                   |             |             |                                              | test                                |   |   |      |              |                                                 |      |      |     |        |   |   |

| FTK Input Mezzanine                                     | w IBL |      | ١ | w DF/ROD  |                               |                 |                                    |     |                                   |             | Global Int. |                                              |                                     |   |   |      |              |                                                 |      |      |     |        |   |   |

| Data Formatter                                          | test  |      |   | w AUX     |                               | (               |                                    |     |                                   | C           | olob        | <mark>al Int</mark>                          | <b>.</b>                            |   |   |      |              |                                                 |      |      |     |        |   |   |

| Miniasic                                                | te    | st   |   |           |                               |                 |                                    |     |                                   |             |             |                                              |                                     |   |   |      |              |                                                 |      |      |     |        |   |   |

| AMchip05                                                | tape  | eout |   |           |                               | te              | st                                 | -   |                                   |             |             |                                              |                                     |   |   |      |              |                                                 |      |      |     |        |   |   |

| AMchip06                                                |       |      |   |           |                               |                 |                                    |     |                                   |             | tapeout     |                                              |                                     |   |   | test |              | est                                             |      |      |     |        |   |   |

| AMBSLP-Mini-LAMBSLP                                     |       | tes  | t |           |                               |                 |                                    |     |                                   |             |             |                                              |                                     |   |   |      |              |                                                 |      |      |     |        |   |   |

| AMBSLP-LAMBSLP                                          |       |      |   | w AMO     |                               | <i>N</i> 05     | )5 w AU                            |     | <b>UX</b>                         | Global Int. |             | <b>.</b>                                     | w AM06                              |   |   |      | 6            | 8-16 PUs                                        |      |      |     |        |   |   |

| AUX CARD                                                | test  |      |   | w DF      |                               |                 | W A                                | AMB | MBSLP                             |             | Global Int. |                                              |                                     |   |   |      |              | 8-                                              | 16 I | Us   | -   |        |   |   |

| Second Stage Board (SSB)                                | test  |      |   | w FLIC/A  |                               | /AU             | IX                                 |     |                                   |             | Global Int. |                                              |                                     |   |   |      |              |                                                 |      |      |     |        |   |   |

| FTK Level-2 Interface Crate (FLIC)                      | test  |      |   | w SSB - R |                               |                 | <mark>DS</mark>                    |     |                                   | Gl          |             | lobal Int.                                   |                                     |   |   |      |              |                                                 |      |      |     |        |   |   |

### Many activities in FTK lab – Pisa (april 2013)

Paola Giannetti (INFN) Pisa FTK Project leader

Saverio Citraro (University of Pisa & INFN) HW/FW engineer Daniel Magalotti (University of Modena and Reggio Emilia – INFN Perugia) Engineer, HW/FW expert Firmware responsible

During a meeting..

Marco Piendibene (University of Pisa & INFN) Engineer, HW/FW expert Hardware responsible

**Andreas Sakellariou** (Prisma Electronics, Greece – **IAPP collaboration**) Engineer, HW/FW expert

*Riccardo Cipriani* (University of Pisa & INFN) HW/FW engineer (student)

*Pierluigi Luciano* (University of Pisa & INFN) HW/FW engineer (student)

Calliope-Louisa Sotiropoulou (Aristotle University of Thessaloniki , Greece – IAPP collaboration) Physicist, HW/FW expert

## **Milestones & Conclusions**

### **Milestones**

- Before August '14: Global integration with AMchip05 (small AM bank)

- Autumn '14: Production and Installation of all boards except AMBSLP+ that will come later (waiting AM06)

### Conclusion

- All the prototypes are in advanced status and soon we will know test results

- The schedule is tight, especially for the AMBSLP board. No contingency

### **Crate needed Power**

LAMB power for AMchip (from AM04 measur.) $\sim 57*4=230$  W as expectedAUX power $\sim 75$  WCrate Power $\sim (75+57*4)*16 =$ 4850 W was OK

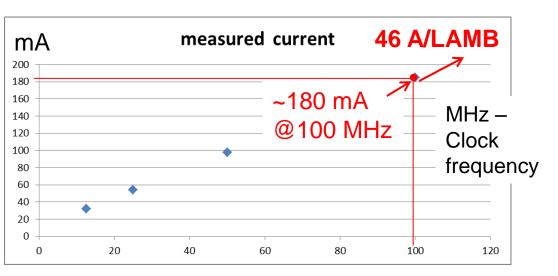

BUT **Serial links** add a not negligible contribution:

~ **30 W** for each LAMB and **24 W** for AMBSLP: Tot~ (4\*30+24)\*16 = **2300 W TOO MUCH**

FURTHER REDUCTION of AMCHIP CONSUMPTION and LARGER BANK (128 Kpatterns) will RENORMALIZE THE TOTAL CONSUMPTION

~5 KWATT

AM System (4) IAPP and STREP FP7 applications for extra funds People Manpower ICT - funds for Amchip – requested to EC 3 Meuros Funded 1.5 Meuros (in March the result) Starts Feb 2013 **UniPisa** (Pisa) Dell'Orso - **AM system boards LPNHE** (Paris) Calderini - **AMchip** (applied also to its funding agency) AUTH (Tessaloniki) Kordas board firmware – simulation **IAPP** CERN (TE-MPE-EM section) Formenti board design consortium **CAEN** (Viareggio) Petrucci - Integration Strong technical Prisma Electronics (Alexandroupolis) Mermigli support board development, assembly, test – firmware

Strong technical

support

**STREP** (coordinator INFN) would add for FTK: **University of Geneva** on **AM system Boards** (applied also to its funding agency)

IMEC for flip chip multi-packaging and AMchip submissions to TSMC MICROTEST - test setup for AMchip massive production tests

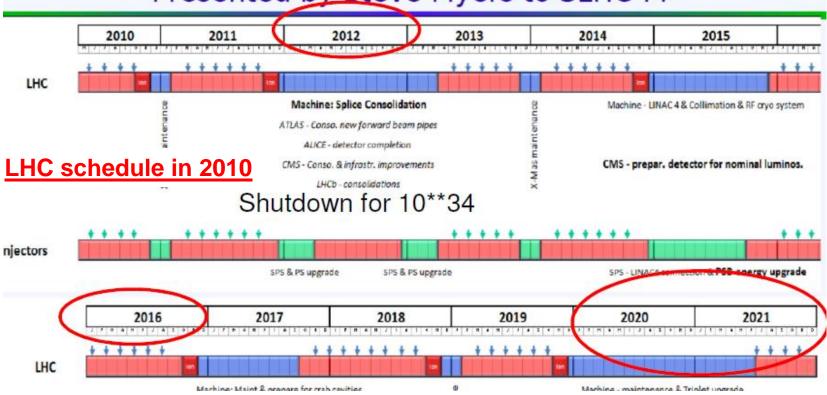

#### Presented by Steve Myers to SLHC-PP

#### Workplan at review time (Dec. 2010)

- 2012 or 2013 installation of all Hola2 during long shutdown Substitute them in small bunches, reconnect to TDAQ & test;

FTE: 2 months, may be more. Procedure to be established with ID people

- 2013 enlargement of vertical slice to cover the barrel first (8 or 16 PUs) *FTE: 4x8 months?*

- 2013-2014 data taking

- 2015 extension to the forward/backward detector regions FTE: 3x5 months?

- 2015-2016-2017 increase computing power as needed FTE: 3x4 months?

# LHC Time-line (CERN DG at ICHEP 2012)

(See also DG New Year Presentation on 6th Jan 2013)

https://indico.cern.ch/getFile.py/access?resId=0&materialId=slides&confId=219327

| 2009          | Start of LHC                                                                                                                                              |                                                                                                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|               | Run 1: 7 and 8 TeV centre of mass energy, luminosity ramping up to few 10 <sup>33</sup> cm <sup>-2</sup> s <sup>-1</sup> , few fb <sup>-1</sup> delivered |                                                                                                |

| 2013/14       | LHC shut-down to prepare machine for design<br>energy and nominal luminosity                                                                              |                                                                                                |

|               | Run 2: Ramp up luminosity to nominal ( $10^{34}$ cm <sup>-2</sup> s <sup>-1</sup> ), ~50 to 100 fb <sup>-1</sup>                                          | (Could go further<br>and need to worry                                                         |

| 2018          | Injector and LHC Phase-I upgrades to go to ultimate luminosity                                                                                            | about high μ before<br>going to 25ns)                                                          |

|               | Run 3: Ramp up luminosity to 2.2 x nominal, reaching ~100 fb <sup>-1</sup> / year accumulate few hundred fb <sup>-1</sup>                                 | (We assume up to<br>3×10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> and<br>25ns, so should |

| ~20 <b>22</b> | Phase-II: High-luminosity LHC. New focussing magnets for very high luminosity with levelling                                                              | plan for µ up to 81)                                                                           |

|               | Run 4: Collect data until > 3000 fb <sup>-1</sup>                                                                                                         |                                                                                                |

| 2030          |                                                                                                                                                           | 2                                                                                              |