## Status of the tests on the 8x32 *3DTC* chips and preliminary results of the 2012 beam test on *INMAPS*

#### beam test on INMAPS

S. Bettarini, G. Casarosa, F. Morsani, A. Perez, G. Rizzo

INFN - Sezione di Pisa

and the 2012 testbeam team

PRIN 2009 / VIPIX Meeting - Milano

#### outline

- ➡ CMOS MAPS in 180 nm INMAPS technology: Apsel4Well

- testbeam results, efficiency vs threshold

- results of the lab tests on inductions

- ➡ Vertically Integrated DNW MAPS: Apsel3D\_TC

- lab characterizations

- interconnection of the two layers

- tests on inductions

NOTE: signal amplitudes in mV are *not corrected* for the buffer scaling factor (0.9)

# Apsel4Well

- ➡ 3x3 analog-only chips

- ➡ thickness: 5 and 12 µm

- resistivity: standard (10  $\Omega$ cm) and high (1 k $\Omega$ cm)

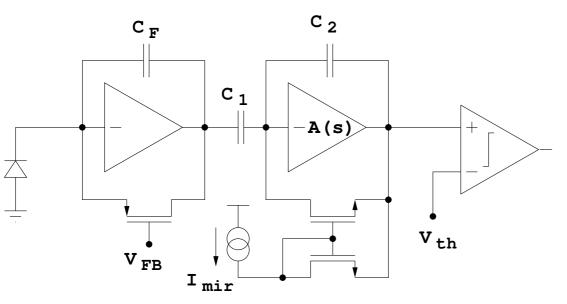

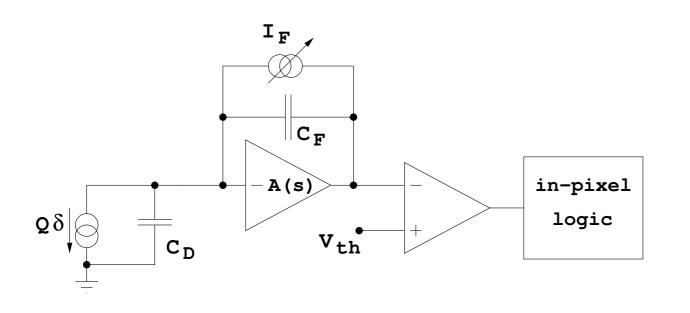

block diagram of the pixel analog front-end:

March 27<sup>th</sup> 2013

#### Apsel4Well on beam

- $\Rightarrow$  analog INMAPS and 3 chips 32x32, (hi $\Omega$ , 12 µm) have been tested with a 120 GeV/c pion beam

- analog INMPAS results not available yet

- presented at the SuperB • preliminary results available for digital chips: presenced at the Super-General Meeting in December

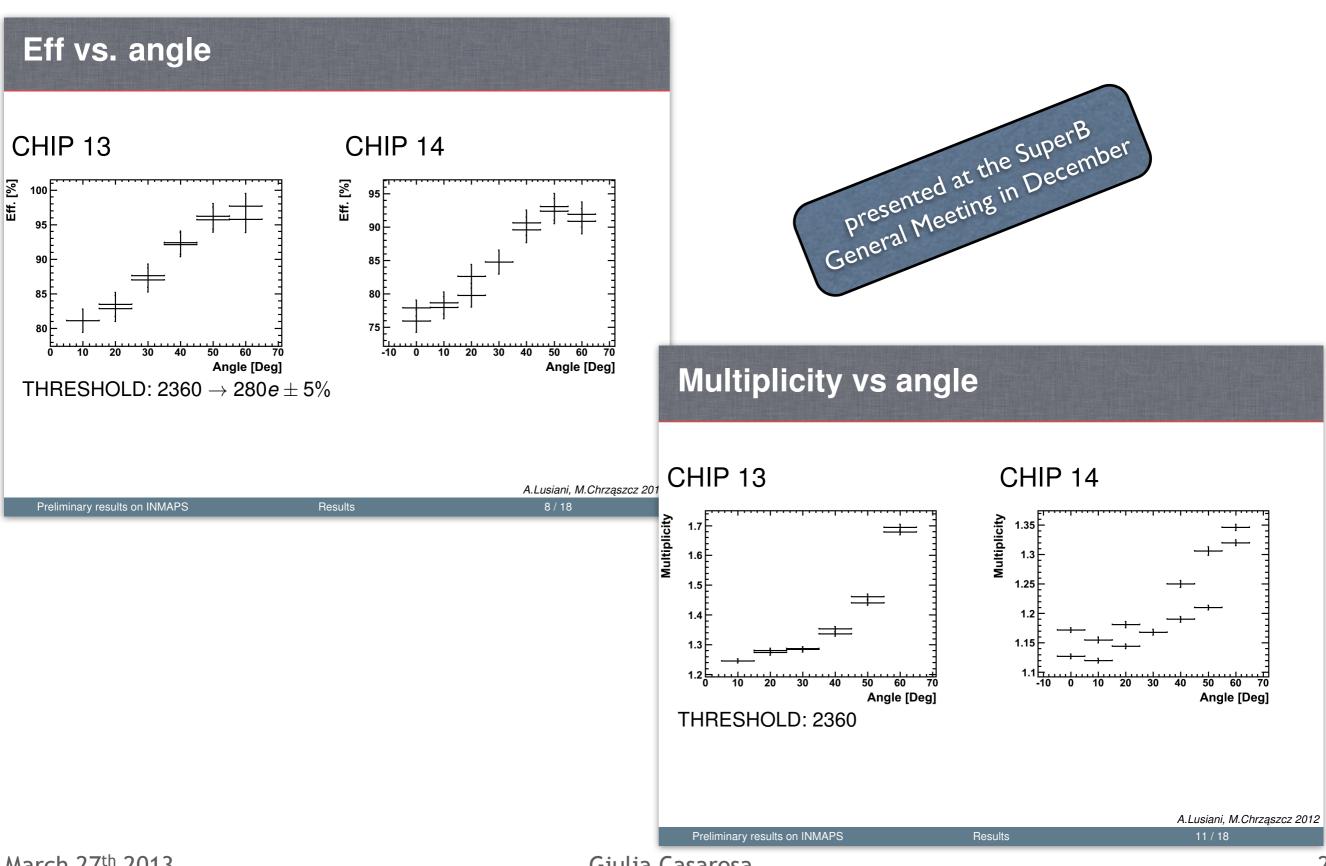

- efficiency vs threshold (DAC)

- efficiency vs angle

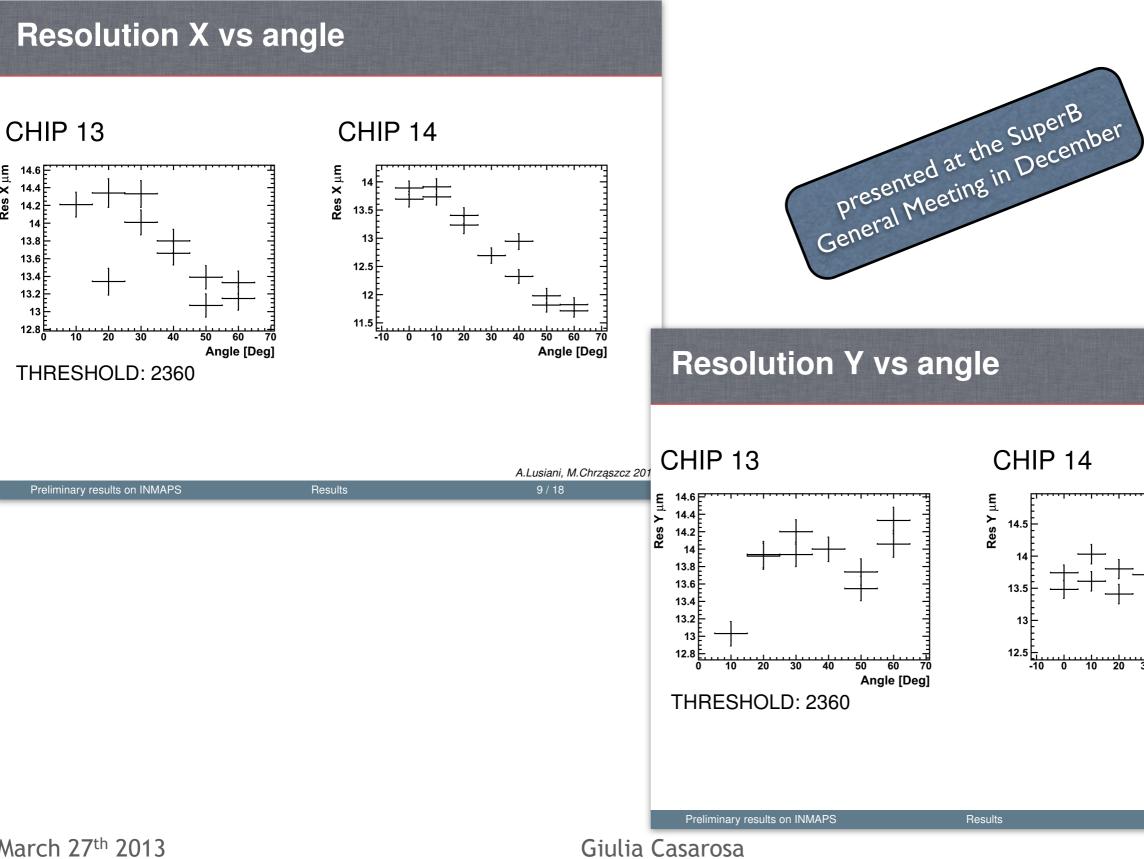

- resolution ۲

- resolution vs angle

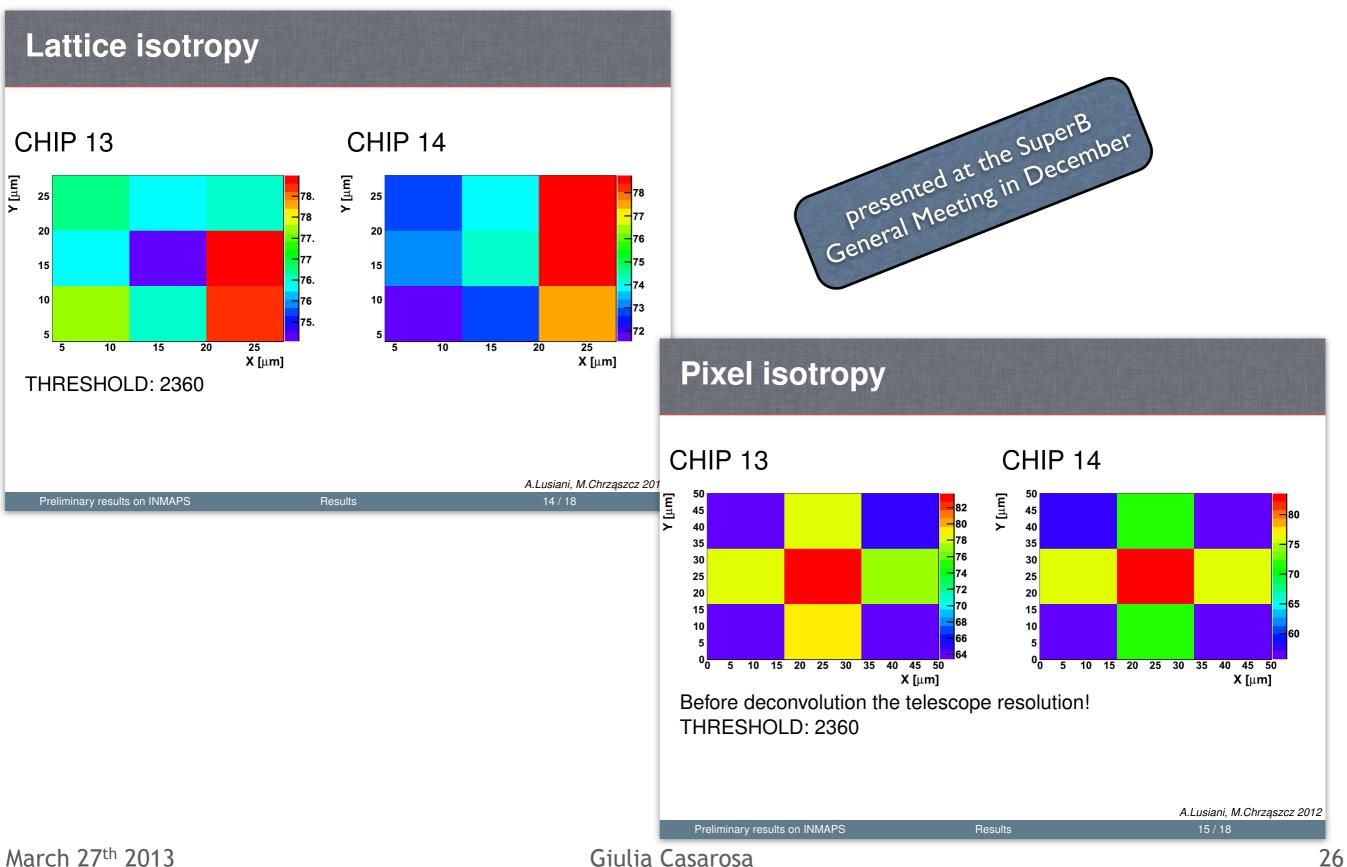

- lattice & pixel isotropy (still convolved with telescope resolution)  $oldsymbol{O}$

- The main issue with this chips is related to the low maximum efficiency reached and its deterioration at low thresholds:

- current explanation: inductions effects

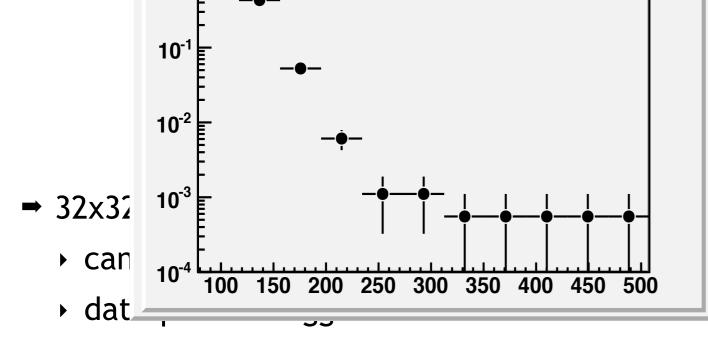

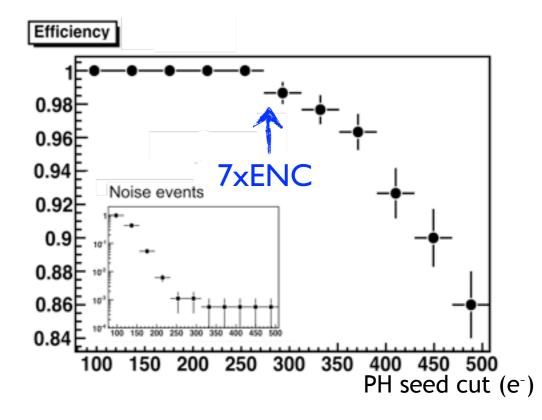

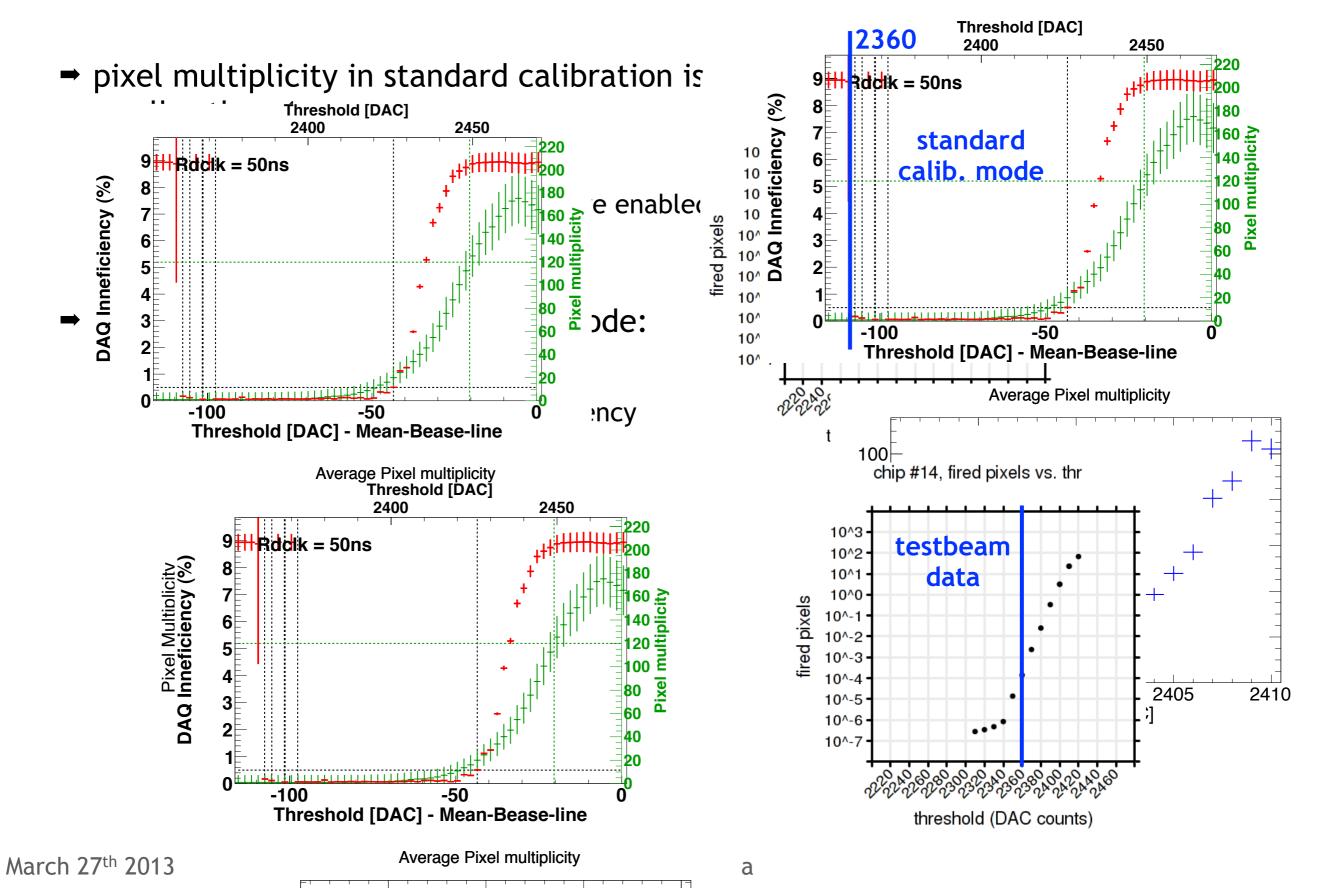

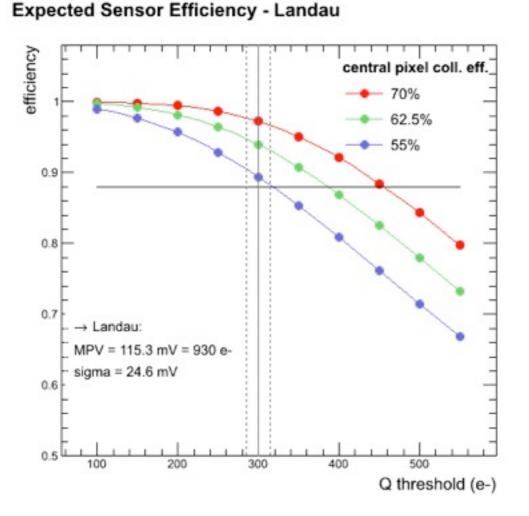

#### Efficiency vs Threshold

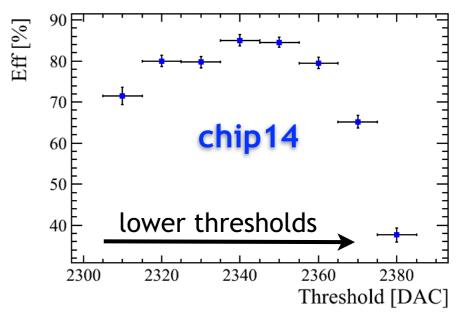

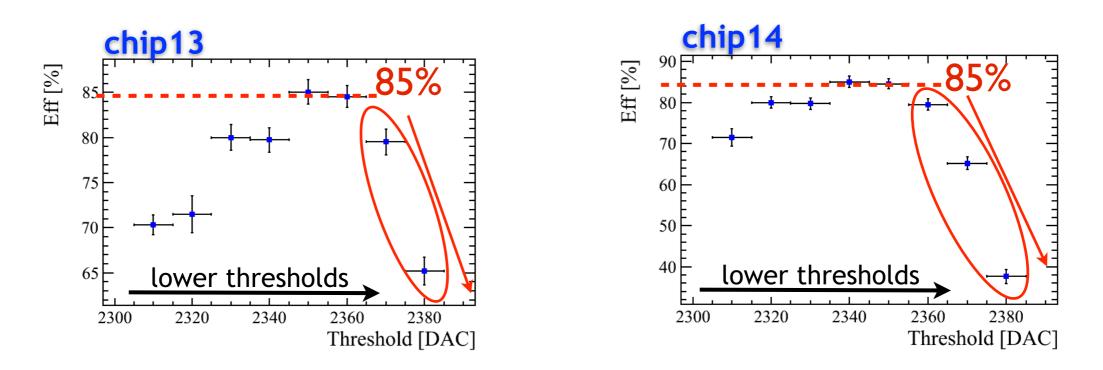

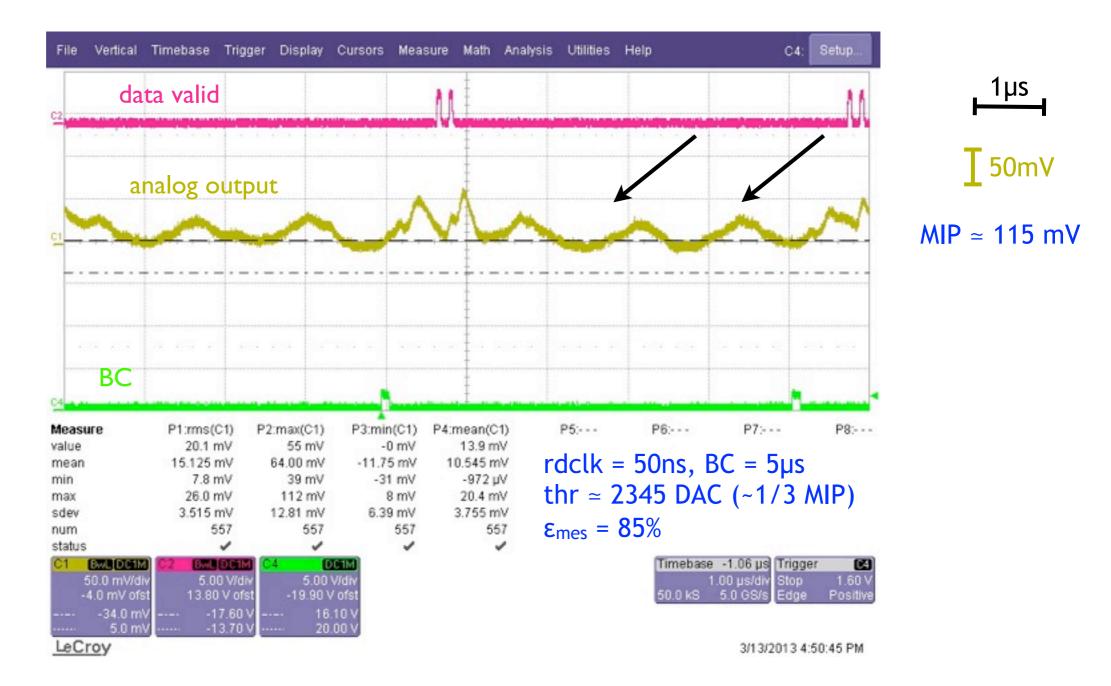

- →  $\epsilon_{max} \sim 85\%$  (@ 2360 DAC ~ 300e<sup>-</sup>), deterioration at lower thresholds.

- ➡ possible answers:

- inefficiency due to the fact that the pixel is already fired (on noise, or other...): excluded (v. bkp slide 20)

- inefficiency due to induction effects (positive induction related to digital activity masks negative signal from particles)

- other effects that may be related to the low maximum efficiency: charge sharing (v. next slide and 27) and too high threshold (v. bkp slide 28)

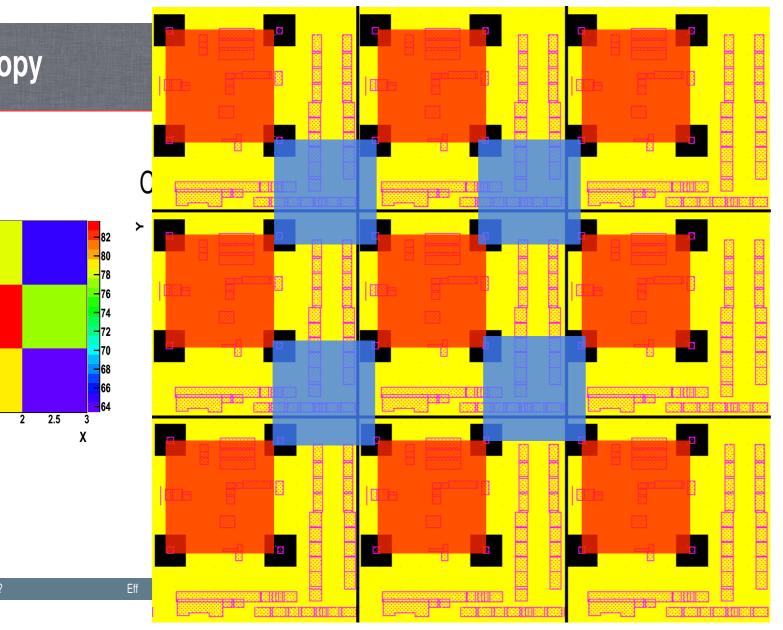

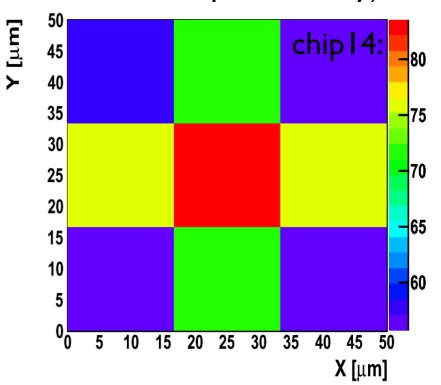

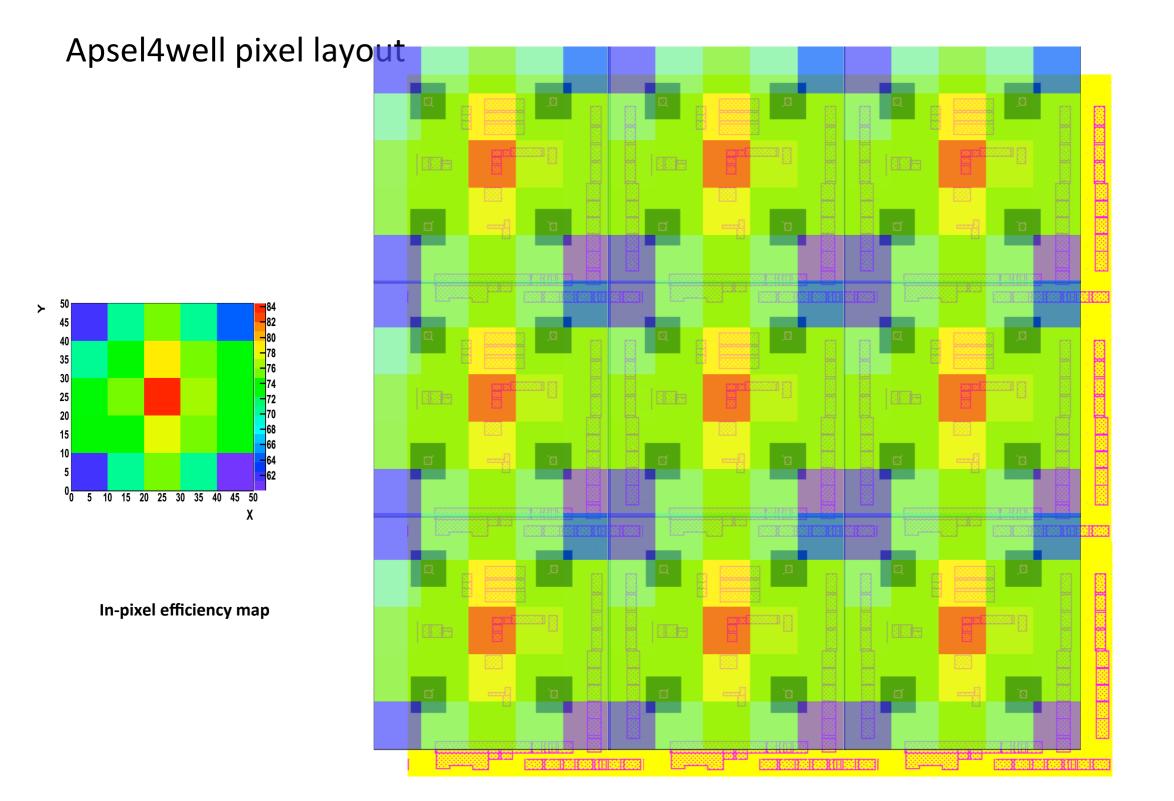

## Efficiency Within Pixel

Low efficiency regions: the released charge is shared among more than 1 pixel and not enough to go below threshold.

in-pixel efficiency (still convolved with telescope efficiency):

Giulia Casarosa

#### Induction Effect #1

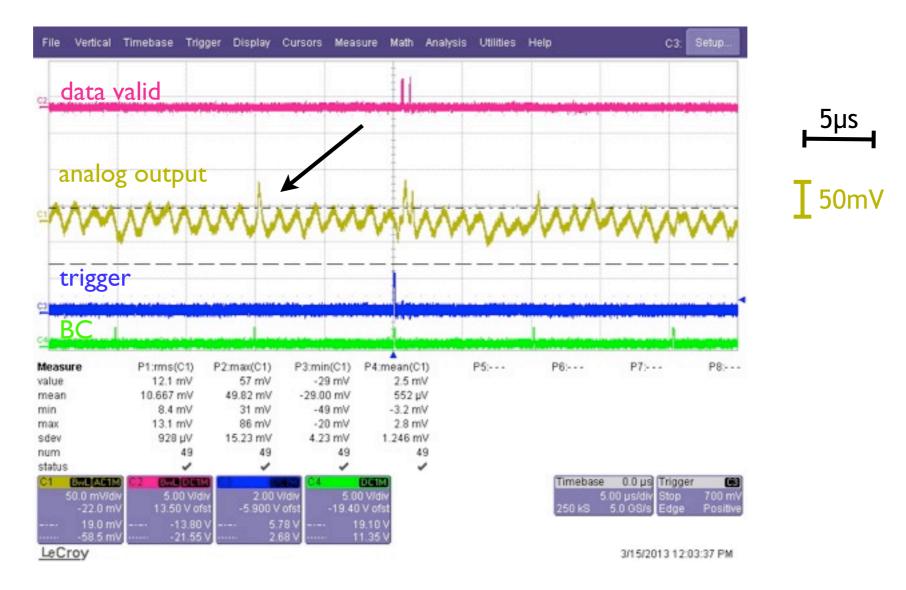

1. When a timestamp or a hit is readout we observe **big positive spikes** on the analog output (50 - 100mV). Also in correspondence of some BCs, signals going towards the matrix (TS update) induce **positive and negative spikes**

#### Inductions Effect #2

2. When rdclk/fastclk > 20MHz (50ns) we observe an **oscillation** independent of the BC period present only if fastclk is active (due to activity in the periphery).

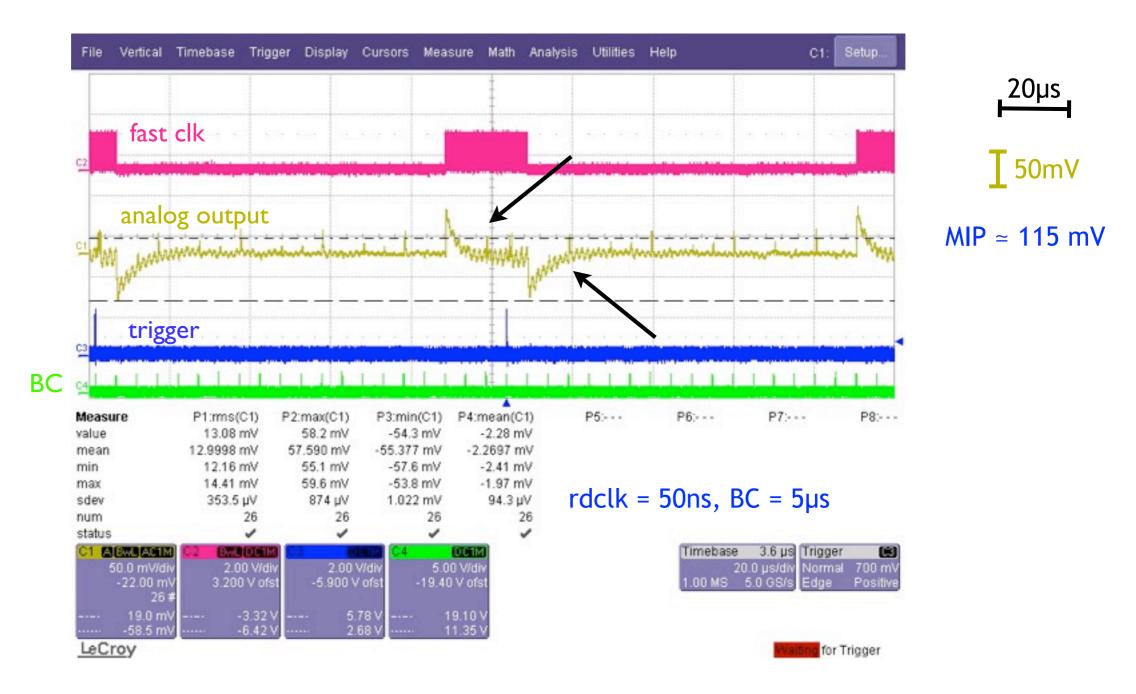

#### Induction Effect #3

3. We observe **big** (50 - 100 mV) **positive (negative) spikes** when fastclk starts (ends) in the periphery. The superimposed **oscillation** is present only if fastclk > 20MHz and is attenuated in ~ 30  $\mu$ s.

## Tests on Analog 3x3 Matrices

- → Tests on a 3x3 analog matrix show similar effects when digital signals run on the chip.

- positive pulse triggered by the start of ldx Edge Time 1 -282 ps 20µs long the train and sensitive to the frequency pulse of pulses train negative pulse, same amplitude as the 50mV positive one, triggered by the analog interruption of the pulses output • when train is shorter, the two pulses merge P12:---111.1 mV 222.8 mV 1117 mV -111 1 mV 22 27 mV -2.33 mV 1117 m 222 8 m\ 222.766 mV 111.693 mV -111.073 mV 111.693 m\ -111.073 mV 22.2669 mV -2.3342 mV 222.8 mV 222.8 mV 111.7 mV -111.1 mV 22.27 mV -2.33 mV -111.1 mV 111.7 mV 111.7 mV -111.1 mV 22.27 mV -2.33 mV -111.1 mV 111.7 mV 222.8 mV ider Display Cursors Measure Math Idx Edge Time 1 -147 ps 500ns high $\Omega$ , 12µm short pulse train 50mV analog 1. maximum effect obtained with pulse train output period of 25 - 30 ns 2. level of induction is ~proportional to the amplitude of the pulse train P2:ampl(C2) 118.20 mV P8:top(C2) 114.11 mV P12:--3. the effect is independent of the stimulated value mean min max 17.71 mV 125.2 mV 115.2 mV -10.0 mV 42.38 mV -4.09 mV 125 208 mV 118 1986 mV 115 190 mV -10 018 mV 42 3772 mV 17 7146 mV -4 0889 mV 114 1097 mV -10.0 mV 118.20 mV 114.11 mV -10.0 mV 125.2 mV 118.20 mV 115.2 mV 42.38 mV 17.71 mV -4.09 mV 114.11 mV track sdev 4. the effect in some low  $\Omega$  chips seems smaller high $\Omega$ , 12µm

March 27<sup>th</sup> 2013

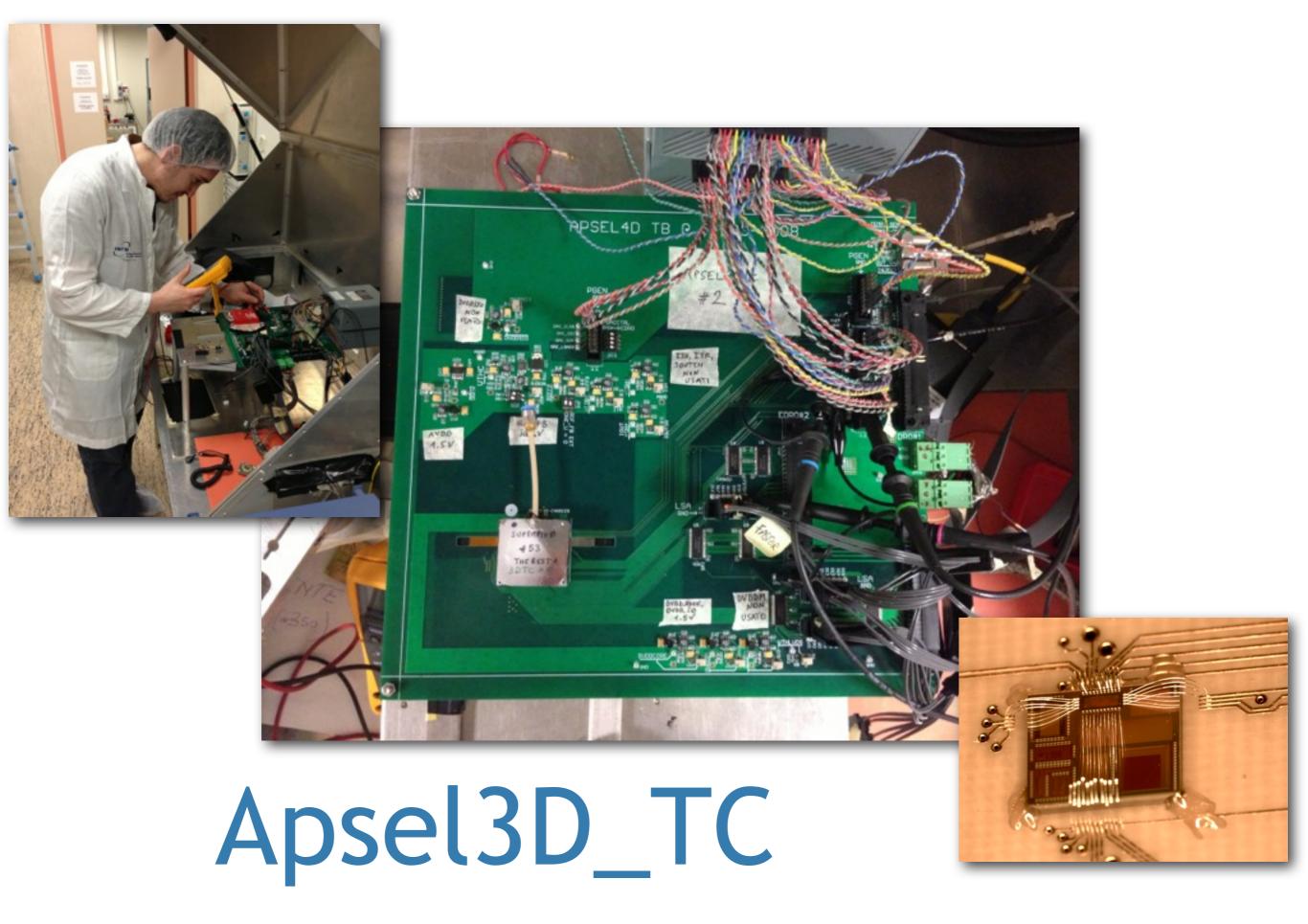

## Apsel3D\_TC reminder

- ➡ 8x32 matrix organized in 4x4 macropixels (MP)

- can mask selected MPs

- data-push readout architecture

- ➡ 3x3 analog-tier only chips

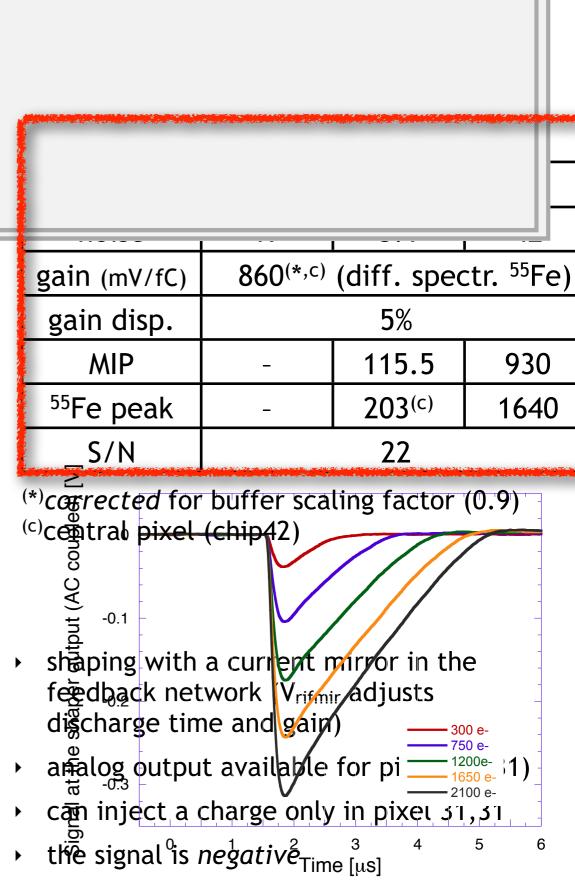

|                       | DAC       | mV        |       | e-       |

|-----------------------|-----------|-----------|-------|----------|

| thr disp              | 11-14     | 3.4       | - 4.3 | 80 - 90  |

| noise                 | 5.4 - 6.2 | 1.7       | - 1.9 | 40       |

| gain (mV/fC)          | 290 (dig  | ital) 320 |       | (analog) |

| gain disp.            | 20%       |           |       |          |

| MIP                   | -         | 40        |       | 1000     |

| <sup>55</sup> Fe peak | _         | 80        |       |          |

| S/N                   | 23        |           |       |          |

block diagram of the pixel analog front-end:

- bandwidth-limited preamplifier to improve signal-to-noise

- analog output available for pixel (31,7)

- can not inject a charge

- the signal is *positive*

## Apsel3D\_TC - analog-tier only

- → tested on beam (2011):

- → 3x3 cluster signal MPV ~ 1000 e-

- ► S/N ≈ 23

- efficiency  $\approx$  98% at thresholds up to 7xENC

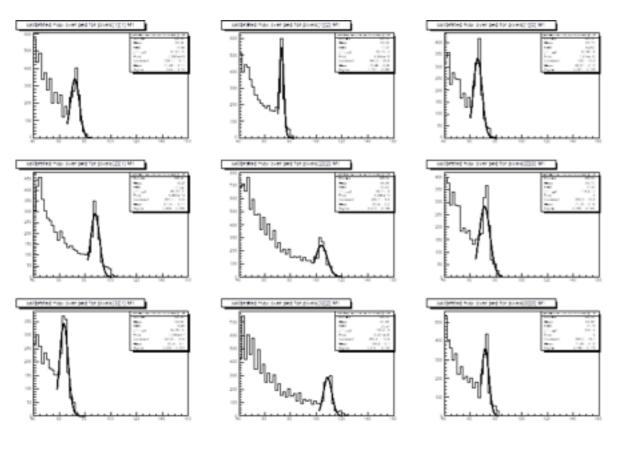

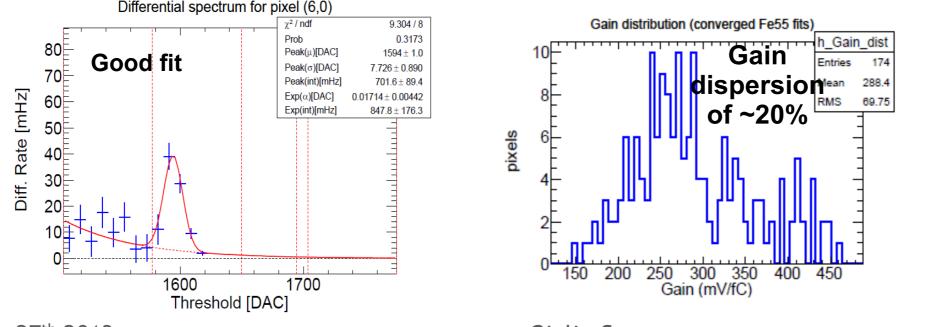

differential spectrum of the 3x3 pixels (55Fe):

- ➡ tested with a <sup>55</sup>Fe source:

- 5.9 keV  $\gamma$ , 1640 e-  $\simeq$  2xMIP

- measured gain ~ 320 mV/fC (half the expected value) and quite dispersed

- feedback capacitance of the preamplifier realized exploiting parasitic capacitance of two tracks

- value estimated from post-layout simulations: not reliable (→ low gain) and quite dispersed (→ dispersed gain)

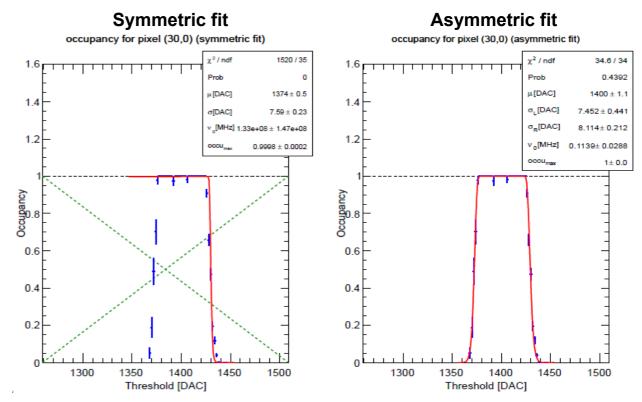

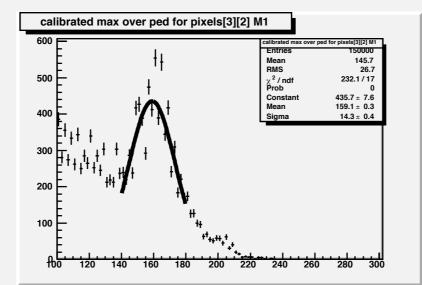

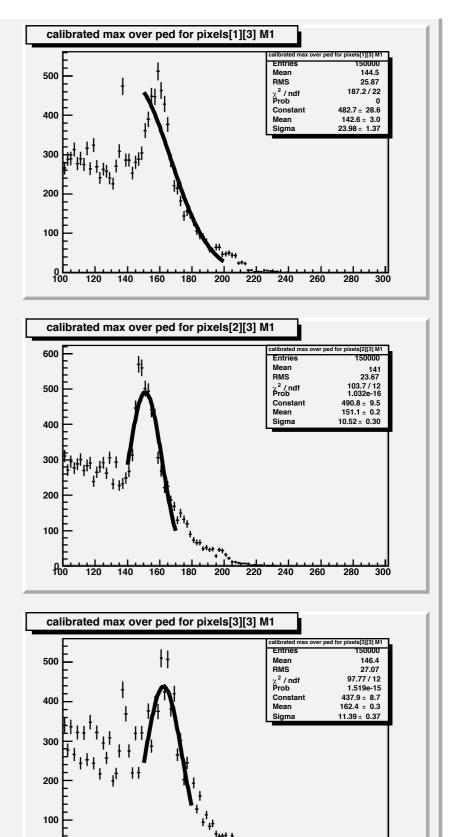

## Apsel3D\_TC calibrations

- → Noise Scans:

- need to fit with *asymmetric* function

- something  $oldsymbol{O}$ asymmetric in

the circuit?

- $\sigma_L \simeq 85\% \sigma_R, \sigma_R \simeq 1.7 1.9 \text{ mV}$

- **comparator**?  $\sigma_R \sim$  in agreement with what seen on the analog output of pixel (31,7)

- limited threshold dispersion

- 3.4 4.2 mV (~2.5xσ<sub>R</sub>)

- → Gain Calibrations with <sup>55</sup>Fe (1640 e-  $\simeq$  2xMIP), differentiated digital scan:

- central value  $\simeq 285 \text{ mV/fC}$ , very large dispersion, o(20%) (even within a MP)

difficult to pilot with a single threshold  $\rightarrow 8x32$ digital matrices not tested on beams

March 27<sup>th</sup> 2013

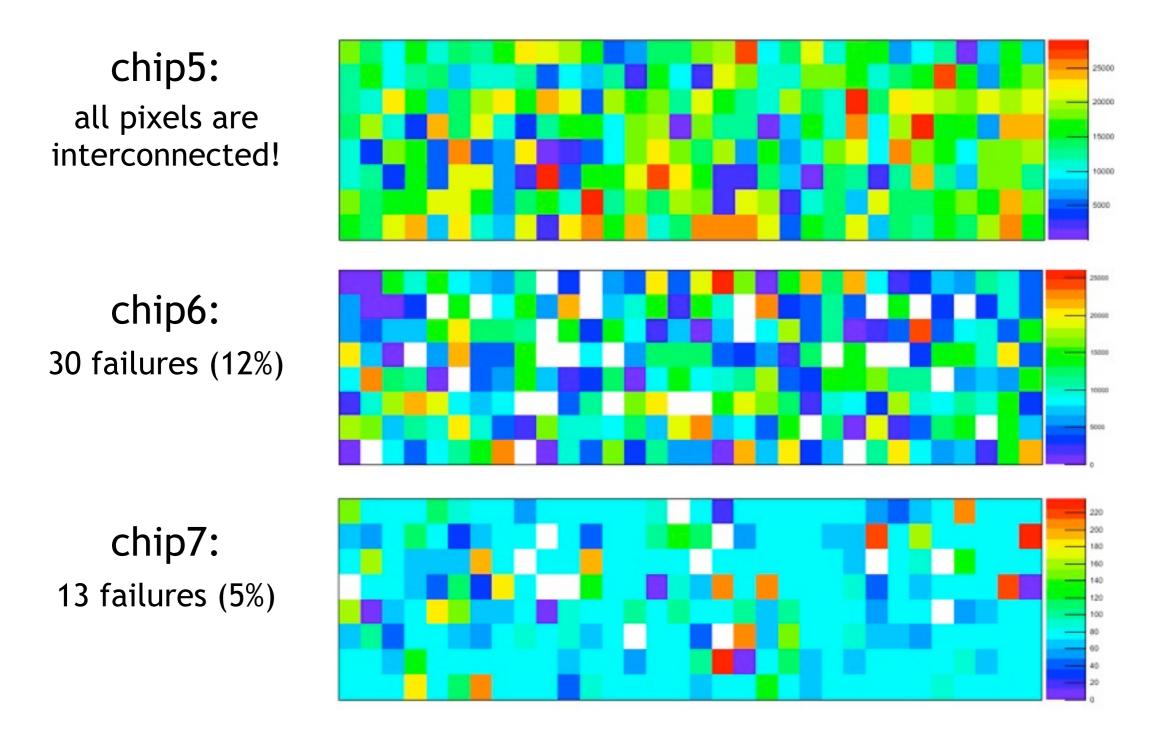

## **Interconnected Chips**

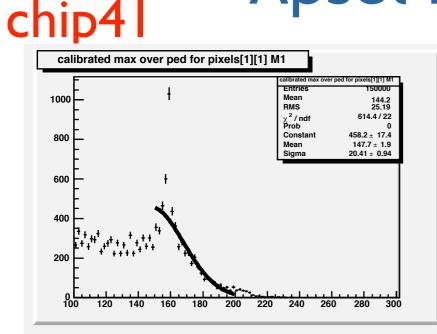

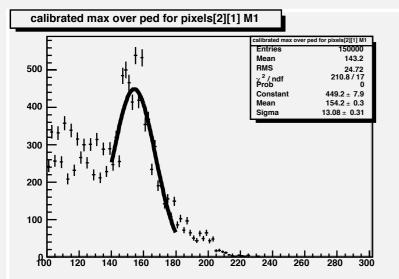

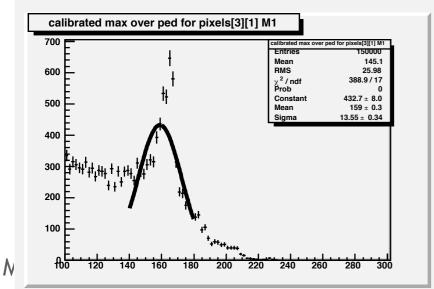

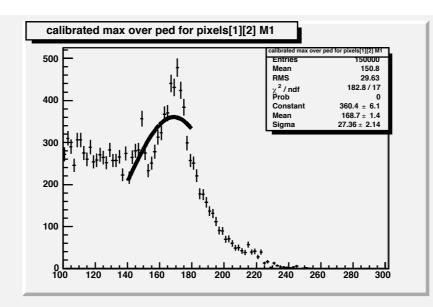

→ response of the digital 8x32 devices to a  $^{55}$ Fe source:

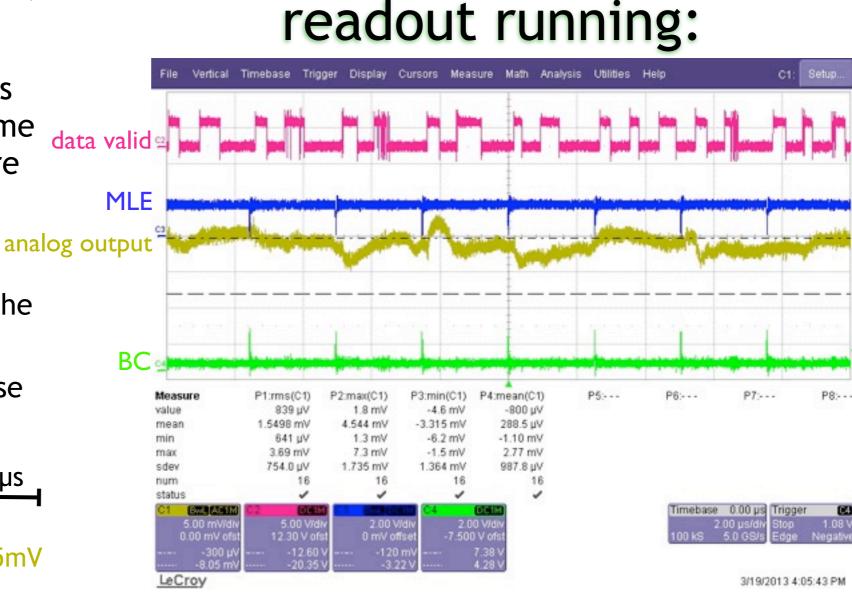

#### **Tests on Inductions**

- $\rightarrow$  No significant inductions visible at the analog output of pixel (31,7): tested at very high clk rates:

- rdclk = 50 MHz (20ns)

- BC  $\simeq 2.5 \ \mu s$

- checked that pixels beloning to the same MP as pixel 31,7 are fired

- small induction, order of the noise (2 mV) due to the clk, on chip? testboard?

- 1/4 MIP (10mV)  $\approx$  5 x noise

- safe operations

$MIP \simeq 40 \text{ mV}$

2µs

T 5mV

#### **Tests on Inductions**

- $\rightarrow$  No significant inductions visible at the analog output of pixel (31,7): tested at very high clk rates:

- rdclk = 50 MHz (20ns)

- BC  $\simeq 2.5 \ \mu s$

- checked that pixels beloning to the same MP as pixel 31,7 are fired

- small induction, order of the noise (2 mV) due to the clk, on chip? testboard?

- 1/4 MIP (10mV)  $\approx$  5 x noise

- safe operations

#### no readout:

2µs

T 5mV

#### Conclusions

- ➡ Apsel4Well:

- serious induction effects deteriorate the performance of high resistivity devices, less pronounced on low res ones

- need to understand the cause of the observed induction

- other effects (as charge sharing) may also play a role to explain the low maximum efficiency

- ➡ Apsel3D\_TC:

- promising results from analog devices: 98% efficiency

- 3 working interconnected chips

- large gain dispersion prevented the test with beams

- no significant induction

## Additional Slides

#### Apsel4Well: Pixel Multiplicity

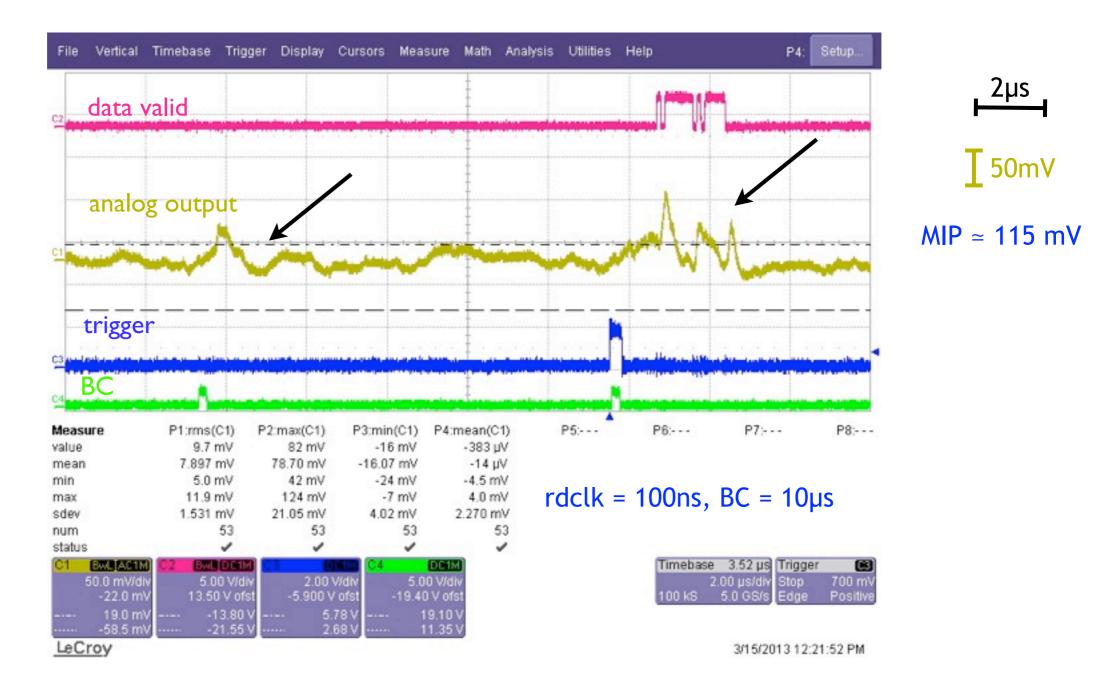

## Apsel4Well Inductions: oscillation

- → when rdclk is fasten to 50ns, an oscillation appears

- period ~1.5µs, ampl ~ 20 mV

note: MIP  $\simeq$  115 mV

#### data-push mode, thr $\simeq$ 2400 DAC

→ positive induction (~ 100mV) covers a non-negligible fraction of the time between two BCs: if a MIP hits the pixel in this time, the signal doesn't cross the threshold → inefficiency!

note: MIP  $\simeq$  115 mV

#### Apsel4Well: angle dependence

#### **Apsel4Well:** resolution

A.Lusiani, M.Chrząszcz 2012 10/18

70

Angle [Deg]

CHIP 14

Res Y µm

14

13.5

13

12.5

Results

-10

10

20

30

40

Res X μm

## Apsel4Well: lattice & pixel isotropy

## Efficiency Within Pixel, 5x5

#### Landau from <sup>90</sup>Sr Measurements

- → Landau measured with <sup>90</sup>Sr on analog devices

- MPV = 115mV, sigma = 24.6 mV

- ➡ use gain to translate mV into e<sup>-</sup>

- → Vary the central pixel collection efficiency

# landau $\int_{0}^{0} \int_{0}^{0} \int_{0}^{$

- central pixel collection efficiency:

- ► **70**%

- ▶ 62.5%

- ► 55%

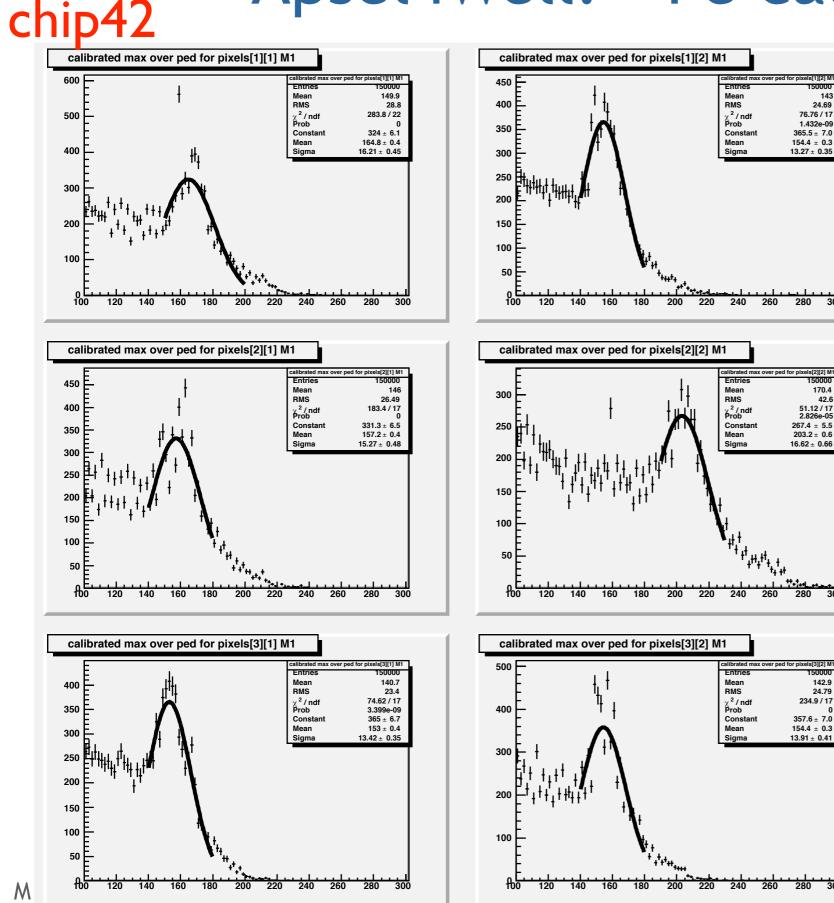

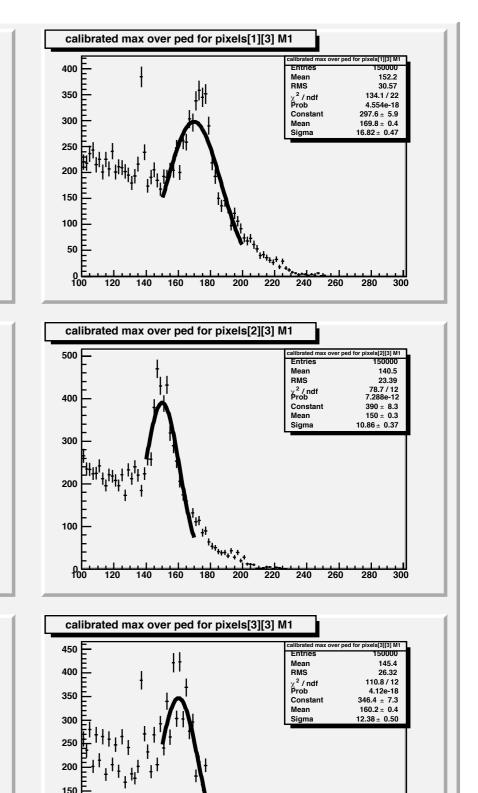

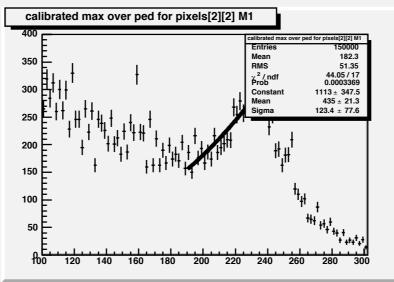

#### Apsel4Well: <sup>55</sup>Fe calibrations

143

24.69

76.76 / 17

1.432e-09

365.5 + 7.0

$154.4 \pm 0.3$

$13.27 \pm 0.35$

280

300

170.4

51.12 / 17 2.826e-05

$267.4 \pm 5.5$

$\textbf{203.2} \pm \textbf{0.6}$

$16.62 \pm 0.66$

280

300

ls[3][2] M1

150000

142.9

24.79

100

50

θб

120

140

160

180

200

234.9/17

357.6 ± 7.0

$154.4 \pm 0.3$

$13.91 \pm 0.41$

280

42.6

29

240 260

220

#### Apsel4Well: <sup>55</sup>Fe calibrations

Ъb

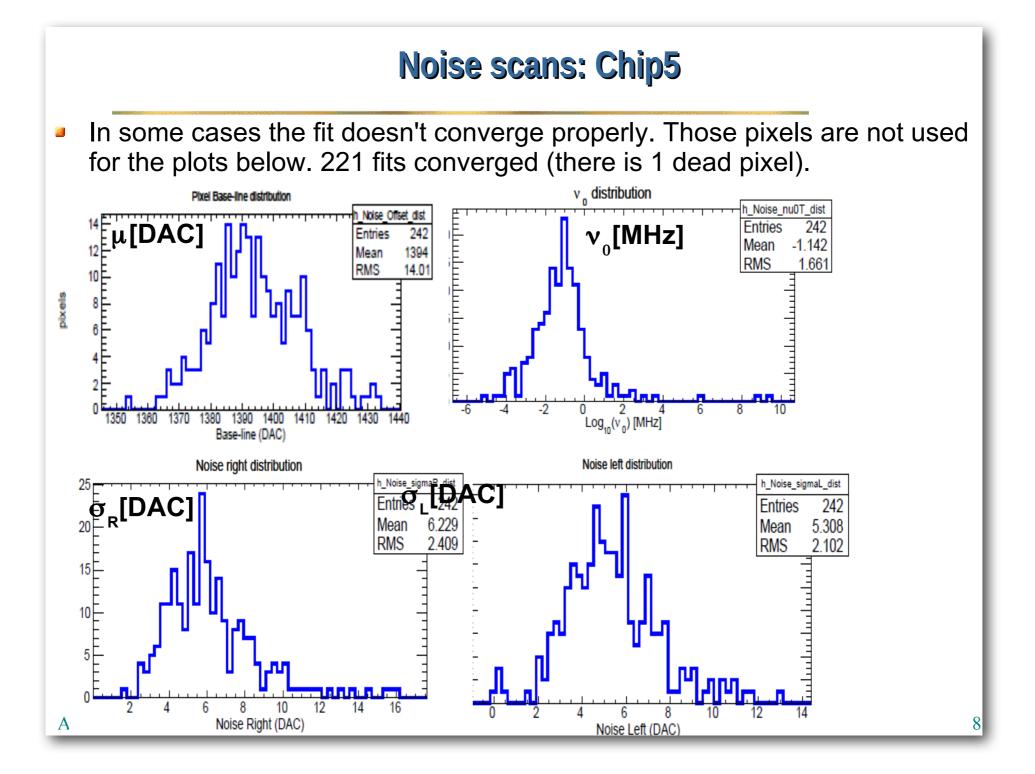

## Apsel3D\_TC characterization

## Apsel3D\_TC characterization

#### Noise scans: Chip6 In some cases the fit doesn't converge properly. Those pixels are not used 2 for the plots below. 204 fits converged (there is 28 dead pixel). Pixel Base-line distribution v distribution Noise\_Offset\_dist Noise nu0T dist μ[DAC] ני<sub>0</sub>[MHz] Entries 220 Entries 220 1385 Mean 14 Mean -1.133 11.06 RMS 0.9657 RMS ппл -1 0 Log<sub>10</sub>(v<sub>0</sub>) [MHz] -2 1390 1370 1380 1410 1420 1360 1400 Base-line (DAC) Noise right distribution Noise left distribution \_Noise\_sigmaR\_dist \_Noise\_sigmaL\_dist <sup>12</sup> **σ [DAC]** <sup>8</sup> $\sigma_{R}^{}$ [DAC] Entries 220 220 Entries 5.459 Mean 4.684 Mean 1.8 RMS 1.613 RMS 8 6 Noise Left (DAC) Noise Right (DAC) Alejandro Pérez, LNF SuperB meeting, Dec. 12th 2012 9