#### Thin Multilayer Bus

Mauro Citterio, Valentino Liberali, Alberto Stabile

**INFN Milano**

### Index

- 3-Chip Bus Status

- Production: lesson learned

- BUS construction phases

- Some consideration

- Test set-up for BUS characterization status

- Future solutions

- Multilayer flex processes used for "interposer" or special components

- Conclusions

#### **3-CHIP BUS**

#### Pixel Bus second generation:

- → Layout details agreed with CERN

- $\rightarrow$  Various iterations ..... about 2 years

- → Signal layers modified

- $\rightarrow$  Opening between layers were optimized

- $\rightarrow$  Production completed on November 2012

- $\rightarrow$  Layer by layer stack-up did not work out ...

- → Thin layers and registration problems

- → Layers separated into 3 groups ... Few pictures

- $\rightarrow$  Evaluation of the «few samples» received ... How we plan to procede

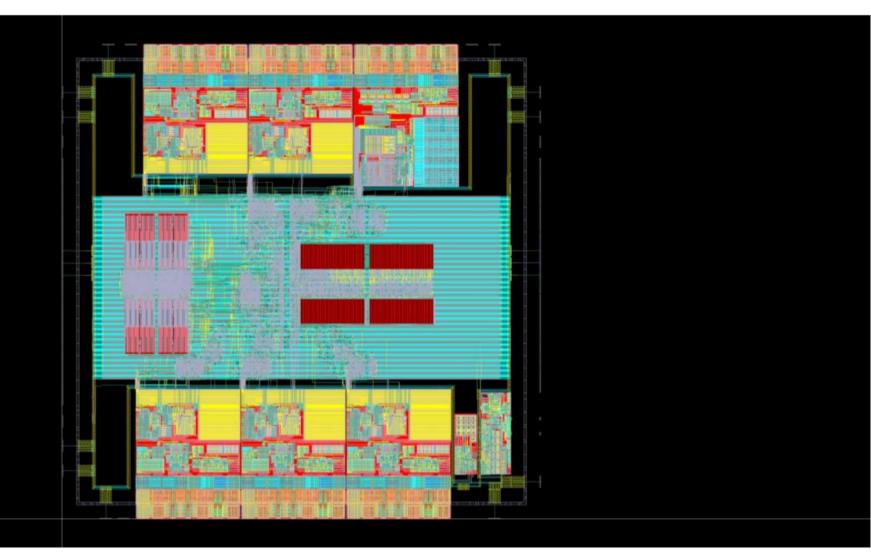

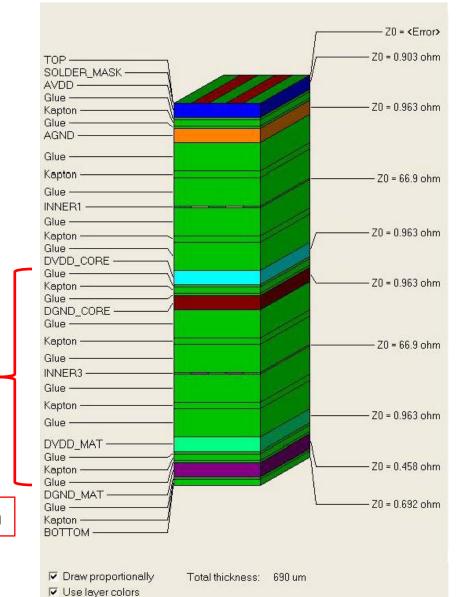

# Signal/Power layers

#### Overall view (using transparent layers)

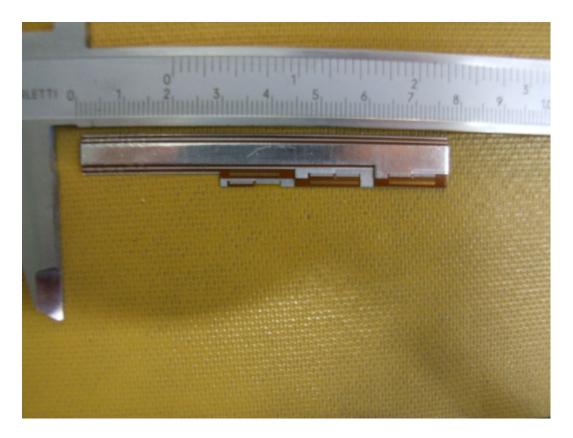

Layers were properly stacked ... cut-outs per each layer were optimized to preserve "bonding topology"

27/03/2013

Clips (soldering terminals) at the four corners

Bus produced using a Frame that contains 16 structures → In the picture "dgnd\_core.bottom" is shown (1 layer) → Extremely flexible layer but difficult to align properly

2<sup>nd</sup> sandwich made of 4 layers: 3 planes, 1 signal layer

- → In the picture are shown: "dvdd\_core.inner6", "signal2.inner5", "dvdd\_mat.inner3" and "dgnd\_mat.inner4"

- → Yield ~ 100 %

2<sup>nd</sup> sandwich made of 3 layers: 2 planes, 1 signal layer

→ In the picture are shown: "avdd.top", "agnd.inner1" and "signal1.inner2"

→ Yield ~ 100 %

# **Final Object**

- ightarrow To obtain the final bus the 3 sandwiches are "glued" together after alignment and preparation

- → Yield is low, < 50 % : 2 pieces in Milan, 2 at CERN plus 3-4 pieces to be evaluated carefully

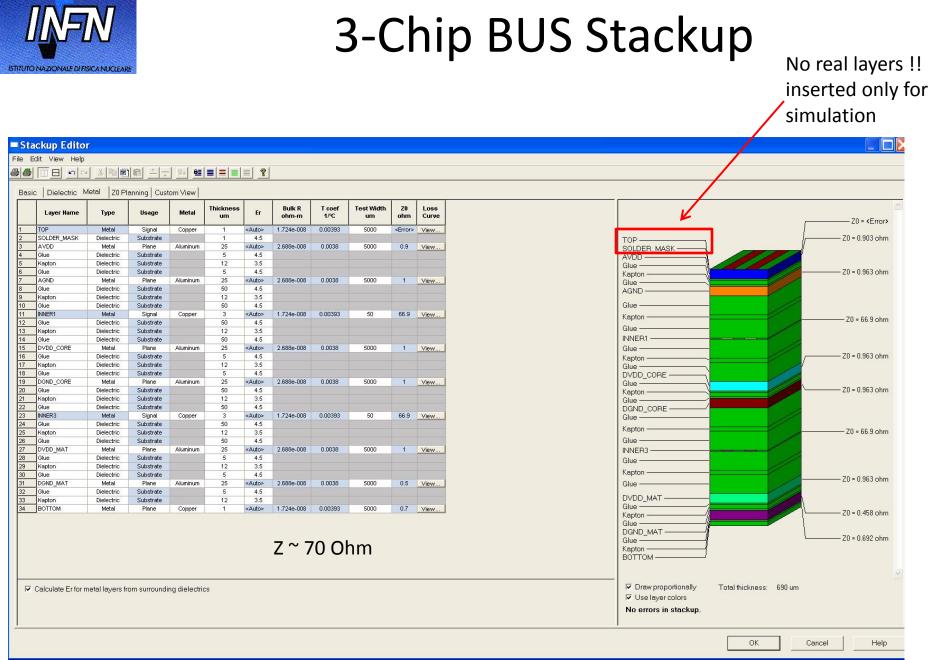

#### **Consideration and X0 reduction**

#### What could be probably done:

- No. of power planes: 2 .... max 3

- One plane subdivided in Analogue and Digital sub-planes? Not clear. No "sophisticated" pattern capability if treated as planes

- However two planes allow strip-lines design (better for crosstalk)

- Signal trace pitch could be reduced to ~ 50 micron to have only one signal layer for the signal.

- Aluminum lines possible !

Thickness, after optimization, could be ~ 350 um

# **BUS Characterization Setup**

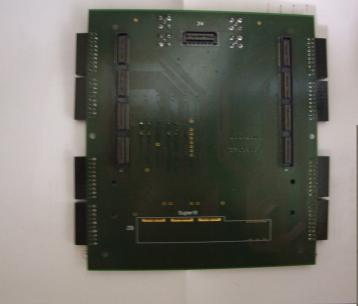

Multipurpose mother/daughter combination of boards developed together with SANITAS S.r.I (Milano):

- Based on a Virtex 5 "controller board" (showed in picture)

- Multiple daughter boards can be plugged in to customize testing (using connectors on the right side of board)

- Daughter board for BUS testing is in production at TVR

- Firmware is almost complete

- To inject signals/patterns (via Pattern generator or via FPGA)

- To measure Bit Error Rate (at various frequency, w/wo jitter, w/wo skew)

- The system can grow to emulate full data link (stacking up more daughter boards)

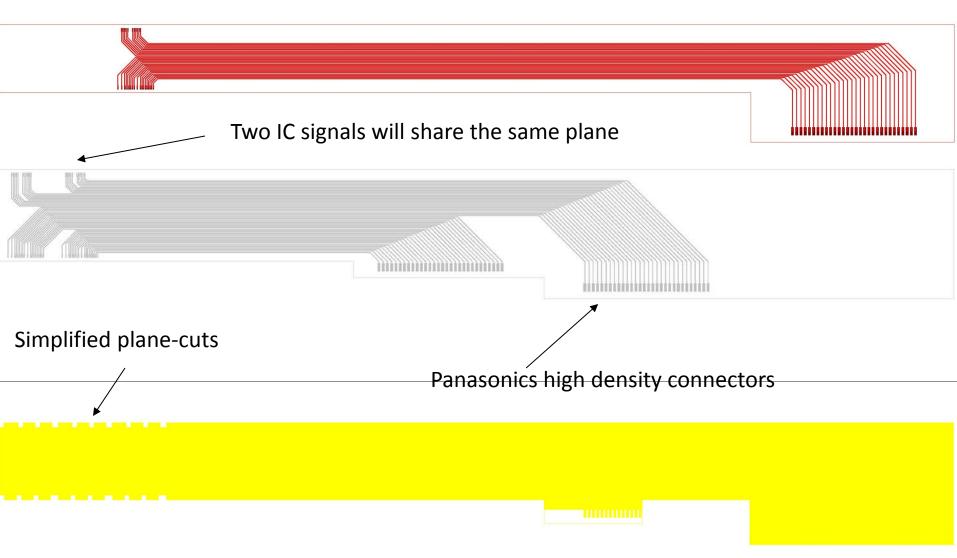

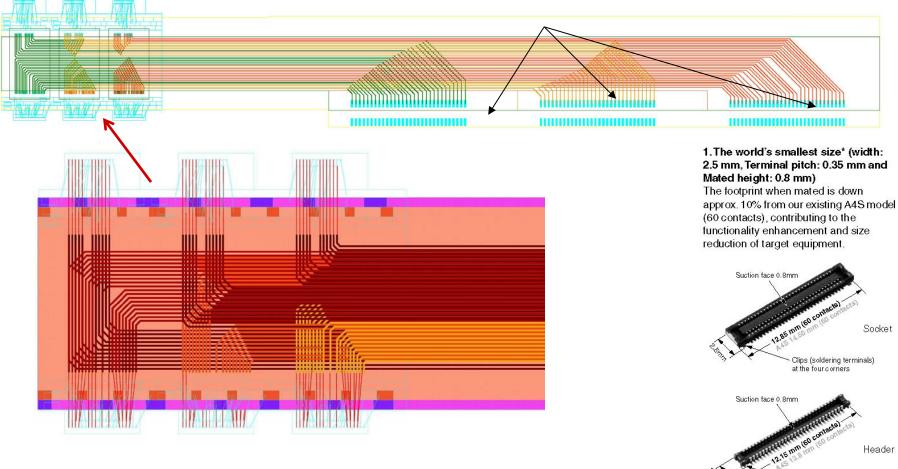

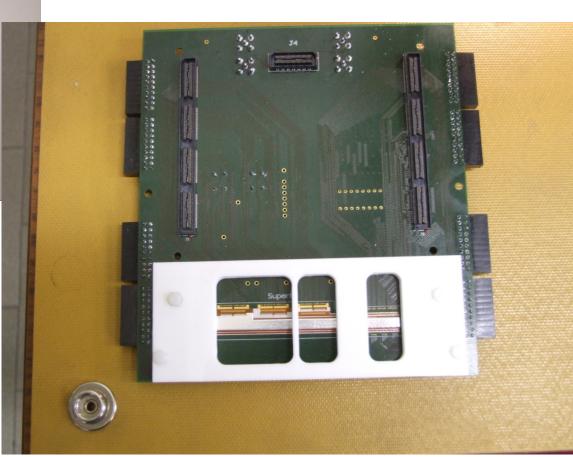

# Daughter board for the BUS

High density connectors matching motherboard

IN/OUT lines matched for impedance and "paired" in length for each chip ( $\Delta L \sim cm$ )

#### **Daughter Card**

# **Future Solution**

What is needed:

- Ultra high resolution single and multilayer circuitry on flexible materials → YES

- Aluminum instead of copper → MAYBE

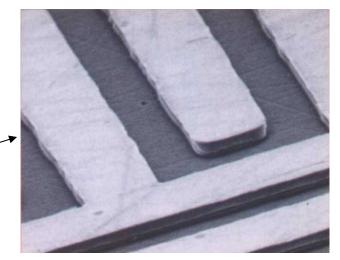

- Using high resolution photolithography, precision electroforming, and thin film deposition, high resolution flex circuits and electrode array plates can be made ... up to ~ 2x2 cm

- Conductor widths and spaces of 5 microns can be achieved .... But on what maximum dimensions? ~ 2cm

- Specialized companies ..... Are they interested in prototyping? YES, initial cost to be understood

MAGNIFICATION: 1.21 KX 5 Micron Conductors 5 Micron Spaces

# Conclusions

- → CERN has undoubtedly a proven capability in producing low mass, multilayer, flexible circuits

- $\rightarrow$  However 3-4 layers it's the limit

- $\rightarrow$  2-3 planes (~50 um), 1 signal (10 um)

- $\rightarrow$  50/50 um pitch in Al possible

- ightarrow We still need to verify how close the BUS matches our design specs

- $\rightarrow$  We should have asked for the individual sandwiches

- $\rightarrow$  Special commercial applications are requesting ultra-thin flexible circuits

- → At least one company is willingly to talk to us and it is also interested in producing prototype

- → Power planes: "strange beasts" for these technologies, again low power is welcome

#### FTK on going effort

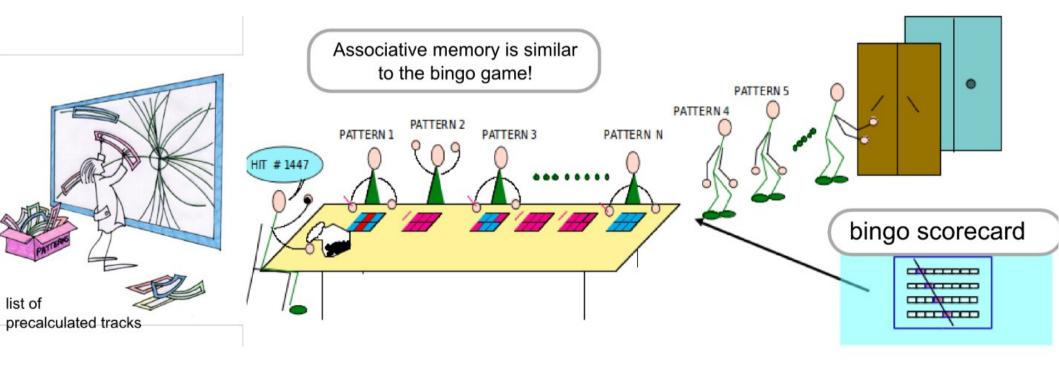

# AMchip theoretical principle

Associative Memory chip: AMchip

- Dedicated VLSI device maximum parallelism

- Each pattern with private comparator

- Track search during detector readout

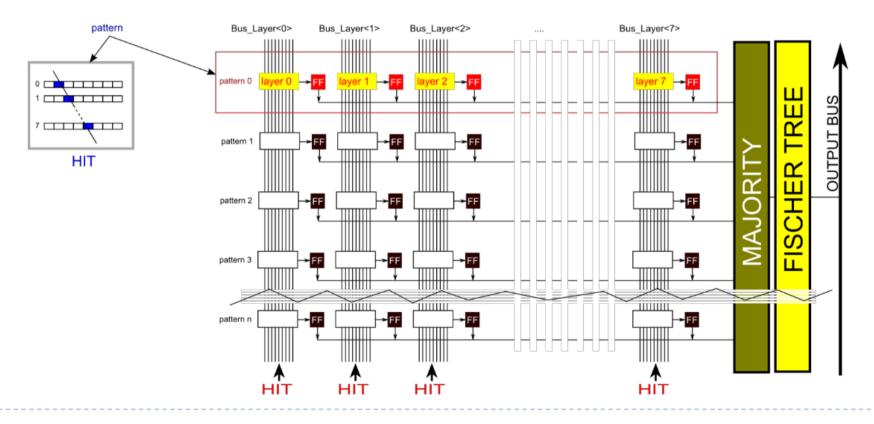

# Amchip

- Main aim: pattern recognition of Super Strips!

- Count the number of matching layers (from 6 to 8 layers)

- Bit map of matching patterns

- Variable resolution "pattern-by-pattern" and "layer-by-layer"

# Mini@sic goals & description

- Test chip between the AMchip04 and AMchip05

- New features

- Hits and roads are serialized and de-serialized inside the chip core

- Silicon Creation® SerDes IP blocks have been used for this purpose

- Silicon Creation® LVDS pad has been used to bring inside the chip an external LVDS clock

- □ The LVDS pad needs of a Band Gap Voltage Reference (always by Silicon Creation ®)

- Two different type of Associative Memory (AM) cells have been used

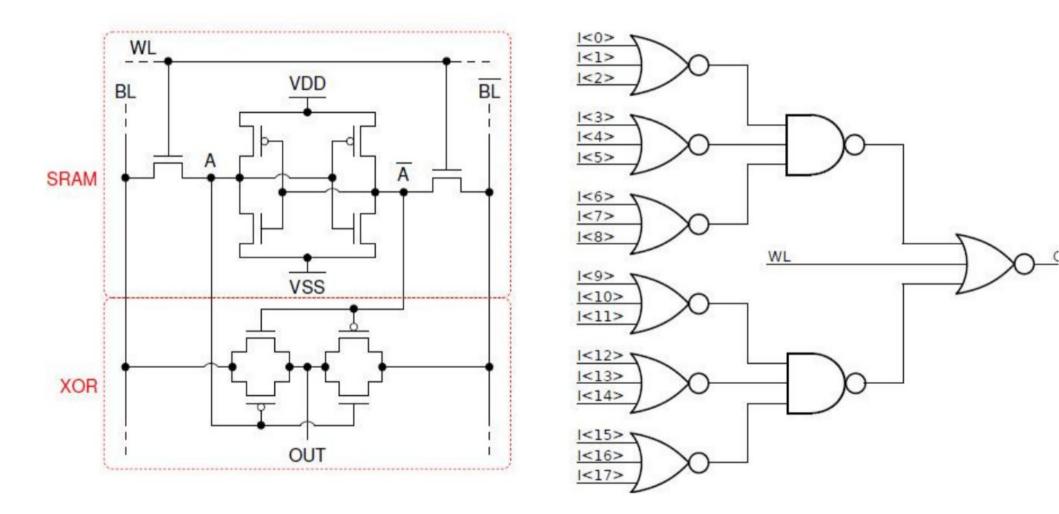

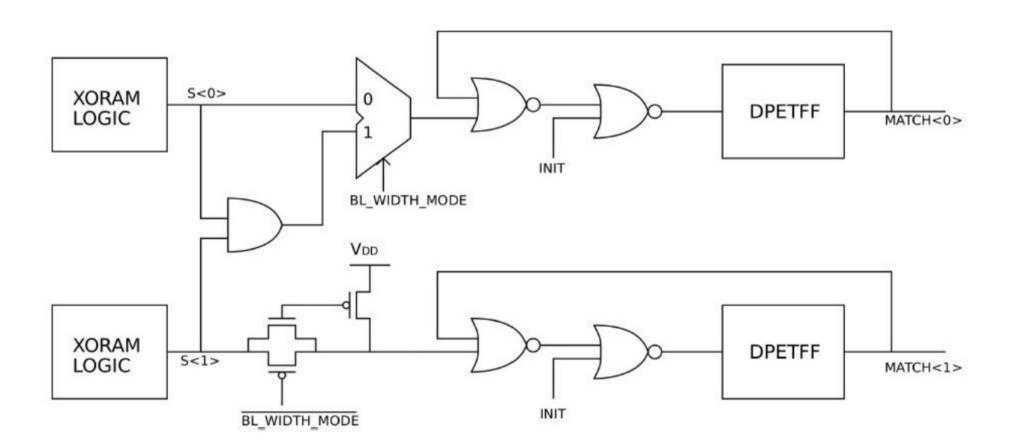

- A new XOR+RAM cell has been used with the aim to reduce silicon area and power consumption

- A more programmable Bit Line (BL) width mode

- With the XOR+RAM is possible to select how much is large the hit buses:

30 bit or 15 bit

- Built-In Self Test (BIST) used to stimulate the AM banks at maximum working frequency through JTAG commands

- $\hfill\square$  PRBS generator to stimulate the banks

#### The new "XOR+RAM = XORAM"

#### XORAM architecture

#### Submission