# Board Design

Andreas Sakellariou, Saverio Citraro

FTK-IAPP Executive Board – Pisa, 27 June, 2013

## Man Power for PCB design

0

Andreas Sakellariou, Secondment from Prisma Electronic to Pisa

April, May 2013

• Saverio Citraro, FTK-IAPP Researcher, UNIPI Fellow.

• Pierluigi Luciano, Master Degree Student University of Pisa.

### About new Boards

• AMBSLP: Associative Memory Board Serial Link Processor (Designed by Andreas Sakelariou, Saverio Citraro, CERN)

• MiniLAMBSLP: Little Associative Memory Board Serial Link Processor for Miniasic (Designed by Pierluigi Luciano)

• LAMBSLP: Little Associative Memory Board Serial Link Processor for Amchip05 (Designed by Saverio Citraro)

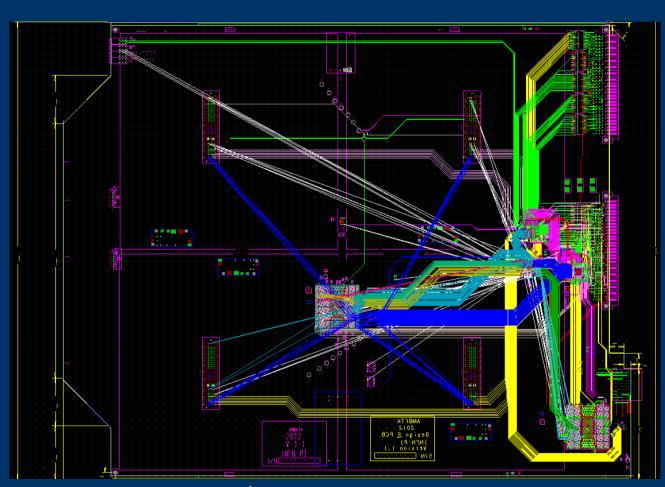

#### AMBSLP

#### Main new features:

• All data paths are differential serial link 2 Gbit/s.

• All clocks are differential LVDS.

• There are only 2 big FPGAs (Artix-7 1156 pads) for data distribution.

#### AMBSLP

#### Work plan:

- → April and May 2013: start schematic editing and routing.

- → Now: electronic group at CERN finalizing layout routing.

- → End of June 2013: submission of the board for production.

PCB layout at 21 June, 2013

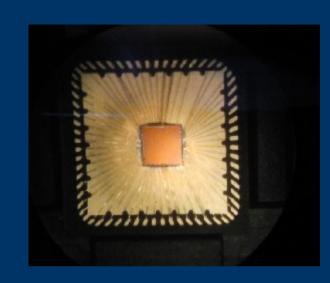

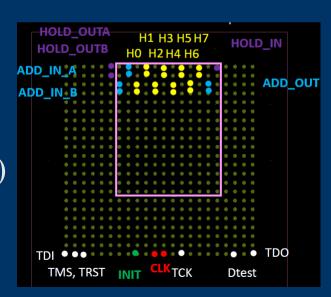

#### MiniLAMBSLP

#### Main features:

- A quarter of final LAMBSLP, with 4 chips.

- Designed for MiniASIC (little AMchip to test SerDes).

- Designed to test the MiniASIC and new data-path (LVDS serial fanout).

### **MiniLAMBSLP**

#### Work plan:

- → May and June 2013: design of schematic and routing.

- → Now: wait of

MiniASIC chip test

result (in Milan).

Then submission of

the board for

production.

Final PCB layout

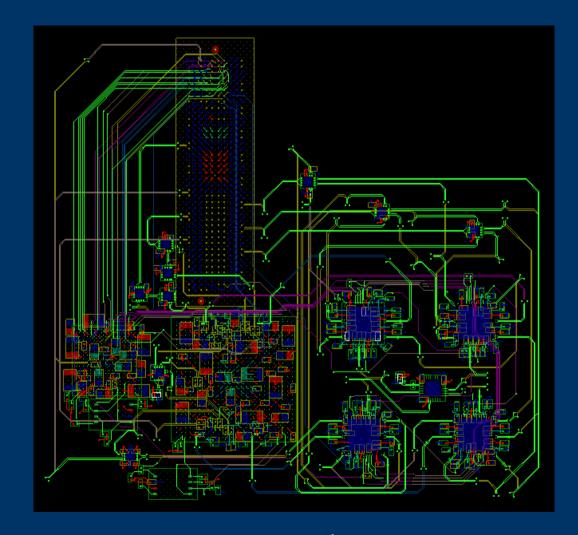

#### LAMBSLP

#### Main new features:

- All data paths are differential serial link 2 Gbit/s.

- New high speed and high power connector.

- Designed for AMChip05 (BGA 23mmx23mm)

#### LAMBSLP

#### Work plan:

- → June 2013: start the schematic editing and routing.

- → Now: work in progress on PCB-layout.

- → After the test of

MiniLAMBSLP (with

MiniAsic chip)

submission the board for

production.

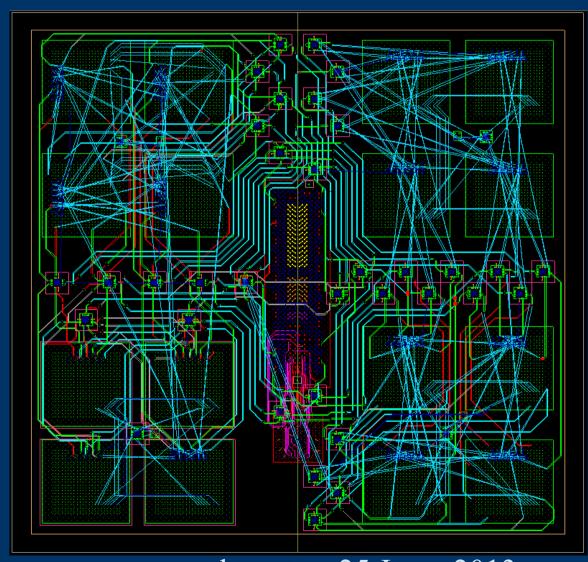

PCB layout at 25 June, 2013

# Next steps

→ End of June submission of AMBSLP.

→ In July mounting component on AMBSLP.

→ End of July send AMBSLP in Prisma Electronic for tests.

→ After test results on Amchip05 submission LAMBSLP.

### Conclusions

Satisfied about PCB design result

• Useful exchange of knowledge

• We are continuing the job with enthusiasm

# Thanks!