## Use of Associative Memories for tracker L1 triggering in LHC environment.

COMPact Muon Solenoid

CMS Upgrade Week: Tracking Trigger, May 21-25, 2012

<u>Leonello Servoli,</u> D. Magalotti

- This work has been carried out in the framework of an Italian National Research Project (PRIN).

- It is in collaboration with italian ATLAS groups who are implementing the FTK Vertical Slice project.

- It has been presented at: RT2012

IEEE2012 Conferenze, Berkeley, June 2012.

- Also at CMS Upgrade Week and WIT2012

Use of Tracker for L1 trigger is important at LHC-HL (you already know why...)

CMS Upgrade Week: Tracking Trigger

#### Track reconstruction and pattern matching

#### Pattern matching algorithm

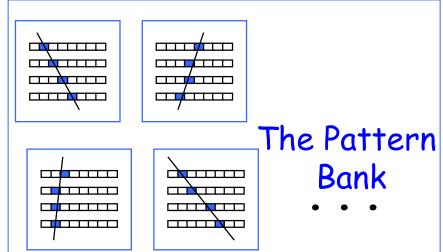

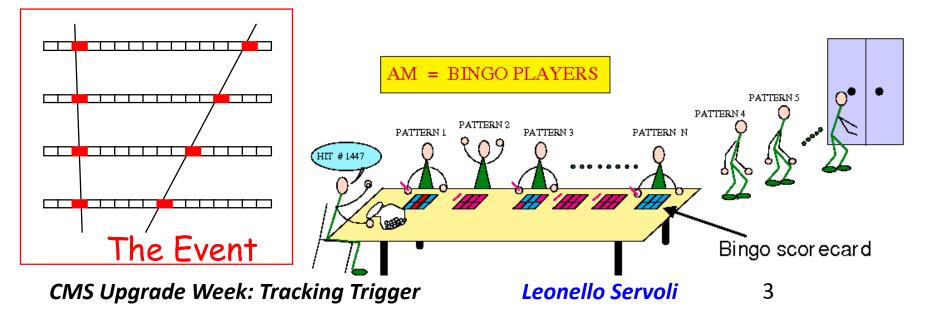

The pattern matching compares the event with ALL the candidates tracks stored in a local memory (Pattern Bank).

The pattern matching can be very fast for online track reconstruction thanks to the Associative Memory (AM) parallelism [see CDF use-case]

## Pattern Matching and Track Fitting

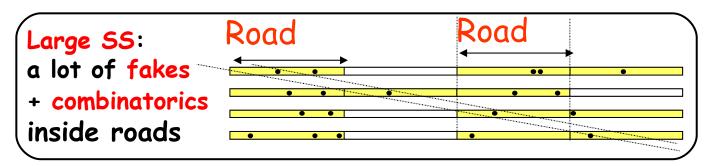

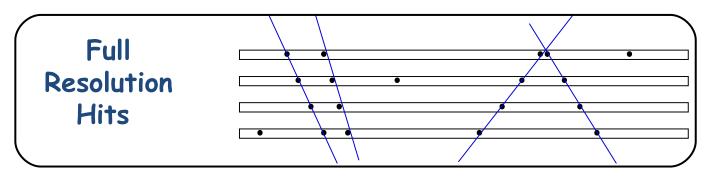

#### First Step: by AMBoard (large road size) → lower track resolution → less patterns

Second Step: by Auxiliary Board (small road size) → higher track resolution

CMS Upgrade Week: Tracking Trigger

# L2 trigger with AM

The Associative Memories can be used both at L1 and L2 trigger

L2: Lower input rate (100kHz), ordered events, longer latency (~25μsec for FTK)

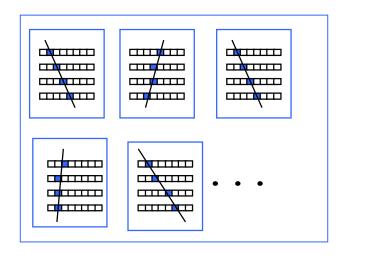

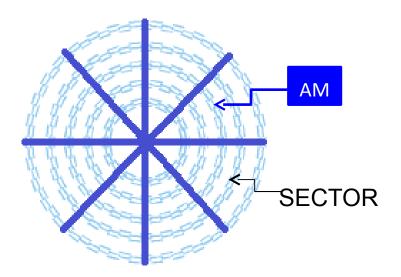

=> one big pattern bank to process 1 event at a time

5

1 sector => 1 bank = 1 logical unit => 1 (crate of) AM card(s)

CMS Upgrade Week: Tracking Trigger

## L2 trigger with AM

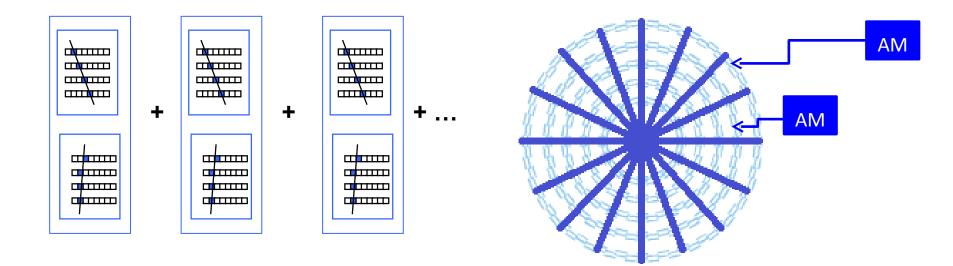

The longer latency could be used in at least two ways:

- To reduce the number of sectors maintaining the same track resolution (save AM Hardware) => big pattern banks

- 2) To maintain the same number of sectors with better track resolution (gain on fake rejection at low level) ==> big pattern banks

Or any linear combination....

CMS Upgrade Week: Tracking Trigger

## L1 trigger with AM

L1: High input rate (40MHz), mixed events, low latency (~6usec)

The shorter latency implies *an increased number of sectors* (*increased number of AM crates*) to process the events.

CMS Upgrade Week: Tracking Trigger

# L1 trigger with AM

**more sectors needed** to reduced the amount of hits to be processed by one AM card;

more sectors => smaller sectors => smaller number of patterns at same track resolution

smaller number of patterns are NEEDED to process in parallel by the same AM card several events coming from the same sector.

# R&D of Associative Memories HW and FW

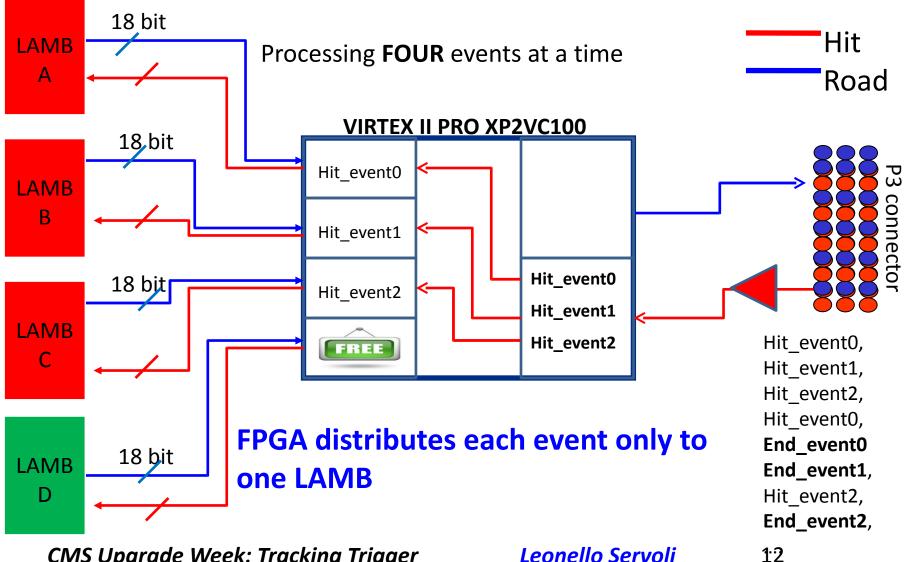

- 1) AMBSLIM firmware development

- Version of firmware of board that manage different event at the same time

- Timing measurement

- 2) AMBFTK

- Test of hardware

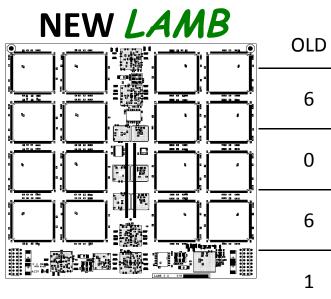

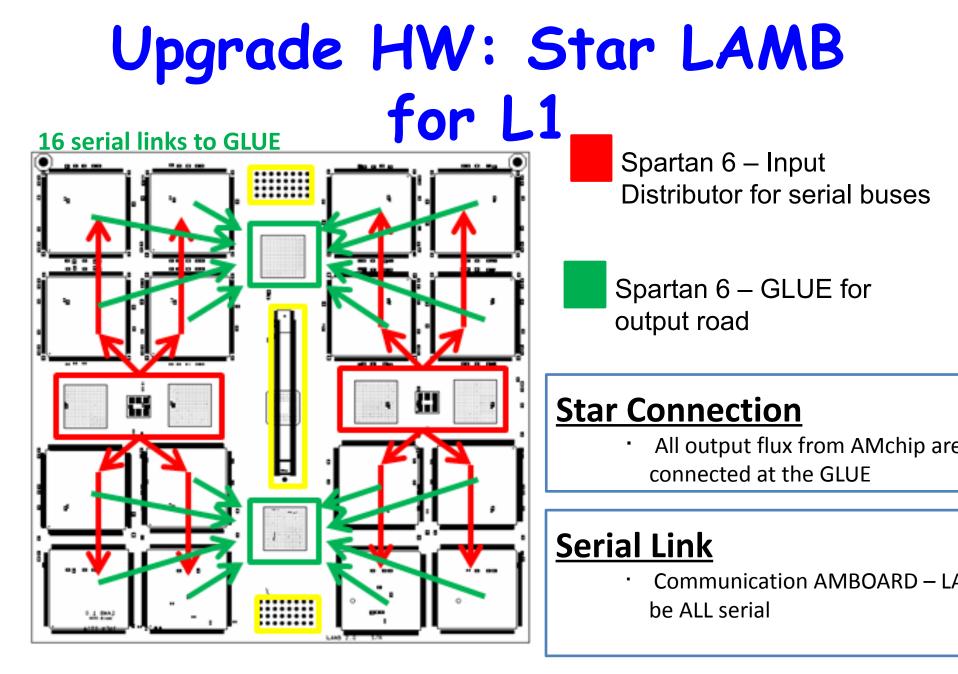

#### 3) New version of LAMB

CMS Upgrade Week: Tracking Trigger

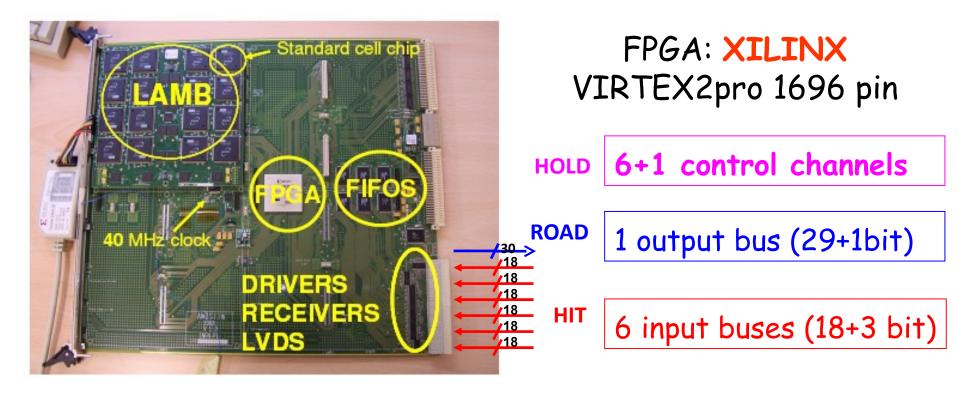

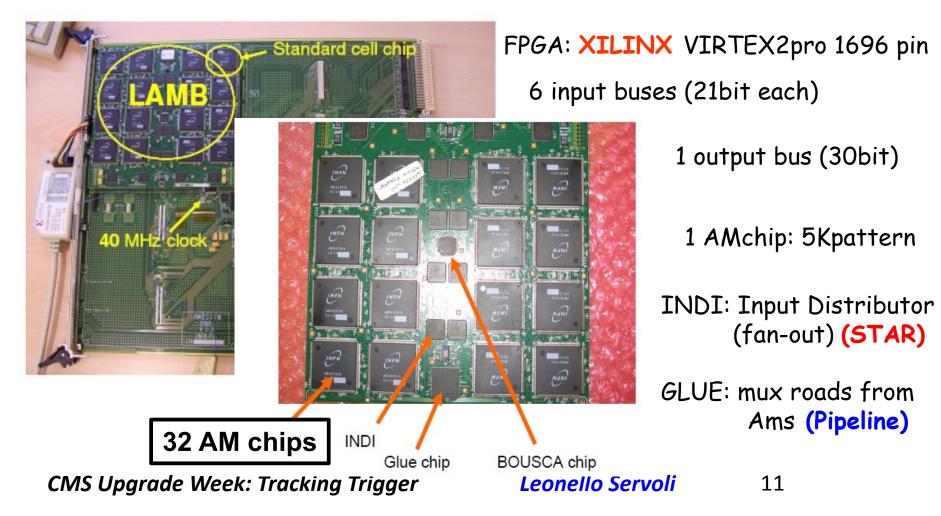

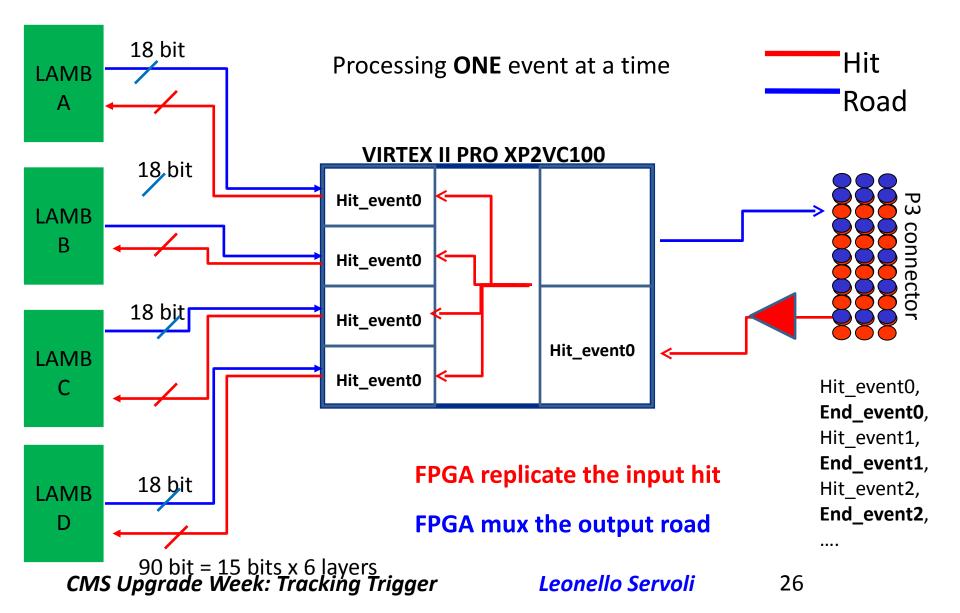

#### AMBSlim firmware development AMBSlim board

A single motherboard for L1 and L2 trigger applications (AMBSLIM, SLIM5 experiment) thanks to flexibility of the powerful control FPGA.

CMS Upgrade Week: Tracking Trigger

### AMBSlim firmware development: CDF LAMB

A single motherboard for L1 and L2 trigger applications (AMBSLIM, SLIM5 experiment) thanks to flexibility of the powerful control FPGA.

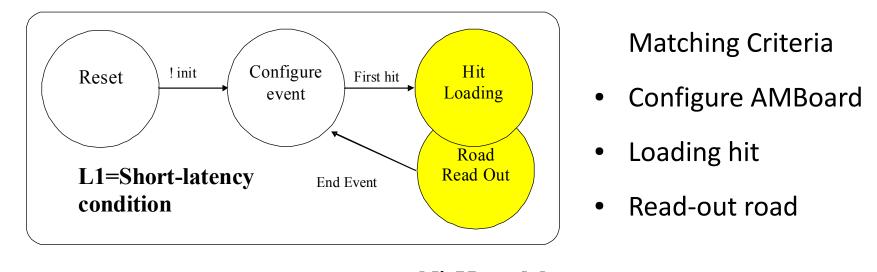

### AMBSIIM Logic Control for L1

CMS Upgrade Week: Tracking Trigger

### AMBSLIM firmware development Status:

- A first version of firmware is simulated

- ... it should be tested .

- The event processing time in the L1 trigger has to be measured.

### Existing hardware: AMBFTK

**NEW**

8

Δ

4

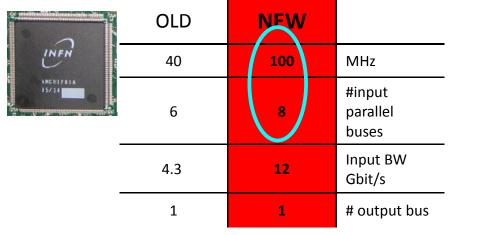

#### NEW AMCHIP

CMS Upgrade Week: Tracking Trigger

Leonello Servoli

14

NEW AMBOARD

AMBSIim 2010 V 2.0 INFN-PI

OLD

6

1

Ο.....

ien 2010 sign & PCB

**NEW**

12

16

О.

10 fam - 194 - 19

. 🖬 🛛 💿

#input

buses

# serial

link bus

link bus

# output

bus

# parallel

:=:\*\*

0

...

Ū

Ω

#input

# output

bus

bus

### Existing hardware: AMBFTK

- From P3 connector

- For the hit

- 12 bus → each bus 15 bit @ 100MHz → **18Gbps**

- For the road

- 16 bus → each bus 14 bit @ 100MHz → 22.4Gbps

- Number of pattern for each LAMB

- 80k pattern/chip → 2.56Mpattern/LAMB

- Indipendent link for the output road from LAMB

CMS Upgrade Week: Tracking Trigger

CMS Upgrade Week: Tracking Trigger

Leonello Servoli

16

### Consideration of event processing at L1: CMS Specification

- CMS specification

- Latency  $\rightarrow$  3usec

- Bunch Crossing  $\rightarrow$  40MHz

- N°hit/event/layer  $\rightarrow$  50

#### (accurate simulation needed)

CMS Upgrade Week: Tracking Trigger

#### Consideration of event processing at L1: First scenario

- Consider one AMBoard to process one event

- Input bandwidth AMBoard/layer = 1.5 Gbps

- Input bandwidth of event → 15 bit \* 50 hit \* 40MHz → 30 Gbps

- => BW AMBoard/BW event → 20 boards needed to manage the event

- Total number of patterns is:

32k/chip \* 128chip = 4M pattern /AMB

CMS Upgrade Week: Tracking Trigger

#### Consideration of event processing at L1: Second scenario

- Consider one LAMB for process one event

- Means 4 P3 one for each LAMB or the input frequency of AMBoard is 400MHz

- Input bandwidth AMBoard = 1.5 Gbps \* 4 = 6.0 Gbps

- Input bandwidth of event → 15 bit \* 50 hit \* 40MHz → 30 Gbps

- => BW AMBoard/BW event → 5 AMBoard are needed to process the event

- Total number of patterns is:

32k/chip \* 32chip/LAMB = 1M pattern /LAMB

CMS Upgrade Week: Tracking Trigger

Leonello Servoli

19

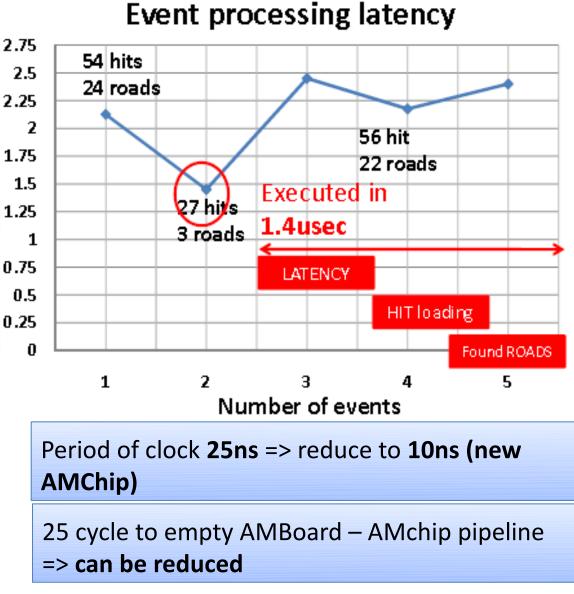

#### HOW to measure the event processing time

The measurement have to be performed in the L1 working condition

$T_{LATENCY} = DELAY \cdot P_{CLOCK} + \frac{N^{\circ}Hit\_Max}{layer} \cdot P_{CLOCK} + N^{\circ}Road \cdot P_{CLOCK}$

- Fixed DELAY

- Time to download hit into AMBoard

- Time to readout matched road

CMS Upgrade Week: Tracking Trigger

P<sub>CLOCK</sub> = 10nsec

## Conclusions

• The use of the Associative Memory for Tracker L2 trigger has already been proved by CDF. ATLAS is also currently implementing the FTK Vertical Slice.

Exploiting the existing HW it is possible to test some ideas about the AM use for L1 tracker trigger (new FW).

• We are working on some HW upgrade (new version of AM card) necessary to proceed further to assess the possibility of AM use for L1 tracker trigger in the CMS LHC-HL environment.

CMS Upgrade Week: Tracking Trigger

٠

### BACKUP

CMS Upgrade Week: Tracking Trigger

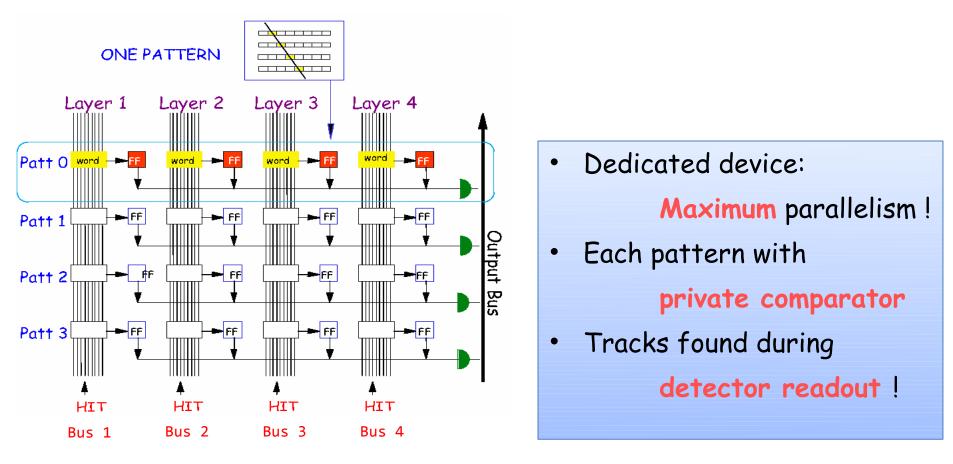

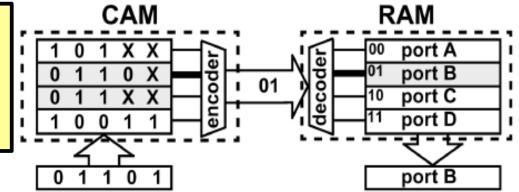

#### Associative Memory Architecture

HIT = detector channel fired by a particle

**ROAD** = fired patterns

CMS Upgrade Week: Tracking Trigger

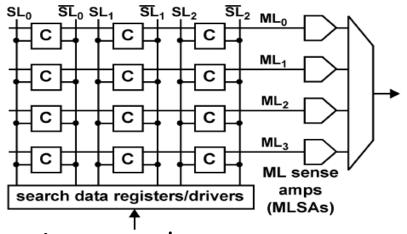

#### What are Associative Memories?

Associative Memories (AM) derive from the Content Addressable Memories (CAM)

Each cell C contains a bit. A column is a word.

All words are compared at the same time with an input word.

If one word matches the input word its address is transmitted as output.

CMS Upgrade Week: Tracking Trigger

#### Limitation of current LAMB for L1 trigger

CMS Upgrade Week: Tracking Trigger

## AMBoard Logic Control (L2)

#### How many patterns we could fit in modern FPGAs?

present: choice based on cost and package: 5SLX150T-4CSG484 (19x19 mm^2) 4 GTPs 296 pins (our package is LQFP208) 3 \$ today → 16400 AMchips → 6 M\$

23 k slices, even assuming ~8 slices/pattern →

~2.9 k patterns/FPGA <<< 80 kpat/(our Amchip: 12x12 mm^2 65 nm)</li>

The future http://www.xilinx.com/technology/roadmap/7-series-fpgas.htm Best Virtex 7 XC7V200T (new family not available now) **305 k slices → ~ 38 kpatterns/FPGA < 80 kpat/(our Amchip)**Using FFs: 2,443 Mff → ~120 FF/pattern → ~ 20,4 kpat/FPGA

Even using Slices and FFs together < 80 kpat/(our Amchip)</p>

Even choosing the **best device of next years** Even if we don't care about **cost and package** Even with very **optimistic hypothesis** on a difficult design

#### we don't get our AMchip power!

CMS Upgrade Week: Tracking Trigger

#### Logic density increases with time: Track Fitting possible @L1 in Phase II 2020? SVT: yesterday FTK: today All in the **AMchip**! All in a mezzanine! AMSequencer – Hit Buffer -It's possible to It's possible to multiply x 4 **Track Fitter** multiply x 128 **9U VME boards** = 3 AUX card DO+TF+HW Super Strip RAMS onnectors AM FPGA Roads SV TEHW **Corresponding Hits** DO Connectors input NPU Tracks + **Corresponding Hits LOW** Latency LOW cost

CMS Upgrade Week: Tracking Trigger

Leonello Servoli

28