# $\begin{array}{c} {\bf Super} B \ {\bf Detector} \\ {\bf Technical} \ {\bf Design} \ {\bf Report} \end{array}$

#### Abstract

This report describes the technical design detector for Super B.

### **Contents**

| 1 | Intro | oductio   |                                 |                                                                | 1   |

|---|-------|-----------|---------------------------------|----------------------------------------------------------------|-----|

|   | 1.1   |           | •                               |                                                                |     |

|   | 1.2   |           |                                 |                                                                |     |

|   | 1.3   | The De    | etector Design Progress Report  |                                                                | 2   |

| 2 | Acc   | elerator  | Overview                        |                                                                | Ę   |

| 3 | Det   | ector O   | verview                         |                                                                | 7   |

|   | 3.1   | Physics   | s Performance                   |                                                                | 7   |

|   | 3.2   | Challer   | nges on Detector Design         |                                                                | 1(  |

|   | 3.3   | -         |                                 |                                                                |     |

|   | 3.4   | Detecto   | or R&D                          |                                                                | L2  |

| 4 | Phy   | sics witl | h SuperB                        | 1                                                              | L 7 |

| 5 | Mad   | chine De  | etector Interface and Backgroun | nds 1                                                          | Į   |

| 6 | Silic | on Vert   | ex Tracker                      | 2                                                              | 21  |

| • | 6.1   |           | Detector Overview               | G.Rizzo - 12 pages                                             |     |

|   |       | 6.1.1     | SVT and Layer0                  |                                                                |     |

|   |       | 6.1.2     | Requirements                    |                                                                | 22  |

|   |       | 6.1.3     | Baseline Detector Concept       |                                                                | 22  |

|   |       |           |                                 |                                                                |     |

|   |       |           |                                 |                                                                |     |

|   |       |           |                                 |                                                                |     |

|   |       |           |                                 |                                                                |     |

|   |       | 6.1.4     |                                 |                                                                |     |

|   |       |           |                                 |                                                                |     |

|   |       |           | <del>_</del>                    |                                                                |     |

|   |       | C 1 F     |                                 | d Cooling                                                      |     |

|   | 6.2   |           |                                 | D. Consi. A name                                               |     |

|   | 6.2   | Backgr    | ounds<br>or Performance Studies | R.Cenci - 4 pages                                              |     |

|   | 0.5   |           |                                 | N.Neff - 0 pages                                               |     |

|   |       | 6.3.2     |                                 | $(about \ 2 \ pages) \ \dots \ \dots \ (2 \ pages)$            |     |

|   |       | 6.3.2     |                                 | $a$ and $a$ analyses $(about \ 2 \ pages) \ \dots \ \dots \ 2$ |     |

|   |       | 6.3.4     |                                 |                                                                | 24  |

|   |       | 6.3.5     |                                 | 2 pages)                                                       |     |

|   | 6.4   |           | Sensors                         | L. Bosisio - 8 pages                                           |     |

|   |       | 6.4.1     |                                 | 1 0                                                            | 24  |

|   |       |           | C 4 1 1 F.C:                    |                                                                |     |

|     |        | 6.4.1.2    | Resolution                   |                                | 25 |

|-----|--------|------------|------------------------------|--------------------------------|----|

|     |        | 6.4.1.3    | Radiation hardness           |                                | 25 |

|     | 6.4.2  | Sensor d   | $esign \dots \dots$          |                                | 25 |

|     |        | 6.4.2.1    | Technology choice            |                                | 27 |

|     |        | 6.4.2.2    | Optimization of strip layout |                                | 27 |

|     |        | 6.4.2.3    |                              |                                | 27 |

|     | 6.4.3  | Prototyp   |                              |                                | 27 |

| 6.5 | Fanou  | t Circuits |                              |                                | 27 |

|     | 6.5.1  |            | for layer0                   |                                | 27 |

|     |        | 6.5.1.1    |                              |                                | 27 |

|     |        | 6.5.1.2    | Technology                   |                                | 27 |

|     |        | 6.5.1.3    | 30                           |                                | 27 |

|     |        | 6.5.1.4    |                              |                                | 27 |

|     | 6.5.2  | Fanouts    | ·                            |                                | 27 |

|     |        | 6.5.2.1    | · ·                          |                                | 27 |

|     |        | 6.5.2.2    |                              | hnique                         | 27 |

|     |        | 6.5.2.3    |                              |                                | 28 |

|     |        | 6.5.2.4    |                              |                                | 29 |

| 6.6 | Electr | onics Reac |                              |                                | 29 |

|     | 6.6.1  | Readout    |                              | V.Re - 10                      | 29 |

|     |        | 6.6.1.1    | *                            | and Striplet Detectors         | 29 |

|     |        | 6.6.1.2    | -                            |                                | 30 |

|     |        | 6.6.1.3    |                              | on                             | 33 |

|     |        | 6.6.1.4    |                              |                                | 34 |

|     | 6.6.2  | Hybrid I   |                              |                                | 34 |

|     | 6.6.3  |            | ansmission                   |                                | 34 |

|     | 6.6.4  | Power St   | upply                        | - 2                            | 34 |

| 6.7 | Mecha  |            |                              |                                | 34 |

|     | 6.7.1  |            | _                            | ,                              | 34 |

|     | 6.7.2  |            |                              |                                | 34 |

|     | 6.7.3  |            | · ·                          |                                | 34 |

|     |        | 6.7.3.1    | Half Detector Assembly       |                                | 34 |

|     |        | 6.7.3.2    |                              | d L 1-5 on the W Shielding     |    |

|     |        | 6.7.3.3    | Installation of Complete Ass | embly into the SuperB Detector | 35 |

|     |        | 6.7.3.4    | Quick Demounting             |                                | 35 |

|     | 6.7.4  | Detector   | Placement and Survey         |                                | 35 |

|     |        | 6.7.4.1    | Placement accuracy           |                                | 35 |

|     |        | 6.7.4.2    | Survey with tracks           |                                | 35 |

|     | 6.7.5  | Detector   | Monitoring                   |                                | 35 |

|     |        | 6.7.5.1    | Position Monitoring System   |                                | 35 |

|     |        | 6.7.5.2    | Radiation Monitoring         |                                | 35 |

|     | 6.7.6  | R&D Pr     | ogram                        |                                | 35 |

|     |        | 6.7.6.1    | Cables                       |                                | 35 |

|     |        | 6.7.6.2    | hybrid                       |                                | 35 |

|     |        | 6.7.6.3    | Inner layer sextant          |                                | 35 |

|     |        | 6.7.6.4    | Arch modules                 |                                | 35 |

|     |        | 6.7.6.5    | Cones and space frame        |                                | 35 |

|     |        |            |                              |                                |    |

|     |               | 6.7.6.6 Full-scale model of IR   |                                                    |

|-----|---------------|----------------------------------|----------------------------------------------------|

| 6.8 | Layer0        | Upgrade Options                  | G.Rizzo/L.Ratti - 10 pages                         |

|     | 6.8.1         |                                  |                                                    |

|     |               | 6.8.1.1 Hybrid pixels            |                                                    |

|     |               |                                  | onolithic sensors                                  |

|     |               |                                  | MOS quadruple well technology                      |

|     | 6.8.2         | R&D activity                     |                                                    |

|     |               | 6.8.2.1 Front-end electronics f  | for hybrid pixels in planar and 3D CMOS            |

|     |               | $technology \dots \dots$         |                                                    |

|     |               | 6.8.2.2 The Apsel DNW MAP        | S series                                           |

|     |               | 6.8.2.3 The Apsel4well quadru    | ple well monolithic sensor                         |

|     | 6.8.3         | Radiation tolerance              |                                                    |

| 6.9 | Service       | s, Utilities and E.S. & H issues | - 8 pages                                          |

|     | 6.9.1         | Service and Utilities            |                                                    |

|     | 6.9.2         | ES&H Issue                       |                                                    |

| D:  | t Cham        | hau Einaa                        | sebiore Doney 60 norses                            |

| 7.1 | Overvi        |                                  | cchiaro, Roney 60 pages<br>cchiaro, Roney 12 pages |

| 1.1 | 7.1.1         | Physics requirements             | cchiaro, Roney 12 pages                            |

|     | 7.1.1 $7.1.2$ | Geometrical constraints          | - 1 page                                           |

|     | 7.1.2         | Machine background consideration |                                                    |

|     | 7.1.3 $7.1.4$ | DCH design overview              | - 2 pages                                          |

|     | 7.1.5         | Expected performance             | - 2 pages                                          |

|     | 7.1.6         | Tracking software and pattern re |                                                    |

| 7.2 |               |                                  | Finocchiaro, Hearty, Piccolo, Roney 9 pages.       |

|     | 7.2.1         |                                  |                                                    |

|     | 7.2.2         |                                  |                                                    |

|     |               | <del>-</del>                     | onsiderations                                      |

|     |               | š -                              | as gain                                            |

|     | 7.2.3         |                                  |                                                    |

| 7.3 | Mecha         |                                  | Cinocchiaro, Lauciani 9 pages                      |

|     | 7.3.1         |                                  |                                                    |

|     | 7.3.2         |                                  |                                                    |

|     | 7.3.3         |                                  |                                                    |

|     | 7.3.4         | •                                |                                                    |

|     | 7.3.5         | Choice of wire and electrostatic | stability                                          |

|     | 7.3.6         |                                  |                                                    |

|     | 7.3.7         | Endplate system                  |                                                    |

|     |               | 7.3.7.1 Supports for on-detector | or boards                                          |

|     |               | 7.3.7.2 Cooling                  |                                                    |

|     |               | 7.3.7.3 Shielding                |                                                    |

|     | 7.3.8         | Stringing                        |                                                    |

| 7.4 | Electro       | onics - Fe                       | elici, Martin 12 pages                             |

|     | 7.4.1         | Design Goals                     |                                                    |

|     |               | 7.4.1.1 Specifications for charg | ge measurements                                    |

|     |               | 7.4.1.2 Specifications for time  | measurements                                       |

|     | 74.2          | DCH Front-end system (block di   | iagram)                                            |

|       |                                       | ${ m ath}$                              |  |

|-------|---------------------------------------|-----------------------------------------|--|

|       |                                       |                                         |  |

|       |                                       |                                         |  |

| 7.5   | High Voltage system                   | - Martin 1 page                         |  |

|       |                                       |                                         |  |

|       |                                       |                                         |  |

| 7.6   | Gas system                            | - Roney 2 pages                         |  |

| 7.7   | Calibration and monitoring            | - Roney 3 pages                         |  |

|       | · · · · · · · · · · · · · · · · · · · |                                         |  |

|       |                                       |                                         |  |

|       | 9 •                                   | em                                      |  |

|       | 7.7.0.4 On-line monitor               |                                         |  |

| 7.8   | Integration -                         | Hearty, Lauciani 6 pages                |  |

|       | 7.8.1 Overall geometry and mechan     | ical support                            |  |

|       | 7.8.2 Cable supports and routing .    |                                         |  |

|       | 7.8.3 Access                          |                                         |  |

|       | 7.8.4 Gas system                      |                                         |  |

|       | 7.8.5 Off-detector electronics crates |                                         |  |

|       | 7.8.6 High voltage crates             |                                         |  |

|       | 7.8.7 Installation and alignment      |                                         |  |

| 7.9   | R&D Program -                         | Finocchiaro, Piccolo 6 pages            |  |

|       | 7.9.1 Results                         |                                         |  |

|       | 7.9.2 Plans                           |                                         |  |

| B Par | ticle Identification                  |                                         |  |

| 8.1   |                                       | nd Detector Performance goals 3-4 pages |  |

| 0.1   |                                       | nati, Maryland                          |  |

|       |                                       |                                         |  |

|       | -                                     | n                                       |  |

| 8.2   | $\mathbf{e}$                          | pages                                   |  |

| 0.2   |                                       |                                         |  |

|       |                                       | FDIRC)                                  |  |

| 8.3   | · · · · · · · · · · · · · · · · · · · | 3 pages                                 |  |

| 0.0   |                                       | ho pages                                |  |

|       |                                       |                                         |  |

|       |                                       | Canci Varma Vararahanka                 |  |

| 0.4   | •                                     | ormance Cenci, Vavra, Kravchenko        |  |

| 8.4   |                                       | w 5-10 pages                            |  |

|       | -                                     | nettoni, Simi, Vavra                    |  |

|       |                                       |                                         |  |

|       |                                       |                                         |  |

|       | <del>_</del>                          | pages                                   |  |

|       | 8.4.5 Mechanical support              |                                         |  |

|   |      | 8.4.6         | Electronics readout, HV and LV 5-6 pages                      |

|---|------|---------------|---------------------------------------------------------------|

|   |      | 8.4.7         | Integration issues 2 pages                                    |

|   |      | 8.4.8         | DAQ and computing 1 page                                      |

|   |      | 8.4.9         | FDIRC R&D Results until now 2-3 pages                         |

|   |      | 8.4.10        | Ongoing FDIRC R&D 1-2 pages                                   |

|   |      | 8.4.11        | System Responsibilities and Management 1-2 pages 62           |

|   |      | 8.4.12        | Cost, Schedule and Funding Profile 1-2 pages 62               |

|   | 8.5  | Forwa         | ard option 4-5 pages                                          |

|   |      | 8.5.1         | Physics motivation Arnaud, Stocchi                            |

|   |      | 8.5.2         | Outline of FTOF detector technology Arnaud, Stocchi, Vavra 62 |

|   |      | 8.5.3         | Committee recommendation Hassan                               |

|   |      | 8.5.4         | Motivation for a Forward PID Detector                         |

|   |      | 8.5.5         | Forward PID Requirements                                      |

|   |      | 8.5.6         | Status of the Forward PID R&D Effort 63                       |

| 9 | Flor |               | netic Calorimeter 67                                          |

| 9 | 9.1  | _             | <b>inetic Calorimeter 67 68</b>                               |

|   | 9.1  | 9.1.1         | Background and radiation issues                               |

|   |      | 9.1.1 $9.1.2$ | Simulation tools                                              |

|   |      | 9.1.2         | 9.1.2.1 Fastsim                                               |

|   |      |               | 9.1.2.1 Fasishi                                               |

|   | 9.2  | Rarrel        | Calorimeter                                                   |

|   | 5.2  | 9.2.1         | Requirements Relevant to the SuperB Environment               |

|   |      | 0.2.1         | 9.2.1.1 Crystal Aging at BABAR                                |

|   |      |               | 9.2.1.2 Backgrounds                                           |

|   |      | 9.2.2         | Description of BABAR Barrel Calorimeter                       |

|   |      | 0.2.2         | 9.2.2.1 Mechanical design                                     |

|   |      |               | 9.2.2.2 Readout                                               |

|   |      |               | 9.2.2.3 Calibration                                           |

|   |      | 9.2.3         | Performance of BABAR barrel                                   |

|   |      |               | 9.2.3.1 Energy and position resolution                        |

|   |      |               | 9.2.3.2 Gamma-gamma mass resolution                           |

|   |      |               | 9.2.3.3 Radiation Damage Effects on Resolution                |

|   |      |               | 9.2.3.4 Expected Changes in Performance at Super $B$          |

|   |      | 9.2.4         | Electronics changes                                           |

|   |      |               | 9.2.4.1 Rationale for changes                                 |

|   |      |               | 9.2.4.2 Premp design                                          |

|   |      |               | 9.2.4.3 Shaping and digitization                              |

|   |      |               | 9.2.4.4 Cabling                                               |

|   |      | 9.2.5         | SLAC De-installation, Transport and Local Storage             |

|   |      | 9.2.6         | Electronics refurbishment                                     |

|   |      | 9.2.7         | Calibration systems                                           |

|   |      | 9.2.8         | Re-installation at Tor Vergata                                |

|   | 9.3  |               | rd Calorimeter                                                |

|   |      | 9.3.1         | Requirements[RF]                                              |

|   |      | 9.3.2         | LYSO Crystals[RZ]                                             |

|   |      |               | 9.3.2.1 Light output                                          |

|     |       | 9.3.2.2  | Radiation hardness                                                                                                                          | 0 |

|-----|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|---|

|     |       | 9.3.2.3  | Timing                                                                                                                                      | 0 |

|     |       | 9.3.2.4  | Uniformity                                                                                                                                  | 0 |

|     |       | 9.3.2.5  | Manufacturing                                                                                                                               | 0 |

|     | 9.3.3 | Readout  | and Electronics[VB]                                                                                                                         | 0 |

|     |       | 9.3.3.1  | APD Readout[DH]                                                                                                                             | 0 |

|     |       | 9.3.3.2  | Electronics Block diagram                                                                                                                   | 0 |

|     |       | 9.3.3.3  | Preamplifier                                                                                                                                | 0 |

|     |       | 9.3.3.4  | Shaper                                                                                                                                      | 0 |

|     |       | 9.3.3.5  | Digitization                                                                                                                                | 0 |

|     |       | 9.3.3.6  | Requirements on mechanics                                                                                                                   | 0 |

|     | 9.3.4 | Calibrat |                                                                                                                                             | 1 |

|     |       | 9.3.4.1  | Initial calibration with source                                                                                                             | 1 |

|     |       | 9.3.4.2  | 6 MeV calibration system                                                                                                                    | 1 |

|     |       | 9.3.4.3  | Electronics calibration                                                                                                                     | 1 |

|     |       | 9.3.4.4  | Temperature monitoring and correction                                                                                                       | 1 |

|     | 9.3.5 | Mechani  | $cal \ Design[CG]  \dots  \dots  7$                                                                                                         | 1 |

|     |       | 9.3.5.1  | Mechanical support                                                                                                                          | 1 |

|     |       | 9.3.5.2  | Services                                                                                                                                    | 1 |

|     |       | 9.3.5.3  | Installation                                                                                                                                | 1 |

|     | 9.3.6 | Performa | ance in simulations[SG] $\dots \dots \dots$ | 1 |

|     |       | 9.3.6.1  | Resolution studies                                                                                                                          | 1 |

|     |       | 9.3.6.2  | Background studies                                                                                                                          | 1 |

|     | 9.3.7 | Tests on | Beam[CC]                                                                                                                                    | 1 |

|     |       | 9.3.7.1  | Description of apparatus                                                                                                                    | 1 |

|     |       | 9.3.7.2  | Electronics noise measurements                                                                                                              | 1 |

|     |       | 9.3.7.3  | Description of beam                                                                                                                         | 4 |

|     |       | 9.3.7.4  | Description of data                                                                                                                         | 5 |

|     |       | 9.3.7.5  | Calibration                                                                                                                                 | 5 |

|     |       | 9.3.7.6  | Data-MC comparison                                                                                                                          | 5 |

|     |       | 9.3.7.7  | Temperature corrections                                                                                                                     | 7 |

|     |       | 9.3.7.8  | Algorithms and results                                                                                                                      | 7 |

|     | 9.3.8 | Alternat | ives                                                                                                                                        | 7 |

|     |       | 9.3.8.1  | Alternative 1                                                                                                                               | 7 |

|     |       | 9.3.8.2  | Comparison with baseline                                                                                                                    | 7 |

| 9.4 | Backw |          | imeter                                                                                                                                      |   |

|     | 9.4.1 | -        | nents                                                                                                                                       |   |

|     |       | 9.4.1.1  | Energy and angular resolution                                                                                                               |   |

|     |       | 9.4.1.2  | Radiation hardness                                                                                                                          | 9 |

|     |       | 9.4.1.3  | Background rates                                                                                                                            | 9 |

|     |       | 9.4.1.4  | Solid angle, transition to barrel                                                                                                           | 9 |

|     | 9.4.2 | Mechani  | $\operatorname{cal design}  \dots  \dots  \dots  \dots  \qquad 7$                                                                           | 9 |

|     |       | 9.4.2.1  | Calorimeter construction                                                                                                                    | 9 |

|     |       | 9.4.2.2  | Support and services                                                                                                                        |   |

|     | 9.4.3 | ,        | PPC readout                                                                                                                                 | 9 |

|     | 9.4.4 |          | ics                                                                                                                                         | 9 |

|     | 9.4.5 | Calibrat | ion                                                                                                                                         | 9 |

| 13 Elec |                                     | 1 <b>5</b><br>15 |

|---------|-------------------------------------|------------------|

| 11 Mag  | gnet and Flux Return                | 99               |

|         | 10.5.1 Flux Return                  | 90               |

| 10.3    |                                     | 95<br>95         |

| 400     |                                     | 94               |

|         |                                     | 93               |

| 10.2    |                                     | 93               |

|         | <u> </u>                            | 92               |

|         | 10.1.2 Baseline Design Requirements | 92               |

|         |                                     | 91               |

| 10.1    |                                     | 91               |

| 10 Inst | rumented Flux Return                | 91               |

|         | 9.11.3 Backward Calorimeter         | 87               |

|         |                                     | 87<br>0 <b>7</b> |

|         |                                     | 86               |

| 9.11    |                                     | 86               |

|         | *                                   | 84               |

|         |                                     | 83               |

|         |                                     | 83               |

|         | v                                   | 83               |

|         | 9.9.1 Mechanical Structure          | 82               |

| 9.9     | Forward Endcap Calorimeter          | 82               |

| 9.8     |                                     | 81               |

|         | 9.7.4 Cost and schedule risks       | 80               |

|         | 9.7.3 Basis of estimates            | 80               |

|         | 9.7.2 Gantt chart                   | 80               |

|         | 9.7.1 WBS structure                 | 80               |

| 9.7     |                                     | 80               |

|         |                                     | 80               |

|         |                                     | 80               |

|         |                                     | 80               |

|         |                                     | 80               |

| 5.0     |                                     | 80               |

| 9.6     | 00 1                                | 80               |

|         |                                     | 80<br>80         |

|         |                                     | 80               |

|         |                                     | 80               |

| 9.5     |                                     | 79               |

|         |                                     | 79<br>           |

|         | *                                   | 79               |

|         | 9.4.7 Performance in simulations    | 79               |

|         | 9.4.6 Backward simulation           | 79               |

|    | 13.2  | Common components                                                         |  |

|----|-------|---------------------------------------------------------------------------|--|

|    |       | 13.2.1 Clock, Control and Data Links                                      |  |

|    |       | 13.2.2 FCTS Links                                                         |  |

|    |       | 13.2.3 Data Links                                                         |  |

|    |       | 13.2.4 Common Front-End Electronics                                       |  |

|    |       | 13.2.5 Power supplies (?)                                                 |  |

|    |       | 13.2.6 Cable Plant (?)                                                    |  |

|    | 13.3  | Subsystem-specific Electronics                                            |  |

|    |       | 13.3.1 SVT Electronics                                                    |  |

|    |       | 13.3.2 DCH Electronics                                                    |  |

|    |       | 13.3.3 PID Electronics                                                    |  |

|    |       | 13.3.4 EMC Electronics                                                    |  |

|    |       | 13.3.5 IFR Electronics                                                    |  |

|    |       | 13.3.6 Level-1 Trigger Electronics                                        |  |

| 14 | Soft  | ware and Computing 123                                                    |  |

|    |       | The Super $B$ baseline model                                              |  |

|    |       | 14.1.1 The requirements                                                   |  |

|    |       | 14.1.2 Super $B$ offline computing development                            |  |

|    | 14.2  | Computing tools and services for the Detector and Physics TDR studies 125 |  |

|    |       | 14.2.1 Fast simulation                                                    |  |

|    |       | 14.2.2 Bruno: the Super $B$ full simulation tool                          |  |

|    |       | 14.2.3 The distributed production environment                             |  |

|    |       | 14.2.4 The software development and collaborative tools                   |  |

|    |       | 14.2.5 Code packaging and distribution                                    |  |

| 15 | Envi  | ronmental Safety and Health 137                                           |  |

| 16 | Facil | lities, Mechanical Integration and Assembly 139                           |  |

| 10 |       | Introduction                                                              |  |

|    | 10.1  | 16.1.1 Magnet and Instrumented Flux Return                                |  |

|    | 16.2  | Component Extraction                                                      |  |

|    |       | Component Transport                                                       |  |

|    |       | Detector Assembly                                                         |  |

| 17 | Proj  | ect Management 143                                                        |  |

| 18 | Cost  | and Schedule 145                                                          |  |

|    | 18.1  | Detector Costs                                                            |  |

|    | 18.2  | Basis of Estimate                                                         |  |

|    | 10 9  | Cabadula 151                                                              |  |

#### 6 Silicon Vertex Tracker

#### 6.1 Vertex Detector Overview

G.Rizzo - 12 pages

The Silicon Vertex Tracker, as in BABAR, together with the drift chamber (DCH) and the solenoidal magnet provide track and vertex reconstruction capability for the Super B detector. Precise vertex information, primarily extracted from precise position measurements near the IP by the SVT, is crucial to the measurement of time-dependent CP asymmetries in  $B^0$  decays, which remains a key element of the Super B physics program. In addition, charged particles with transverse momenta lower than  $100 \, \mathrm{MeV}/c$  will not reach the central tracking chamber, so for these particles the SVT must provide the complete tracking information.

#### 6.1.1 SVT and Layer0

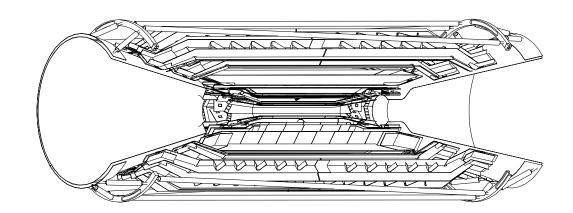

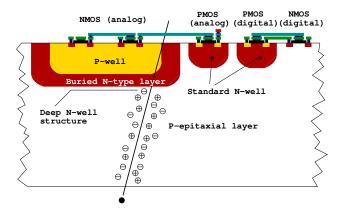

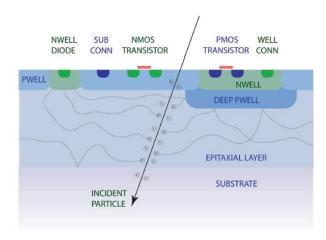

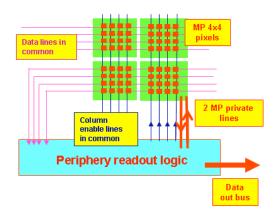

These goals have been reached in the BABAR detector with a five-layer silicon strip detector. The BABAR SVT provided excellent performance for the whole life of the experiment, thanks to a robust design that took into account the physics requirements as well as enough safety margin, to cope with the machine background, and redundancy considerations. The SuperBSVT design is based on the BABAR vertex detector layout with the addition of an innermost layer closer to the IP (Layer0) as shown the in Fig. 6.3. The Layer0 close-in position measurements lead to an improved vertex resolution, which is expected to largely compensate for the reduced boost at the SuperB, thus retaining the  $\Delta t$  resolution for B decays achieved in BABAR. Physics studies and background conditions, as explained in detail in the next sections, set stringent requirements on the Layer design: radius of about 1.5 cm; high granularity ( $50 \times 50 \,\mu\text{m}^2$  pitch); low material budget (about 1%  $X_0$ ); and adequate radiation resistance.

Several options are under study for the Layer0 technology, with different levels of maturity, expected performance and safety margin against background conditions. These include striplets modules based on high resistivity sensors with short strips, hybrid pixels and other thin pixel sensors based on CMOS Monolithic Active Pixel Sensor (MAPS).

The current baseline configuration of the SVT Layer is based on the striplets technology, which has been shown to provide the better physics performance, as detailed in the next sections. However, options based on pixel sensors, which are more robust in high background conditions, are still being developed with specific R&D programs in order to meet the Layer0 requirements, which include low pitch and material budget, high readout speed and radiation hardness. If successful, this will allow the replacement of the Layer0 striplets modules in a "second phase" of the experiment. For this purpose the SuperB interaction region and the SVT mechanics will be designed to ensure rapid access to the detector for fast replacement of Layer0.

The external SVT layers (1-5), with a radius between 3 and 15 cm, will be built with the same technology used for the BABAR SVT (double sided silicon strip sensor), which is adequate for the machine background conditions expected in the SuperB accelerator scheme (i.e. with low beam currents).

The SVT angular acceptance, constrained by the interaction region design, will be 300 mrad in both the forward and backward directions, corresponding to a solid angle coverage of 95% in the center-of-mass frame.

$\downarrow$

Figure 6.1: Three dimensional cutaway of the SVT.

- 6.1.2 Requirements

- 6.1.3 Baseline Detector Concept

- 6.1.3.1 Technology

- 6.1.3.2 Layout

- 6.1.3.3 Electronics

- 6.1.3.4 Mechanical Support

- 6.1.4 Layer Pixel Upgrade

- 6.1.4.1 Technology Options

- 6.1.4.2 Pixel Module Design

- 6.1.4.3 Mechanical Support and Cooling

- 6.1.5 R&D Main Activities

- 6.2 Backgrounds R.Cenci 4

pages

- 6.3 Detector Performance

Studies N.Neri 6 pages

#### **6.3.1 Introduction** (about 1/2 page)

• write some considerations about the main differences between BaBar and SuperB (i.e. luminosity, boost, beampipe, beamspot);

- describe the main idea behind the new detector design focusing on performances;

- cite BaBar TDR and BaBar NIM paper as reference for strip detectors.

# **6.3.2** Impact of Layer0 on detector performances (about 2 pages)

- definition of Layer0 requirements for physics (material budget, inner radius vs boost, outer radius, intrinsic resolution, coverage);

- $B^0$  decay and tag vertex and  $B^0$  proper time resolution for different solutions;

- baseline solution performances;

- discussion of pro and cons.

# **6.3.3 Sensitivity studies for time-dependent analyses** (about 2 pages)

- studies of benchmark channels  $B^0 \to \phi K_S^0$ ,  $B^0 \to \pi^+\pi^-$ , etc.;

- include time-dependent sensitivity studies at charm threshold?

- impact of background on detector performances.

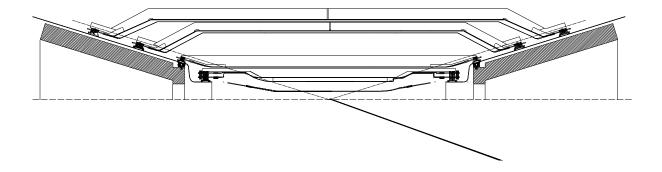

Figure 6.2: Cross section of the SVT in the plane containing the beam axis.

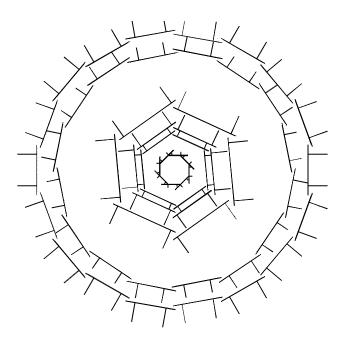

Figure 6.3: Cross section of the SVT in the plane perpendicular to the beam axis. The lines perpendicular to the detectors represent structural support beams.

# **6.3.4 Vertexing and Tracking performances** (about 1 pages)

- track parameter resolutions;

- considerations for pattern recognition, efficiency vs numbers of layers, reconstruction capabilities for low momentum tracks,  $K_S^0$ reconstruction.

# **6.3.5 Particle Identification** (about 1/2 pages)

- dE/dx resolution and relevance for QED pairs suppression.

- discussion of relevance of ToT information and number of bits of the FEE.

# 6.4 Silicon Sensors L. Bosisio - 8 pages

(Striplets will be discussed together with the other sensors)

Layers 1 to 5 of the SVT will be based on 300  $\mu$ m thick double-sided silicon strip detectors, with integrated AC-coupling capacitors and polysilicon bias resistors. These devices are a technically mature and conservative solution to the requirements the SVT must meet to provide precise, highly segmented tracking near the interaction point. For the new layer 0, the baseline option also foresees double-sided silicon strip detectors, but with a thickness reduced to 200  $\mu$ m. The detailed requirements which the detectors must meet are discussed below.

#### 6.4.1 Requirements

To achieve good vertex resolution, it is especially important to minimize the material up to and including the first measurement. This requirement, and the need to provide precise vertexing in both z and  $\phi$ , leads to the choice of double-sided detectors. Given the increased module length with respect to the BaBar SVT, in order to minimize the number of sensors required, the complexity of the assembly and the insensitive area between adjacent sensors and to

ease the alignment task, we foresee to have the sensors fabricated on 150 mm diameter wafers, which is by now a widely available option from sensor suppliers. For layers 1 to 5 we plan to use 300  $\mu$ m-thick silicon wafers, which are a standard choice and present acceptable handling properties. For layer 0, given the very stringent limitations on the amount of material we will be forced to go to 200  $\mu$ m thick silicon. Processing double sided sensors on thin, 150 mm wafers is a significant challenge, which very few manufacturers are willing to tackle. Unfortunately, while the other layers could also be assembled from smaller sensors, fabricated on 100 mm wafers, layer 0 sensors do not fit in 100 mm wafers. This is due to the requirement to have only one sensor per layer 0 module, which in turn is dictated by the need to avoid insensitive regions and mechanical support structures, and also by limitations on the available number of readout channels. These difficulties are mitigated by the very small number of Mod. 0 sensors required and the fact that five of them can fit in a single 150 mm wafer. Because of this, a low fabrication and assembly yield can be tolerated.

#### 6.4.1.1 Efficiency

The silicon detectors must maintain high singlepoint efficiency in order to achieve the requirements given in Section xxx for high overall track reconstruction efficiency and good tracking resolution. Loss of efficiency can occur from intrinsic strip inefficiencies, from bad interconnections, or from faulty electronics channels. Intrinsic strip inefficiencies can occur due to production defects which result in strips with unacceptably large leakage currents, from accidents during assembly causing the strip to be physically damaged, or from a breakdown in the AC-coupling capacitor. The latter problem is referred to as a pinhole and is due to a small hole in the oxide separating the implant from the metal readout strip above it. Pinholes can occur during fabrication, or they can be generated later on. Understanding and controlling the level of pinholes is one of the primary concerns in our program of silicon detector R&D.

Our goal is to achieve an overall single detector strip failure rate of less than 1%. Data from a large production of double-sided DC-coupled detectors (ALEPH) show that 60–70% can be achieved with a maximum inefficiency of 1%. On this basis, we expect that a 50% yield can be achieved for double-sided AC-coupled detectors while maintaining similar standards.

#### 6.4.1.2 Resolution

As described in Section xxx, we have determined from Monte Carlo simulations [xxx] that the intrinsic point resolution should be  $15\mu \rm m$  or better in both z and  $\phi$  for the inner layers. These are the point resolutions for tracks at near-normal incidence. As the angle between the track and the plane normal to the strip increases, the resolution degrades. We require the resolution to degrade by no more than a factor of approximately 3 for angles up to  $75^{\circ}$  ( $\lambda \sim 1.3$ ) from normal.

#### 6.4.1.3 Radiation hardness

A further requirement is that the quoted resolution values hold up to an integrated dose of  $\sim 2\,\mathrm{Mrad}$  of ionizing radiation (electromagnetic in origin). This requirement leads to the use of AC-coupled detectors in order to avoid the problems associated with direct coupling of the large leakage currents which can occur at such large doses. It also has implications in the choice of the biasing scheme.

#### 6.4.2 Sensor design

From the above requirements and from the discussion in Sections xxx, we have arrived at the detector specifications and design parameters which are described in this section. A more complete discussion can be found in Reference xxx.

**Substrate and implant type.** The wafers will be n-type, with a resistivity in the range 4–8 k $\Omega$  cm, corresponding to a depletion voltage of 40 to 80 V. These values seem to be a reasonable compromise between the need to have a low depletion voltage and the need to avoid type inversion in the presence of radiation damage.

We will employ  $p^+$  strips on the junction side and  $n^+$  strips on the ohmic side, with  $p^+$ -

blocking implants in between; see Figure xxx for a cross-sectional view. This choice has proven to be a reliable technology xxx] which is directly available without extensive R&D.

Coupling to preamplifier. The strips are connected to the preamplifiers through a decoupling capacitor. AC coupling prevents the amplifier from integrating the leakage current with the signal; handling high leakage currents due to radiation damage imposes an additional burden on the preamplifier design and hasother undesirable operational implications.

The value of the decoupling capacitance must be much larger than the total strip capacitance, which is as large as 35 pF. Capacitors integrated on the detectors are the most compact solution, yielding a value for the decoupling capacitance of 30–80 pF/cm [xxx], depending on the implant width.

Bias resistors. The bias resistors must be between 4 and 20 M $\Omega$ . The lower limit is determined by two factors. The noise has a  $1/\sqrt{R_B}$  dependence, and if several strips are ganged together, the effective resistance is correspondingly decreased. Another factor is the requirement that, for floating strips, the product  $R_B \cdot C_{TOT}$  must be much larger than the amplifier peaking time (100–400 ns) to allow for capacitive charge partition. The upper limit (20) is dictated by the allowable potential drop due to the strip leakage current, which is taken to be 100 nA at maximum. A good target value is 8 M $\Omega$ . A final requirement is that the bias resistor be quite stable for the expected radiation doses.

To meet these requirements, we plan to use polysilicon bias resistors. Values of  $50 \text{ k}\Omega/\text{square}$  for the sheet resistance of polysilicon can be achieved. Thus, it is possible to fabricate an  $8 \text{ M}\Omega$  resistor with a  $6 \mu$ m-wide,  $960 \mu$ m-long polysilicon resistor. With a suitable shaping of the polysilicon line, the space required by the resistor will be  $480 \mu$ m for a  $25\mu$ m implant pitch.

Considering the space needed to accommodate the biasing resistors and to gracefully de-

| Sensor Type              | 0     | I     | II   | III    | IVa    | IVb    | Va     | Vb     | VI                   |

|--------------------------|-------|-------|------|--------|--------|--------|--------|--------|----------------------|

| Dimensions (mm)          |       |       |      |        |        |        |        |        |                      |

| z Length (L)             | 105.2 | 111.7 | 66.4 | 96.4   | 114.6  | 119.8  | 102.2  | 106.0  | 68.0                 |

| $\phi$ Width (W)         | 15.1  | 41.3  | 49.4 | 71.5   | 52.8   | 52.8   | 52.8   | 52.8   | 52.8-43.3            |

| Thickness                | 0.20  | 0.30  | 0.30 | 0.30   | 0.30   | 0.30   | 0.30   | 0.30   | 0.30                 |

| PN junction side reads   | u     | z     | z    | $\phi$ | $\phi$ | $\phi$ | $\phi$ | $\phi$ | $\phi$               |

| Strip Pitch (µm)         |       |       |      |        |        |        |        |        |                      |

| z (u  for Layer  0)      | 54    | 50    | 50   | 55     | 105    | 105    | 105    | 105    | 105                  |

| $\phi$ (v for Layer 0)   | 54    | 50    | 55   | 50     | 50     | 50     | 50     | 50     | $50 \rightarrow 41$  |

| Readout Pitch (µm)       |       |       |      |        |        |        |        |        |                      |

| z ( $u$ for Layer 0)     | 54    | 100   | 100  | 110    | 210    | 210    | 210    | 210    |                      |

| $\phi$ (v for Layer 0)   | 54    | 50    | 55   | 100    | 100    | 100    | 100    | 100    | $100 \rightarrow 82$ |

| Number of Readout Strips |       |       |      |        |        |        |        |        |                      |

| z ( $u$ for Layer $0$ )  | 1536  | 1104  | 651  | 865    | 540    | 565    | 481    | 499    | 318                  |

| $\phi$ (v for Layer 0)   | 1536  | 799   | 874  | 701    | 512    | 512    | 512    | 512    | 512                  |

Table 6.1: Physical dimensions, number of strips and pitches for the nine different sensor models.

grade the electric field close to the edge with a guard ring structure, we specify the active region of the detectors to be 1.4 mm smaller than the physical dimensions (700  $\mu$ m on each edge).

Optimization of z and  $\phi$  readout strips. A major issue is which side of the detector (junction or ohmic) should read which coordinate (z)or  $\phi$ ). The capacitance, and consequently, the noise is somewhat smaller on the junction side than on the ohmic side, and the strip pitch on the junction side can be  $25\mu m$ , while on the ohmic side, it is limited to about  $50\mu$ m because of the prep-stop implant. For these reasons and because the z vertex measurement is more important from the point of view of physics, we use the junction side for the z strips on the inner layers. The better performance of the junction side also helps compensate for the additional resistance and capacitance imposed by the longer z fanout circuit.

In order to maintain acceptable signal-tonoise ratios for tracks at large dip angles, we employ a  $100\mu m$  readout pitch for these z strips with one floating strip in between every two readout strips. We have considered using a wider readout pitch, for example,  $200\mu m$  for the very forward and backward regions in order to increase the signal at large dip angles. However, this would involve yet another detector design, and based on our present estimates of achievable electronic noise, it does not appear to be necessary.

Acceptable resolution can be obtained for the  $\phi$  strips on the inner layers using the ohmic side. Two solutions are possible; either a  $50\mu m$  readout pitch without floating strips, since there is no room for them on the ohmic side, or a  $100\mu m$ readout pitch with one floating strip. Either solution is feasible, and they should give roughly equivalent position resolution for single tracks. Double-track resolution is better for the first solution, and the noise contribution due to detector leakage currents is doubled in the latter solution. Therefore, preference goes to a  $50\mu m$ readout pitch without floating strips. Although this choice has twice as many readout channels, the cost implications are not very important because the electronics cost is dominated by the development effort and consequently the per channel incremental cost is not significant.

Using the numbers in Table xxx, we see that the current design employs seven different types

Table 6.2: Number of the different sensor types per module, area of the installed sensors, number of installed sensors and number of sensors including spares. Spare sensors include one spare module per module type (two for layer 0) plus additional sensors accounting for possible losses during assembly of SVT.

| Sensor Type                    | 0      | I      | II     | III   | IVa   | IVb   | Va    | Vb    | VI    | All  |

|--------------------------------|--------|--------|--------|-------|-------|-------|-------|-------|-------|------|

| Layer0                         | 1      | -      | -      | -     | -     | _     | -     | -     | -     | 1    |

| Layer1                         | _      | 2      | _      | _     | _     | _     | _     | _     | _     | 2    |

| Layer2                         | _      | _      | 4      | -     | _     | _     | _     | _     | _     | 4    |

| Layer3                         | _      | _      | _      | 4     | _     | _     | _     | _     |       | 4    |

| Layer4a                        | _      | _      | _      | -     | 4     | _     | _     | _     | 2     | 6    |

| Layer4b                        | _      | _      | _      | _     | _     | 4     | _     | _     | 2     | 6    |

| Layer5a                        | _      | _      | _      | _     | _     | _     | 6     | _     | 2     | 8    |

| Layer5b                        | -      | _      | _      | -     | _     | _     | -     | 6     | 2     | 8    |

| Silicon Area (m <sup>2</sup> ) | 0.0127 | 0.0554 | 0.0787 | 0.166 | 0.194 | 0.203 | 0.201 | 0.302 | 0.222 | 1.51 |

| Nr. of Sensors                 | 8      | 12     | 24     | 24    | 32    | 32    | 54    | 54    | 68    | 308  |

| Nr. Including Spares           | 20     | 20     | 40     | 35    | 44    | 44    | 72    | 72    | 92    | 439  |

of detectors (*i.e.* seven sets of masks) and needs 36 fabrication batches, for a total of 340 installed detectors. Having so many types of detectors complicates both the design and production phases, especially for prototype and spare production. A reduction in the number of detector types would be most welcome; however, this represents the minimum which we have been able to achieve in our present baseline design.

6.4.2.1 Technology choice

6.4.2.2 Optimization of strip layout

6.4.2.3 Wafer sizes and quantities

6.4.3 Prototyping and tests

6.5 Fanout Circuits L.Vitale - M.Prest4+4 pages

(Layer0 will be treated separately from the other ones)

#### 6.5.1 Fanouts for layer0

6.5.1.1 Requirements

6.5.1.2 Technology

6.5.1.3 Design

6.5.1.4 Prototyping and tests

#### 6.5.2 Fanouts for outer layers

#### 6.5.2.1 Requirements

The requirements will be fixed by the detector designs. From the production point of view, the minimum line width is 15  $\mu$ m with a space between the lines of 15  $\mu$ m. With the present technology, it is not possible to go below these numbers. No constraints are present on the fanout length given the same machines used for the micropattern gas detector production will be used.

#### 6.5.2.2 Material and production technique

The BaBar fanouts were produced on  $50 \mu m$  Upilex (by UBE) with a deposit of 150 nm of Cr,  $4.5 \mu m$  of copper followed by a layer of 150 nm of Cr and  $1.5 \mu m$  of amorphous gold. The SuperB SVT fanouts will be produced on a similar material by UBE ( $50 \mu m$  of polyamide with  $5 \mu m$  of copper directly deposited on the base material) which should ensure less defects and thus a better yield. This material will be tested in the prototype phase. The old Upilex is anyway still wait by if the trow Pratrice is anyway not adequate.

Table 6.3: List of different mask sets for 150 mm wafers, specifying the content of each wafer layout, the minimum value of the distance between the sensors and the wafer edge, the number of wafer required for each design and the total number of wafer. Quoted numbers include the spare sensors, but not the fabrication yield.

| Mask Design | Wafer content            | Min. Clearance to | Number    |

|-------------|--------------------------|-------------------|-----------|

|             |                          | Wafer Edge (mm)   | of Wafers |

| A           | $5 \times \text{Mod } 0$ | 10.2              | 5         |

| В           | Mod I + Mod VI           | 8.2               | 20        |

| С           | Mod III                  | 15.0              | 35        |

| D           | Mod IVa                  | 11.9              | 44        |

| E           | Mod IVb                  | 9.5               | 44        |

| F           | $Mod\ IVb + Mod\ VI$     | 9.8               | 72        |

| G           | Mod IVa + Mod II         | 6.9               | 72        |

| Total       |                          |                   | 287       |

Table 6.4: Electrical parameters for the different detector types Numbers to be updated.

|               | z-:       | readout Sid | le                     | $\phi$ -readout Side |          |                        |  |

|---------------|-----------|-------------|------------------------|----------------------|----------|------------------------|--|

| Detector Type | $C_{int}$ | $C_{AC}$    | $R_{series}$           | $C_{int}$            | $C_{AC}$ | $R_{series}$           |  |

|               | (pF/cm)   | (pF/cm)     | $(\Omega/\mathrm{cm})$ | (pF/cm)              | (pF/cm)  | $(\Omega/\mathrm{cm})$ |  |

| I             | 1.3       | 40          | 7                      | 2.8                  | 40       | 7                      |  |

| II            | 1.3       | 40          | 7                      | 2.8                  | 40       | 7                      |  |

| III           | 1.3       | 40          | 7                      | 2.8                  | 40       | 7                      |  |

| IVa           | 1.5       | 80          | 3.5                    | 1.3                  | 40       | 7                      |  |

| IVb           | 1.5       | 80          | 3.5                    | 1.3                  | 40       | 7                      |  |

| Va            | 1.5       | 80          | 3.5                    | 1.3                  | 40       | 7                      |  |

| Vb            | 1.5       | 80          | 3.5                    | 1.3                  | 40       | 7                      |  |

| VI            | 1.5       | 80          | 3.5                    | 1.3                  | 30       | 9.2                    |  |

A new technique for the production will be implemented in order to reduce the production times. In the BaBar production line, the photoresist was impressed through a mask after its being deposited on the Upilex requiring to work in a clean room. For SuperB, the idea is to impress the photoresist directly with a laser; this means the photoresist is solid and allows to complete the procedure in a much faster way. This technique has already been tested on the same pitches foreseen for the SVT fanouts.

The increase in the production speed allows to repeat the production of pieces with defects without delaying the SVT assembly. All the pieces will be gold plated with 1.5  $\mu$ m of amorphous gold for the bonding.

#### 6.5.2.3 Design

The design will follow the same rules of the BaBar fanouts adapting it to the different length of the modules. Differently from the BaBar pieces, no test-tree is foreseen (see next section). To allow the gold plating, all the lines will be shorted. A suitable cutting device will be developed to cut the shorting line after the visual inspection.

Figure 6.5: Design of a z fanout prototype.

The Table 6.5 summarizes the geometrical parameters as well as number of readout strips and channels, typical pitch and total number of required circuits per layer and type.

Figure **6.4** ...

Ganging vs pairing to be discussed (is this the proper place?).

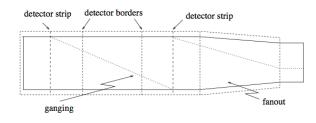

Figure 6.4: Schematic view of two z strips ganged with the fanout circuit.

#### 6.5.2.4 Tests and prototyping

All the fanouts will be automatically optically checked by a dedicated machine which will use the gerber files of the fanouts to find shorts or open lines. The machine can work with 25  $\mu$ m lines. The region with smaller lines (15  $\mu$ m with a 15  $\mu$ m space) corresponding to the bonding area (1.5 mm long and around 6 mm wide) will have to be controlled manually.

Given the much shorter time needed for the production, no correction is foreseen for shorts or

open lines; the damaged pieces will be produced again. On the other hand, if a short is present in the larger pitch region, the same correction procedure used for BaBar (the use of a microprobe) can be implemented.

As far as the tests are concerned, a batch of fanouts will be produced starting from the BaBar design to check the whole production and test chain. These fanouts in principle can be used with working detectors to test also the assembly procedures.

Figure 6.5 shows the design of a z fanout prototype ... These prototypes were also used to measure the typical capacitance and average radiation thickness ...

#### 6.6 Electronics Readout 28 pages

#### 6.6.1 Readout chips

#### V.Re - 10

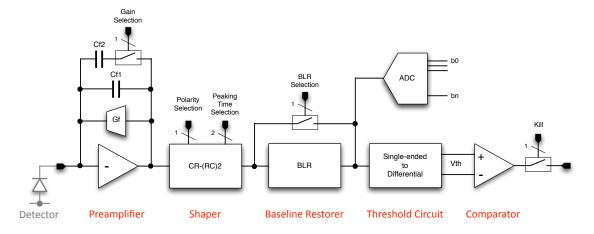

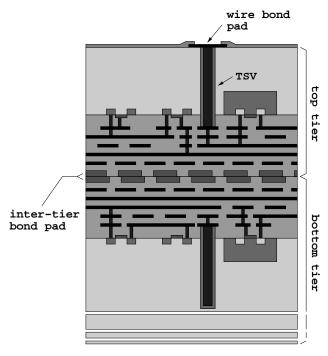

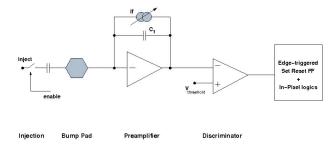

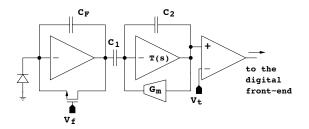

# 6.6.1.1 Electronic Readout for Strip and Striplet Detectors

The front-end processing of the signals from the silicon strip detectors will be performed by custom-designed ICs mounted on hybrid circuits that distribute power and signals, and thermally interface the ICs to the cooling system. As discussed below, the very different features of inner (Layer 0-3) and outer layers (4 and 5) of the SVT set divergent requirements to the readout chips, which most probably makes it necessary to develop two distinct integrated circuits. This obviously holds also in the case a different technology (pixels) is adopted for Layer 0 instead of short strips (striplets). Generally speaking, both types of ICs will consist of 128 channels, each connected to a detector strip. The signals from the strips, after amplification and shaping will be compared to a preset threshold. If a signal exceeding the threshold is detected, a 3-4 bit analog information about the signal amplitude will be provided by an ADC: this will mostly serve for calibration and monitoring purposes in the innermost layers, whereas in outer layers it will be essential for dE/dx measurements. The dimensions of the readout IC are

| Layer | Fanout                                | Length | Number of Readout |          | Typica         | Number           |             |

|-------|---------------------------------------|--------|-------------------|----------|----------------|------------------|-------------|

|       | Type                                  | (cm)   | Strips            | Channels | $Input(\mu m)$ | Output $(\mu m)$ | of Circuits |

| 1     | z                                     |        |                   |          |                | ROchip           | 12          |

|       | $\phi$                                |        |                   |          |                | 50?              | 12          |

|       |                                       |        |                   |          |                |                  |             |

| 2     | z                                     |        |                   |          |                |                  | 12          |

|       | $\phi$                                |        |                   |          |                |                  | 12          |

|       |                                       |        |                   |          |                |                  | 10          |

| 3     | z                                     |        |                   |          |                |                  | 12          |

|       | $\phi$                                |        |                   |          |                |                  | 12          |

| 10    |                                       |        |                   |          |                |                  | 16          |

| 4a    | $egin{array}{c} z \ \phi \end{array}$ |        |                   |          |                |                  | 16<br>16    |

|       | $   \phi $                            |        |                   |          |                |                  | 10          |

| 4b    | z                                     |        |                   |          |                |                  | 16          |

|       | $\phi$                                |        |                   |          |                |                  | 16          |

|       | Ψ                                     |        |                   |          |                |                  | 10          |

| 5a    | z                                     |        |                   |          |                |                  | 18          |

|       | $\phi$                                |        |                   |          |                |                  | 18          |

|       |                                       |        |                   |          |                |                  |             |

| 5b    | z                                     |        |                   |          |                |                  | 18          |

|       | $\phi$                                |        |                   |          |                |                  | 18          |

|       |                                       |        |                   |          |                |                  |             |

Table 6.5: Summary of fanout circuit characteristics.

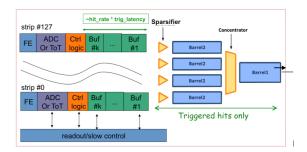

expected to be about  $6\times4$  mm<sup>2</sup>. As discussed in the SVT HDI subsection of this TDR, the dimensions of the HDI set a 6 mm upper limit on the side of the chip with the bonding pads for the interconnection with the strip sensors. The power dissipation will be about 4 mW/channel including both analog and digital sections. For each channel with a signal above threshold, the strip number, the amplitude information, the chip identification number and the related time stamp will be stored inside the chip waiting for a trigger signal for a time corresponding to the trigger latency (about 6  $\mu$ s). When a trigger is received, data will be read out and transmitted off chip, otherwise they will be discarded. The data output from the microstrip detector will be sparsified, i.e. will consist only of those channels generating a hit. The readout integrated circuits must remain functional up to 5 times nominal background. The option of operating in a data push fashion could be preserved for the external layers, where this will be allowed by the low strip hit rate. This will give the possibility to feed data from these layers to the trigger system.

#### 6.6.1.2 Readout chips requirements

The microstrip electronics must ensure that the detector system operates with adequate efficiency, but also must be robust and easy to test, and must facilitate testing and monitoring of the microstrip sensors. AC coupling is assumed between the strips and the readout electronics.

#### • Mechanical Requirements:

Number of channels per chip: 128 Chip size: width  $\leq 6$  mm, length  $\leq 4$  mm Pitch of input bonding pads:  $<45~\mu m$  • Operational Requirements: Operating temperature: <40 °C

Radiation tolerance: >3 Mrad/year,

$>5.10^{12} \text{ n}_{eq}/\text{cm}^2/\text{year}$

Power dissipation: <4 mW/channel

- Dynamic range: The front-end chips must accept signals from either P and N-side of the strip detectors. A linear response of the analog processing section is required from a minimum input charge corresponding to 0.2 MIP up to a full dynamic range of 10-15 MIP charge for dE/dx measurements.

- Analog Resolution: The front-end chips have to provide an analog information about the charge collected in the detector, which will be also used for calibrating and monitoring the system. A resolution of 0.2 MIP charge is required for dE/dx measurements. In case of a compression-type ADC characteristic, this may translate in 3-4 bits of information.

- Efficiency: At design luminosity, the microstrip readout must have a hit efficiency of at least 95% during its entire operational lifetime. This includes any loss of data by readout electronics or readout dead time.

- Readout bandwidth: Data coming out of the chip will be substantially reduced by operating in a triggered mode. The chips can use up to 4 output LVDS lines, as it is needed to handle the higher data throughput in inner SVT layers.

- Radiation Tolerance: All the components of the microstrip readout system must remain operational up to 10 years of SuperB running at the nominal luminosity.

- Peaking Time: The constraints for the peaking time of the signal at the shaper output are dictated by different needs in inner and outer layers. In Layer 0, the high occupancy due to background and the need to avoid pulse overlap and consequent

- hit inefficiencies set the maximum peaking time at  $t_p{=}25$  ns, which also allow for a high timing resolution (see below). In the external layers, where background hit frequency is much smaller and where strips are longer and have a larger capacitance, the peaking time will be mostly determined by the need of reducing series noise contributions and has to be in the range of 0.5-1.0  $\mu$ s.

- Signal-to-Noise Ratio: Concerning the signal, this requirement has to take into account the different thickness of silicon detectors in inner (200  $\mu$ m) and outer  $(300 \mu m)$  layers, as well the signal spread among various strips that depends on the track angle inside detectors and that, again, may vary in different SVT layers. Noiserelated parameters (strip capacitance and distributed resistance) also sizably vary across the SVT. A signal-to noise ratio of 20 has to be ensured across the whole SVT and should not increase significantly after irradiation. Here are the two extreme cases (where the equivalent noise charge ENC includes the thermal noise contribution from the distributed resistance of the strips):

- Layer 0 striplets: ENC  $\approx$ 700 e- at  $C_D$ =10 pF and at  $t_p$ =25 ns

- Layer 5 strips: ENC  $\approx$ 1000 e- at  $C_D$ =70 pF and at  $t_p$ =1  $\mu$ s

- Threshold and Dispersion: Each microstrip channel will be read out by comparing its signal to a settable threshold around 0.2 MIP. Threshold dispersion must be low enough that the noise hit rate and the efficiency are degraded to a negligible extent. Typically, this should be 300 rms electrons at most and should be stable during its entire operational lifetime.

- Comparator Time Resolution: The comparator must be fast enough to guarantee that the output can be latched in the right time stamp period.

- Time Stamp: 30 ns time stamp resolution is required for inner layers to get a good hit time resolution in order to reduce the occupancy in the offline time window (50-100 ns). In the outer layers the time stamp resolution is less critical since the hit time resolution will be dominated by the long pulse shaping time. A single 30 ns time stamp clock in all layers will be used.

- Chip clock frequency: Two main clocks will be used inside the readout chip, the time stamp clock (33 MHz) and the readout clock (132 MHz or 198 MHz). These clocks will be synchronized with the 66 MHz SuperB system clock. In case the analog-todigital conversion is based on the Time-Over-Threshold (TOT) method, a ToT clock has to be generated inside the chip. The TOT clock period should at least match the pulse shaping time to get a good analog resolution. A faster TOT clock could slightly improve the analog resolution but an upper limit ( $\approx 3.5$ ) on the ratio between TOT clock frequency and the shaping time frequency is imposed by the required dynamic range needed for low momentum particle dE/dx measurements  $(\approx 10\text{-}15 \text{ MIP})$  and the number of bits available for TOT. With the experience of the BaBar Atom chip a TOT clock frequency 3 times higher than the pulse shaping frequency could be used: 120 MHz (60 MHz are probably ok too??) for L0, 60 MHz for L1-2, 15 MHz for Layer3 and 6-3 MHz for L4-5.

- Mask, Kill and Inject: Each micro-strip channel must be testable by charge injection to the front-end amplifier. By digital control, it shall be possible to turn off any micro-strip element from the readout chain.

- Maximum data rate: Simulations show that machine-related backgrounds dominate the overall rates. At nominal background levels, the maximum hit rate per strip is 2 MHz/strip in Layer 0

- (45 MHz/cm<sup>2</sup>), 0.7 MHz/strip in Layer 1, 0.4 MHz/strip in Layer 2. These numbers include a safety factor of 5.

- **Deadtime limits:** The maximum total deadtime of the system must not exceed 10 % at a 150 kHz trigger rate and background 5 times the nominal expected rate.

- Trigger specifications: The trigger has a nominal latency of 7  $\mu$ s, a maximum jitter of 0.1  $\mu$ s, and the minimum time between triggers is 70 ns. The maximum Level 1 Trigger rate is 150 kHz.

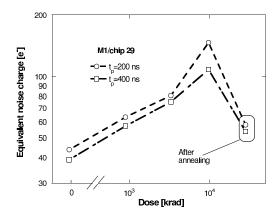

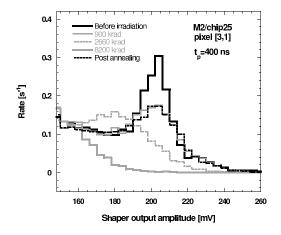

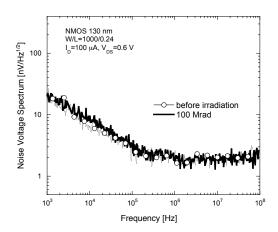

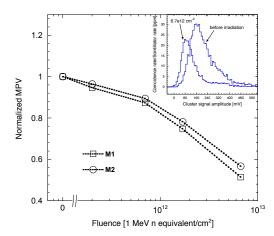

- Cross-talk: Must be less than 2 %.