# SEVENTH FRAMEWORK PROGRAMME THE PEOPLE PROGRAMME

# Annex I - "Description of Work"\*

# PART A:

# Grant agreement for:Industry-Academia Partnerships and PathwaysCall identifier:FP7-PEOPLE-2012-IAPP

**Project acronym:** FTK **Grant agreement no.:** 324318

**Project full title:** Fast Tracker for Hadron Collider Experiments

Date of approval of Annex I by REA: *date of the last version* Project start date: *DD/MM/YYYY*

**Duration of the project: 48 months**

\* This Annex I refers to the 2012 PEOPLE Work Programme (European Commission C(2011)5033 of 19 July 2011)

### A.1 Project abstract

**Keywords:** trigger, online tracking, pattern matching, content addressable memories, FPGA, VLSI, real-time, electronics, Higgs.

#### Abstract:

This project aims to develop an extremely fast but compact processor, with supercomputer performances, for pattern recognition, data reduction, and information extraction in high quality image processing. The proposed hardware prototype features flexibility for potential applications in a wide range of fields, from triggering in high energy physics to simulating human brain functions in experimental psychology or to automating diagnosis by imaging in medical physics. In general, any artificial intelligence process based on massive pattern recognition could largely profit from our device, provided data are suitably prepared and formatted.

The first goal consists in demonstrating the system can perform online track reconstruction of full events at the highest luminosities of the LHC and SLHC) at CERN, beyond the limits of any existent or planned device and despite the overwhelming confusion due to the very high track multiplicity and the exceedingly large event pile-up. With this goal we participate to the construction and the test for an high precision real-time tracker built for the ATLAS experiment: the Fast Track (FTK) processor. FTK can improve the capability of the ATLAS detector to select interesting events reach of heavy leptons or quarks within the enormous LHC background. It uses FPGA and ASIC chips to implement, real-time, complex track reconstruction algorithms. The track's trajectories are reconstructed in 3D, in few dozens of microseconds and the quality of the parameters is almost offline. FTK will increase the ATLAS discovery capability.

In parallel we will pursue challenging R&D & new real time computing ideas for more complex applications. A new industry-academia cooperation will reinforce the FTK team making it suited for such applications. The knowledge transfer will significantly increase the research quality and overall RTD capability and competitiveness of the partners, opening new scientific directions for our technology dissemination.

# PART B:

| <u>B.1 List</u> | of | <b>participants</b> |

|-----------------|----|---------------------|

|                 |    |                     |

| Beneficiary<br>Number * | Beneficiary<br>short name** | Commercial<br>Sector (Y/N) | SME<br>(Y/N) | Country     | Scientist<br>in charge | Month Enter-Exit<br>Project*** |

|-------------------------|-----------------------------|----------------------------|--------------|-------------|------------------------|--------------------------------|

| 1                       | UniPisa                     | Ν                          | Ν            | Italy       | Dell'Orso              | M1-M48                         |

| 2                       | CAEN                        | Y                          | Y            | Italy       | Petrucci               | M1-M48                         |

| 3                       | CERN                        | Ν                          | Ν            | Switzerland | Formenti               | M1-M48                         |

| 4                       | AUTH                        | Ν                          | Ν            | Greece      | Kordas                 | M1-M48                         |

| 5                       | PRIELE                      | Y                          | Y            | Greece      | Mermigli               | M1-M48                         |

| 6                       | CNRS                        | Ν                          | Ν            | France      | Calderini              | M1-M48                         |

|                         |                             |                            |              |             |                        |                                |

|                         |                             |                            |              |             |                        |                                |

\* Please use the same beneficiary numbering as that used in the A2 forms of PSFs.

\*\* In case of a Joint Research Unit; add to the footnote: partner X represents the joint Research Unit "XXX" formed together with Y and W (if applicable)

\*\*\* Insert the month when the participant will start and end its contribution in the project (Month 1, Month 12, etc). These columns are needed in case of future modifications to the grant agreement if existing participants leave or new participants join the consortium.

# **B.2 S&T Quality**

### **B.2.1.** Objectives of the research programme

The Physics programme at CERN's Large Hadron Collider (LHC) has been extremely successful since the early phase of data taking in the year 2010. The LHC detectors were designed to search for new discoveries in the head-on collisions of protons of extraordinarily high energy. The origin of mass, extra dimensions of space, unification of fundamental forces, evidence for dark matter candidates in the Universe are among the most interesting searches.

Moreover, the LHC upgrade, currently called the Super LHC (SLHC), will provide continuously increasing instantaneous luminosity, and will widen our capability to search new phenomena that are beyond the scope of our current theory of matter and energy, the Standard Model (SM). In the next few years an impressive harvest of data will be collected at the LHC and at the same time R&D at the technological frontier will be pursued for SLHC.

The proponents of this project are active essential participants of both events. These experiments will have a fundamental impact on physics and technology for the next 20 years. There are good reasons to expect that these new areas of research will have heavy quarks as well as tau leptons – the so-called third fermion generation - in the interesting events. These third generation objects will be excellent probes to search for New Physics.

Tracking devices, and in particular the Silicon devices that are becoming the predominant tracking technology, play an essential role in the identification of the third fermion generation. On the other hand the electronics required to process the signals from the detectors is taking a very important role, and it must be state of the art. The most interesting processes are very rare and hidden in an extremely large level of background. Implementing the most powerful selections in real time is therefore essential to fully exploit the physics potential of experiments where only a very limited fraction of the produced data can be recorded. A drastic real-time data reduction must be obtained. This makes on-line event reconstruction a critical component at any hadron collider experiment. A multi-level trigger is an effective solution for an otherwise impossible problem at LHC. The level-1 (L1) trigger is based on custom processors and reduces the rate from 40 MHz to ~100 kHz . The level-2 (L2) is based on standard CPUs. The L2 output rate is ~3 kHz. The Level-3 (L3) selection, called Event Filter in Atlas (EF) is performed by CPU farms, which write to tape about 200 events/s (at LHC L2 and L3 can also be called High Level Trigger, HLT).

This project directly addresses the main technological challenges of hardware and software necessary to identify heavy flavour objects and jets with a tau lepton. These are tracking issues at detector and trigger level. Addressing the challenging physics goals at the terascale requires a high degree of detector sophistication and significant technological breakthroughs in: (a) new developments in Silicon tracking technologies for thin, radiation-hard sensors; (b) sophisticated triggering and real time processing; (c) use of very deep sub-micron electronics

The high-occupancy environment experienced at the LHC and even more at the SLHC, will require a huge computing power to reconstruct very complex events with hundreds of particles emanating from the proton-proton collisions happening every 25 ns at the heart of the detector. The increase in luminosity of accelerators will require highly segmented and radiation-hard sensors. Given the difficulty to fully deplete the sensors under those conditions and considering the importance of material budget in the quality of track reconstruction, a new development of thin sensors is necessary. We propose collaboration between research companies active in high energy physics and research institutions to face these challenging future conditions.

**The first important goal** of this project is the realization and optimization of the Associative Memory (AM) system to make it work in the FastTracker (FTK) processor for the Atlas experiment at LHC and its future evolution for **new applications**. FTK is a high-performance "super-processor" based on the combination of two innovative technologies: powerful FPGAs

(Field Programmable Gate Arrays) working with standard-cell ASICs (Application-Specific Integrated Circuits), the Associative Memory (AM) chips, for utmost gate integration density. Optimal partitioning of complex algorithms on a variety of computing technologies has been already proved to be a powerful strategy, which turned the past hadron collider experiment CDF at the Tevatron accelerator in the Fermilab Laboratory, near Chicago (USA) into a major player in the field of B-physics, on par with dedicated experiments operating at e+e- colliders.

A complementary and secondary goal is the participation to the development of new sensors and electronics for the upgrade of the Silicon tracker of the ATLAS experiment. The sensors should be able to provide charge collection efficiency still larger than 50% even in condition of partial depletion at an equivalent fluence of 1016 neq/cm2 (neq: neutron equivalent).

There are also important reasons, outside High Energy Physics (HEP), for the research proposed in the present program. Our approach to use powerful modern electronics is extremely flexible and its spread outside the realm of HEP would be extremely beneficial. The strategy of the "optimal mapping of a complex algorithm in different technologies" is a general approach that can speed up enormously any calculation by providing a high degree of parallelism. Handling complex electronics components (dedicated AM chips and FPGAs) is less straightforward than programming a multi-core CPU, since it requires availability of FPGA hardware and knowledge of computer-aided-design (CAD) tools. For this reason we think that the HEP development in this area is important to show the potential of these devices and to spread the skills needed to use them with top efficiency. There are already examples showing that the use of a tuned combination of CPUs and FPGAs could expand not only in HEP, but also in other academic and even non-academic fields, for example in financial applications. The "Workshop on High Performance Computational Finance" is an instance of the many occasions for discussing FPGA acceleration techniques in the financial domain.

These techniques could be very important in the area of medical imaging for real-time diagnosis, when the patient is under examination. The computing power is still a limiting factor for some high quality applications. High-resolution medical image processing, for example, demands enormous memory and computing power to allow 3D processing in a limited time. The same approach could be incisive for astrophysical and meteorological calculations, for robotic automation, for security applications. It could be essential for neurophysiologic studies of the brain. **This is a goal of our proposal, a study to apply our technology outside HEP.**

The use of the associative memory processor for brain studies is particularly fascinating. The most convincing models that try to validate brain functioning hypotheses are extremely similar to the real time architectures developed for HEP. A multilevel model seems appropriate also to describe the brain organization to perform a synthesis certainly much more impressive than what done in HEP triggers. The AM pattern matching has demonstrated to be able to play a key role in high rate filtering/reduction tasks. We can test the AM device capability as the first level of this process, dedicated to external stimuli preprocessing. We follow the conjecture of reference [Punzi & Del Viva (2006) Visual features and information theory JOV 6(6) 567]: the brain works by dramatically reducing input information by selecting for higher-level processing and long-term storage only those input data that match a particular set of memorized patterns. The double constraint of finite computing power and finite output bandwidth determines to a large extent what type of information is found to be "meaningful" or "relevant" and becomes part of higher level processing and longer-term memory. The AM-based processor will be used for a real-time hardware implementation of fast pattern selection/filtering as studied in these models of human vision and other brain functions.

We could apply this filtering function to medical images, to extract the salient features and apply fast but complex reconstruction algorithms to them. We would measure the extracted features in a very short time and automatic fashion providing a computer-diagnosis. The reduction of execution time of image reconstruction to be applied after the AM filtering function, would exploit the computing power of parallel arrays of Field Programmable Gate Arrays (FPGAs) as we do in FTK to find clusters of contiguous pixels above a certain programmable threshold. As we process them producing measurements that characterize their shape, we can measure quantities of interest in medical applications like the size of the found spots, how circular or irregular the spot is. The algorithm can be extended to 3-D images.

Also the development of sensors and related electronics has the inter-sectorial aspect of the medical physics. Solid state detectors have been used in medical imaging for many years for early diagnostic in cancerology. Digital images provided by this kind of sensors can also be processed with pattern-recognition algorithms to increase the diagnostic capability.

**The long-term goal** of this research is to increase the importance of parallel computing based on dedicated real-time techniques, disseminating them to a large scientific community.

#### **B.2.2. Research methodology and approach**

FTK is a second generation processor, much more ambitious than its progenitor, SVT, built for the CDF experiment. FTK reconstructs all events coming out of the L1 (100 kHz) to provide into few dozens of microseconds all the tracks with transverse momentum above 1 GeV to the L2. The power of FTK is mainly based on the AM chip. The same AM technology can be used also at L1, even in much more adverse conditions. All the LHC experiments, ATLAS, CMS and even LHCb, are thinking to it for SLHC. Let's compare the Tevatron and LHC machines to explain the increase of complexity of events and, as a consequence, of the tracking detectors. The CDF collision rate was ~2 MHz and at the instantaneous luminosity (ILum) of  $3 \times 10^{32}$  cm<sup>-2</sup> sec<sup>-1</sup> the average number of soft, not-interesting interactions per bunch crossing (pile-up) was 6 (396 ns bunch spacing). The LHC environment is much more demanding: a bunch spacing of 25 ns at high ILum ( $10^{34}$  cm<sup>-2</sup> sec<sup>-1</sup>) produces ~25 pile-up interactions. The LHC upgrade (SLHC), with the recently proposed scenario of 50 ns bunch spacing, will produce a pile-up of hundreds of events at the ILum of  $5 \times 10^{34}$  cm<sup>-2</sup> sec<sup>-1</sup>.

Today we can exploit a very important advantage to face the increased complexity: on the technological side, (a) the detector granularity is strongly increased (the SLHC silicon projects are an extreme result in this direction), (b) the digital electronics is becoming so powerful that the difference between the performance of the algorithms executed in real-time and in the offline analysis is significantly reduced, even in the extremely hard conditions of high data rates and limited processing time. Since the background suppression needed at trigger level is becoming similar to that of the usual offline analysis, the offline quality is required already at trigger level. Our goal is "online exploitation" of the full silicon detector resolution: it is challenging, but it is not impossible. Let's see how we plan to do it.

The FTK tracking algorithm is subdivided into 2 sequential steps of increasing resolution. In step 1 the dedicated VLSI device, the AM, finds track candidates with low spatial resolution, called roads. In step 2, the real tracks are searched within the roads and fitted to determine their parameters with the best resolution (sigma(IP)=35  $\mu$ m, sigma (1/PT) = 0.3 % and sigma( $\phi$ 0)=1 mrad). Tracks with PT>1 GeV/c are finally selected to tag secondary vertexes or to search for hadronic taus or to perform high quality track-based isolation of muons, electrons and gammas.

The AM performs the most CPU intensive part of the pattern recognition, exploiting dedicated highly parallel structures. It exploits the idea of a pattern matching algorithm based on pre-calculated and stored track candidates, which are compared in parallel with the actual event. It has to solve a very difficult problem since the silicon detector has millions of channels and the number of track candidates is very large (~10<sup>9</sup>). For this reason a high density dedicated chip has been developed for the AM. FTK includes important pre/post processing functions, complementary to the intensive pattern recognition performed by the AM. Pre-processing corresponds to (a) cluster finding in the silicon data, performed by ATCA boards called Data Formatters (DF); (b) smart database for immediate retrieval of full resolution detector clusters associated to roads found by the AM, performed by Data Organizers (DO). Post-processing includes (a) the track fitting performed by Track Fitters (TF) and (b) duplicate-track cleanup performed by the Hit Warrior (HW). The most important function is the track fitting, which refines the candidate tracks in order to determine the track parameters with the full detector resolution. The TF makes use of methods based on local linear approximations and learn-from-data techniques for online misalignment corrections. The fit calculation consists of scalar products. The FTK simulation shows that the approximations, made to be fast, do not significantly affect the fit performance.

The event processing is highly parallel into all online tracking processors, with the detector segmented into towers. Our main goal is to build the Processor Unit (PU) that pipelines all the functions needed by a high quality real time tracker. This is the processor core. A full coverage online tracking for ATLAS at the Phase 1 instant luminosity is estimated to require 8 9U VME crates with 16 PUs each (128 PUs), using the best technology available today. In addition to that, two ATCA crates of Data Formatters are necessary to cluster the raw hits coming from the detector and to provide the correct data to each PU. The main DF processing device is the FTK Input Mezzanine, (FTK\_IM), a data concentrator-processor for pixel and strip silicon detectors. It performs online clustering for uni- (strips) and bi-dimensional (pixel) detectors. Different clustering approaches will be studied and implemented on FPGAs.

The FastTracKer (FTK) has been approved recently by ATLAS for a Technical Design Report (TDR) submission in 2013 and to build a small demonstrator taking data in 2015. FTK is today mainly a collaboration between Italy and USA with a smaller contribution from Japan. If the demonstrator is successful, FTK will be enabled for a large production and will be a trigger upgrade for the LHC Phase1 (Phase I, up to  $L = 2x10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> and 40-80 pileup events). The Italian funding agency, INFN, has taken the responsibility to fund the PCBs and chip costs for the AM system in the demonstrator, but no money is provided for man-power costs, neither for future tests and commissioning periods, neither for further developments. The EU funds would provide the complementary contribution to push further this research, involve new Institution and Companies in an area that is in quick expansion, where new manpower and organization capabilities are strongly needed.

In parallel we need to gain experience on the modern TDAQ systems to face early the integration problems such a complex device could meet. Atlas is allowing us to test the integration of the FTK functions in the experiment, today, well before production. We plan early parasitic commissioning (no impact on normal ATLAS data taking, thanks to a duplicated additional output fiber provided for FTK by the tracking front-end) of a small proto-FTK, based on existing prototypes and able to reconstruct tracks inside a narrow azimuthal slice (tower) of the detector. The FTK output can be written to the calibration stream for offline studies. We call this proto-FTK a "vertical slice" because it will be small (operating on a slice of the detector) but functionally complete from the detector inputs up to the track output available for the L2 CPUs. The vertical slice will continue to exist as a test stand for new

output available for the L2 CPUs. The vertical slice will continue to exist as a test stand for new prototypes while the FTK demonstrator will start to take data in 2015.

In addition a new R&D is planned for the FTK evolution necessary for the many new foreseen applications, like online tracking at L1 and use of the AM for image processing. Time for FTK production after the TDR approval will be quite long, because of the LHC schedule, so even the FTK final production could profit of the electronic and algorithm advancement we plan to pursue in the next years. While the demonstrator will convince the collaborations of the FTK capabilities, we will provide modern, much more powerful prototypes (AMBSLP), fully tested in the vertical slice, ready to substitute the FTK default one (AMBFTK) in the final production.

#### The Serial Link Processor (SLP): a new Processor Unit for many different uses.

In the R&D area our goal is to build a new Processor Unit called "Serial Link Processor" or SLP. The SLP has many points in common with the past developments: it pipelines all the functions needed by high quality real time tracking (AM, DO, TF, HW); it will occupy a single VME slot, and will consist of a 9U VME board, the AMBSLP, along with an AUX card on the back of the crate, built by the USA FTK collaboration. The two future boards will exchange data through the P3 connector.

The AMBSLP, the object of the European research, will perform pattern recognition (128 AMchips on it). The AMBSLP has the same modular structure of the AMBFTK. It consists of 4 smaller boards, the Local Associative Memory Banks (LAMB). Each LAMB contains 32 AM chips, 16 per face. The AM chips come in LQ208 packages, and contain the stored patterns with the readout logic. They are connected into eight 4-chip pipelines on each LAMB. The found roads flow down in the 8 pipelines and are collected and merged into 4 parallel output streams by two readout logics called GLUEs. The SLP has a flexible control logic placed inside powerful FPGA chips (Xilinx). The FPGA flexibility allows to use the same architecture in different applications characterized by short- or long-latency trigger decisions, with the only exception of the LAMB, which needs to be specialized. In the case of long-latency (SLP2 for L2 trigger application or seeding of the offline tracking or image processing) very large associative memory banks can be obtained pipelining boards and AM chips. For low-latency applications (SLP1 for L1 trigger application) we reduce the pipelines as much as possible. We will develop a unique motherboard for all possible conditions. Two type of different LAMBs will be

developed, one for long-latency and one for low-latency applications. In the second case GLUE chips will be placed in the center of "stars" of AM chips directly connected to them, reducing significantly the latency for the road readout.

The SLP innovation consists in the use of high speed serial links everywhere in the system. The AM system is today overloaded by the enormous traffic of words flowing to the AM chips. Eight TTL 15 bit buses bring hits to the SLP with a consequent enormous fan out problem (128 AM chips). This is made even more complex by the board output traffic that in the LHC high luminosity will become extremely demanding and will require a larger number of output buses (16), of larger words (32 bit). A redesign of the boards and a new AM chip equipped with serializers, deserializers & differential I/O are required. The chip development is funded by INFN. Serial links will provide important advantages:

1. The system would gain in flexibility: data words with variable size could be delivered and collected without any change to the boards. It would gain also robustness, since the LVDS connection is much more robust against noise and cross talk.

2. We can push the transmission frequency into new ranges, far from what we faced in the past.

3. The board routing will be optimized and much less crowded. In particular the LAMB reorganization for L1 application, where direct connections are required between the many AM chips and the readout controllers (GLUEs) would not be possible using a large TTL road bus for each AM chip.

4. The necessary number of pins for signals in the AM chip package will be reduced. This is important because the AM chip silicon area has to increase in the future by a factor of 10, to contain a much larger number of patterns with no change of the package size. Unfortunately also the needs of the chip in terms of VCC and GND pins increases correspondingly, while the package we have (LQ208) is totally occupied by the many necessary TTL buses. Serialized I/O will provide space for VCC and GND pins.

5. The connection between the AMBFTK/AMBSLP and the AUX board is implemented with a very compact, high performance P3 connector, while in the past the AMBoard needed complex connections with the other boards. No backplane is anymore necessary.

**Appropriateness of research methodology and approach.** Our research methodology is based on the idea of a "continuous evolution". Our final goals are very challenging, so we need to advance per steps. For this reason we organize our work in such a way that design, tests and commissioning are performed in parallel, instead of executing them sequentially as usually is done. It is important that test results and commissioning provide a feedback on design before the system is frozen for a large production.

This working plan is extremely ambitious. The methodology of parallel design, tests, commissioning and future R&D is very demanding in terms of manpower and infrastructures. In addition the interest for this technology, as explained above, is quickly expanding. New studies are necessary for L1 and outside-HEP applications. It is particular relevant to have the possibility to involve new institutions and new companies that can learn about the project in the development phase and be fundamental in the future at the production and running time. The work is organized in 5 areas, or **work packages (WP)**.

**WP1**, "**Prototype Construction & Production validation**", includes board and FPGA firmware design, PCB construction and assembly, standalone test for a first validation. It is important that the designer can participate also to the first tests, before his product is integrated on the complete system. The board design is based on Cadence tools while the firmware is developed with the Xilinx CAD. The board assembly is complex, especially for the LAMB mezzanine that holds 32 AM chips, 12 Xilinx chips, and 8 devices for clock distribution in a small space. LAMBs, motherboards and FTK\_IM mezzanines will be produced. The experience gained on prototypes will allow PRIELE to assembly the FTK boards at production time and validate them at the company before commissioning.

**WP2**, "**Infrastructures and Integration**", first of all takes care of the crates, the power supplies and the space for integrated lab tests. We use 9U VME crates with custom VME VIPA backplane, 48V power source and large DC-DC converters from 48 Volts down to 1.2 V to provide the needed power for 128 AMchips per board. The board has 4 DC-DC converters, each one providing a maximum of 25 A at 1.2 Volts, for a total of 100 A and a maximum power of 120 W. Each AM board has a weight of 2 Kg, so the crate has to support a total weight of 40 kg. Cooling and mechanical tests will be performed. The air flow must be sufficient to keep cold the boards. Each rack will contain two crates, each one provided of its own power supply. The power supply has to be transparent as much as possible to air flux. The whole system will be collected in a single place, including parts developed by USA. There realistic experimental conditions will be reproduced and tests enough complex will be performed with Monte Carlo data to guarantee the hardware is complete and can run flawlessly. Software will be

developed to monitor and control the processor. The detector data will be produced in the lab by a "pseudo front-end" (a CPU). Data will be delivered via S-link from a mezzanine inserted in the CPU.

**WP3**, "**Commissioning**", closes the research path described above. After tests in the laboratory, the new hardware will be moved to the experiment and will spy real data during normal data taking. In fact commissioning implies the insertion in the experiment, the development of monitoring and control software compatible with its rules, long tests to validate the system, data taking and data understanding.

**WP4** is "Architecture Simulation". It is just software, but it has an important impact on hardware choices. A complex package, FTKsim has to simulate the hardware on Monte Carlo data, or real data. It is used to optimize the hardware design, to specify, build and test the internal data paths needed for the LHC high luminosity, to determine the optimal size of the AM system, to produce the Physics case. The simulation is an essential part of all tests since it allows to predict the hardware output, starting from the inputs, to validate the hardware (sometime the simulation) functionality.

**WP5**, "**Image Processing**", is a new very interesting atypical working area. We will use our AM-based Processor to process static images and movies in real time. We will check the capability of the AM to extract from the images and from a movie the relevant features and substantially suppress the not-relevant information. The images have to be formatted in the right way to provide data for the AM system. For static images groups of 3x3 pixels (black and white) are detected in the images and each particular configuration constitutes a 9-bit pattern. For films we need to add a third dimension, the time, so the patterns becomes 3x3x3, made of 27 bits (128 million possible configurations). All found patterns will be sent to the AM and their frequency will be measured by the FPGA that controls the board. The pattern frequency is the determinant feature to decide if a pattern is relevant or not. After this learning phase, the relevant patterns will be downloaded in the AM bank and the processor will be ready to filter the images/movies selecting only  $\sim 5\%$  of the input data (a maximum number of 1.5 million patterns can be downloaded today). The AM system always monitors the pattern frequencies and if the distribution changes the list of good patterns is updated. The mezzanine FTK\_IM, developed to process bi-dimensional pixel detector data, could process the AM output, the filtered image.

WP6 is "Silicon Detector R&D". This WP has a reduced role compared to the electronics tasks, however it provides a solid link with the evolution of the on-going R&D for the silicon sensors and the front-end readout electronics in view of the high luminosity upgrade of the LHC. This link is important for FTK since a constant dependence connects the evolving features of the future tracker (segmentation, geometry, expected hit efficiency, noise, readout speed) with the future of the FTK architecture. CAEN will collect together competencies about the different aspects of the detector and the processing system. To resist in the high-radiation environment of the SLHC interaction region, new pixel sensors are being developed. The p-type bulk is being investigated and this is expected to improve the radiation tolerance (no type-inversion) and the cost of the process. In facts the layout of n-in-p pixel sensors requires the guard ring region to be on the same face of the pixels, basically giving a much cheaper single-side process with respect to the sensors presently used. After radiation damage, the maximum achievable depletion region will be reduced to a fraction of the detector thickness and consequently the signal size will be reduced. The sensors will be back-thinned considerably (well below the 300um, and possibly even below 200um if the technology evolution will allow to reach this in the next few years). The sensors will be operated at below-zero temperature to keep the leakage current to a still acceptable level of a few uA per sensor at -10C. The segmentation will also be reduced. The phi coordinate will follow closely the limit given by the interconnection technology (the present pitch is 50um but this will be reduced to at least 35um) while the pixel length in eta will probably be constrained by the consequent area of the cell and the component density of the readout electronics. Prototypes of a chip in 65nm CMOS process are being developed for the readout chip, to increase the component density of the readout chip and to allow a further reduction of the sensor pixel size. In all this, the power dissipation will play an important role and the high voltage distribution system will be one of the key ingredients in the evolution of the detector design. Even if the detector is operated at a below-zero temperature, a power supply system able to provide 1KV tension at a maximum current of about 10mA per channel will be necessary, with excellent temperature stability and excellent ripple/noise specifications even at full current. The test-stand for the module evaluation will be assembled at CAEN in Viareggio, Italy, to test how the CAEN devices can perform in these difficult conditions. The silicon sensors with their readout electronics will be used with the CAEN high- and low-voltage distribution system. CAEN has a long-tradition as one of the leader producers.

### **B.3.1.** Quality and Importance of the Transfer of Knowledge programme

There is a large exchange of knowledge in our research work, since this application is generated by the growing interest on this technology and the enlargement of the FTK collaboration. We have a very rich program of secondments characterized by some peculiarities. First of all many physicists and engineers will be exchanged among the participant institutions, some of them working on the same items. This is justified by the fact that the project is complex and an important goal of this application is the transfer of competencies to new teams that should be strong enough to support all the new applications and developments. The new components of the collaboration have a first period dedicated to learn the technology, followed by a second period where they will become the leading actors of a new application or a working package. The new teams need a significant number of participants to face the effort of the development of a new application. A second feature of our plan is frequent splitting of secondments in multiple periods. This is justified by a scientific program with multiple phases of design, construction, test and commissioning. Transfer of knowledge (ToK) is optimized with multiple periods, as explained below. The multi-return-mechanism will ensure each time efficient ToK back into the organisation of origin of the seconded staff, spreading the experience to the whole group.

Particularly important is the ToK to CAEN & PRIELE. The FTK project has been developed in a very long time (R&D started in 1989) with a very low budget per year. One reason for such a slow increase of budget has been the large diffusion of the CPU-farm based trigger strategy at LHC. The FTK research field had to compete with the predominant idea that commercial devices were the best choice to perform the FTK tasks. FTK was never allowed to assign part of the design to a company, because of the high costs. CAEN itself never participated to FTK in the past, even if it would have been natural given its experience in the field and its small distance from Pisa, the place where FTK was born. The LHC data taking and the machine working conditions changed this scenario. The large number of secondary interactions (high pile-up) that characterized the 2011 run and will increase in the future favour the FTK very powerful parallel architecture. The increase in precision necessary for future measures requires huge samples collected in extremely hard conditions. This gives increasing importance to parallel computing and dedicated real-time techniques. Not only was FTK recently approved for the TDR, but even more ambitious applications are now conceived. FTK has to evolve from its status of R&D. Now that the project is slowly moving from design and prototyping to production we really need the collaboration of companies with a wide experience in test, integration and commissioning of many complex boards. The complexity increase of FTK compared to SVT at CDF, requires this level of organization also for future possible expansions at CMS or LHCb and spin off outside HEP. In addition a new market is opened to these companies. Intensive, parallel computation based on FPGAs and specific VLSIs is again a field where electronics has an enormous potential. This is obviously very interesting for the SMEs participating to this network.

Here we describe the need of ToK inside each WP keeping into account the project schedule described in section B.4 (see Schedule Table).

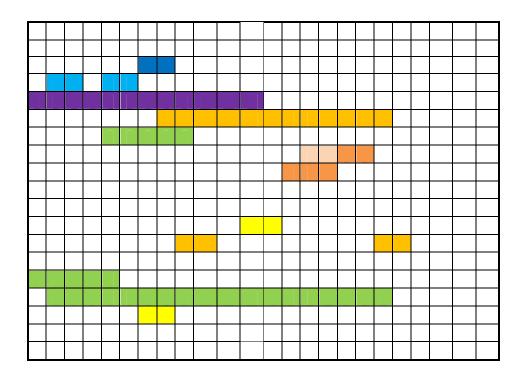

WP1 production & development (green in Schedule Table) – A flux of information is necessary inside the WP1, from the institutions already expert of tracking, as UniPisa, to the new collaborators, AUTH, CNRS and the PRIELE SME. The new Academia collaborators were mainly involved in detector construction in the past (AUTH for muon detectors, CNRS for silicon detectors). Now they are interested to start their activity in the trigger sector and in particular in the real time track reconstruction applied to their detectors. Also PRIELE manufactured electronics for CMS and did not have specific experience in online tracking in the past. On the other hand AUTH and CNRS have been in ATLAS for a long time, and PRIELE had experiences in CMS, while the UniPisa FTK researchers only recently joined the ATLAS collaboration . The experience of AUTH, CNRS and PRIELE about the LHC experiments will be valuable for the new group that has to integrate a challenging device in the already installed and working detector. PRIELE offers also a wide experience in electronics design & development as well as in manufacturing prototypes and/or mass production, in particular for space, defence and CERN applications, that is electronics constructions to function in hard environments. This could be a unique training opportunity for secondments and recruitments visiting PRIELE. Also AUTH and CNRS have a strong electronic division with significant FPGA expertise, so exchanging design experiences will certainly be worthwhile. This large availability of different design skills will increase the initial FTK project goals, the research quality and the overall RTD capability and competitiveness of all the partners. Contacts among the research institutions and the PRIELE SME are guaranteed by the large number of secondment months. UniPisa experienced personnel (Piendibene and Donati) has planned some months of the first year at PRIELE to (a) start the prototype design, (b) install the FTK test stand to check the assembly quality before the delivery of boards to integration (c) and also to collaborate on firmware and PCB design for the SLP2 prototype. They will also come back to PRIELE in the 3rd and 4th years for the final FTK small productions after the FTK demonstrator success. The seconded ERs will bring back to UniPisa their experience and will share it with other researchers opening their minds towards new opportunities, becoming familiar with practice in industrial routine. Similarly young personnel will be seconded from AUTH to PRIELE and viceversa. PRIELE and AUTH will collaborate for the design of boards and also the development of firmware. PRIELE secondments to Pisa will have the same goal. During the first year they will work on the system for L2 (SLP2) with the help of UniPisa and after that they will apply their acquired knowledge to L1 (SLP1), starting from the last quarter of the 2nd year. PRIELE engineers will profit of the high level tools (Cadence) available at the Universities and CERN. Coming back home they will transfer the knowledge to the company to reinforce it in its leading role of the WP1. Secondments dedicated to a certain job are split among collaborating Institutions to increase the connections among all the participants . For example the PCB design of the SLP2 will start in UniPisa with the secondment of Sakellariou from PRIELE to work with Piendibene. It will continue at PRIELE with the collaboration of both and Konstantakos from AUTH. The same will be done for the SLP1. This scheme is certainly the best way to reinforce the collaboration of the team, trained on a strong common background. The designers will spend time working together in different places, practicing different realities. CERN will have a particular role for the prototype design since they will provide important trainings. The Electronic Service at CERN belongs to the accelerator sector but it has the typical organization of a company. They provide very professional service for board design based on the Cadence tools. Designing with them the future FTK boards will be a wonderful opportunity to learn all the Cadence details/functionality. This is the goal of the recruitment there. The Electronic Service will recruit a young engineer (ER, less than 10 years experience) with advanced experience in the area of hardware real time tracking processors and initial experience of Cadence board design. The engineer will work in the electronic service, learn at the best level the use of Cadence tools and transfer the acquired knowledge about the tracking project. He/she will work also for the tests of the prototypes and will also gain commissioning experience. His/Her career will certainly profit from this valuable experience at CERN. Also AUTH will recruit one ER (less than 10 years experience) to work on online pattern recognition applied at Level 1 for the muon upgraded system. He/she will have to be expert of AM technology and its simulation, to reinforce the AUTH expertise in this field.

WP3 – Commissioning @ CERN (blue in Schedule Table). Commissioning of such a complex device in such a complex experiment & hard environment, already built & running is new for everybody within and also outside our collaboration. For this reason it is important to start early and proceed with small steps. All of us will learn gradually from the experience in the experiment. However CAEN has much more experience than the others, as far as infrastructure installation, security rules and procedures are concerned. CAEN will provide valuable support to researchers that will work there. At the same time CAEN will directly experience on the experiment the new field of application of advanced parallel and dedicated computing. It will acquire all the necessary expertise to help maintaining and expandinding this system in the future years of LHC data taking. This continuous exchange of expertise will be achieved with the secondment of Petrucci, high qualified CAEN personnel. He will participate to the 3 commissionings in the last 3 years. PRIELE engineer (ESR) K. Mermikli will be trained both by CERN and UniPisa experienced personnel and she will participate to the design of FTK tests and commissioning.

WP2 – WP4 Integration at CAEN & simulation (red and black in Schedule Table). This is a real training for all participating institutions. The exchange of experience and knowledge is maximum: we will collect all the results of all tests performed at each individual Institution to test the entire system of

boards working together. This is the synthesis of all the individual efforts. For this reason we schedule a large number of secondment months there from all the research institutions involved in WP1 except CERN that will offer similar experience in commissioning. The secondment includes both experienced researchers (Piendibene, Donati, Crescioli, Kordas, Sampsonidis) and a younger team. The experienced staff will guide and supervise the young ESRs and ERs work. We will have a significant group from AUTH coming the 1st and 2nd years to work with Piendibene. After the experience of the first year on the AMBFTK, the second year they will become expert of serial links in the SLP2 and they will be able to discuss L1 architectures. Crescioli will advance in the tests in alternative periods, working with Piendibene that will guarantee the contact with the previous experience. The 4th year the AUTH group will come back for the SLP1 tests. This will complete their effort and the success of these tests will be the transfer of knowledge. CAEN offers large enough infrastructures to allow this effort and will provide its competence to lead it. The integration will provide a common experience and background that will be brought back home to prepare a competent and coherent collaboration, ready to produce powerful super-processors. The secondments at PRIELE and CAEN will also be ideal to exchange information about simulation studies and developments. UniPisa will recruit an ER (less than 10 years experience) with software (C++), GRID and online hardware dedicated tracking expertise. He/she will have to be expert of FTK simulation, an item that is not currently supported at UniPisa.

WP5 – Image processing (violet in Schedule Table) Finally the AM system will be used by UniPisa for Image Processing. An ER (less than 10 years experience) with specific expertise in this field will be recruited by dimas the last year. He/she will have to be expert in C++ software and AM technology to adapt the existing AM system to the need of this application. The collaboration with CAEN in this work package is conceived to transfer knowledge to a company that could be interested in future applications if the system turns out to be successful. AUTH is also interested in WP5, since their electronic division is expert in image processing., However, given the complexity of the L1 system they plan to build for muons, they prefer to not officially participate to this WP.

WP6 – Silicon Detector R&D (pink in Schedule Table). This package foresees secondments of Calderini to CAEN to test CAEN power supply market for silicon detectors at SLHC. The work is diluted in the project 4 years, even if it could be executed in a much shorter time. We choose this strategy because the main goal of this work package is to keep the FTK collaboration, in particular CAEN, in contact with the detector R&D evolution, that will be important in all the years of our project, given the fact that this detectors are studied for LHC Phase II, scheduled after 2020. For this reason Calderini's secondment is split into 4 years, even if in total it amounts to only 4 months. An ER with more than 10 years experience will be recruited the second year by CNRS to work on both subjects Silicon R&D and online tracking. He should have expertise of silicon detectors and of hardware for online tracking. He will participate to the pixel R&D and the running of the FTK test stand that will be installed at CNRS to allow firmware and test developments in Paris.

### **B.3.2.** Role of exchanged/recruited staff within the ToK programme

The ToK will be guided by experienced researchers, physicists and engineers. They have wide experience in experiments and in electronics development as well as trigger and data acquisition (TDAQ). We describe here the personnel that will be seconded, their role in the ToK plan and more in general in the project. The additional qualified personnel, participating to the project without requiring secondments, is not described.

From UniPisa, M. Piendibene (2003 laurea at the University of Pisa) is the responsible and most expert engineer of the AM system. He worked for several years to the SVT design, its test and commissioning and after that to the development of the 3 second generation prototypes designed for FTK. The AMBFTK board, currently under design for the new AM chip, is the third existing prototype and will be used in the FTK Demonstrator. S. Donati is an experienced physicist that had an important role in the construction, commissioning and operation of SVT at CDF where he was also the trigger coordinator. Piendibene and Donati will transfer knowledge of the FTK project outside UniPisa with their secondments, in particular to PRIELE to make them sufficiently expert to lead the Production of new prototypes.

The other key person holding a large experience on SVT and FTK is F. Crescioli (Ph.D. in Applied Physics in 2010 at the University of Pisa). He was very recently recruited by CNRS. He had an important role in the SVT upgrade as responsible of the Giga Fitter, a single board that replaced the old 12 Track Fitters and performed 10<sup>9</sup> track fits per second. Crescioli had also a key role in developing the FTK simulation package, designing the AMchip, and organizing the vertical slice environment for tests.

From AUTH, SAMPSONIDIS D. (Ph.D. in 1995 Experimental Particle Physics at AUTH), Assistant Professor and KORDAS, Konstantinos (Ph.D. in Experimental Particle Physics from McGill University in Canada in 2000), Lecturer, are the two expert physicists that will be deeply involved in the Micromegas detector for the upgrade of the muon spectrometer at SLHC, including the Level 1 trigger application. Their curricula below demonstrate the quality of their research, their interest in the ATLAS upgrades, but also their need of learning in the area of FTK applications. Sampsonidis worked as Research Associate at CNRS at Strasbourg (France) and at CERN. In 1996 he joined the ATLAS group of Thessaloniki and worked on the construction of the chambers of the muon spectrometer. His research activity is focussed in detector instrumentation and GRID applications. He is actively involved in the ATLAS bphysics. The results of his research have been published in more than 150 papers in international scientific journals and conference proceedings. Kordas worked at the CDF experiment at Fermilab, implementing a dedicated penguin trigger at L2 and L3 and searching for penguin decays of B mesons in the data. In 2000 he joined the ATLAS experiment at CERN, as Research Associate at LAL, Orsay, France, working on the electromagnetic liquid Argon calorimeter simulation. In 2002-2004 he went back to CDF as Research Associate at the University of Toronto, where he measured the mass of the top quark. Since then he has been working on the ATLAS TDAO; initially as Research Associate at INFN Frascati Laboratories (Italy), and then with the University of Bern (Switzerland). Since 2010 he has been a faculty member at the Aristotle University of Thessaloniki. He is still working on the ATLAS TDAQ and participating to analyses with an interest in Di-boson, Higgs and physics beyond the Standard Model. Since December 2011 he coordinates the ZZ $\rightarrow$ 4 leptons analysis. He is interested in the TDAQ upgrade projects and in the detector upgrade activities (Micromegas).

The last experienced researchers that will participate to secondments are the engineer Stefano Petrucci (CAEN) and the physicist Giovanni Calderini (CNRS). Stefano Petrucci started his activity in electronics in 1997 as power supply designer for nuclear physics in CAEN; in 2000 he became vice-coordinator of the power supply system design for LHC experiments. In 2004 he became the person in charge for the entire power supply system of all the 4 LHC experiments. Since 2009 he is the CAEN responsible for regional, national and international funded projects. He has the perfect background to learn about FTK, to lead the integration WP and to help in commissioning at CERN. Giovanni Calderini, the ATLAS/SLHC LPHNE group leader, had a leading role in the Babar silicon vertex design, test and commissioning.

In addition a team of young researchers will be seconded together with the experienced group. They provide the manpower necessary to face the big project effort. FTK is a great opportunity to gain an important position in this emerging technology that will offer opportunities during its expansion in ATLAS and other experiments. These curricula shows the young research group quality and background.

#### From AUTH Atlas group:

SIDIROPOULOU O., MS student, studied two years Information Systems & Web Development in a Business and Computing School in Thessaloniki, Natural Sciences in the Hellenic Open University of Greece from 2006 to 2011. Her BSc thesis subject was "Development of a Data Acquisition System using the GPIB protocol with Labview". The application was implemented in the Nuclear Physics Laboratory in the Aristotle University of Thessaloniki, where she is currently a MS student in Computational Physics.

**From AUTH electronics group**: VOUDOURIS L., Ph.D. student, was graduated (2005) and received his M.Sc. in Electronic Physics in Physics Department of Aristotle University of Thessaloniki (2008), specializing in Electronic Circuit Technology with the thesis "". Now he is Ph.D. candidate on the subject "Development of optimal digital systems design methodology on reconfigurable devices". His research interests include optimal design on reconfigurable devices and real time image/video processing.

SOTIROPOULOU C., Ph.D. student, graduated (2005) with a CGPA 8.88/10 and received a M.Sc. Diploma in Electronics specializing in the Technology of Electronic Circuits, (2008, CGPA: 9.08/10) in the Physics Department of the Aristotle University of Thessaloniki. She is a Ph.D. candidate. Her research area is multiprocessing systems design and methodology for application implementation and hardware/software co-design. She works as a primary researcher for the Greek Ministry of Development and EU funded research projects "Corallia LoC: Lab On Chip" and "JEWEL: Jordan Europe Wide Enhanced Links in ICT". She is an experienced programmer in C/C++ & hardware description languages (HDLs).

KONSTANTAKOS V., Adjoint Lecturer, received his MSc Diploma (2005) in Electronic Physics (Radioelectrology) and his Ph.D. degree (2010) from the Physics Department of Aristotle University of Thessaloniki where he is now working as an adjunct Lecturer. He has published about 15 papers in conference proceedings and journals. His research is related to system design of automated low power instrumentation systems, measurements and techniques for the energy consumption estimation, evaluation of the good operating condition of electronic circuits based on energy measurements, and sensors technologies, PCB implementation.

#### From PRIELE:

A. SAKELLARIOU, Electrical & Computer Engineering, Aristotle University. Member of the R&D Sector of Prisma Electronics since 2009, experienced in design/simulation of Low-Noise Amplifiers in high frequencies, in design of VLSI subsystems and in the examination of RF amplifiers (CADENCE, Spice, Agilent ADS). Performs schematic capturing and physical layout, of multilayer PCBs, simulation of RF structures, like analog transceivers. Participates in national and EU research programs: NextGenMiliWave (design and development 60GHz communication), Hypersol (developing of hyper-fine solder powders for miniaturized consumer electronics), Nanorganic (development of organic photovoltaic systems).

D. DIMAS Physicist in AUTH and MSc in Electronics Physics (2008), currently working on his Ph.D. thesis (development of photonic sensors for wireless sensor networks). Researcher of the R&D sector of Prisma Electronics since 2009, mostly involved in software-hardware development especially for embedded devices and firmware, participates in national and EU projects: MEMSENSE (Development of Innovative Sensor Systems Offering Distributed Intelligence), MEDOUSA (Autonomous fiber sensors for aquaculture quality control), WELCOM (Wireless Sensors for Engineering Asset Life Cycle Optimal Management), VASIS (Value Added Services Integrated System Based on Optical Sensors of FTTH Infrastructure).

K. I. MERMIKLI, Electrical & Computer Engineering, AUTH. She has been a Researcher in Prisma Electronics since 2010 involved in EU and national R&D projects. She has embedded software development capabilities and good knowledge of C, C++, C#, Java, Assembly, Matlab, Linux, Mac OS X, MS SQL Server, Oracle SQL Developer, SPICE, SPSS. Project Manager in all CERN projects. Currently involved in CERN ATLAS WPSS project.

KALAITZIDIS P., Electrical & Computer Engineering, Democritus University of Thrace (DUTH). He has been a member of Prisma Electronics since 2007 as Production Manager. He undertakes all Space & Defense complex projects as well as CERN productions. Experienced in production materials and electronics board behaviour in hard environment. Highly skilled in setting up test kits and run functional tests on PCBs and/or electronic devices. He has very good knowledge of Embedded programming (C, C++) and programming with PHP. Currently involved in CERN RD51 manufacturing and test project.

| Work<br>package<br>No | Work package title                             | Lead<br>Beneficiary | Type of<br>activity | Start-End<br>month |

|-----------------------|------------------------------------------------|---------------------|---------------------|--------------------|

| 1                     | Prototype Construction & Production Validation | PRIELE              | RTD                 | M1-M42             |

| 2                     | Infrastructure & Integration                   | CAEN                | ToK                 | M1-M48             |

| 3                     | Commissioning                                  | CERN                | RTD                 | M12-M48            |

| 4                     | Architecture Simulation                        | UniPisa             | RTD                 | M1-M48             |

| 5                     | Image Processing                               | UniPisa             | RTD                 | M25-M48            |

| 6                     | Silicon Detectors                              | CNRS                | RTD                 | M1-M48             |

| 7                     | Outreach                                       | AUTH                | DISS                | M1-M48             |

| 8                     | Workshops & Trainings                          | AUTH                | TR                  | M1-M48             |

# **B.4 Implementation**

# **B.4.1. List of Work Packages**

### **B.4.2.** Work Packages description

| Work package number    | 1                                              | Planned start date: | 1 <sup>st</sup> day of M1 |

|------------------------|------------------------------------------------|---------------------|---------------------------|

| Work package title     | Prototype Construction & Production Validation |                     |                           |

| Beneficiary short name | Ma                                             |                     |                           |

#### Objectives

**O.1.1.** Construction of SLP prototypes

**O.1.2.** ToK to PRIELE for board assembly and validation before integration or commissioning

**O.1.3. Standalone validation of SLP prototypes**

**O.1.4. Standalone validation of FTK production**

O.1.5. ToK between research institutions about AM technology

#### **Description of work**

**T.1.1.** Installation of an FTK test stand at PRIELE and AUTH for board validation tests & ToK

**T.1.2.** Design of SLP2 PC boards (schematic capture, layout & routing with Cadence tools)

**T.1.3.** Design of SLP2 firmware (HDLs language and use of Xilinx CAD)

T.1.4. SLP2 PCB construction

T.1.5. SLP2 assembly at PRIELE

T.1.6. Standalone validation of SLP2 at PRIELE before integration at CAEN

**T.1.7.-T.1.11.** Same tasks for SLP1 as T1.2-T.1.6 for SLP2

T.1.12. Validation of 1<sup>st</sup> FTK production

#### **Deliverables and Milestones**

- **D.1.1.** SLP2 prototype constructed at PRIELE delivery date M12

- **D.1.2.** 1<sup>st</sup> FTK production assembled at PRIELE delivery date M32

- **D.1.3.** SLP1 prototype constructed at PRIELE delivery date M36

- **D.1.4**. 2<sup>nd</sup> FTK production assembled at PRIELE delivery date M42

- M.1.1. SLP2 prototype validated at PRIELE M12

- M.1.2. FTK Technical Design Report: Atlas evaluation of FTK prototypes M12

- **M.1.3.**  $1^{st}$  FTK production validated at PRIELE M32

- M.1.4. SLP1 prototype validated at PRIELE M36

- M.1.5. 2<sup>nd</sup> FTK production validated at PRIELE M42

#### **Seconded Fellows**

MER 1 Piendibene – From Partner UniPisa to PRIELE – Month 7 to 8

Expertise: AM system responsibility; PC board and firmware design; quality assurance.

Tasks where involved: T.1.1, T.1.2, T.1.3 (M.1.1 SLP2 validated at Priele); T.1.12 (M.1.3 FTK prod)

MER 2 Donati – From Partner UniPisa to PRIELE – Month 8 to 9; Month 23-24.

Expertise: AM system; PC board and firmware design; quality assurance.

Tasks where involved: T.1.1, T.1.2, T.1.3 (M.1.1 SLP2 validated at Priele);

ER 3 Konstantakos – From Partner AUTH to PRIELE – Month 5 to 6; 10 to 11; 20 to 21

Expertise: automated low power instrumentation systems; energy consumption estimation; PC board implementation.

Tasks where involved: T.1.2, T.1.3 (M.1.1 SLP2 validated at Priele); T.1.7, T.1.8 (M.1.4 same SLP1)

ER 4 Voudouris - From Partner AUTH to PRIELE - Month 11 to 12

Expertise: Design of Reconfigurable Processors.

Tasks where involved: T.1.3 SLP2 firmware (M.1.1)

ER 5 Dimas

From Partner PRIELE to UniPisa - Month 5 to 6

From Partner PRIELE to AUTH – Month 8 to 9

Expertise: embedded devices and firmware

Tasks where involved: T.1.3 SLP2 firmware (M.1.1)

ER 6 Sakellariou

From Partner PRIELE to UniPisa – Month 3 to 4; Month 26 to 27; Month 29 to 30

Expertise: schematic capturing and physical layout of multilayer PCBs

Tasks where involved: T.1.2 SLP2 PC design (M.1.1); T.1.7 SLP1 PC design (M.1.4)

From Partner PRIELE to AUTH – Month 22 to 23

Tasks where involved: T.1.7 SLP1 PC design (M.1.4)

ER 7 Kalaitzidis

From Partner PRIELE to AUTH – Month 31 to 32

Expertise: setting up test kits and run functional tests on PCBs and/or electronic devices

Tasks where involved: T.1.11 SLP2 tests at Priele (M.1.4)

ESR 8 Mermikli

From Partner PRIELE to UniPisa - Month 14 to 15

Expertise: setting up test kits and run functional tests on PCBs and/or electronic devices

Tasks where involved: T.1.12 SLP2 firmware (M.1.3)

#### **Recruited Fellows**

**ER 9** – Partner AUTH– Month 13 to 36 (note: ER 9 fellow also active in WP3, WP4)

Expertise: AM technology

Tasks where involved: T.1.7, T.1.8, T.1.11 SLP1 PCB & firmware design, tests (M.1.4)

**ER 10** – Partner CERN– Month 32 to 43 (note: ER 10 fellow also active in WP3)

Expertise: AM technology

Tasks where involved: T.1.7, T.1.8, T.1.11 (M.1.4) SLP1 PCB & firmware design, tests at CERN

#### **Risk Analysis**

**M.1.1.** Risk: SLP2 validation fails; it looses the possibility to be used in the FTK demonstrator. Action: (a) the demonstrator can be based on existing AMBFTK boards; (b) SLP2 design will be fixed and a second prototype built.

**M.1.2.** Risk: Atlas review of entire FTK system fails (extremely unlikely). Action: this project continues on R&D items to be used for longer-term goals (L1 applications for muons, for Phase II LHC upgrade, and Image Processing outside HEP); productions D.1.2 and D.1.4 will be dropped.

**M.1.3.** Risk: major fault found in produced boards. Action: investigate and solve the problem, then repeat the production. In this case we will propose to ATLAS a later commissioning to be approved by the experiment.

**M.1.4.** Risk: SLP1 validation fails; it looses the possibility to be used in the Atlas muon upgrade. Action: evaluate the opportunity to continue L1 R&D with a second SLP1 prototype during the last year.

**M.1.5.** Risk: major fault in production due to factory responsibility. Action: propose to ATLAS a later commissioning to be approved by the experiment.

| Work package number    | 2                             | Planned start date: | 1 <sup>st</sup> day of M1 |

|------------------------|-------------------------------|---------------------|---------------------------|

| Work package title     | Infrastructures & Integration |                     |                           |

| Beneficiary short name | CAEN                          |                     |                           |

Objectives

**O.2.1.** Infrastructure construction and validation: racks, crates, power supplies, cooling system

O.2.2. Integration of prototypes from Europe, Japan and USA, validation before production

O.2.3. Software development for system control, monitoring, and test

**O.2.4.** ToK between CAEN and research institutions for integration, commissioning, and maintenance

O.2.5. ToK between research institutions about FTK technology for any kind of applications

#### **Description of work**

- **T.2.1.** Installation of a vertical slice (VS) at CAEN for board integration, validation tests & ToK

- **T.2.2.** Prototyping of a CAEN power supply for the final crate (5kW)

- T.2.3. Software development for tests of the VS

- T.2.4. Tests and validation of the baseline FTK system for the demonstrator

- T.2.5. Tests and validation of the SLP2-based system

- T.2.6. Tests and validation of the SLP1-based system

- T.2.7. Tests of cooling and mechanics of a rack with complete final crates

#### **Deliverables and Milestones**

- D.2.1. VS infrastructure at CAEN for FTK demonstrator integration delivery date M6

- D.2.2. FTK demonstrator fully integrated with old power supply delivery date M12

- D.2.3. CAEN power supply ready for integration delivery date M18

- D.2.4 FTK cooling and mechanical tests completed delivery date M20

- **D.2.5.** SLP2 fully integrated delivery date M20

- D.2.6 SLP1 fully integrated delivery date M48

- M.2.1. FTK demonstrator running flawlessly at CAEN M12

- M.2.2. SLP2-based FTK running flawlessly at CAEN M20

- M.2.3. Infrastructure (crate, cooling, power supplies, mechanics) validated M20

- M.2.4. Comparison and choice between FTK baseline and SLP2 systems M20

- M.2.5. SLP1-based FTK running flawlessly M48

#### **Seconded Fellows**

MER 1 – Piendibene - From Partner UniPisa to CAEN – Month 10 to 20, Month 29, 33

Expertise: Integration responsibility; test, firmware design; quality assurance.

Tasks where involved: T.2.1., T.2.3., T.2.4., T.2.5. (M.2.1., M.2.2. FTK demo & SLP2 running flawl.)

MER 11 Kordas- From Partner AUTH to CAEN - Month 4 to 5, Month 39 to 40.

Expertise: Trigger and Data acquisition

Tasks where involved: T.2.4. FTK demo tests (M.2.1.); T.2.6 SLP1 tests (M.2.5)

MER 12 Sampsonidis – From Partner AUTH to CAEN – Month 41 to 42.

Expertise: Grid and muon detectors

Tasks where involved: T.2.6 SLP1 tests (M.2.5)

ESR 13 Sidiropoulou – From Partner AUTH to CAEN – Month 38 to 40

Expertise: Grid and data acquisition

Tasks where involved: T.2.6 SLP1 tests (M.2.5)

ER 4 Voudouris – From Partner AUTH to CAEN – Month 4 to 5, Month 16 to 17

Expertise: Design of Reconfigurable Processors.

Tasks where involved: T.2.4. FTK demo tests (M.2.1.); T.2.5. SLP2 tests (M.2.2.)

**ER 13** Sotiropoulou – From Partner AUTH to CAEN – Month 4 to 5, Month 15 to 17

Expertise: multiprocessing systems design and methodology for application, implementation and hardware/software co-design

Tasks where involved: T.2.4. FTK demo tests (M.2.1.); T.2.5. SLP2 tests (M.2.2.)

**ER 14** Crescioli – From Partner CNRS to CAEN – Month 7 to 8, Month 12 to 13, Month 20 to 21, Month 36 to 37.

Expertise: AM system, firmware, tests, software and GRID

Tasks where involved: T.2.4. FTK demo tests (M.2.1.); T.2.5. SLP2 tests (M.2.2.), T.2.6 SLP1 tests (M.2.5)

#### **Risk Analysis**

**M.2.1** Risk: problems detected in the FTK demonstrator. Action: Solve the problems and move commissioning start at CERN to a later date (maximum delay allowed by contingency is 8 months).

M.2.2 Risk: problems detected in the SLP2-based FTK. Action: Choose baseline technology

M.2.5 Risk: major problems in the SLP1-based FTK. Action: This system is not suitable for ATLAS

| Work package number    | 3             | Planned start date: | 1 <sup>st</sup> day of M12 |

|------------------------|---------------|---------------------|----------------------------|

| Work package title     | Commissioning |                     |                            |

| Beneficiary short name | CERN          |                     |                            |

#### **Objectives**

**O.3.1.** Infrastructure Installation and validation at point 1: racks, crates, power supplies, cooling system

**O.3.2.** Board installation and validation

**O.3.3. Running control and functional monitoring**

**O.3.4.** ToK between CAEN and research institutions for board commissioning and maintenance

**O.3.5.** ToK between research institutions about FTK technology for any kind of future application

#### **Description of work**

**T.3.1.** Installation of Infrastructures, validation tests & ToK

T.3.2. Installation of boards (SLP2 or FTK baseline) for the demonstrator

T.3.3. Tests and validation of the FTK demonstrator

T.3.4. T.3.5 as T.3.2, T.3.3. for the first production

**T.3.6. T.3.7.** as **T.3.2**, **T.3.3**. for the second production

#### **Deliverables and Milestones**

**D.3.1.** FTK demonstrator commissioned – delivery date M22

**D.3.2.** FTK first production commissioned – delivery date M34

D.3.3. FTK second production commissioned - delivery date M46

M.3.1. FTK demonstrator running flawlessly inside Atlas- M24

M.3.2. FTK first production running flawlessly inside Atlas – M36

M.3.3. FTK second production running flawlessly inside Atlas – M48

#### **Seconded Fellows**

ESR 8 Mermikli – From Partner Priele to CERN – Month 18 to 19

Expertise:

Tasks where involved: T.3.1. (M.3.1.) FTK Demo commissioning

**MER 14** Petrucci– From Partner CAEN to CERN –Month 18 to 19, Month 33 to 34, Month 43 to 44 Expertise:

Tasks where involved: T.3.1., T.3.2, T.3.3. FTK demo comm & 1<sup>st</sup>, 2<sup>nd</sup> FTK comm.. (M.3.1.), (M.3.2)

#### **Recruited Fellows**

ER 10 –Partner CERN– Month 32 to 43 (note: ER 10 already inserted in WP1, also active in WP1)

Expertise: AM technology

Tasks where involved: T.2.6., T.2.7., (M.2.3.) commissioning at CERN

#### **Risk Analysis**

**M.3.1., M.3.2., M.3.3.** Risk: any kind of failure at level of commissioning will produce the same action: understand the problem and fix it, requiring extra time to Atlas for the final activation.

| Work package number    | 4          | Planned start date: | 1 <sup>st</sup> day of M1 |

|------------------------|------------|---------------------|---------------------------|

| Work package title     | Simulation |                     |                           |

| Beneficiary short name | UniPisa    |                     |                           |

#### Objectives

O.4.1. Definition of L1, L2 architectures optimizing the physics reach

O.4.2. Validation of tests: production of test vectors to validate HW configurations

#### **Description of work**

- **T.4.1.** SW simulation of the HW details of the FTK demonstrator

- **T.4.2** Production of test vectors for the FTK demonstrator

- **T.4.3.** Production of test vectors for the SLP2 based FTK

- **T.4.4.** Study of high level event selection algorithms based on FTK tracks

- T.4.5. Study of the L1 Muon Trigger architecture

- T.4.6. Production of test vectors for the SLP1 based FTK

#### **Deliverables and Milestones**

- D.4.1. FTK Demonstrator detailed simulation delivery date M9

- D.4.2. Test Vectors for the FTK demonstrator delivery date M10

- D.4.3. Test Vectors for the SLP2 based FTK delivery date M16

- **D.4.4.** Trigger table for FTK demonstrator with performance prediction delivery date M25

- D.4.5. SLP1 architecture simulation delivery date M28

- **D.4.6.** SLP1 detailed simulation delivery date M38

- **D.4.7.** Test Vectors for the SLP1 based FTK delivery date M42

- M.4.1. FTK Demonstrator simulated in its general architecture M6

- M.4.2 Predicted trigger performances meet Atlas requirements M26

- M.4.3. Approval of SLP1 architecture in Atlas M30

#### Seconded Fellows

MER 12 Sampsonidis – From Partner AUTH to CAEN – Month 15 to 16.

Expertise: Grid and muon detectors

Tasks where involved: T.4.1 SLP1 simulation and architecture studies & tests (M.2.5)

ESR 13 Sidiropoulou - From Partner AUTH to CAEN - Month 15 to 17

Expertise: Grid and data acquisition

Tasks where involved: T.4.1 SLP1 tests (M.4.1)

#### **Recruited Fellows**

**ER 15** – Partner UniPisa– Month 10 to 29

Expertise: FTK system simulation, FTK architecture

Tasks where involved: T.4.3.-T.4.6.

#### **Risk Analysis**

**M.4.1.** Risk: general simulation not ready. Action: increase manpower to satisfy test vector deliveries.

**M.4.2** Risk: predicted trigger performances do not meet Atlas requirements, FTK could be rejected. Action: FTK productions could be dropped, R&D program would continue

**M.4.3.** Risk: SLP1 architecture rejected by Atlas . Action: correct the architecture to satisfy Atlas requirements.

| Work package number    | 5                | Planned start date: | 1 <sup>st</sup> day of M25 |

|------------------------|------------------|---------------------|----------------------------|

| Work package title     | Image Processing |                     |                            |

| Beneficiary short name | UniPisa          |                     |                            |

#### Objectives

**O.5.1.** Test AM real time capability to extract relevant features of natural and medical images

**O.5.2.** Evaluate the impact on medical imaging and diagnosis

**0.5.3.** Evaluate the impact on robotic automation

#### Description of work (brief description; possibly broken down into tasks)

- T.5.1. Installation of a separate crate and AM system at CAEN for image processing

- T.5.2. Production of software and firmware for image formatting and system training

- T.5.3. Evaluate performances of natural still image processing

- **T.5.4.** Perform tests on moving image processing

- T.5.5. Perform tests on medical image processing

#### **Deliverables and Milestones**

- D.5.1. Infrastructure at CAEN for Image Processing delivery date M26

- **D.5.2.** Software & firmware ready for training and image processing delivery date M30

- D.5.3. Performances of natural still image processing delivery date M34

D.5.4. Results of tests on movie processing - delivery date M40

- **D.5.5.** Results of tests on medical image processing delivery date M48

- M.5.1. Hardware still-image processor running flawlessly M34

- M.5.2. Filtering and data reduction of natural movies running flawlessly M40

- **M.5.3.** Procurement of medical image data M42

#### **Recruited Fellows**

ER 16 – Partner UniPisa– Month 26 to 43

Expertise: AM system, FTK architecture, image processing

Tasks where involved: T.5.2., T.5.3., T.5.4., T.5.5.

#### **Risk Analysis**

**M.5.1.** Risk: Hardware still-image processor not working as expected. Action: understand the problem and fix it, reducing the time available for users inside the project time window.

**M.5.2.** Risk: the movie processing is not producing the expected results. Action: try more to understand problems and fix them, reducing the time available for medical image processing

M.5.3. Risk: we fail to procure medical image data. Action: drop this part of the program.

| Work package number    | 6                | Planned start date: | 1 <sup>st</sup> day of M8 |

|------------------------|------------------|---------------------|---------------------------|

| Work package title     | Silicon Detector |                     |                           |

| Beneficiary short name | CNRS             |                     |                           |

#### Objectives

O.6.1. CAEN Power supply (PS) optimization for Phase-II LHC pixel detectors

#### **Description of work**