# HDSoC (High Density Digitizer System on Chip) Status

Nov. 4, 2025

Aera Jung<sup>1</sup>, Ben Rotter<sup>2</sup>, Luca Macchiarulo<sup>2</sup>, Marcus Luck<sup>2</sup>, Christopher Chock<sup>2</sup>, Isar Mostafanezhad<sup>2</sup>, Jennifer Ott<sup>3</sup>, Boris Murmann<sup>3,1</sup>

<sup>&</sup>lt;sup>1</sup> Department of Physics and Astronomy, University of Hawai'i at Mānoa, Honolulu, HI 96822, USA

<sup>2</sup> Nalu Scientific, LLC, Honolulu, HI, 96822, USA

<sup>&</sup>lt;sup>3</sup> Department of Electrical and Computer Engineering, University of Hawai'i at Mānoa, Honolulu, HI 96822, USA

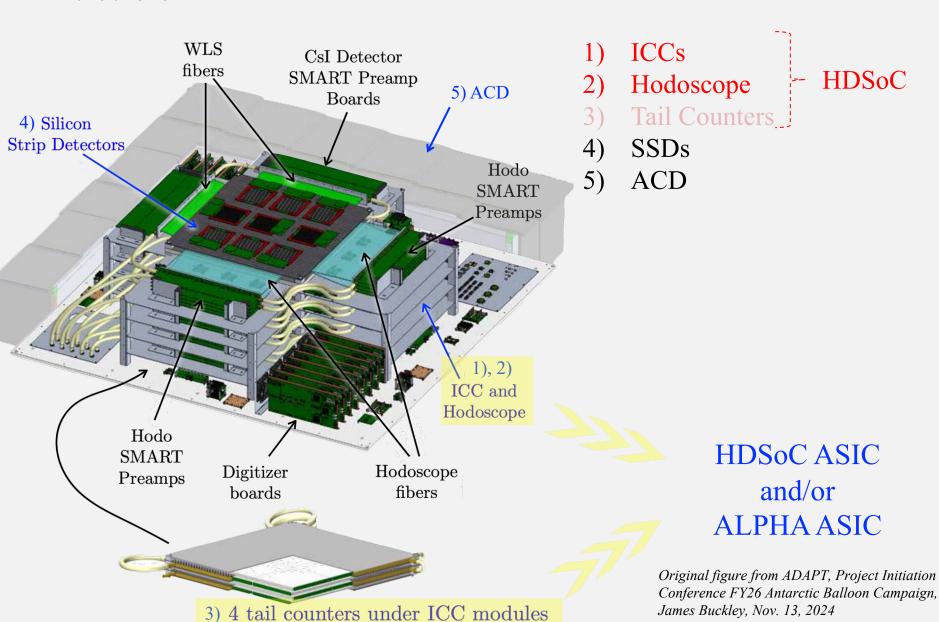

### Detectors

- Mar. 2023: ALPHA v2 was submitted.

- May 2023: 40 ALPHA v2 ASICs arrived at UH from company.

- and designed ALPHA, passed away on July 14, 2023.

July 2023: Gary Varner, professor of physics and astronomy at the UH and built

- Oct. 2023: The ALPHA v2 ASIC test board modified in WashU has arrived Oct. 19, 2023.

- Oct. 23, 2023 ~ now: ALPHA v2 debugging.

- Nov. 2023: Boris proposed the HDSoC made by Nalu company on 1<sup>st</sup> ADAPT collaboration meeting.

- Dec. 2023 ~ Dec. 2025: Boris' group ran several tests related to the HDSoC together with Nalu company and nearly complete.

- May 2024 ~ Mar. 2025: 75 HDSoC chips procured and readout boards developed at WashU.

- Jan.  $2025 \sim$  now: readout boards fabbed & assembled at WashU and special FW developed at WashU with help from Nalu.

- Jan. 16, 2025 ~ now: Jennifer's group is primarily/mainly leading the testing of the ALPHA and also includes HDSoC.

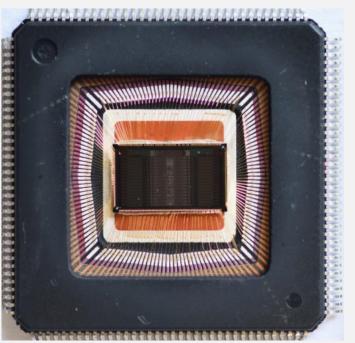

### HDSoC ASIC

## HDSoC (High Density Digitizer System on Chip) description

| Technology          | CMOS 250 nm                      |

|---------------------|----------------------------------|

| Voltage Supply      | 2.5V                             |

| Input voltage range | 0.5-2.2V                         |

| Power consumption   | 20-47mW/ch                       |

| Package             | QFP 144-pin package (22 mm side) |

| Sampling Rate       | 1 – 1.8 GSPS                     |

HDSoC ver. 1 package

- Specifications:

- DLL (Delay-Locked Loop) based timing for the sampling

- Dynamic range: large dynamic range with 12 bits resolution

- Noise: low noise

- Power consumption: low power consumption

- Sampling frequency: ~250MHz up to ~1.8GHz

- Readout channels: 32ch (for ver. 1), 64ch (for ver. 2)

### HDS<sub>0</sub>C ASIC

# • Large number of adjustable parameters

| • | analog_registers |

|---|------------------|

|   | bufbias_bias_0   |

|   | bufbias_bias_1   |

|   | bufbias_bias_10  |

|   | bufbias_bias_11  |

|   | bufbias_bias_12  |

|   | bufbias_bias_13  |

|   | bufbias_bias_14  |

|   | bufbias_bias_15  |

|   | bufbias_bias_16  |

|   | bufbias_bias_17  |

|   | bufbias_bias_18  |

|   | bufbias_bias_19  |

|   | bufbias_bias_2   |

|   | bufbias_bias_20  |

|   | bufbias_bias_21  |

|   | bufbias_bias_22  |

|   | bufbias_bias_23  |

|   | bufbias_bias_24  |

|   | bufbias_bias_25  |

|   | bufbias_bias_26  |

|   | bufbias_bias_27  |

|   | bufbias_bias_28  |

|   | bufbias_bias_29  |

|   | bufbias_bias_3   |

|   | bufbias_bias_30  |

|   | bufbias_bias_31  |

|   | bufbias_bias_4   |

|   | •                |

| ľ | of adjusta          |

|---|---------------------|

|   | trigger_threshold_4 |

|   | trigger_threshold_5 |

|   | trigger_threshold_6 |

|   | trigger_threshold_7 |

|   | trigger_threshold_8 |

|   | trigger_threshold_9 |

|   | ts_left             |

|   | ts_right            |

|   | tsel_left           |

|   | tsel_right          |

|   | tsgn_left           |

|   | tsgn_right          |

|   | vadjn_left          |

|   | vadjn_right         |

|   | vadjp_left          |

|   | vadjp_right         |

|   | vanbuf_left         |

|   | vanbuf_right        |

|   | vapbuf_left         |

|   | vapbuf_right        |

|   | wrstrb1_le_left     |

|   | wrstrb1_le_right    |

|   | wrstrb1_te_left     |

|   | wrstrb1_te_right    |

|   | wrstrb2_le_left     |

|   | wrstrb2_le_right    |

|   | wrstrb2_te_left     |

|   | wrstrb2_te_right    |

|   |                     |

|   | Parameters         |

|---|--------------------|

| • | digital_registers  |

|   | chanmask0          |

|   | chanmask1          |

|   | chanmask2          |

|   | chanmask3          |

|   | convertresetwait   |

|   | dig_to_an          |

|   | idconfig           |

|   | readoutchannels    |

|   | readoutlookback    |

|   | readoutwindows     |

|   | regclr_bk          |

|   | regclr_chan        |

|   | reglatchperiod_bk  |

|   | reglatchperiod_cha |

|   | regloadperiod_bk   |

|   | regloadperiod_char |

|   | regmisc            |

|   | regspeed           |

|   | regwaitaddr        |

|   | regwaitread        |

|   | scal0              |

|   | scal1              |

|   | scal10             |

|   | scal11             |

|   | scal12             |

|   | _                  |

```

pclk

pclkwidth

pedram_addr

pedram_data

pg_2v5

reg_data0

reg_data1

regclr

rx_en

sel

ser_rx_crc_en

ser_rx_div

ser_rx_eof_en

ser_rx_neg_pol

ser_tx_clk_locked

ser_tx_neg_pol

stopacq

sysrst

t user

timeout15_0

timeout31_16

tx_en

tx_mode

version

wave_fifo_rst

write_address

```

| * | control_registers    |

|---|----------------------|

|   | 1v2_en               |

|   | 2v5_en               |

|   | 3v3_i2c_en           |

|   | analog_debug_disable |

|   | asic_clk_locked      |

|   | auto_numwinds_en     |

|   | ch_en15_0            |

|   | ch_en31_16           |

|   | clk1v8_en            |

|   | clk2v5_en            |

|   | clk_i2c_sel          |

|   | clk_intr_n           |

|   | clk_lol_n            |

|   | clk_oeb              |

|   | clk_reset            |

|   | clk_sync             |

|   | debug_addr           |

|   | debug_data           |

|   | dhcp_addr15_0        |

|   | eth_addr_sel         |

|   | eth_ar_en            |

|   | eth_dest_addr15_0    |

|   | eth_dest_addr31_16   |

|   | eth_dest_port        |

|   | eth_dhcp_en          |

|   | eth_port_sel         |

|   |                      |

- Serial interface data transfer rate

- Resolution

- Timing calibration

- WashU's mother board + HDSoC daughter boards

- Serial interface data transfer rate

- Resolution

- Timing calibration

- WashU's mother board + HDSoC daughter boards

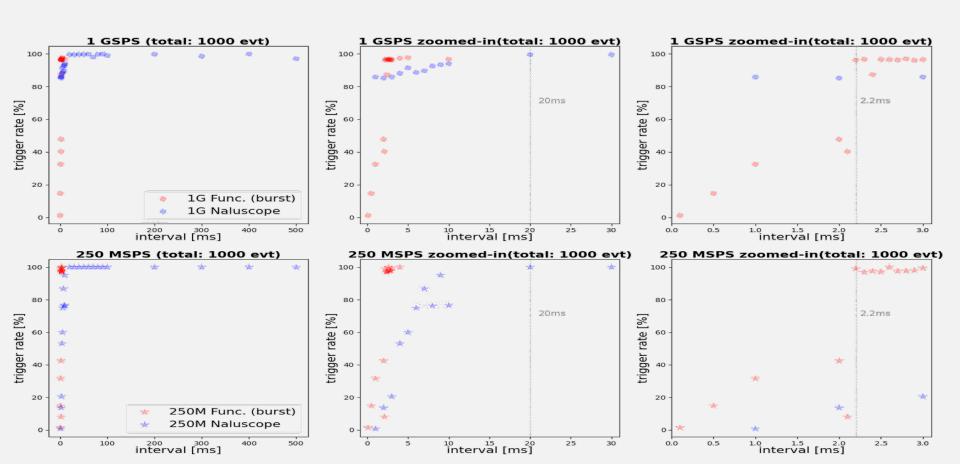

### Serial interface data transfer rate

- Parallel interface (default) → Serial interface between HDSoC and FPGA

- External trigger: Naluscope (~ 20 ms) for both 1 GSPS and 250 MSPS Func. generator (~ 2.2 ms) for both 1 GSPS and 250 MSPS

- ~33% power savings

- Residual noise rms error compared across 3 different channels

- Single photo-electron measurement

- Serial interface data transfer rate

- Resolution

- Timing calibration

- WashU's mother board + HDSoC daughter boards

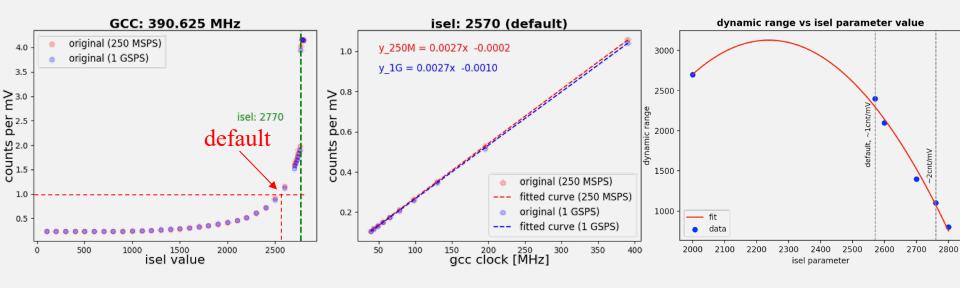

- 01

- High resolution [cnt/mV]: higher isel value and higher GCC clock speed

- High isel value: reduction in dynamic range

• Optimized value: 1 count / mV at 2570 (isel) and 390.625 MHz (GCC) for both 1 GSPS and 250 MSPS

- Reducing sampling frequency to 250MHz

- ~33% power savings

- Residual noise rms error compared across 3 different channels

- Single photo-electron measurement

- Serial interface data transfer rate

- Resolution

- Timing calibration

- WashU's mother board + HDSoC daughter boards

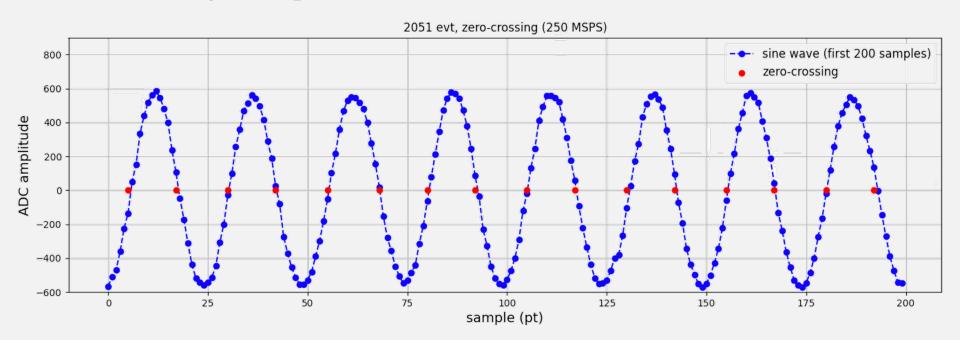

• Zero-crossing example

Input: 2V, 11.1234 MHz sine wave to 3ch splitter

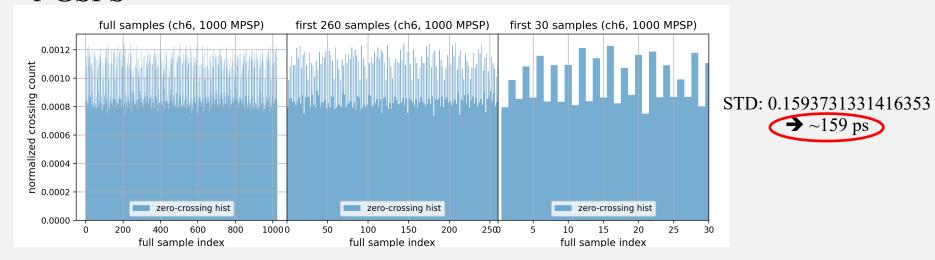

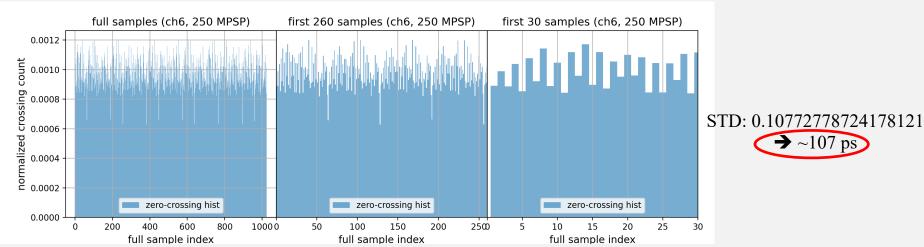

### Results of timing resolution using zero-crossing

### 1 GSPS

### • 250 MSPS

- Reducing sampling

- Reducing sampling frequency to 250MHz

- ~33% power savings

- Residual noise rms error compared across 3 different channels

- Single photo-electron measurement

- Serial interface data transfer rate

- Resolution

- Timing calibration

- WashU's mother board + HDSoC daughter boards

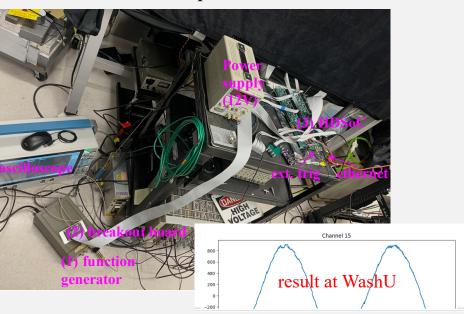

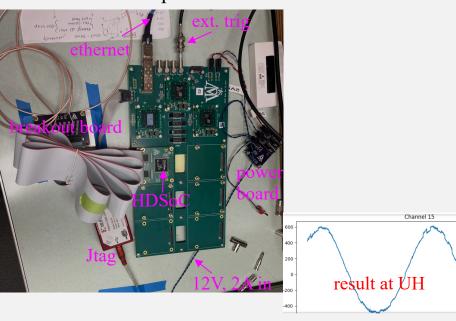

### Setup duplication at UH

- Aera visited WashU on Oct. 16-17, 2025, and we have duplicated the WashU setup in UH.

- WashU setup

01

• UH setup

- There were several issues alone the way, but thanks to Marion, we now have a working setup at UH.

- Contact people

| Ashtar Aggelopoulos | Undergraduate + master course      |

|---------------------|------------------------------------|

| Guanchen Wu         | Undergraduate + master course      |

| Lawrence Zheng      | 3 <sup>rd</sup> year undergraduate |

**←** Lawrence helped me the most.