# dRICH Back-End: FLX 182 status/updates

Francesca Lo Cicero INFN Roma, APE Lab

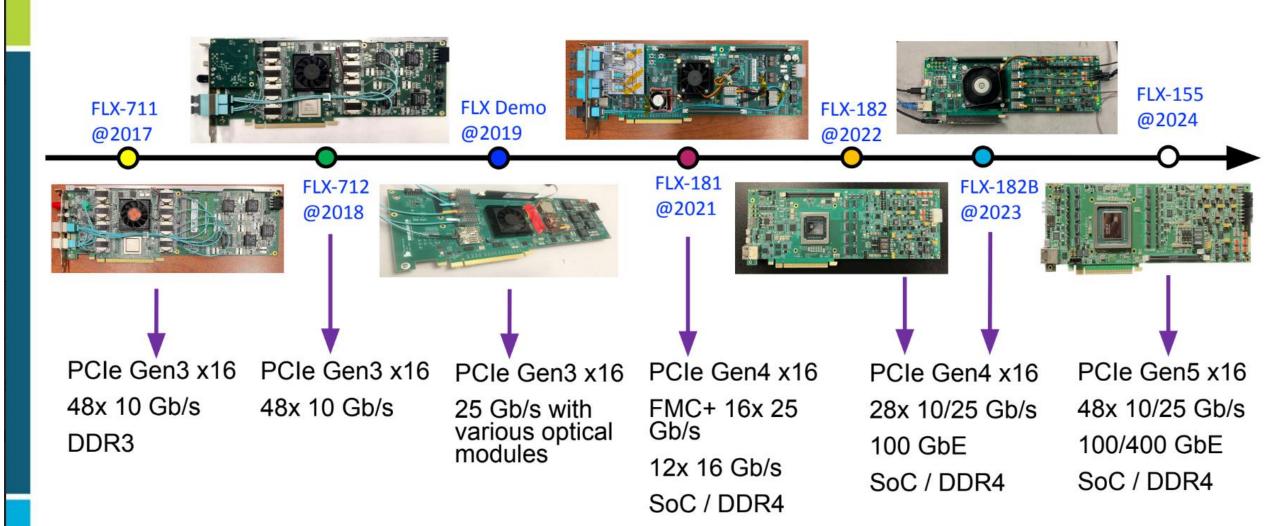

# **FELIX Hardware Development at BNL**

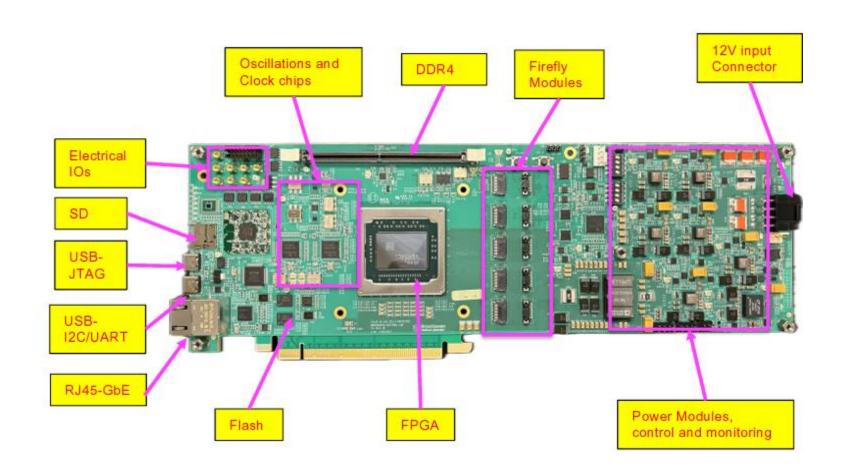

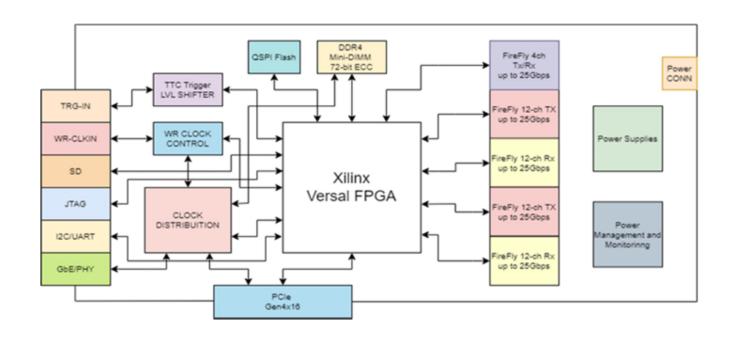

### **FLX-182B Hardware**

Assembled FLX-182B

- FPGA: Xilinx Versal Prime XCVM1802

- PCle Gen4 x16, 256 GT/s

- 24 FireFly links with 3 possible configurations

- 24 links up to 25 Gb/s

- 24 links up to 10 Gb/s (CERN-B FireFly)

- 12 links up to 25 Gb/s + 12 links up to 10 Gb/s

- 4 FireFly links with 2 possible configurations with 14 or 25 Gb/s FireFly TRx

- LTI interface

- 100 GbE

- Built-in self test, online configuration and monitoring

- White Rabbit

- DDR4 Mini-UDIMM

- GbE/SD3.0/PetaLinux

### **Procurement of a Felix-182 Card**

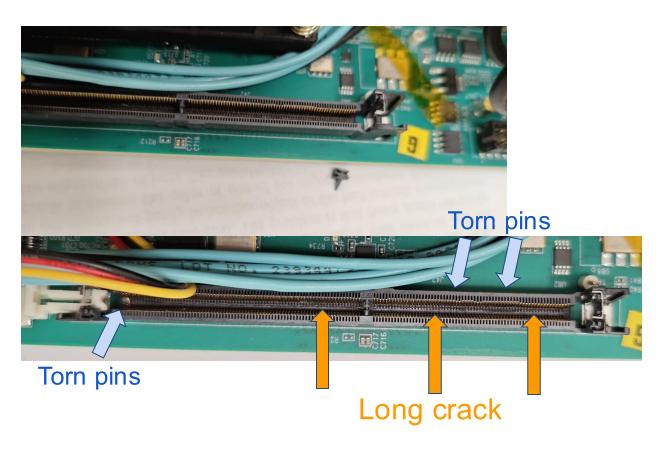

Felix-182 board on loan from Jlab arrived in Rome end of December '24 (thanks David Abbott!).

Unfortunately it showed damages to the DRAM slot:

- torn contact pins

- a crack along the inner side of the slot

They likely occurred due to the pressure of a DRAM module left in the slot during the delivery.

As a consequence, DRAM is not detected by the system.

We attempted to load official firmware onto the board (https://gitlab.cern.ch/atlas-tdaq-felix/firmware/) but the process failed due to a DRAM check error.

#### We consulted:

- the INFN Electronics Laboratory in Rome

- CERN EP-ESE Electronic Systems for Experiments (thanks Markus Joos!)

Both agreed that is extremely difficult to repair the DRAM slot and not worth the effort considering the costs and the likely not optimal result, we were ready to send it back...

# Installation of a Felix-182 Card @ APE Lab

**Homemade fix:** We experimented with various imaginative tools to better connect the DRAM.

#### The issue persisted!

• We got advice from Carlo Alberto Gottardo (Coordinator of the FELIX project) about the fact that the DRAM is used only by the PS (ARM SoC) and that in current FW versions the PS performs just ancillary functions (BIST,...), while all the design core functionalities are implemented in the PL.

**Preliminary solution:** we modified the release FW removing the PS (and DRAM) from the design -> modified FW loaded and board detected!

The issue was solely related to the unconnected DDR

### Installation of a Felix-182 Card @ APE Lab

#### Final solution:

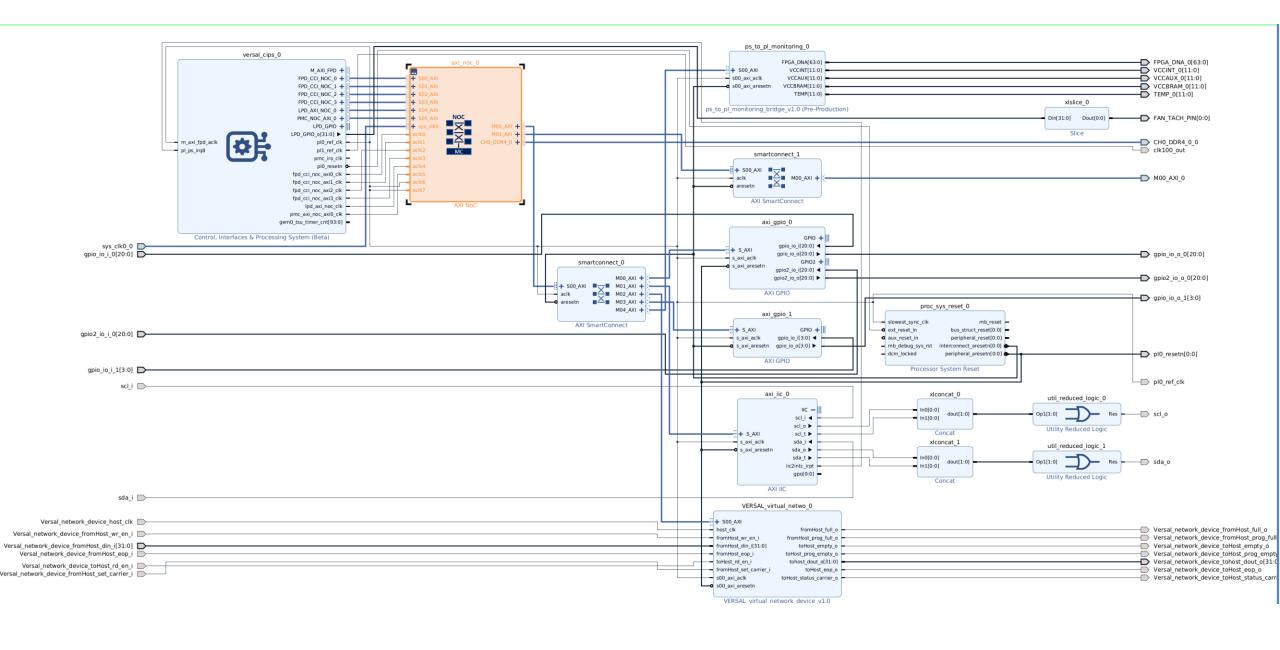

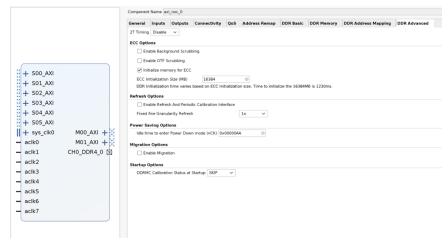

• in the FELIX-182 FW (in cips\_BD\_BNL182 block design) there is a component, the Xilinx AXI NoC that functions as a high-bandwidth scalable fabric to connect blocks. Xilinx AXI NoCcan be configured to include one or more integrated DDR

memory controllers (MCs).

Startup Options: DDRMC Calibration Status at Startup to SKIP. The default behavior for the Versal PLM at boot is to gate the assertion of the Configuration DONE signal if a DDRMC fails calibration. If this option is set to SKIP then the DDRMC calibration status will be ignored at startup and DONE will assert regardless of the DDRMC status.

#### FW loaded and board detected!

```

[locicero@apestation0 ~]$ lspci -vvvvvv | grep CERN

34:00.0 Network controller: CERN/ECP/EDU Device 0428

Subsystem: CERN/ECP/EDU Device 0038

35:00.0 Network controller: CERN/ECP/EDU Device 0427

Subsystem: CERN/ECP/EDU Device 0038

```

2 PCIe Gen4 x8 (on a bifurcated x16 slot)

## **Project Summary**

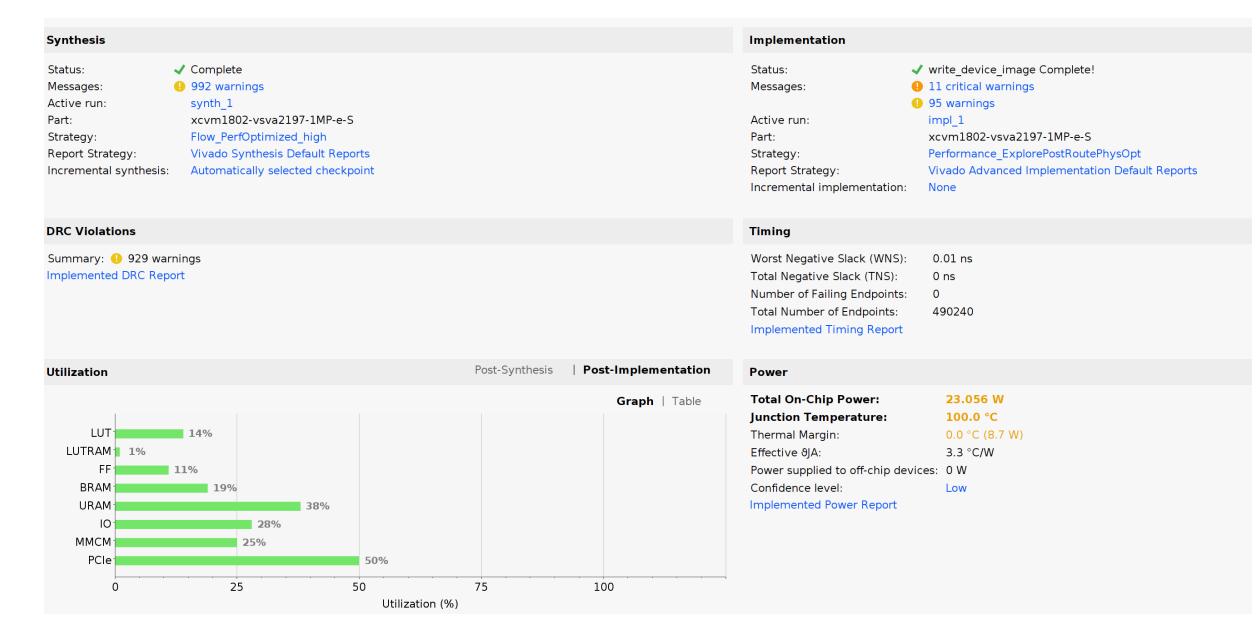

# Implementation: Report utilization

| Name                                                                                | Registers (1799680) | CLB LUTs<br>(899840) | LUT as Logic<br>(899840) | LUT as Memory<br>(449920) | LOOKAHEAD8<br>(112480) | SLICE<br>(112480) | CLB Registers<br>(1799680) | Block RAM<br>Tile (967) | URAM<br>(463) | Bonded IOB<br>(692) | BUFGCE_DIV/MBUFGCE_DIV<br>(40) | BUFG_PS/MBUFG_PS<br>(12) |

|-------------------------------------------------------------------------------------|---------------------|----------------------|--------------------------|---------------------------|------------------------|-------------------|----------------------------|-------------------------|---------------|---------------------|--------------------------------|--------------------------|

| ∨ N felix_top                                                                       | 203420              | 122179               | 116949                   | 5230                      | 1267                   | 30221             | 203420                     | 186                     | 174           | 192                 | 1                              | 2                        |

| > <b>1</b> axi_dbg_hub (axi_dbg_hub_axi_dbg_hub_0)                                  | 955                 | 669                  | 669                      | 0                         | 7                      | 177               | 955                        | 0                       | 0             | 0                   | 0                              | 0                        |

| > I axi_noc (design_axi_noc_axi_noc_0)                                              | 0                   | 0                    | 0                        | 0                         | 0                      | 0                 | 0                          | 0                       | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> busy0 (ttc_busy)                                                         | 86                  | 96                   | 96                       | 0                         | 0                      | 23                | 86                         | 0                       | 0             | 0                   | 0                              | 0                        |

| > I clk0 (clock_and_reset)                                                          | 19                  | 16                   | 16                       | 0                         | 0                      | 8                 | 19                         | 0                       | 0             | 0                   | 0                              | 0                        |

| J g_endpoints[0].crth0 (CRToHost_xdcDup_1)                                          | 8156                | 2480                 | 2476                     | 4                         | 80                     | 1157              | 8156                       | 0.5                     | 27            | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[0].decoding0 (decoding_xdcDup_1)                             | 2358                | 1227                 | 1039                     | 188                       | 16                     | 359               | 2358                       | 5                       | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[0].encoding0 (encoding_xdcDup_1)                             | 24428               | 21805                | 21805                    | 0                         | 0                      | 4464              | 24428                      | 42                      | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[0].g_enableFromHost.crfh0 (CRFromHostAxisxdcDup1)            | 1754                | 1760                 | 1344                     | 416                       | 4                      | 361               | 1754                       | 16                      | 0             | 0                   | 0                              | 0                        |

| > 📘 g_endpoints[0].g_EnableFullModeEmulator.emu0 (FullModeDataEmulator_xdcDup_1)    | 1314                | 1009                 | 1009                     | 0                         | 16                     | 234               | 1314                       | 12                      | 0             | 0                   | 0                              | 0                        |

| > I g_endpoints[0].g_EnableFullModeEmulator.fosel0 (axis_32_fanout_selectorxdcDup1  | ) 4                 | 70                   | 70                       | 0                         | 0                      | 36                | 4                          | 0                       | 0             | 0                   | 0                              | 0                        |

| > I g_endpoints[0].pcie0 (wupper)                                                   | 53896               | 26800                | 25004                    | 1796                      | 489                    | 8631              | 53896                      | 16                      | 60            | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[0].resetmgr_fromhost (CRresetManagerxdcDup1)                 | 10                  | 69                   | 69                       | 0                         | 0                      | 62                | 10                         | 0                       | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[0].resetmgr_tohost (CRresetManager_xdcDup_2)                 | 10                  | 11                   | 11                       | 0                         | 0                      | 4                 | 10                         | 0                       | 0             | 0                   | 0                              | 0                        |

| g_endpoints[0].sync_fromhost_fifo_flush (xpm_cdc_sync_rst_parameterized279)         | 2                   | 0                    | 0                        | 0                         | 0                      | 1                 | 2                          | 0                       | 0             | 0                   | 0                              | 0                        |

| <pre>g_endpoints[0].sync_fromhost_reset (xpm_cdc_sync_rstparameterized280)</pre>    | 2                   | 0                    | 0                        | 0                         | 0                      | 1                 | 2                          | 0                       | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[1].crth0 (CRToHost)                                          | 8156                | 2496                 | 2492                     | 4                         | 80                     | 1193              | 8156                       | 0.5                     | 27            | 0                   | 0                              | 0                        |

| > I g_endpoints[1].decoding0 (decoding)                                             | 2358                | 1236                 | 1048                     | 188                       | 16                     | 351               | 2358                       | 5                       | 0             | 0                   | 0                              | 0                        |

| > I g_endpoints[1].encoding0 (encoding)                                             | 24420               | 21827                | 21827                    | 0                         | 0                      | 4440              | 24420                      | 42                      | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[1].g_enableFromHost.crfh0 (CRFromHostAxis)                   | 1754                | 1753                 | 1337                     | 416                       | 4                      | 360               | 1754                       | 16                      | 0             | 0                   | 0                              | 0                        |

| > I g_endpoints[1].g_EnableFullModeEmulator.emu0 (FullModeDataEmulator)             | 1314                | 990                  | 990                      | 0                         | 16                     | 245               | 1314                       | 12                      | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[1].g_EnableFullModeEmulator.fosel0 (axis_32_fanout_selector) | 4                   | 68                   | 68                       | 0                         | 0                      | 35                | 4                          | 0                       | 0             | 0                   | 0                              | 0                        |

| > I g_endpoints[1].pcie0 (wupper_parameterized0)                                    | 53645               | 26532                | 24736                    | 1796                      | 489                    | 8855              | 53645                      | 16                      | 60            | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[1].resetmgr_fromhost (CRresetManager_xdcDup_3)               | 10                  | 69                   | 69                       | 0                         | 0                      | 62                | 10                         | 0                       | 0             | 0                   | 0                              | 0                        |

| > <b>I</b> g_endpoints[1].resetmgr_tohost (CRresetManager)                          | 10                  | 11                   | 11                       | 0                         | 0                      | 4                 | 10                         | 0                       | 0             | 0                   | 0                              | 0                        |

| g_endpoints[1].sync_fromhost_fifo_flush (xpm_cdc_sync_rst_parameterized2106)        | 2                   | 0                    | 0                        | 0                         | 0                      | 1                 | 2                          | 0                       | 0             | 0                   | 0                              | 0                        |

| <pre>g_endpoints[1].sync_fromhost_reset (xpm_cdc_sync_rst_parameterized2)</pre>     | 2                   | 0                    | 0                        | 0                         | 0                      | 1                 | 2                          | 0                       | 0             | 0                   | 0                              | 0                        |

| > I hk0 (housekeeping_module)                                                       | 3554                | 2702                 | 2653                     | 49                        | 12                     | 597               | 3554                       | 3                       | 0             | 0                   | 0                              | 2                        |

| > I linkwrapper0 (link_wrapper)                                                     | 5613                | 2940                 | 2936                     | 4                         | 10                     | 1142              | 5613                       | 0                       | 0             | 0                   | 0                              | 0                        |

| <pre>&gt; I proc_sys_reset (proc_sys_reset_proc_sys_reset_0)</pre>                  | 35                  | 20                   | 19                       | 1                         | 0                      | 6                 | 35                         | 0                       | 0             | 0                   | 0                              | 0                        |

| > I TTCLTI.ltittc0 (ltittc_wrapper)                                                 | 9549                | 5738                 | 5370                     | 368                       | 28                     | 1437              | 9549                       | 0                       | 0             | 0                   | 1                              | 0                        |

# Installation of a Felix-182 Card @ APE Lab

Ionardo@apestation0 x86 64-el9-gcc13-opt]\$ bin/flx-init 2025-05-14 18:06:05 Opening card 0 (device 0)... 2025-05-14 18:06:05 Card type: FLX-182 2025-05-14 18:06:05 Firmware: FULL 2025-05-14 18:06:05 Clock : Local 2025-05-14 18:06:05 FLX soft reset 2025-05-14 18:06:05 SI5345A hard reset 2025-05-14 18:06:07 ### SI5345A part nr: read 0xFF, expected 0x45; device not present/accessible? 2025-05-14 18:06:07 Found SI5345A BETA 2025-05-14 18:06:12 Links soft reset 2025-05-14 18:06:12 Setting up links... 2025-05-14 18:06:19 Links set up 2025-05-14 18:06:19 WARNING: 4 channels not aligned 2025-05-14 18:06:19 Resetting FireFly devices... 2025-05-14 18:06:19 FIREFLY TX1: PartNr="CERNBY12040213M", SerNr="UA2042001A" 2025-05-14 18:06:19 FIREFLY RX1: PartNr="CRRNBY12040213M", SerNr="UA2042001A" 2025-05-14 18:06:20 FIREFLY TX2: PartNr="CERNBY12040213M", SerNr="UA2042001F" 2025-05-14 18:06:20 FIREFLY RX2: PartNr="CRRNBY12040213M", SerNr="UA2042001F" 2025-05-14 18:06:20 FIREFLY TXRX: PartNr="B042804005170", SerNr="UA231005DX" 2025-05-14 18:06:20 WARNING: CDR not changed, part expected "B042504005170" 2025-05-14 18:06:20 FireFly done 2025-05-14 18:06:20 INA226 configured 2025-05-14 18:06:20 Initializing LTI...

2025-05-14 18:06:20 LTI alignment: NO

# **Backup Slides**

#### **FLX-182B**

# **FLX-182 Features**

#### Main features of FLX-182

- XCVM1802 production chip

- PCIe Gen4 x16: PL and CPM compatible

- PL: Hard PCIe endpoint like in earlier FPGA series

- CPM: Hard PCIe endpoint integrated in SoC, data transferred over NoC

- 24 FireFly links with 3 possible configurations

- 24 links up to 25 Gb/s

- 24 links up to 10 Gb/s (CERN-B FireFly)

- 12 links up to 25 Gb/s + 12 links up to 10 Gb/s

- 4 FireFly links with 2 possible configurations with 14 or 25 Gb/s FireFly TRx

- LTI interface

- 100 GbE

- 1 DDR4 Mini-UDIMM

- USB-JTAG/USB-UART

- SD3.0/QSPI

- GbE

Block diagram of FLX-182