# Switzerland interests in FCC

- Detectors and systems:

- Tracker, Vertex, TDAQ

- Groups interested in vertex detectors for FCC-ee:

- Bern, ETH, PSI, UZH

- Funding in the past 5 years:

- One SNF grant for a postdoc (UZH) and 2 PhD students (UZH/VUB)

- Funding 2025-2029:

- CHEF: Swiss High Energy Physics for the FCC

- Partly (1/2) supported by the Science, Education, Research, Innovation ministry (SERI)

- Consortium of Institutions: Basel, Bern, ETHZ, EPFL, Geneva, PSI, Zurich

- About 20 PhD students + 10 postdocs

- Mostly for detectors

- Computing, Theory, Physics studies also covered

Experiment HEP groups (Canelli and Kilminster)

- Groups currently consists of

- 2.5 senior scientists

- 7 postdocs

- 13 PhD students (+3 PSI +1 CERN)

- Department funds our access to:

- Well-equipped mechanics shop (9 staff & apprentices)

- Electronics shop (4 engineers)

HEP group within laboratory of particle physics (LTP) at PSI

- Group currently consists of

- 6 senior scientists

- 5 postdocs

- 4 PhD students (1 ETHZ + 3 UZH)

- 3 technicians and engineers

- Main focus of these groups: CMS experiment

- Physics analysis

- Pixel detector operation and upgrade

- CH consortium (PSI, ETH, UZH) led design, construction, integration and commissioning of original and Phase-1 CMS barrel pixel detector

- UZH/PSI currently constructing TEPX Phase-2 upgrade

## **UZH**

#### Competences & Infrastructrure

Key competences for pixel detector development at UZH and PSI

- Design of planar silicon sensors

- Hybrid pixel detector module design

- System conception of pixel detector control and readout

- Design and construction of lightweight mechanical structures

- Design of readout ASICs and planar silicon sensors (PSI)

#### Available infrastructure

- UZH DEMETER center for silicon detectors R&D

- Clean room facility

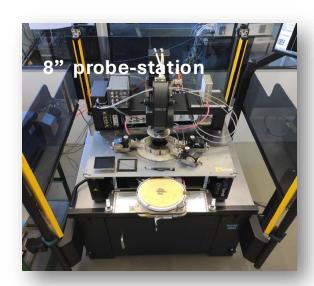

- 8" wafer probe-station

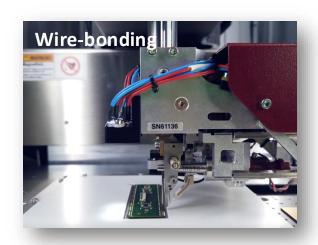

- Semi-automatic wire bonder

- Two Photon Absorption system to be acquired in 2026

- MARTA and Lucasz CO2 cooling systems

- PSI

- In-house bump-bonding and wire-bonding

- Wafer-level testing of ASICs and sensors

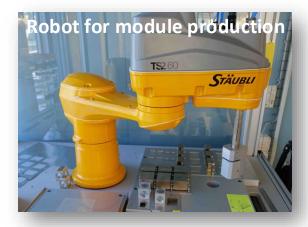

- Module assembly lines (manual and robotic)

- Clean room facilities

## **UZH** - R&D for future detectors

R&D in view of future upgrades of CMS and FCC-ee detectors:

- **Vertex and silicon wrapper simulation:** development of versatile tracking detector constructor algorithms in DD4hep, enabling detailed performance evaluation (slide 9 see A. Ilg's talk)

- OCTOPUS and its predecessors: characterization of APTS and CE-65 structures in 65 nm CMOS by doing calibrations with radioactive source and test beam studies (slide 10 – in IPHC's talk)

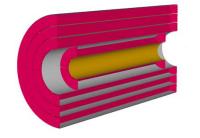

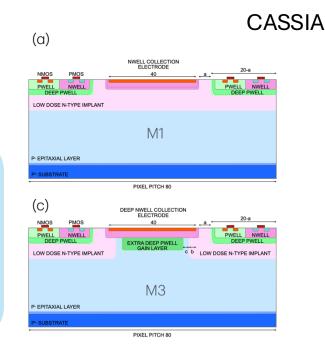

- Silicon Wrapper Timing Layer: Feasibility study of pixelated LGAD sensors for time-of-flight detectors, aiming at a spatial resolution of ≈10 µm and a timing resolution of ≈30 ps for use as a silicon wrapper and also study of possible alternative: monolithic CASSIA timing MAPs, also an option for the final vertex layer (slide 11)

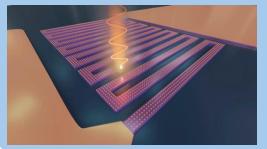

- Quantum sensors: validation of superconducting nanowire particle detectors (SNSPDs) of different material and geometries for detecting charged particles (slide 12 – a different workshop)

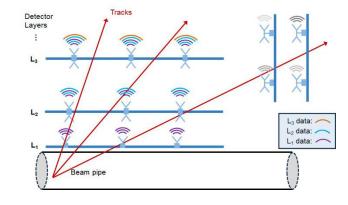

- Wireless communication: prototyping implementation of wireless data transmission for vertex detector using 60 GHz transmission (slide 12 A. Macchiolo's talk)

## **PS** - R&D for future detectors

R&D in view of future upgrades of CMS, FCC-ee detectors, and low-energy experiments at PSI

#### Two main R&D lines:

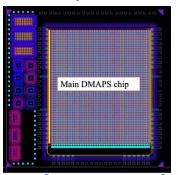

1) Development of depleted monolithic active pixel sensors (DMAPS) with timing capabilities (currently targeting O(100ps)) (with ETHZ)

MOTIC (LF 110 ARCADIA, 2022)

A. Ebrahimi et al.

**Proceedings VERTEX2023**

80x64 pixels 50x50μm²

**MAPSI (TSI 180nm, 2023)**

T. Rohe et al.

43rd RD50 meeting

20x20 pixels 50x150μm²

#### **PANTHER (LF150, 2025)**

Currently under test

#### **PANTHERv2 (LF150, 2025)**

Submission early 2026 shared within DRD3

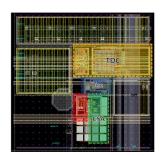

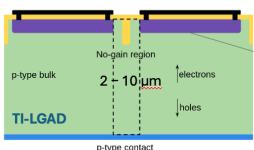

#### 2) Development of readout electronics for fast silicon timing detectors (with resolution <30ps) (with

#### UZH)

- Started from test structures of TDCs in 110nm to fit in pixels of  $100x100\mu m^2$

- Demonstrated that O(10ps) can be achieved

M. Senger et al. <a href="https://arxiv.org/pdf/2302.06711">https://arxiv.org/pdf/2302.06711</a>

#### **LIGHT (28nm CMOS, 2025)**

- First small-scale chip

- 8x8 pixels of 100x100μm²

- For TI-LGAD sensors

- submitted yesterday

## Backup

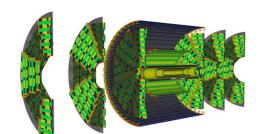

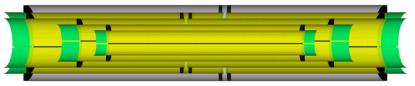

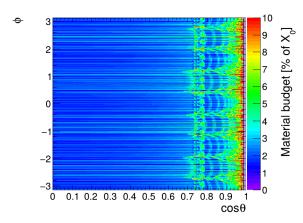

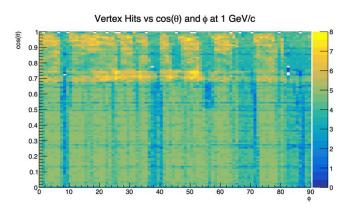

#### Vertex and silicon wrapper simulation

Development of versatile tracking detector constructor algorithms in DD4hep, enabling detailed performance evaluation

IDEA classic mat. Budget distribution

Number of hits in ultra-light concept

IDEA vertex detector perf.

- Plans for the future:

- Optimise VXD layouts in DD4hep

- Compare IPC hit rates in different sensor designs technologies (high vs. low charge sharing)

- Reassess vertexing performance using track reconstruction chain of VTXD + gas tracker + SiWr

- $B^0 \rightarrow K^{*0}\tau^+\tau^-$  full simulation study

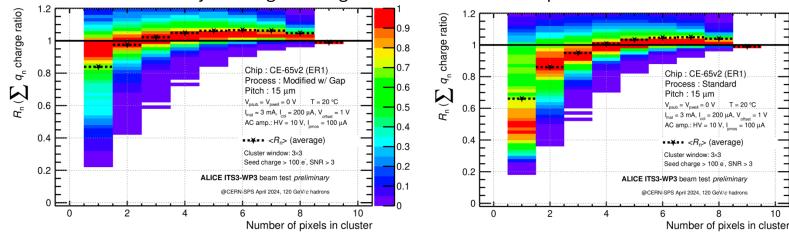

## OCTOPUS and its predecessors

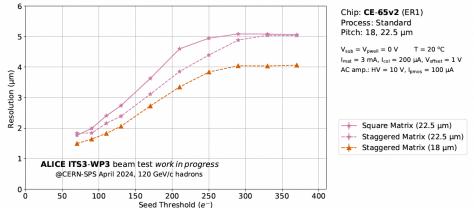

- In-depth characterization of APTS and CE-65 structures in 65 nm CMOS

- Calibrations with radioactive source and test beam studies

CE-65: Study of charge sharing in the Modiofied with Gap and Standard Proces

Radiation tolerance O(10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>)

- Plans for the future:

- Participate to the characterization of the SPARC prototype chip and of Wolfi

- Simulation of the detector response: digitization

- Development of DAQ SW for the Caribou board

## 4D Tracking for the Silicon Wrapper

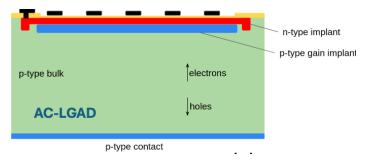

#### LGADs for 4D tracking and ToF within DRD3 WG2

| WG2 research goals <2027 |                                                               |

|--------------------------|---------------------------------------------------------------|

|                          | Description                                                   |

| RG 2.3                   | LGAD for 4D tracking $<$ 10 $\mu m, <$ 30 ps, wafer 6" and 8" |

| RG 2.4                   | LGAD for ToF (Large area, $< 30 \mu m$ , $< 30 ps$ )          |

- Goal: demonstration of the feasibility of producing pixelated LGAD sensors to achieve a position resolution around 10  $\mu$ m, with a timing resolution of the order of 30 ps before irradiation.

- Plans: characterize full modules (PSI chip LIGHT, INFN IGNITE in 28 nm CMOS) and study system aspect (power dissipation and cooling)

- CASSIA timing MAPs within DRD3 WG1

#### Goal:

- Validation of the technology

- Study the feasibility and the physics case of implementing monolithic timing sensors as last Vertex layer before the drift chamber

Collaboration with BNL/Brown

UZH coordination of DRD3 project

= overlap of electrode and low-dose n-type impla

### Quantum sensors and wireless communication

- NSSPD: validation of superconducting nanowires SPDs of different material and geometries for detecting charged particles

- Study of hit efficiency and timing properties in comparison to silicon sensors

- Investigation of the feasibility of applying the technology to FCC luminometers

- Understanding MDI constraints for detector concept & providing cryogenics

- Study possible improvements in the determination of the fiducial region thanks to 100 nm wire size and in the background rejection by using correlated timing measurements

- Wireless communication: prototype implementation of wireless channels using commercial 60 GHz integrated circuits

- Antenna design and link optimization

- Study interference between links in the FCC environment topology, test in a mock-up

- Study interlayer intelligence for a fast-track trigger