# **OCTOPUS:**

R&D program towards a vertex detector for the future e<sup>+</sup>e<sup>-</sup> collider

Serhiy Senyukov (IPHC-CNRS) on behalf of the OCTOPUS project

### **OCTOPUS:**

### Optimized CMOS Technology for Precision Ultra-thin Silicon

- Project: simulate, produce and test MAPS prototypes

- Target: reticle-size demonstrator sensor for future lepton collider vertex detectors

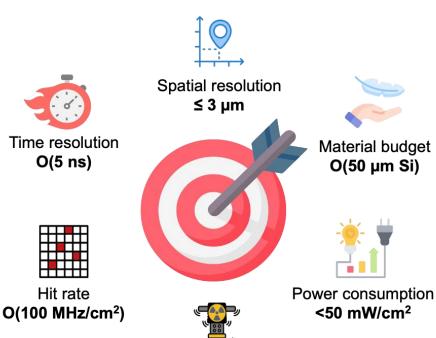

- Requirements: based on 2021 ECFA detector roadmap

- Performed in: DRD3 WG1

- **CMOS process:** TPSCo 65 nm via DRD7.6a

- https://octopus.web.cern.ch/

Radiation tolerance O(10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>)

## Intermediate project target:

New sensor for beam telescopes

Power consumption

<50 mW/cm²

<500 mW/cm²

Radiation tolerance

O(10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>)

not explicitly required

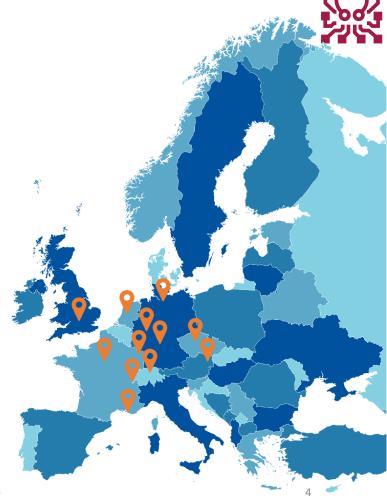

## 14 member institutes

| Institute            | Main areas of contribution             |

|----------------------|----------------------------------------|

| APC Paris            | Simulations, testing                   |

| University of Bonn   | ASIC design, testing                   |

| CPPM Marseille       | ASIC design                            |

| NIKHEF               | Testing, DAQ                           |

| CERN                 | Testing, DAQ, ASIC design support      |

| DESY                 | ASIC design, testing, DAQ, simulations |

| ETH Zurich           | ASIC design, testing                   |

| CTU Prague           | ASIC design, DAQ, testing              |

| GSI Darmstadt        | Simulations, testing                   |

| MBI Vienna           | DAQ, testing, ASIC design              |

| IPHC Strasbourg      | ASIC design, testing                   |

| University of Oxford | Powering, integration, testing         |

| University of Zurich | Testing, DAQ, simulations              |

## 4 working groups

#### OCTOPUS project S. Spannagel, D. Dannheim

WP1: Simulations A. Ilg, A. Velyka WP2: A SIC design F. Guezzi, L. Huth, S. Senyukov WP3: Data Acquisition Y. Otarid WP4: Testing and characterization F. King, M. Franks

System Demonstator (DRD8)

Task 1: Sensor optimization / TCAD Task1: Sensor and pixel front-end design

Activity 1: Caribou 2 development

Task 1: Summary of current 65 nm demonstrator results

Activity 1: Concept, design of mechanics & cooling

Activity 1: Allpix<sup>2</sup> development Task 2: Matrix architecture & readout design

Task 1: Chipboard design for prototypes

Task 2: Lab characterization, FE optimization, calibration

Activity 2: Design & Construction of beam telescope

Task 2: Detecor performance / Allpix<sup>2</sup> Task 3: Periphery, DACs & slow control

Task 2: FW and SW integration of prototypes

Task 3: Testbeam caracterization, simulation comparison

Activity 3: Prototype construction

Activity 2: Physics performance / Geometry optimization

Task 3: Trancievers & readout design Task 3: Chip / board assembly, bonding & logistics

Activity 1: Sensor irradiation & testing

Activity 1: Submission coordination & DRD7 liason

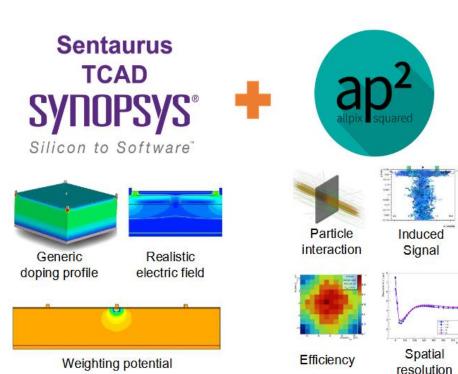

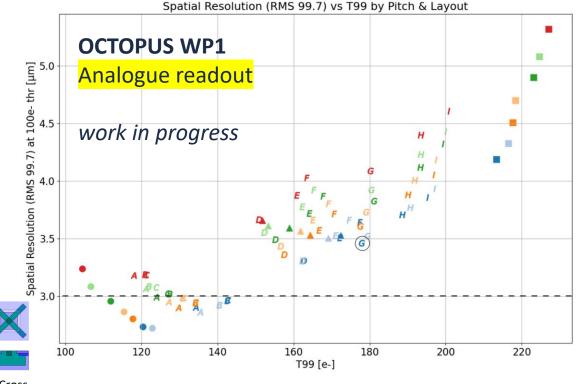

## WP1: Sensor optimization

#### **Tech-independent simulation framework:**

- TCAD sensor simulation

- Allpix squared particle interaction, signal propagation

#### Aim: 3 µm resolution with full efficiency

- Large parameter space:

- Process variants

- Pitch

- Trade-off between:

- Charge sharing

- Efficiency

- Timing

- Existing TPSCo 65 test results used to benchmark simulations

## WP1: Novel layout - NCross

- Novel cross shaped **layout (Ncross)** provides 3 µm resolution at 18-20 µm pitch

- New layout may be implemented in the next TPSCo 65 nm submissions (2026-2027)

- A=1.5, B=high

- A=0.5, B=medium

- A=1.0, B=medium

- A=1.5, B=medium

- A=0.5, B=1.0

- A=1.0, B=1.0

- A=1.5, B=1.0

Standard

**NCross**

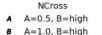

### WP2: Pixel front-end

- MOSAIX (ALICE ITS3) frontend as a starting point of development

- Previous versions proven in silicon (DPTS/MOSS)

- Compact footprint

- Significant time walk at low power

- Time stamp for rising and falling edge needed for:

- Time walk correction

- Charge interpolation for spatial resolution

- Alternative front-ends are under consideration (e.g. CSA from H2M)

https://indico.cern.ch/event/1461789/

Charge over threshold (e - ) 0.05  $I_{bias} = 25 \text{ nA}$ RMS = 43.2 ns $I_{bias} = 50 \text{ nA}$ 0.04 RMS = 26.4 nscount per 2  $I_{bias} = 100 \text{ nA}$  $RMS = 16.8 \, ns$  $I_{bias} = 200 \text{ nA}$ RMS = 10.7 nsNormalized o  $I_{bias} = 300 \text{ nA}$  $RMS = 8.1 \, ns$ 50 100 150 200 250

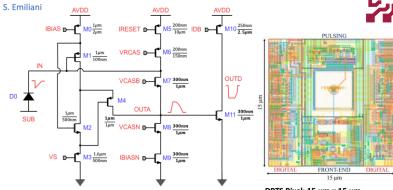

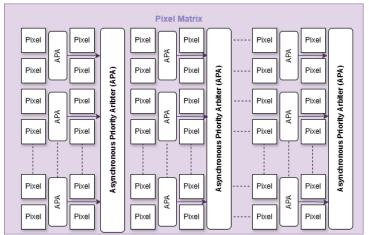

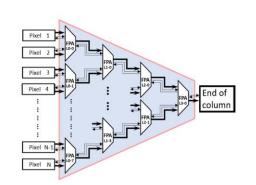

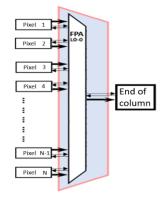

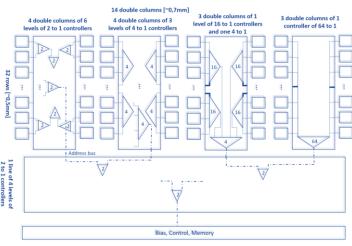

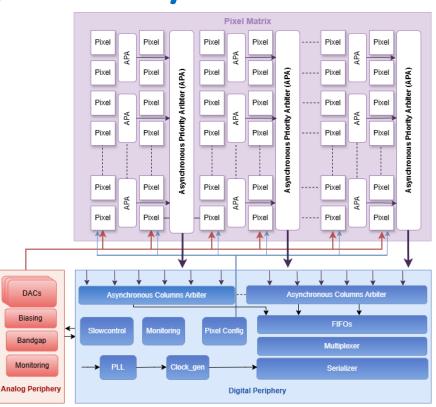

### WP2: Matrix readout

### APA – Asynchronous Priority Arbiter

- Pixels are grouped in double columns

- Hits are propagated via APA tree to the periphery asynchronously (no clock)

- Time ordering of hits is preserved

- Expected time resolution: 5 ns

- Evaluating the best tree topology inbetween

- Many 2:1 (better bandwidth)

- One N:1 (Less area)

- SPARC chip (ER2) to be tested in 2026 to verify the performance of the architecture

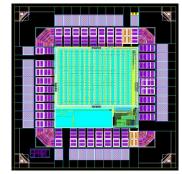

# SPARC: first prototype of asynchronous

readout

• Pixel matrix:  $32 \times 28$

• Pixel pitch:  $24 \times 16 \ \mu m^2$

• Pixel front-end: DPTS-like (CERN)

• FPA tree types: 2:1, 4:1, 16:1, 64:1

• Power dissipation: 5 mW/cm<sup>2</sup>

• Mean readout time: 6.3 ns

• Designed by: IPHC, IRFU

• Submission: summer 2025 (ER2)

Test system in preparation for 2026

1.5×1.5 mm<sup>2</sup>

## WP2: Chip periphery and layout

- Time stamping for ToA and ToT via TDC in the end-of-column

- 4 level event buffer

- Various options for column merging are studied with simulations

- Serialization and data packaging by in-chip lpGBT logic

- Expected output data rate:

10 Gb/s per cm<sup>2</sup>

## WP3: DAQ for OCTOPUS

<u>Caribou</u> – open modular DAQ platform for testing silicon pixel detectors.

Already used for various projects:

H2M, ATLASpix, APTS, DPTS, etc.

### Hardware components:

- SoC board (3000 €)

- Embedded CPU runs DAQ

- CaR board (800 €)

- Power supply

- Data and control links

- Chip board (100 €)

- First use in OCTOPUS

- Test of SPARC chip (from 2026)

### WP4: Test and characterization

- 2025: Finalizing summary report of current results of TPSCo 65 nm prototypes. Publication submission by the end of the year

- 2026: SPARC characterization

- Lab test in several institutes with Caribou DAQ

- 2-3 weeks of the test beam in summer (CERN and DESY)

- >2026: Possible characterization of Ncross layout with APTS chips of ER2-respin or ER3.

- Discussion ongoing with DRD7.6a on possible submissions

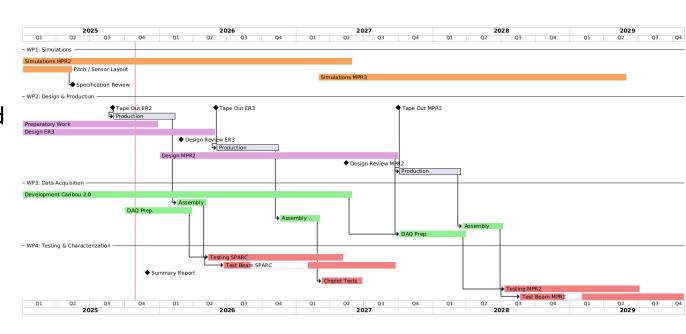

## Project timeline

Project schedule largely depends on the TPSCo 65 nm submissions organized by DRD 7.6a

#### **Current targets:**

- ER3 (2026) several "chiplets" (1.5×1.5 mm²) to test individual blocks

- MPR2 (2027) full column prototype (2 × 1 cm²)

## Summary and outlook

- OCTOPUS project aims to build a MAPS prototype for the vertex detector for future lepton collider

- Spatial resolution: 3 μm

- Time resolution: 5 ns

- Power consumption: < 50 mW/cm<sup>2</sup>

- Hit rate: 100 MHz/cm<sup>2</sup>

- Targeting ER3 and MPR2 submission in 2026/27 for the first prototypes in TPSCo 65 nm process

- Preparation for testing async readout using SPARC chip in 2026

Thank you!