## **TEST SYSTEM FOR MLR1 and ER2 CHIPLETS**

**MLR1**: First submission of MAPS in 65 nm. Used to validate the 65 nm technology (2021-2023). Three types of Test Structures (TS) characterized: APTS (Analog Pixel Test Structures), DPTS (Digital Pixel Test Structures), CE65 (Circuit Exploratoire 65 nm).

APTS: 4×4 matrix, 10-25 µm pixel, w/o process modification, analog readout

DPTS: 32×32 matrix, 15  $\mu$ m pixel, modified with gaps, digital readout, time-encoded signal amplitude and position

CE65: Rolling shutter readout, 3 submatrices, both amplifier and source-follower output buffers.

**ER2**: Production of MOSAIX, babyMOSAIX and chiplets. List of chiplets:

| R2 Chiplets                              | 5                    |                                                                    |                                                                   |

|------------------------------------------|----------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|

| 1 TT51<br>3 TT52                         |                      | Process monitoring and modeling<br>Process monitoring and modeling | Evolution of MLR1 test structures in view of<br>ALICE 3 upgrade   |

| 5 APTS - SF standard                     | 15 um pitch          | Sensor reference                                                   |                                                                   |

| 6 APTS - SF modified                     | 15 um pitch          | Sensor reference                                                   |                                                                   |

| 7 APTS - SF modified with gap            | 15 um pitch          | Sensor reference/optimization                                      | APTS SF:                                                          |

| 8 APTS - SF modified with gap            | 20 um pitch          | Exploration of larger pixel pitches/optimization                   | APTS SF:                                                          |

| 9 APTS - SF modified with gap            | 30 um pitch          | Exploration of larger pixel pitches/optimization                   | <ul> <li>Several size implemented (20-50µm)</li> </ul>            |

| 10 APTS - SF modified with gap           | 40 um pitch          | Exploration of larger pixel pitches/optimization                   | • Several size implemented (20-30µm)                              |

| 11 APTS - SF modified with gap           | 50 um pitch          | Exploration of larger pixel pitches/optimization                   | <ul> <li>Study maximum pixel pitch</li> </ul>                     |

| 12 APTS - SF modified with gap and Nwell | 50 um pitch          | Study of impact of Nwell.                                          |                                                                   |

| 13 APTS - SF modified with gap           | 20.8 x 22.8 um pitch | Sensor pitch in MOSAIX/optimization                                | <ul> <li>Study radiation tolerance of different splits</li> </ul> |

| 14 APTS - OA modified with gap           | 10 um pitch          | Sensor reference/optimization                                      |                                                                   |

| 15 DPTS modified with gap                | 15 um pitch          | Sensor + FE reference/optimization                                 |                                                                   |

| 16 DPTS modified with gap                | 15 um pitch          | Sensor + FE reference/optimization                                 | Variant with same pitch of MOSAIX: could                          |

| 17 DPTS modified with gap                | 15 um pitch          | Sensor + FE reference/optimization                                 | give hint on split selection                                      |

| 18 SEU 3                                 |                      | Custom cell libraries SEE/SEL characterization                     |                                                                   |

| 19 RING-OSC-v1 ported                    |                      | Custom cell libraries leakage and delay                            | APTS OA:                                                          |

| 20 RING-OSC-v2                           |                      | Custom cell libraries leakage and delay                            | Charge collection time and time recolution of                     |

|                                          |                      | Standalone qualification of other versions of DAC                  | <ul> <li>Charge collection time and time resolution of</li> </ul> |

| 21 MOSAIX BIASING                        |                      | and biasing blocks as backup                                       | different splits                                                  |

| 22 MOSAIX SERIALIZER                     |                      | Full chain serializer test chip as in MOSAIX                       |                                                                   |

|                                          |                      |                                                                    | DPTS:                                                             |

| 23 TDC HEIDELBERG                        |                      | TDC                                                                | <ul> <li>Sensor + FE reference</li> </ul>                         |

| 24 IPHC ASYNCH READOUT (SPARC)           |                      | architecture study                                                 |                                                                   |

| 25 SLAC NAPA-v2                          |                      | update on pulsed readout                                           |                                                                   |

| 26 BNL ADC                               |                      | Special architecture for monitoring ADC                            |                                                                   |

| 27 BNL Data transmission                 |                      | Test chip for transmission without repeater                        | Same test system as MLR1, testing plan not yet                    |

| 28 Bandgap/Tmonitoring                   |                      | Test chip Bgap/Tmon as in MOSAIX                                   |                                                                   |

|                                          |                      |                                                                    | prepared                                                          |

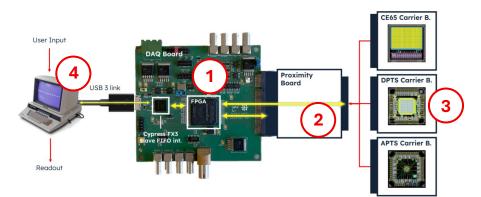

**<u>SETUP</u>**: Same test system for MLR1 and ER2 chiplets.

DAQ (1) + Proximity (depending on the specific test structure under test) (2) + carrier with the test structure bonded (3) + computer + power supply (4)

### COST ESTIMATION:

• DAQ: provided by CERN

- Proximity: ~ 1000 CHF

- Computer: for example HP Elite Mini 800 G9 Desktop PC 5M981EA#ABZ (i7) ~ 1200 euro

- Power supply: R&S®NGC100 Power supply series ~ 1200 EUR

#### **REFERENCE PUBLICATIONS:**

- DPTS: <u>https://doi.org/10.1016/j.nima.2023.168589</u>

- APTS-SF: <u>https://doi.org/10.1016/j.nima.2024.169896</u>

- APTS-OA: https://doi.org/10.1016/j.nima.2024.170034

#### **RECENT SUMMARY OF ITS3 CHARACTERISATION ACTIVITIES @ INFN:**

https://agenda.infn.it/event/46163/

# **TEST SYSTEM FOR BABY-MOSAIX (ER2)**

|      |                      |                           |                                    | AL: |

|------|----------------------|---------------------------|------------------------------------|-----|

| Item |                      | Unit price (CERN via EDH) | Reference                          |     |

| 1a   | FPGA module          | 666,60 CHF                | Enclustra ME-AA1-270-3E4-D11E-NFX3 |     |

| 1b   | FPGA module rework   | 200,00 CHF                | Enclustra-provided BoM & placement |     |

| 1c   | Heat sink            | 29,70 CHF                 | Enclustra ACC-HS4-SET              |     |

| 2    | Base board           | 289,30 CHF                | Enclustra ME-ST1-W                 |     |

| 3    | (baby)MOSAIX carrier | -                         | Design: A. Junique / J. Morant     |     |

| 4    | Power supply (2x)    | 1241,00 EUR               | Rhode & Schwarz NGC103             |     |

| Dist | tribution and supp   |                           |                                    |     |

With respect to small TS test system, you need a FPGA module + rework (1), an Enclustra board (2), the carrier (3) and an additional power supply (4)  $\rightarrow \sim +2500$  euro