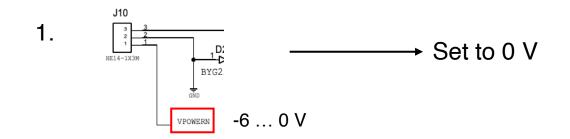

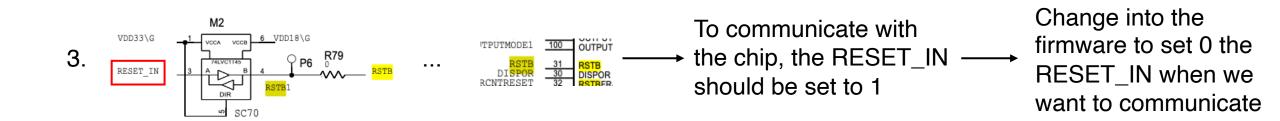

## What we have changed to initiate the communications:

2. RESET\_IN, SYNC\_IN, START\_IN can be controlled through SWITCHES (1, 2, 3) [controllable also with 3 bit (24, 8, 16) in the register 0]

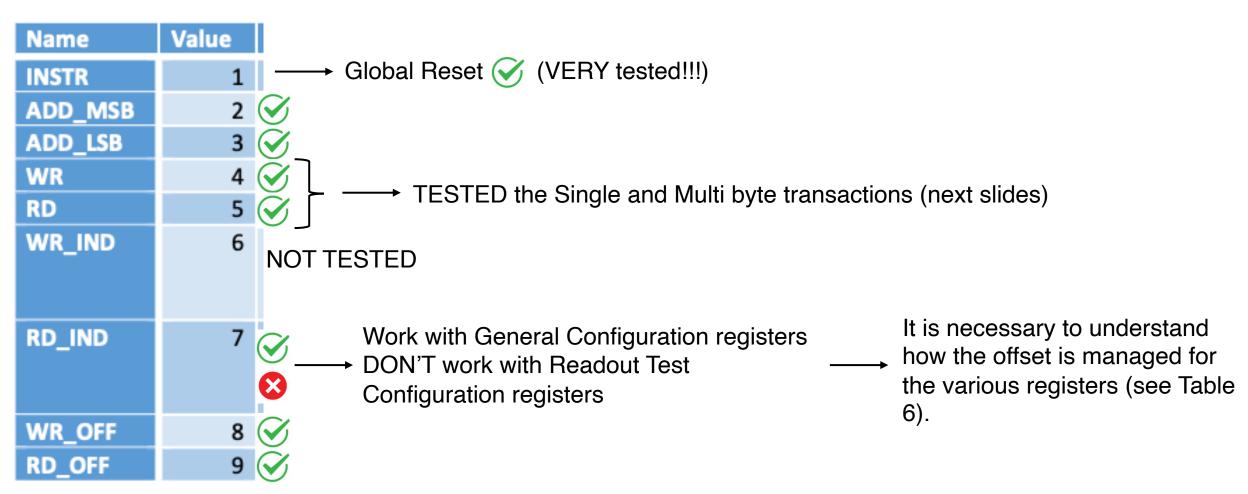

## **Tests: Commands**

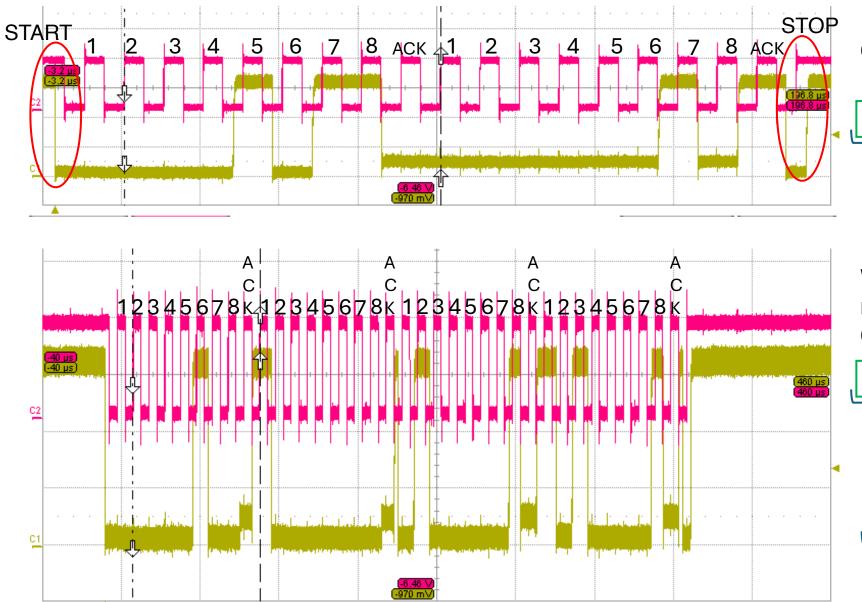

EACH COMMUNICATION IS DISPLAYED ON THE OSCILLOSCOPE TO CHECK THE COMMUNICATION PROTOCOL

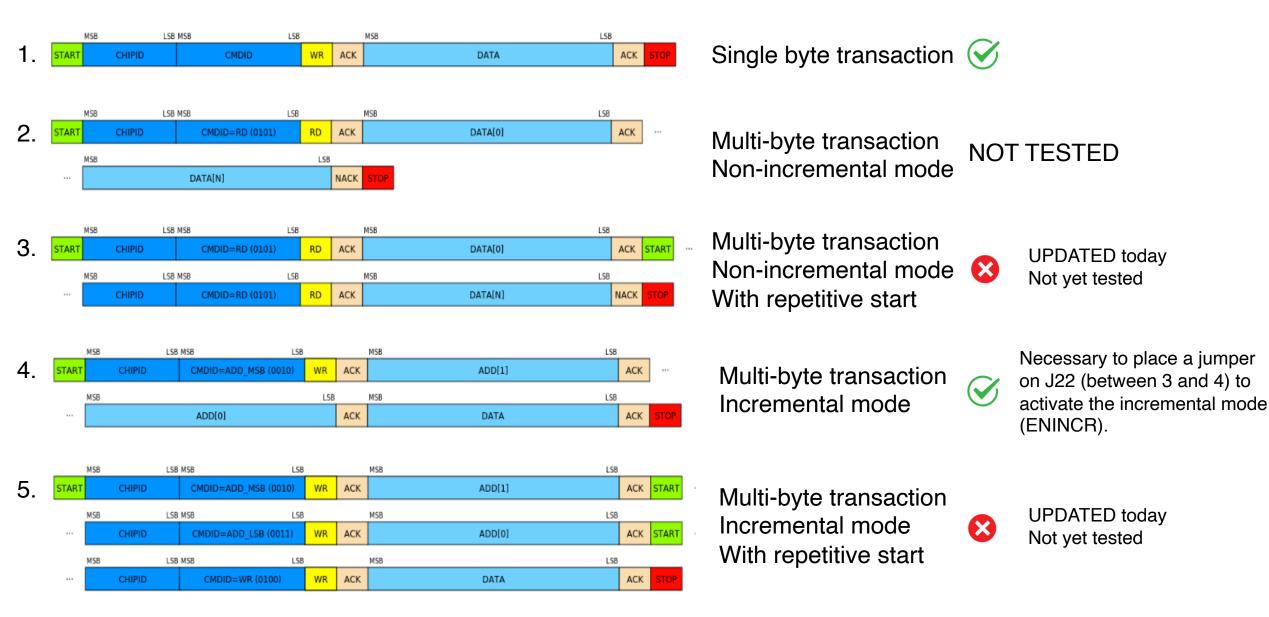

## Single and Multi byte transactions

## **Communication Protocol**

READ of the General Configuration/RUNMODE register

$$\begin{array}{c} 0 \ 0 \ 0 \ 0 \ 1 \ 0 \ 1 \ 1 \\ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 1 \ 0 \\ = 02 \\ (default value) \\ Write/Read bit (= 1) \end{array}$$

WRITE "a1" in incremental mode the register 8041 (Read Out Test Configuration/PATTERN1 register)

## **Tests: Registers**

| Function                     | Bank number  |                                                                 |                     |        |        |

|------------------------------|--------------|-----------------------------------------------------------------|---------------------|--------|--------|

| General Configuration        | 1            | Read the Reset value of all the registers                       |                     |        |        |

| DAC                          | 2            | NOT TESTED                                                      |                     |        |        |

| Sequencer Configuration      | 3            | NOT TESTED                                                      | Name                | Bits   | Reset  |

| Pixel Control                | 4 NOT TESTED | NOT TESTED                                                      | Not Used            | 7-6    |        |

| Monitoring                   | 7            | $\longrightarrow MON_PAD \bigotimes \longrightarrow NOT TESTED$ | DISPOR<br>ENINCR    | 5      | -      |

| <b>Multi-Frame Emulation</b> | 8            |                                                                 | SYNC_IN<br>START_IN | 3<br>2 | -      |

| Analogue Pixel Selection     | 9            | NOT TESTED                                                      | OUTPUTMODE          | 1-0    | -      |

| Readout Configuration        | 10           | → Read/Write on the re                                          | egisters (IDs: 8    | 8040   | -8053) |

In general, sometimes, regardless of the register we are reading, the chip responds with incorrect data. Everything remains consistent with the communication protocol, so it seems to be an issue with the chip itself rather than the way we are communicating.

#### Problems with even registers

| Register<br>ID | Written<br>word | Read<br>word |              |

|----------------|-----------------|--------------|--------------|

| 8040           | a0              | 40           | $\bigotimes$ |

| 8041           | a1              | a1           | $\checkmark$ |

| 8042           | a2              | 42           | $\bigotimes$ |

| 8043           | a3              | a3           | $\checkmark$ |

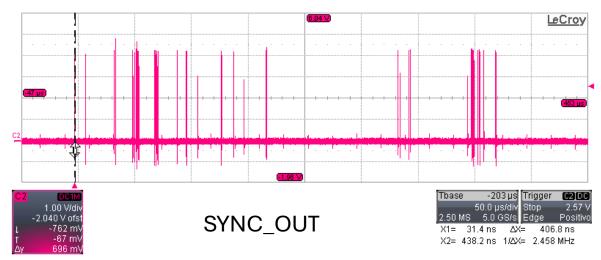

### Tests: Clock-in/out

| -       |      |    | _/ |

|---------|------|----|----|

| CLKGEN1 | 0027 | 00 |    |

| CLKGEN2 | 0028 | 00 |    |

| PLL     | 0029 | 11 |    |

| PLLLOCK | 002A | 38 |    |

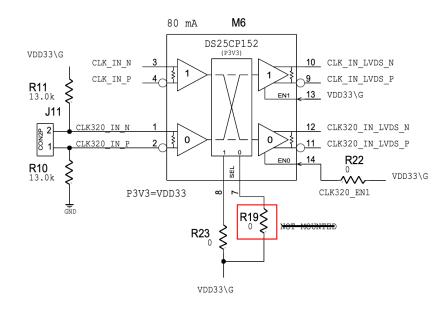

## External clock (R19 mounted) Clock Rescue mode (not used the PLL) New firmware with 320 MHz clock

Nai

SEL

EN

SEL

# clock out.

We still can't see the

| ime     | Bits | Reset | Description                                                                                                                                                                                          |

|---------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L_PHASE | 7-4  | 0     | 320 MHz Clock phase adjustment to adjust internal and external 40 MHz clocks                                                                                                                         |

| _SYNC   | 3    | 0     | Enable synchronization of multiple MIMOSIS1 through SYNC_IN_P and SYNC_IN_N SLVS pads                                                                                                                |

| L_START | 2-1  | 0     | Start mode selection:<br>Automatic: 0 (by default after PLL locked)<br>Software: 1 (by sending 03 to INSTR CMDID see section 2 page 10)<br>External: 2 or 3 (via START_IN_P and START_IN N SLVS pad) |

| L_CLOCK | 0    | 0     | Clock selection:<br>Main @ 40 MHz (CLK_P and CLK_N SLVS pad): 0<br>Rescue @ 320 MHz <sup>4</sup> (CLKRESCUE_P CLKRESCUE_N SLVS pad): 1                                                               |

|   | Name               | Bits | Reset | Description                                                           |

|---|--------------------|------|-------|-----------------------------------------------------------------------|

|   | Not Used           | 7-6  | 0     |                                                                       |

| × | EN_START_SYNC_TERM | 5    | 0     | Enable START_IN and SYNC_IN SLVS 100 Ω termination                    |

|   | FILTER_VAL         | 4-1  | 0     | Filter glitches on PLL lock flag of N times main clock period (25 ns) |

|   | DIS_LOCK_GATING    | 0    | 0     | Disable generated clocks gating with filtered PLL lock flag           |

## Next steps...

- Tests of the new firmware with the possibility of multiple START

- Tests of the configuration files as input

- Try to understand the meaning of some signals: SYNC\_OUT, TMON, ...

- Understand the actual configuration of the board and the significant bit to change to see the clock-out