#### Parallelism, Parallel Systems, and vector computing

Tim demonstrates his new invention: Kayak snorkeling. Palawan Philippines, 2019

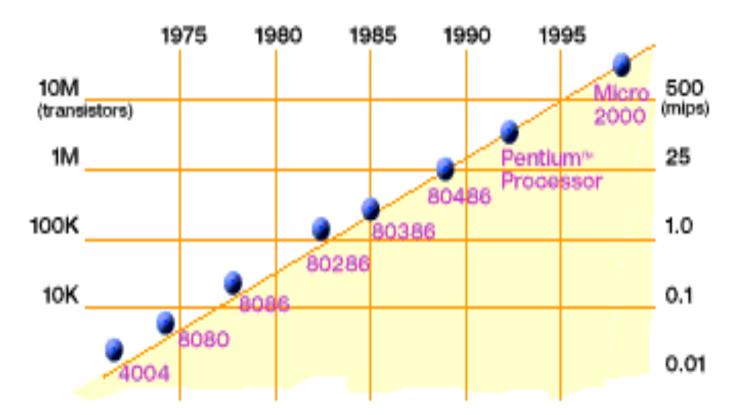

# **Moore's Law**

- In 1965, Intel co-founder Gordon Moore predicted (from just 3 data points!) that semiconductor density would double every 18 months.

- He was right! Over the last 50 years, transistor densities have increased as he predicted.

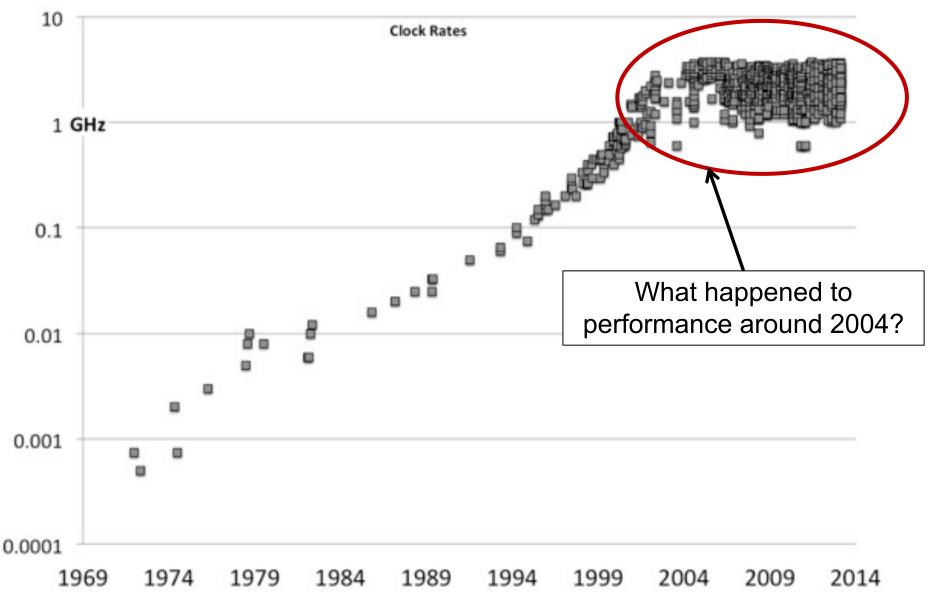

# **CPU Frequency (GHz) over time (years)**

Source: James Reinders (from the book "structured parallel programming")

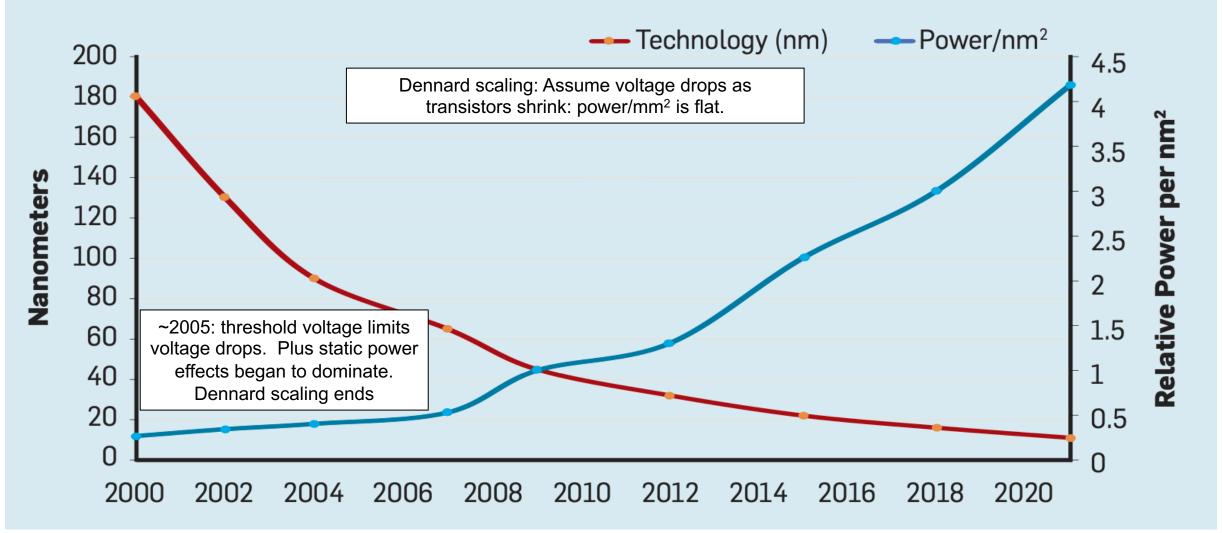

#### **Dennard Scaling**

• Process technology (translates to Transistors per chip) and power per mm<sup>2</sup>

Process technology nodes defined by the smallest feature on a chip (i.e. gate length in nm). After 22 nm, it's become a marketing term that doesn't map to a specific feature's length.

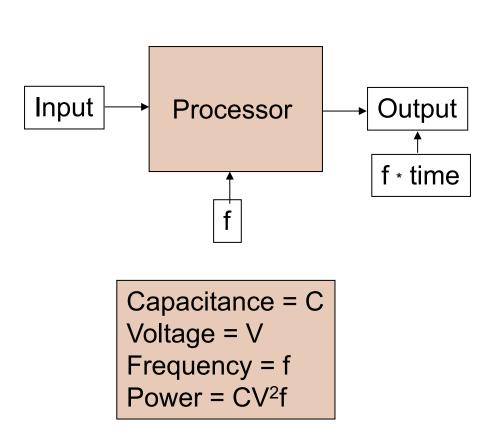

#### Consider power in a chip ....

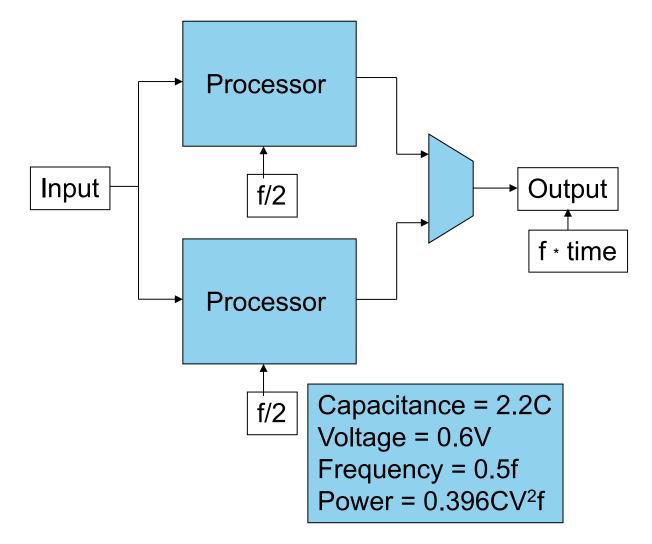

Capacitance = C Voltage = V Frequency = f Power =  $CV^2f$  C = capacitance ... it measures the ability of a circuit to store energy:

$$C = q/V \rightarrow q = CV$$

Work is pushing something (charge or q) across a "distance" ... in electrostatic terms pushing q from 0 to V:

$$V * q = W.$$

But for a circuit q = CV so

$$W = CV^2$$

power is work over time ... or how many times per second we oscillate the circuit

Power =

$$W^* F \rightarrow Power = CV^2 f$$

#### ... Reduce power by adding cores

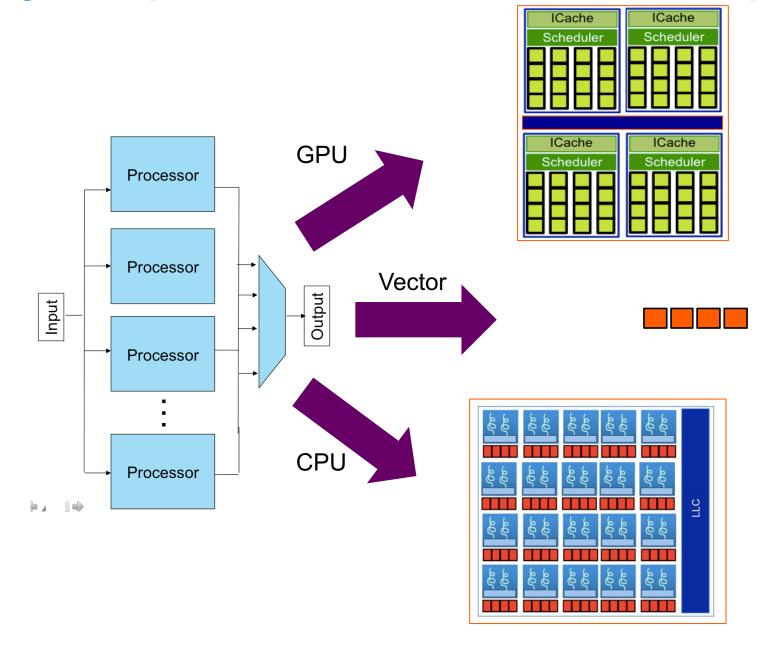

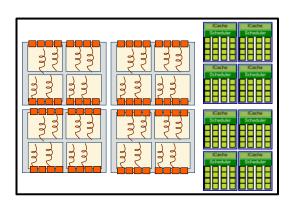

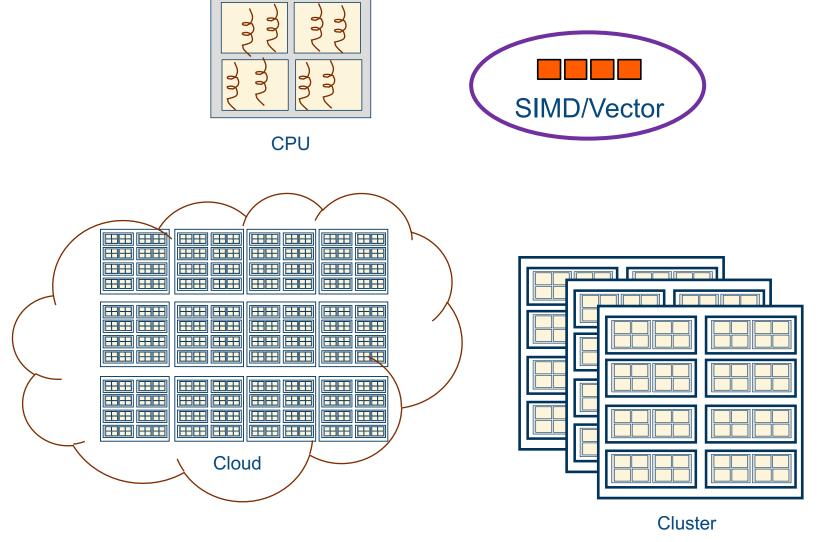

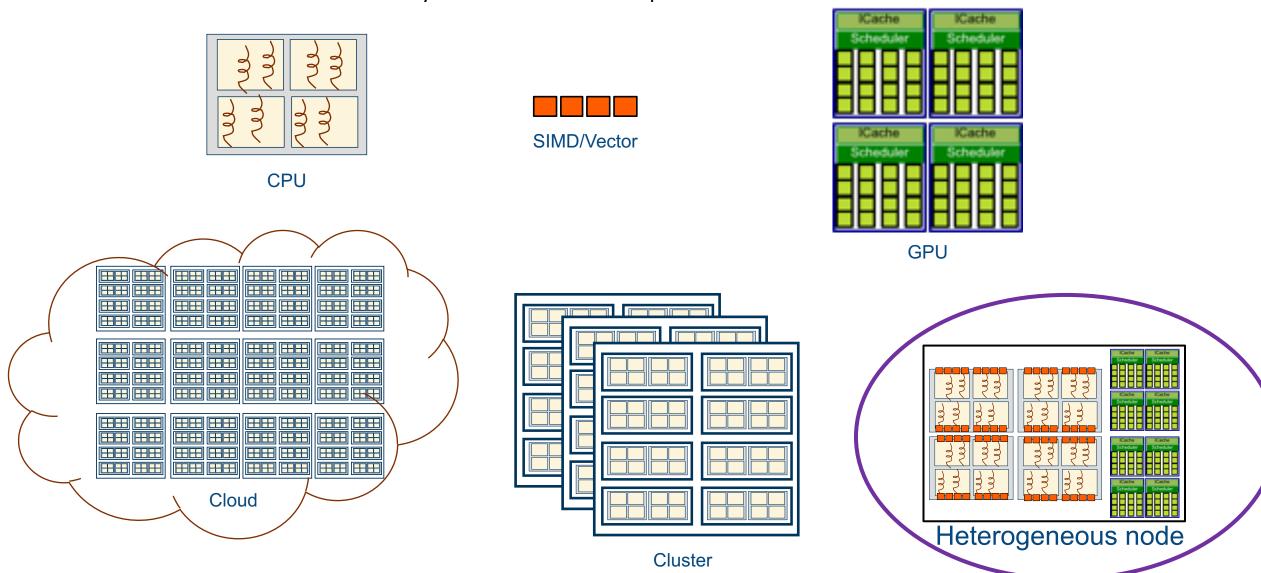

Manycore processors: three hardware options

#### For hardware ... parallelism is the path to performance

All hardware vendors are in the game ... parallelism is ubiquitous so if you care about getting the most from your hardware, you will need to create parallel software.

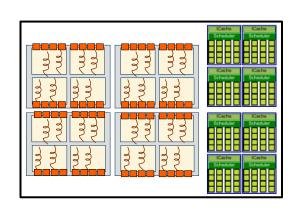

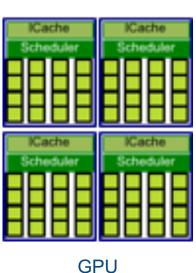

**GPU**

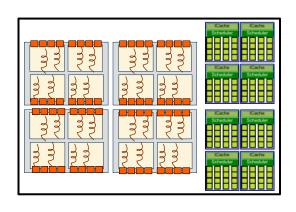

Heterogeneous node

#### Before we continue ...

Let's discuss the idea of parallelism and the terminology we use when working with it.

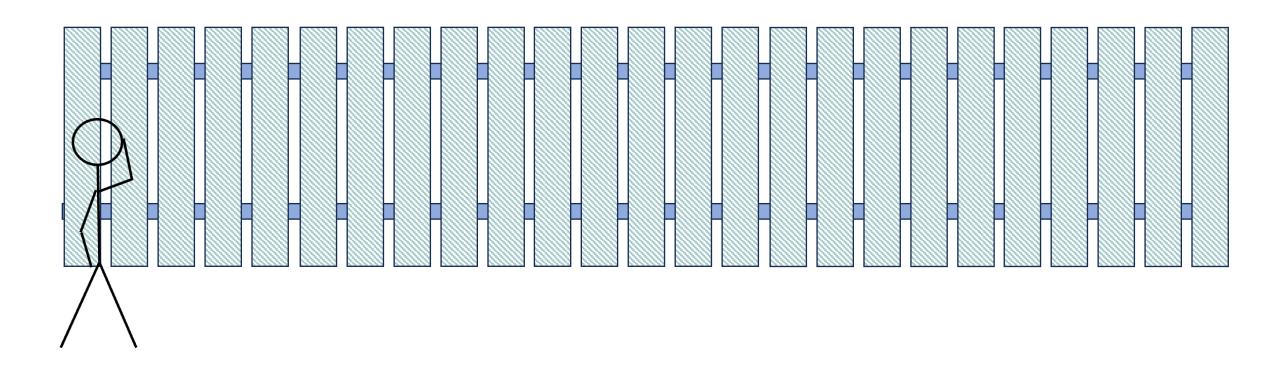

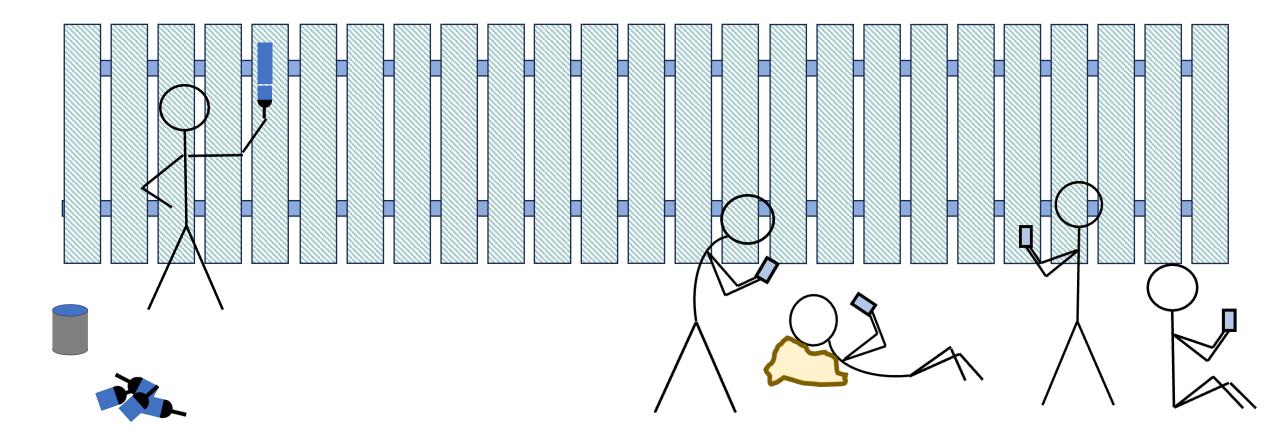

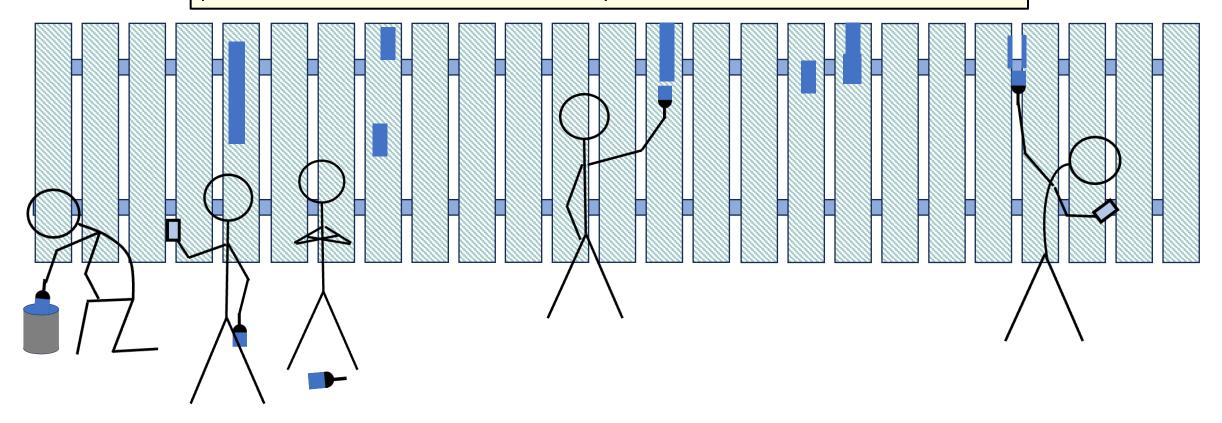

#### Painting a fence

• You must paint a fence. It has 25 planks.

#### Painting a fence: Doing it as a serial process

- You must paint a fence. It has 25 planks. You are going to do this one plank at a time (a serial process)

- How long should it take?

#### Ideal case

It takes  $T_p$  minutes to paint a plank. Therefore it takes  $25*T_p$  minutes to paint the entire fence.

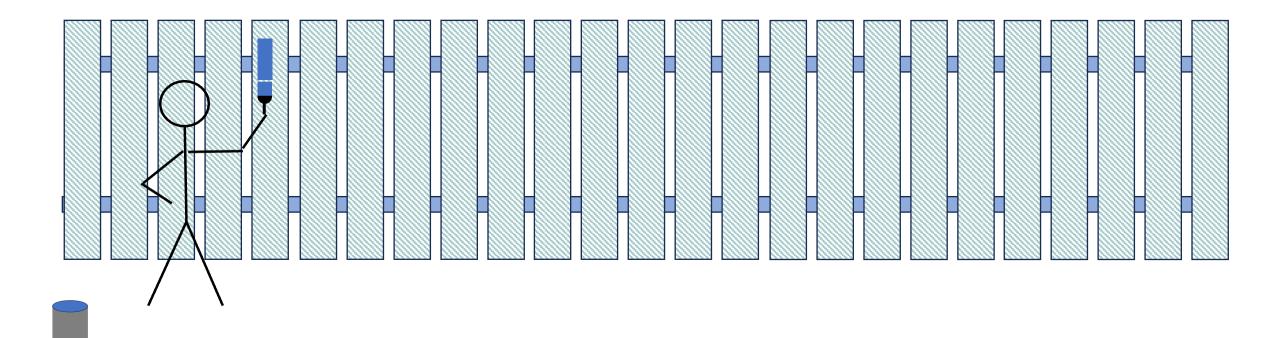

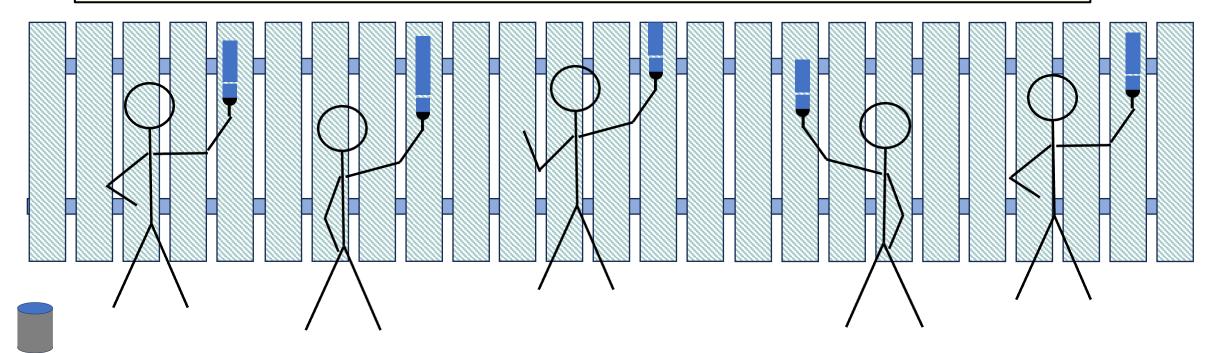

#### Painting a fence: Getting help to finish the job in less time

- You must paint a fence. It has 25 planks.

- You have five brushes, one can of paint, and four friends. How long should the job take with the five of you working in parallel?

#### Painting a fence: Getting help to finish the job in less time

- You must paint a fence. It has 25 planks.

- You have five brushes, one can of paint, and four friends. How long should the job take?

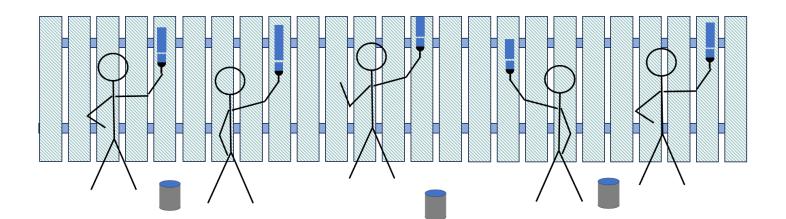

#### Ideal case

It takes  $25*T_p$  minutes to paint the fence on your own ("in serial"). With N = 5 people each taking an equal chunk of the fence, then each person paints 25/N planks. If they do it all at the same time (that is, "in parallel"), the fence will be done in  $(25*T_p)/N = 5*Tp$  minutes

**Speedup**: How many times faster does your job complete when N people work in parallel? Ideally, Speedup = N.

#### Painting a fence: Sometimes, Reality Sucks

- You must paint a fence. It has 25 planks.

- You have five brushes, one can of paint, and four friends. How long should the job take?

#### Reality

Not everyone works equally hard. More importantly with only one can of paint (a **shared resource**) people waste time waiting for their turn to dip their brush in the paint. These and other issues mean that you almost never achieve the ideal case.

# Summary: the concept of parallelism

- This sequence of definitions explains the term "parallelism"

- Agent: A person, process, thread, or other "unit of execution" that can work on a task.

- **Problem Decomposition**: Break the problem into a collection of distinct tasks that are mostly (if not completely) independent.

- Serial: When a single agent carries out a problem's tasks one after the other.

- Parallel: When the tasks execute and make forward progress at the same time.

- Parallelism: the features of problem and its solution that support parallel execution.

- Assume you have multiple agents to carry out a set of tasks. You are not done until the last agent is done. It never goes as well as you hope.

- Making the set of tasks (the work) for each agent balanced so they all finish at the same time is hard (load balancing).

- Agents share resources (such as paint) and often waste time waiting for their turn for the shared resource (contention).

- Coordinating the work of the multiple agents is extra work you wouldn't have if you did the job in serial. This is called parallel overhead.

- Recasting the problem into a collection of distinct and largely independent subproblems (tasks) can be difficult

- There is almost always a small fraction of the work that cannot be done in parallel (serial fraction).

- The serial fraction limits the number of agents that can productively help you complete the job

# Lets consider parallelism across the major classes of parallel system

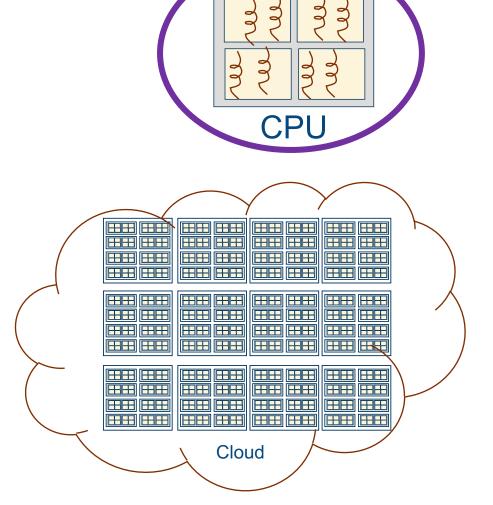

#### For hardware ... parallelism is the path to performance

All hardware vendors are in the game ... parallelism is ubiquitous so if you care about getting the most from your hardware, you will need to create parallel software.

Scheduler Scheduler

Kache

Scheduler

Scheduler

Scheduler

Scheduler

Scheduler

Scheduler

Heterogeneous node

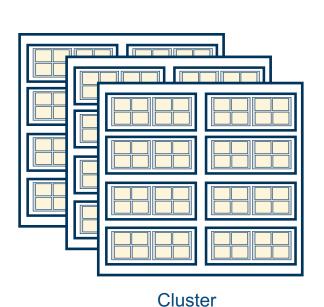

Cluster

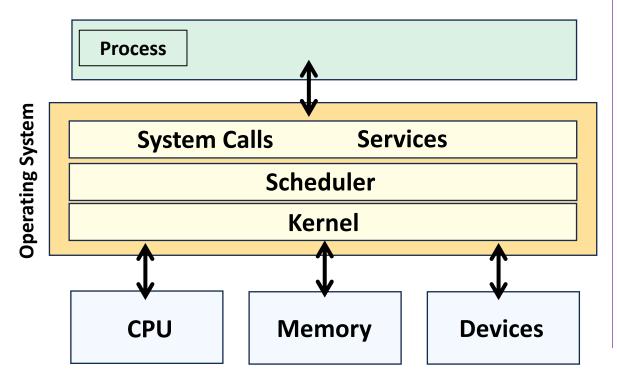

#### The operating system running on a CPU

- The Operating System (OS) is software the manages the computer hardware.

- It consists of a low-level kernel and a collection of services running on top of the kernel to support the needs of system users.

- The kernel provides security guarantees and isolation between running programs (processes).

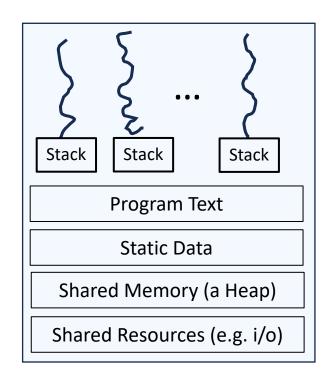

A process is an instance of an executing program.

One or more threads running the same program text

Each thread has private memory (a stack)

Static Memory fixed at compile time

Shared Memory and shared resources are available to all threads

- Modern operating systems support multi-tasking. This

means that multiple processes are active at one time with a

scheduler (part of the OS) quickly switching (a context

switch) between processes.

- For the user, this creates the illusion that all of the processes are running at the same time (more on this later).

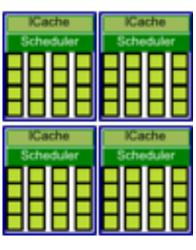

#### **CPU parallelism: Multicore CPUs**

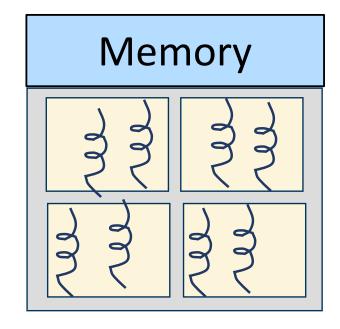

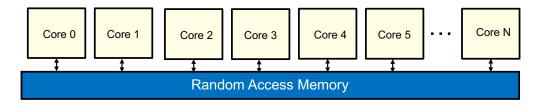

- A modern CPU optimized for performance will have multiple cores sharing a single memory hierarchy.

- The memory appears as a single address space.

- An instance of a program is a process.

- The process has a range of available memory addresses, system resources, and one or more threads.

- Parallelism is managed by the programmer as multiple threads mapped to the various cores.

- When every core is treated the same by the operating system (OS) and has an equal cost function to any location in memory, we call this a <u>symmetric multiprocessor</u> or <u>SMP</u>.

A four core CPU running a process with 8 threads mapped as 2 threads per core

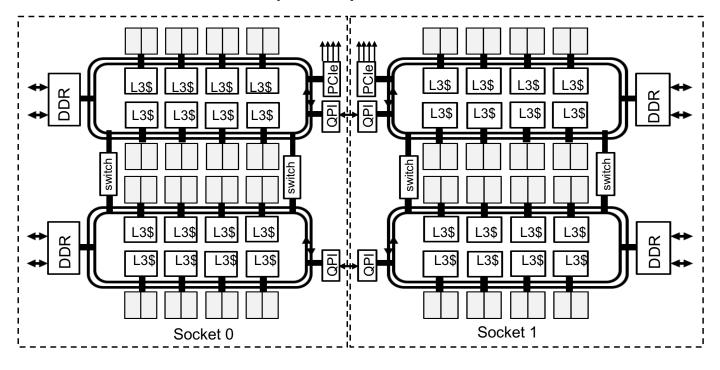

#### A Harsh dose of reality: System memories are non-uniform

A single dual processor node for the Cori system at NERSC: 2 Intel® Xeon™ E5-2698 v3 CPUs at 2.3 GHz, 2 16 GB DIMMs per **DDR memory controller**, 16 cores per CPU. 2 CPUs connected by a high-speed interconnect (QPI)

#### All systems today are nonuniform memory architectures (NUMA)

Given all this complexity in real hardware ....

It's amazing our SMP model works at all ....

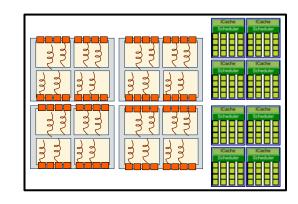

#### For hardware ... parallelism is the path to performance

All hardware vendors are in the game ... parallelism is ubiquitous so if you care about getting the most from your hardware, you will need to create parallel software.

Heterogeneous node

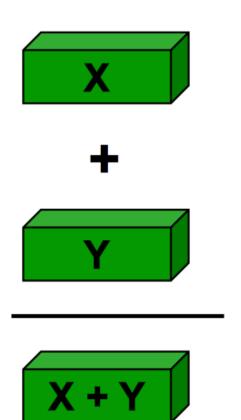

# **Vector (SIMD) Computing**

#### **Scalar computing**

One op produces one value

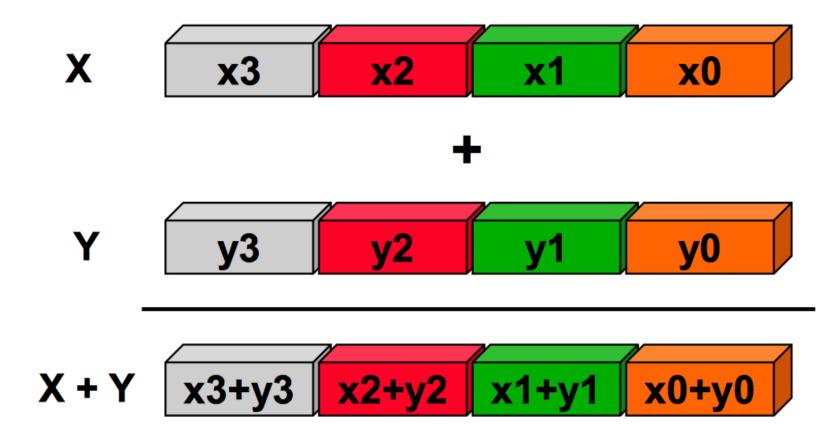

#### Vector computing .. Pack multiple values into vector registers

One op produces multiple values

Hardware architects love vector computing, since they permit space- and energy- efficient parallel implementations.

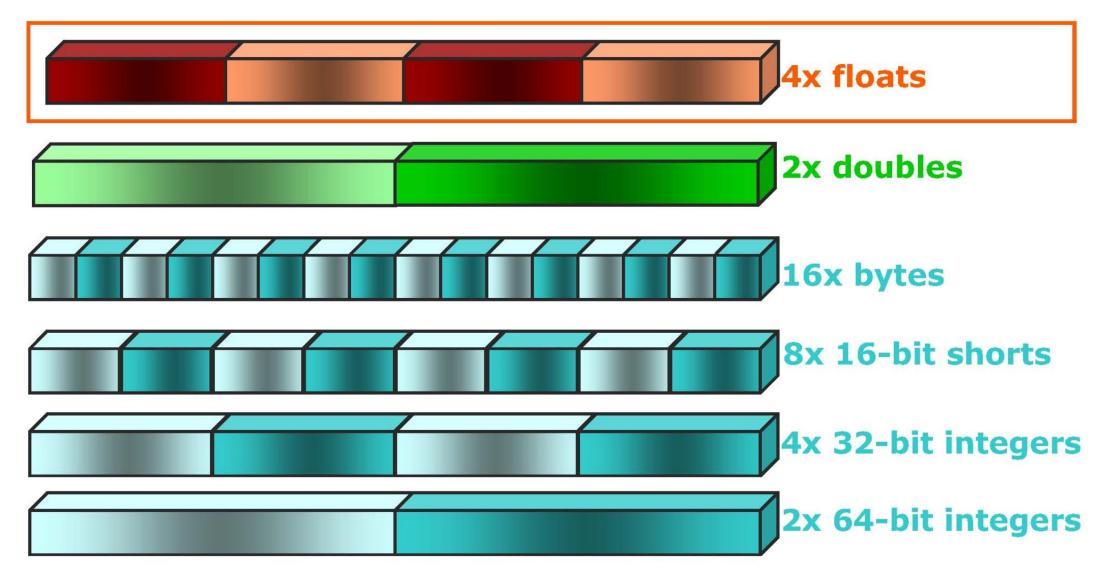

#### Packing numbers into fixed width vector registers

**Example: 128 bit SSE (from Intel) and Neon (from ARM)**

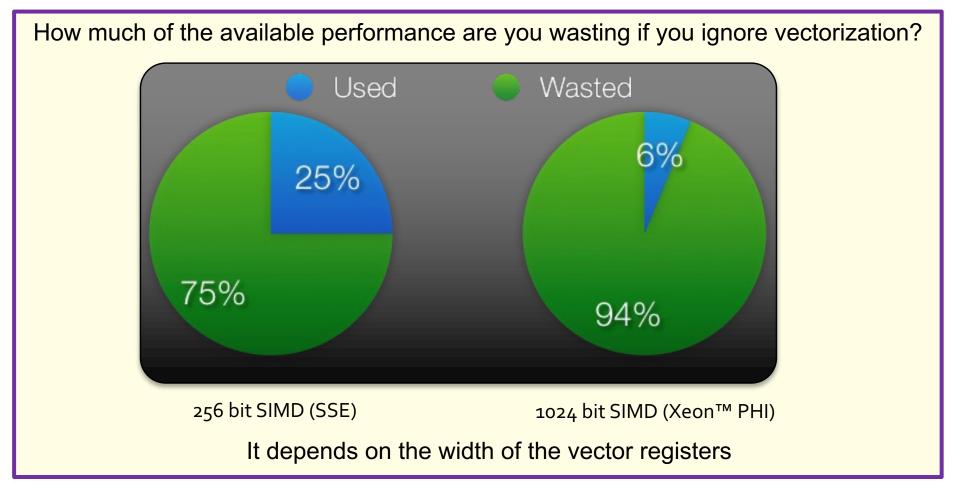

## The importance of using the vector units on your CPU

Writing code to fully utilize vector units can be difficult ... most applications make poor use of the vector units.

In one corporate sponsored study\* of leading applications in engineering and scientific computing, of the instructions retired, on average only 4% were vector instructions.

<sup>\*</sup> I do not have permission to share any details on this study ... but the result speaks for itself

# Let's consider a specific example to understand how vectorization works in software

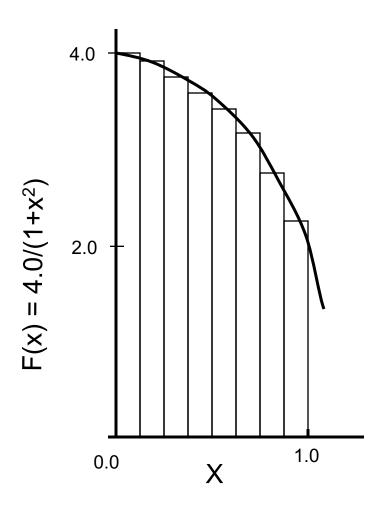

#### **Example Problem:** Numerical Integration

Mathematically, we know that:

$$\int_{0}^{1} \frac{4.0}{(1+x^2)} dx = \pi$$

We can approximate the integral as a sum of rectangles:

$$\sum_{i=0}^{N} F(x_i) \Delta x \approx \pi$$

Where each rectangle has width  $\Delta x$  and height  $F(x_i)$  at the middle of interval i.

# Serial PI program

Literals as double (no-vec), 0.012 secs Literals as Float (no-vec), 0.0042 secs

```

static long num_steps = 100000;

float step;

int main ()

float x, pi, sum = 0.0;

int i:

step = 1.0/(float) num steps;

for (i=0;i< num_steps; i++){

x = (i+0.5)*step;

sum = sum + 4.0/(1.0+x*x);

pi = step * sum;

```

By default, literals (such as 0.5) are double precision. So, all arithmetic involving such literals is done in double precision which reduces how many values can be packed into vector registers).

To avoid this problem, you must indicate the literal is a float by adding and 'f' at the end of the number (e.g. 0.5f).

Normally, I'd use double types throughout to minimize roundoff errors especially on the accumulation into sum. But to maximize impact of vectorization for these exercise, we'll use float types.

#### Explicit vectorization of our Pi Program: Step 1 ... Unroll the loop

We need one interation to fit in the vector unit

What is the width of your vector unit?

```

We'll use SSE which is 128 bits wide.

float pi unroll(int num steps)

A float in C is 32 bits wide ... 4 floats fits in 128 bits

float step, x0, x1, x2, x3, pi, sum = 0.0;

So, unroll the loop by four

step = 1.0f/(float) num steps;

for (int i=1;i<= num steps; i=i+4){

//unroll by 4, assume num steps%4 = 0

x0 = (i-0.5f)*step;

x1 = (i+0.5f)*step;

x2 = (i+1.5f)*step;

x3 = (i+2.5f)*step;

sum += 4.0f*(1.0f+x0*x0) + 1.0f/(1.0f+x1*x1) + 1.0f/(1.0f+x2*x2) + 1.0f/(1.0f+x3*x3));

pi = step * sum;

return pi;

```

#### Explicit SSE\* vectorization of our Pi Program: Step 2 ... Add SSE intrinsics

```

#include <immintrin.h> ← Function prototypes for C functions that map to SSE assembly code

float pi sse(int num steps)

float scalar one =1.0, scalar zero = 0.0, ival, scalar four =4.0, step, pi, vsum[4];

step = 1.0/(float) num steps;

m128 ramp = mm setr ps(0.5, 1.5, 2.5, 3.5);

m128 \text{ one} = mm \log 1 ps(\&scalar one);

Load

__m128 four = _mm_load1_ps(&scalar_four);

needed constants

into vector

m128 \text{ vstep} = mm \text{ load1 ps(&step)};

registers

m128 sum = mm load1 ps(&scalar zero);

m128 xvec; m128 denom; m128 eye;

for (int i=0;i< num steps; i=i+4) \{\leftarrow \text{Unroll the loop by 4 and assume (num steps } \% 4=0)\}

ival

= (float)i;

Vector ops on

= mm load1 ps(&ival);

eye

four floats at a

= mm mul ps( mm add ps(eye,ramp),vstep);

xvec

time ... i.e.,

packed single

denom = _mm_add_ps(_mm_mul_ps(xvec,xvec),one);

(ps) values.

= mm add ps( mm div ps(four,denom),sum);

sum

_mm_store_ps(&vsum[0],sum); ←Copy a packed single value in a vector(sum) register into a float array (vsum)

pi = step * (vsum[0]+vsum[1]+vsum[2]+vsum[3]);

return pi;

```

The vast majority of programmers never write explicitly vectorized code.

It is important to understand explicit vectorization so you appreciate what the compiler does to vectorize code for you

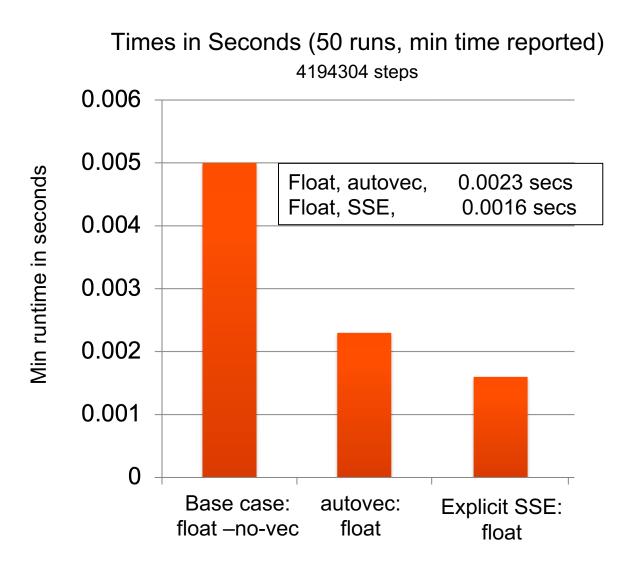

## PI program Results:

- Intel Core i7, 2.2 Ghz, 8 GM 1600 MHz DDR3, Apple MacBook Air OS X 10.10.5.

- Intel(R) C Intel(R) 64 Compiler XE for applications running on Intel(R) 64, Version 15.0.3.187 Build 20150408

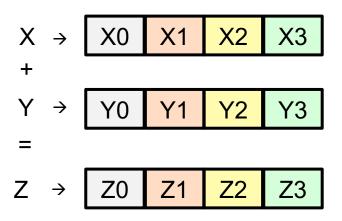

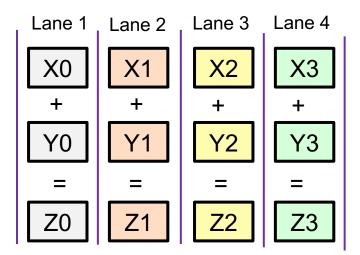

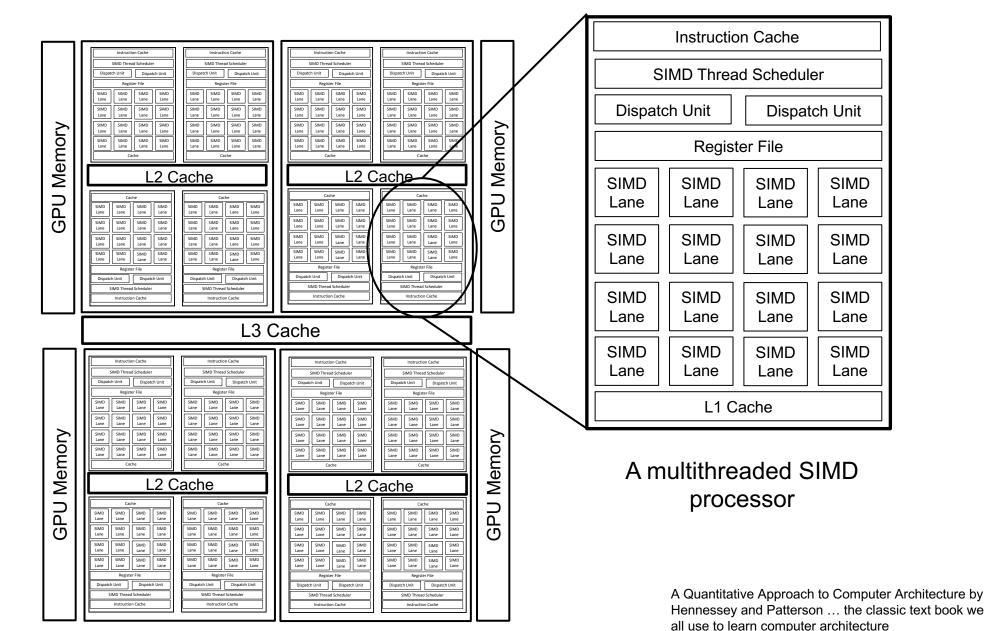

#### **SIMD Lanes**

It can help you reason about more complex algorithms or performance issues if you think about execution of instruction on a vector unit in terms of a number of SIMD lanes.

#### **Vector operations acting on vectors**

#### **Vector operations as SIMD lanres**

# How do people actually use vectorization in practice?

#### **Compiler vectorization**

- Explicit Vectorization: Vector instructions built around vector registers.

- It is challenging and to programmers unfamiliar with assembly code, it's a foreign style of programming

- The code is not portable ... for example, moving to Arm CPUs broke all my x86 vector code

Most programmers settle for the vectorization the compiler can generate automatically.

- Compiler Vectorization: Organizes code into blocks, packs variables into vector registers, and uses vector instructions for the operations.

- Typically loop oriented ... unrolling loops to create blocks of instructions (though sometimes can create blocks from non-loop code using SLP ... Superword level parallelization)

- Vector registers are packed with single data types so compiler must deduce which type to use

Dependency analysis for values packed into vector registers must assume worst case scenarios ... therefore missing many opportunities for vector parallelism.

```

// Basic block SLP example

void foo ()

{

unsigned int *pin = &in[0];

unsigned int *pout = &out[0];

*pout++ = *pin++;

*pout++ = *pin++;

*pout++ = *pin++;

*pout++ = *pin++;

}

```

## **Enabling Compiler Vectorization**

Compiler vectorization is enabled with the flag –ftree-vectorize

```

% gcc -ftree-vectorize pi.c

```

- Compiler optimization levels O2 and O3 imply vectorization

- O2 optimization will optimize code, but it will be conservative in the optimizations to assure the code is correct and does not greatly expand the size of the executable.

- O3 optimization is aggressive and will take chances with order of instructions and will potentiall

greatly increase the size of the executable.

```

% gcc -O3 pi.c

```

- Other compiler flags to consider (for gnu compilers)

- -Ofast relax arithmetic rules and freely reorder operations to maximize performance

- -finfo-opt-vec generate information on loops that were or were-not vectorized (doesn't work on Arm)

#### Helping the compiler vectorize

- When in doubt, the compiler will do the safe thing and not vectorize your code

- Knowing how explicit vectorization works, it's clear the compiler needs:

- Countable innermost loops

```

// Countable loop: .. But maybe aliasing? // Uncountable loop: while (--n > 0 L) *q++ = *p++; while (*p != NULL) *q++ = *p++;

```

Avoid aliasing problems

```

// Tell compiler to ignore potential aliasing

#pragma GCC ivdep

while (--n > 0 L) *q++ = *p++;

```

Types must be consistent

```

float x, step, sum;

for (i=0;i< num_steps; i++){

x = (i+0.5)*step;

sum = sum + 4.0/(1.0+x*x);

}

The literals 0.5, 4.0 and 1.0 are double by default. So, vectorization over double types even though variables are float

```

#### **Optimizing vector code**

- Occupancy

- You need enough vectorizable work to keep all the SIMD lanes fully occupied

- Converged execution flow

- Conditional logic prevents vectorization or causes subset of SIMD lanes to pause/no-op

for(i=0; i

$$<$$

N;i++) if(c[i]!=0.0) a[i]=b[i]/c[i];

- Memory coalescence

- Stride one memory access across lanes is best

for(i=0; i<N;i++) a[i]=b[i]+c[i];

for(i=0; i<N;i++) a[i]=b[i+2]+c[i+3];

- Fixed strides may work (depending the quality of the vectorizer)

for(i=0; i<N;i++) a[i]+=b[c[i]];

- Irregular meory access patterns break vectorization.

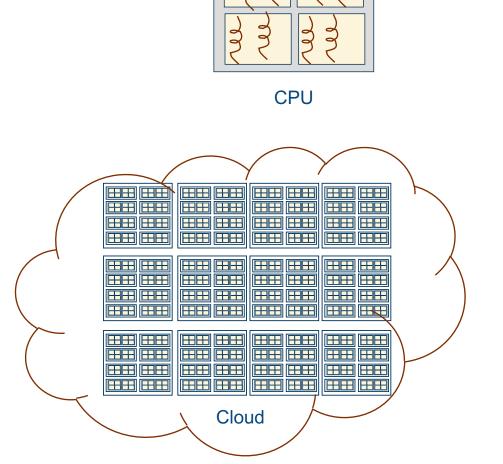

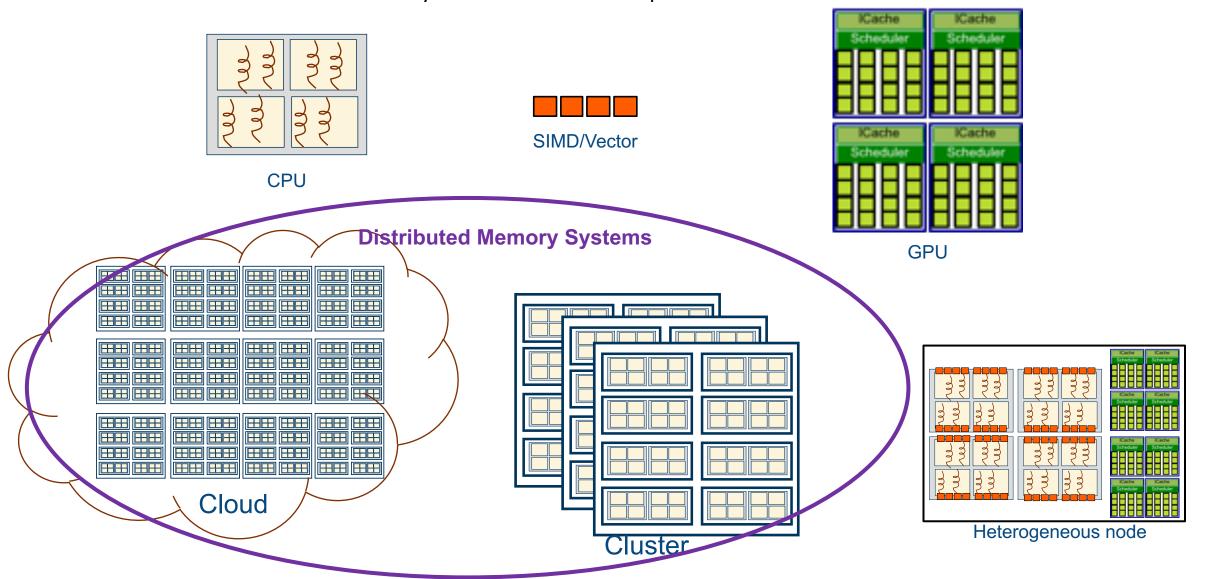

### For hardware ... parallelism is the path to performance

All hardware vendors are in the game ... parallelism is ubiquitous so if you care about getting the most from your hardware,

you will need to create parallel software.

Cloud

Heterogeneous node

#### The "BIG idea" Behind GPU programming

#### Traditional Loop based vector addition (vadd)

```

int main() {

int N = \dots;

float *a, *b, *c;

a* =(float *) malloc(N * sizeof(float));

// ... allocate other arrays (b and c)

// and fill with data

for (int i=0;i<N; i++)

c[i] = a[i] + b[i];

```

#### **Data Parallel vadd with CUDA**

```

// Compute sum of length-N vectors: C = A + B

void global

vecAdd (float* a, float* b, float* c, int N) {

int i = blockIdx.x * blockDim.x + threadIdx.x;

if (i < N) c[i] = a[i] + b[i];</pre>

Assume a GPU with

unified shared memory

int main () {

... allocate on host,

visible on device too

int N = \dots;

float *a, *b, *c;

cudaMalloc (&a, sizeof(float) * N);

// ... allocate other arrays (b and c)

// and fill with data

// Use thread blocks with 256 threads each

vecAdd <<< (N+255)/256, 256 >>> (a, b, c, N);

```

### How do we execute code on a GPU: The SIMT model (Single Instruction Multiple Thread)

Turn kernel code into a scalar work-item

```

// Compute sum of order-N matrices: C = A + B

void global

matAdd (float* a, float* b, float* c, int N) {

int i = blockIdx.x * blockDim.x + threadIdx.x;

int j = blockIdx.y * blockDim.y + threadIdx.y;

if (i < N && j<N) c[i][j] == a[i][j] + b[i][j];</pre>

int main () {

int N = \dots;

float *a, *b, *c;

cudaMalloc (&a, sizeof(float) * N);

// ... allocate other arrays (b and c)

// and fill with data

// define threadBlocks and the Grid

dim3 dimBlock(4,4);

dim3 dimGrid(4,4);

// Launch kernel on Grid

matAdd <<< digGrid,dimBlock>>> (a, b, c, N);

```

This is CUDA code

4. Run on hardware Map work-items onto an designed around the N dim index space. same SIMT execution model Map data structures onto the same index

space

### A Generic GPU (following Hennessey and Patterson)

#### For hardware ... parallelism is the path to performance

All hardware vendors are in the game ... parallelism is ubiquitous so if you care about getting the most from your hardware, you will need to create parallel software.

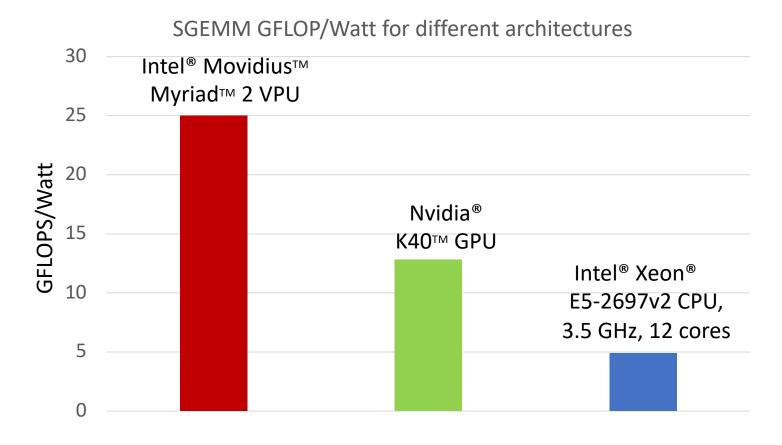

#### If you care about power, the world is heterogeneous?

Specialized processors doing operations suited to their architecture are more efficient than general purpose processors.

Hence, future systems will be increasingly heterogeneous ... GPUs, CPUs, FPGAs, and a wide range of accelerators

Source: Suyash Bakshi and Lennart Johnsson, "A Highly Efficient SGEMM Implementation using DMA on the Intel/Movidius Myriad-2. IEEE International Symposium on Computer Architecture and High Performance Computing, 2020

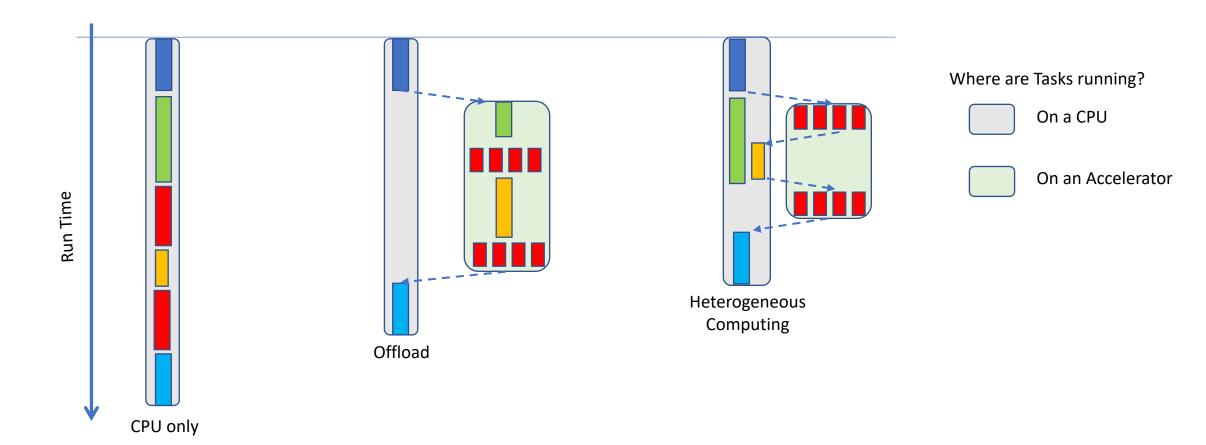

### Offload vs. Heterogeneous computing

- Offload: The CPU moves work to an accelerator and waits for the answer.

- Heterogeneous Computing: Run sub-problems in parallel on the hardware best suited to them.

#### For hardware ... parallelism is the path to performance

All hardware vendors are in the game ... parallelism is ubiquitous so if you care about getting the most from your hardware, you will need to create parallel software.

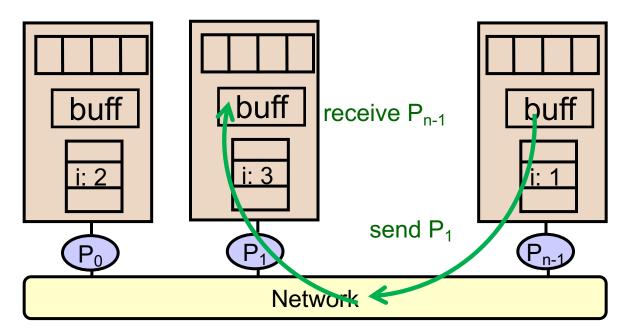

#### Programming Model for distributed memory systems

- Programs execute as a collection of processes.

- Number of processes usually fixed at program startup time

- Local address space per node -- NO physically shared memory.

- Logically shared data is partitioned over local processes.

- Processes communicate by messages ... explicit send/receive pairs

- Synchronization is implicit by communication events.

- MPI (Message Passing Interface) is the most commonly used API

A collection of n

MPI processes

(P<sub>0</sub> to P<sub>n-1</sub>)

running on n

nodes

#### Throughput oriented computing

- A common pattern occurs when you need to run a large collection of problems that are truly independent

- Map/Reduce: Run many independent programs (map) and combine results once when they are all done (reduce). Hadoop and Spark are optimized for this type of job

- Parameter studies: Optimize a set of parameters by sampling a set of parameters and collecting overall statistics when done. Example:

Finding a set of small molecules (ligands) that dock with a protein. It's geometry dependent so many ligand orientations must be tested.

- Data Parallel jobs where each data point is a large compute intensive operation without any dependencies to manage.

These problems are ideally suited to running in the cloud.

#### Clusters vs the Cloud for parallel programmers

Beyond embarrassingly parallel, throughput-oriented computing, the cloud is different from cluster computing (unless you pay to define a dedicated cluster in the cloud)

| Platform*                       | HPC Cluster                                                    | Cloud                                                                      |  |

|---------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|--|

| Execution<br>Agent              | Processes                                                      | Microservices                                                              |  |

| Memory                          | Distributed memory, local memory owned by individual processes | Distributed object store (in memory) backed by a persistent storage system |  |

| Typical<br>Execution<br>Pattern | SPMD                                                           | Event driven tasks,<br>FaaS, and Actors                                    |  |

# Parallel Systems are great, but they are not much use without parallel software

#### **Parallel Software**

- Vectorization is defined around a narrow range of data parallel operations. That narrow scope and the limited complexity in how data is laid out allows automatic vectorization to work.

- Automatic parallelization beyond vectors, however, has never adequately worked.

Why:

- Decomposing a problem into tasks that can run in parallel effectively is not directly apparent in the code for cases beyond vectors extracted from basic loops

- Decomposing data to manage memory movement across multiple processing elements requires reasoning across the full range of functions in a program.

- Typcally, the algorithm that is best for a serial program is different from the algorithm that is berst for parallel execution.

- Hence, software for parallel systems requires parallel programmers using programming models that explicitly support parallelism.

## Consider the state of programming models from the early days of parallel computing.

Parallel programming environments in the 90's

| ABCPL<br>ACE<br>ACT++<br>Active messages<br>Adl                                                                                   | C4<br>CC++<br>Chu<br>Charlotte<br>Charm                                                                                              | DOLIB DOME DOSMOS. DRL DSM-Threads                                                                                                | HAsL.<br>Haskell<br>HPC++<br>JAVAR.<br>HORUS                                                                                    | P4-Linda<br>Glenda<br>POSYBL<br>Objective-<br>Linda                                                                                          | Nano-Threads<br>NESL<br>NetClasses++<br>Nexus<br>Nimrod                                                                     | Parallel-C++<br>Parallaxis<br>ParC<br>ParLib++<br>ParLin                                                        | QPC++<br>PVM<br>PSI<br>PSDM<br>Quake                                                                                            | Sthreads<br>Strand.<br>SUIF.<br>Synergy<br>Telegrphos                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Adl Adsmith ADDAP AFAPI ALWAN AM AMDC AppLeS Amoeba ARTS Athapascan-0b Aurora Automap bb_threads Blaze BSP BlockComm C*. "C* in C | Charm Charm++ Cid Cilk CM-Fortran Converse Code COOL CORRELATE CPS CRL CSP Cthreads CUMULVS DAGGER DAPPLE Data Parallel C DC++ DCE++ | DSM-Threads Ease . ECO Eiffel Eilean Emerald EPL Excalibur Express Falcon Filaments FM FLASH The FORCE Fork Fortran-M FX GA GAMMA | HORUS HPC IMPACT ISIS. JAVAR JADE Java RMI javaPG JavaSpace JIDL Joyce Khoros Karma KOAN/Fortran-S LAM Lilac Linda JADA WWWinda | Linda LiPS Locust Lparx Lucid Maisie Manifold Mentat Legion Meta Chaos Midway Millipede CparPar Mirage MpC MOSIX Modula-P Modula-2* Multipol | Nimrod NOW Objective Linda Occam Omega OpenMP Orca OOF90 P++ P3L p4-Linda Pablo PADE PADRE PADRE Panda Papers AFAPI. Para++ | ParLin Parmacs Parti pC pC++ PCN PCP: PH PEACE PCU PET PETSc PENNY Phosphorus POET. Polaris POOMA POOL-T PRESTO | Quake Quark Quick Threads Sage++ SCANDAL SAM pC++ SCHEDULE SCITL POET SDDA. SHMEM SIMPLE Sina SISAL. distributed smalltalk SMI. | Telegrphos SuperPascal TCGMSG. Threads.h++. TreadMarks TRAPPER uC++ UNITY UC V ViC* Visifold V- NUS VPE Win32 threads WinPar WWWinda XENOOPS |

| C** CarlOS Cashmere                                                                                                               | DDD<br>DICE.<br>DIPC                                                                                                                 | Glenda<br>GLU<br>GUARD                                                                                                            | ISETL-Linda<br>ParLin<br>Eilean                                                                                                 | MPI<br>MPC++<br>Munin                                                                                                                        | Paradigm Parafrase2 Paralation                                                                                              | P-RIO<br>Prospero<br>Proteus                                                                                    | SONiC<br>Split-C.<br>SR                                                                                                         | XPC<br>Zounds<br>ZPL                                                                                                                         |

## Consider the state of programming models from the early days of parallel computing.

Parallel programming environments in the 90's

ABCPL ACE ACT++

Active messages

Adl

Adsmith ADDAP

AFAPI

ALWAN

AM

**AMDC**

AppLeS

Amoeba

**ARTS**

Athapascan-0b

Aurora Automap

bb threads

Blaze BSP

BlockComm

C\*.

"C\* in C

C\*\*

CarlOS

Cashmere

| C4   | DOLIB   | HAsL.   | P4-Linda | Nano-Threads | Parallel-C++ |

|------|---------|---------|----------|--------------|--------------|

| CC++ | DOME    | Haskell | Glenda   | NESL         | Parallaxis   |

| Chu  | DOSMOS. | HPC++   | POSYBL   | NetClasses++ | ParC         |

This diversity made the life of a parallel application developer much more difficult.

Different communities and different system-vendors had different "favorite" preprogramming models. Developers had to waste vast ammounts of time porting applications to different systems.

Furthermore, engineering is a "zero-sum" game ... that is time spent supporting multiple programming models means less time to make a small number of common models just work.

|                 |           | ,           |           |            |          |

|-----------------|-----------|-------------|-----------|------------|----------|

| DAGGER          | TOIK      | LAWI        | MpC       | IADKL      | I OL I.  |

| DAPPLE          | Fortran-M | Lilac       | MOSIX     | Panda      | Polaris  |

| Data Parallel C | FX        | Linda       | Modula-P  | Papers     | POOMA    |

| DC++            | GA        | JADA        | Modula-2* | AFAPI.     | POOL-T   |

| DCE++           | GAMMA     | WWWinda     | Multipol  | Para++     | PRESTO   |

| DDD             | Glenda    | ISETL-Linda | MPI       | Paradigm   | P-RIO    |

| DICE.           | GLU       | ParLin      | MPC++     | Parafrase2 | Prospero |

| DIPC            | GUARD     | Eilean      | Munin     | Paralation | Proteus  |

**PVM** Strand. **PSI** SUIF. **PSDM** Synergy **Telegrphos** Quake Quark SuperPascal Quick TCGMSG. Threads.h++. Threads TreadMarks Sage++ **SCANDAL TRAPPER** SAM uC++pC++UNITY **SCHEDULE** UC SciTL V ViC\* **POET** SDDA. Visifold V-**SHMEM** NUS **SIMPLE VPE** Sina Win32 SISAL. threads distributed WinPar smalltalk WWWinda SMI. **XENOOPS** XPC **SONiC** Split-C. Zounds SR **ZPL**

Sthreads

QPC++

- In HPC, 2 programming environments dominate ... covering the major classes of hardware.

- MPI: distributed memory systems ... though it works nicely on shared memory computers.

OpenMP: Shared memory systems ...

• Even if you don't plan to spend much time programming with these systems ... a well rounded HPC programmer should know what they are and how they work.

- In HPC, 3 programming environments dominate ... covering the major classes of hardware.

- MPI: distributed memory systems ... though it works nicely on shared memory computers.

- OpenMP: Shared memory systems ... more recently, GPGPU too.

Then GPUs Came and things got a bit more messy

CUDA, OpenCL, Sycl, OpenACC, OpenMP ...: GPU programming (use CUDA if you don't mind locking yourself to a single vendor ... it is a really nice programming model)

• Even if you don't plan to spend much time programming with these systems ... a well rounded HPC programmer should know what they are and how they work.

- In HPC, 3 programming environments dominate ... covering the major classes of hardware.

- MPI: distributed memory systems ... though it works nicely on shared memory computers.

OpenMP: Shared memory systems ... more recently, GPGPU too.

CUDA, OpenCL, Sycl, OpenACC, OpenMP ...: GPU programming (use CUDA if you don't mind locking yourself to a single vendor ... it is a really nice programming model)

What's different today is C++. OpenMP and MPI work with C++, but they were not created with the structure, style, and capabilities of C++ in mind.

C++ contains threads as first class language elements, standard parallel containers and algorithms, a formal memory model, and a number of high-level programming models specifically designed around the language (e.g., Kokos, Sycl and TBB)

Fortunately, the C++ language design community is working on support for parallelism and painstakingly working to pull the best ideas into the core language.

- In HPC, 3 programming environments dominate ... covering the major classes of hardware.

- -(MPI:) distributed memory systems ... though it works nicely on shared memory computers.

- **OpenMP**: Shared memory systems ... more recently, GPGPU too.

- Covered in ESC

-CUDA, OpenCL, Sycl, OpenACC, OpenMP ...: GPU programming (use CUDA if you don't mind locking yourself to a single vendor ... it is a really nice programming model)

What's different today is C++. OpenMP and MPI work with C++, but they were not created with the structure, programming philosophy, and capabilities of C++ in mind.

C++ contains threads as first class language elements, standard parallel containers and algorithms, a formal memory model, and a number of high-level programming models specifically designed around the language (e.g., Kokos, Sycl and TBB)

Fortunately, the C++ language design community is working on this problem and painstakingly working to pull the best ideas into the core language. Much work remains to be done, but the progress so far is very exiling.

#### **Summary**

- High performance computing depends on parallel computing.

- Scientific programmers need to be comfortable with the full range of parallel systems:

- CPUs with multiple cores sharing an address space ... optimized for latency sensitive problems.

- Vector (or SIME) units integrated with the CPU.

- GPUs for compute intensive, high throughput problems.

- Distributed memory systems with heterogeneous nodes built from the above for extreme scale

- It's a lot to learn, but fortunately, these systems can be fully addressed with a modest number of parallel programming models ... we covered vectorization in this lecture and we'll cover the others over the next two weeks.

... But for now, let's forget parallel computing and more on to computer arithmetic.

It's boring, but if you care about high quality answers to your scientific problems, you need to understand that **Floating Point numbers are not real**