# Electronics, **DAQ** and signal processing techniques

Pierre-André Amaudruz

TRIUMF, Vancouver, BC, CANADA

#### What does DAQ mean?

Data AcQuisition...

**Data**

**information** "converted" into numbers to be able to digitally manipulate the "information"

**Acquisition** refers to the **Equipment** involved in the extraction, conversion and gathering of the "data"

How did we do it before our time?

### Pencil, Paper and Patience (PPP)

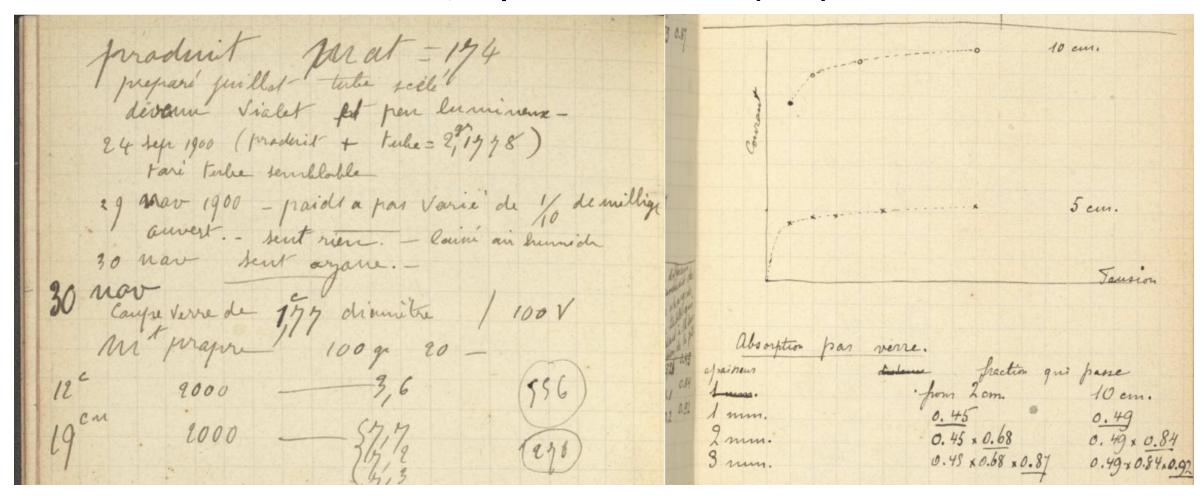

Curie, Marie, 1867-1934.

Nobel Prize 1903, Physics for her research of radiation phenomena.

Nobel Prize 1911, Chemistry for the discovery of polonium and radium.

Logbook Marie Curie ~1900

# Pencil, Paper, Patience and Ruler

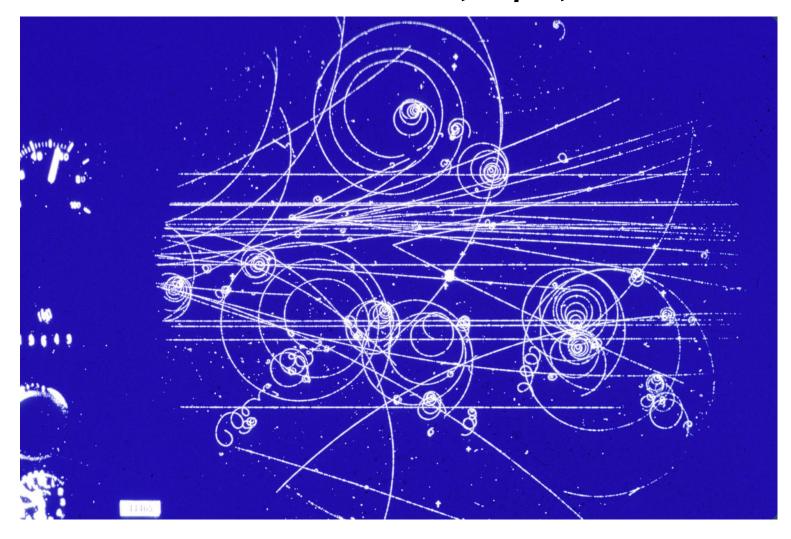

Bubble Chamber event INFN - National Institute for Nuclear Physics (Trieste Section) - Sistema Scientifico

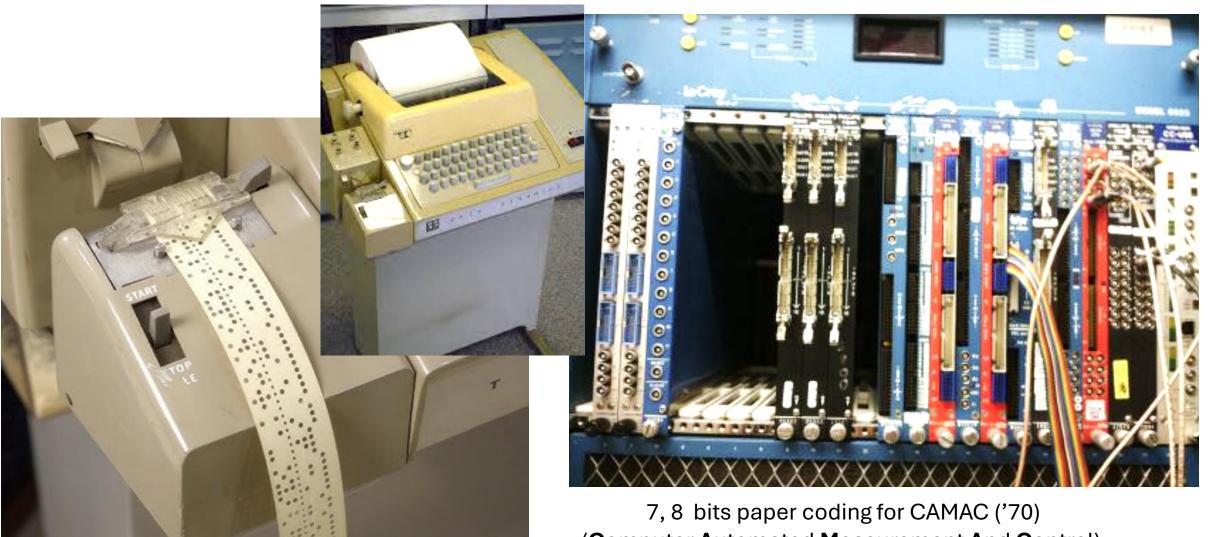

# **Teletypewriter**

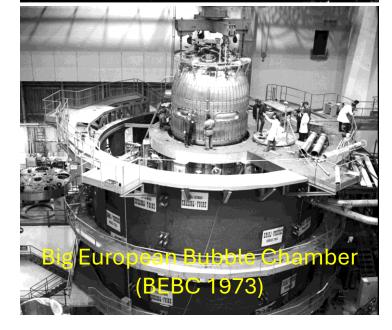

(Computer Automated Measurement And Control)

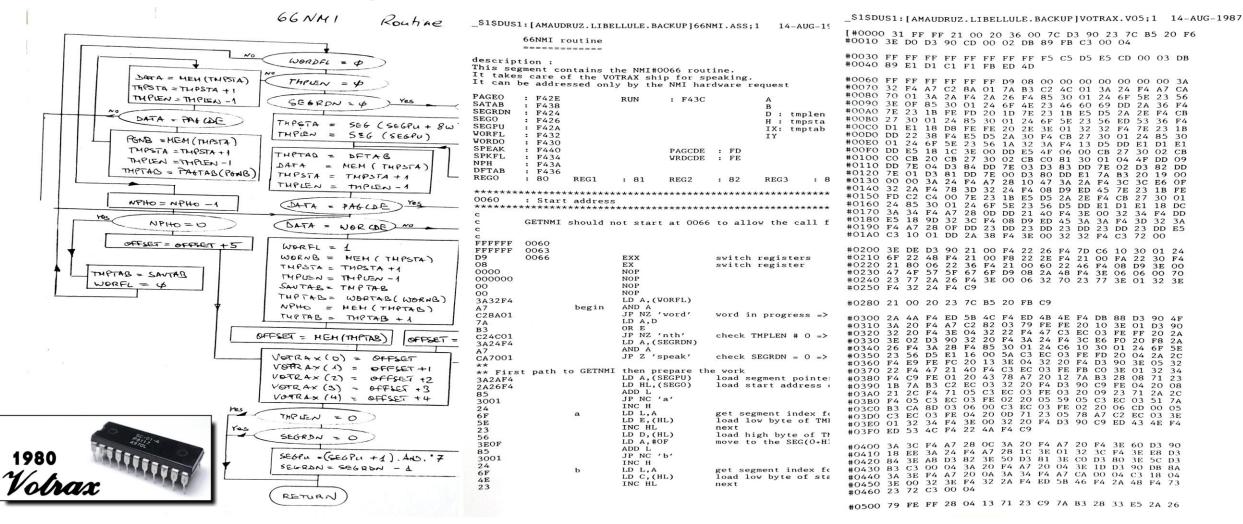

## Microprocessors (CPU Z80, MC6800, Intel8080)

block diagram

assembler

downloaded code

Votrax Voice Synthesizer IC (Text to speech converter)

#### **DAQ**

# What is DAQ now-a-days?

DAQ is everywhere meaning...

Where information needs to be collected and sent, the sensors information is first converted to digital/numerical format, transmitted and analyzed and eventually converted back to an analog form for human convenience (graph, text).

#### Examples:

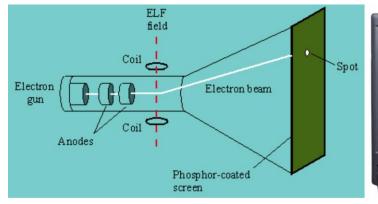

- Microphone (analog) A to D converter Digital storage (CD, memory) D to A convert Speaker (analog)

- Images (films, CCDs) A to D converter Digital storage (CD, DVD, memory) D to A convert CRT (analog)

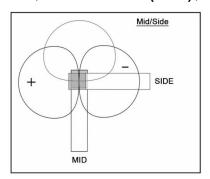

#### Stereo recording:

XY, ORTF, Mid-Side (MS), Blumlein, DIN

# What is DAQ now-a-days?

### In Physics:

- What "information" can we have access to?

- Quantitative data (position ({x, y, z}, {r, θ, z}), "event" Time, "signal" Amplitude, Charge, Magnetic Field, Temperature, Pressure conditions, ... momentum, energy, ...)

- Collect data using a combination of detectors/sensors to acquire the relevant parameters.

- Convert all in a digital form for easier processing.

#### **Experiments results**

https://www.nature.com/articles/s41586-023-06527-1

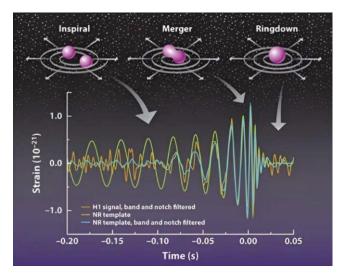

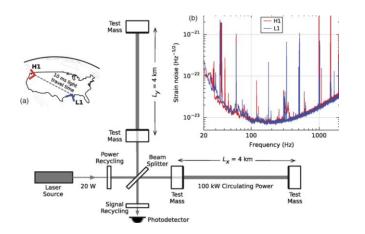

LIGO-Virgo-KAGRA (2016)

Laser Interferometer Gravitational-Wave Observatory Nobel 2017, Rainer Weiss, Barry Barish, Kip S. Thorne

https://phys.org/news/2024-07-creation-deep-algorithm-unexpected-gravitational.html

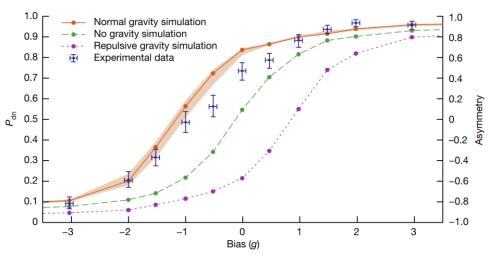

Alpha-g (2023)

Antihydrogen Laser Physics Apparatus

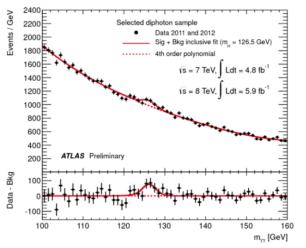

https://home.cern/resources/image/physics/higgs-collection-images-gallery

Nobel 2013, Peter Higgs, François Englert

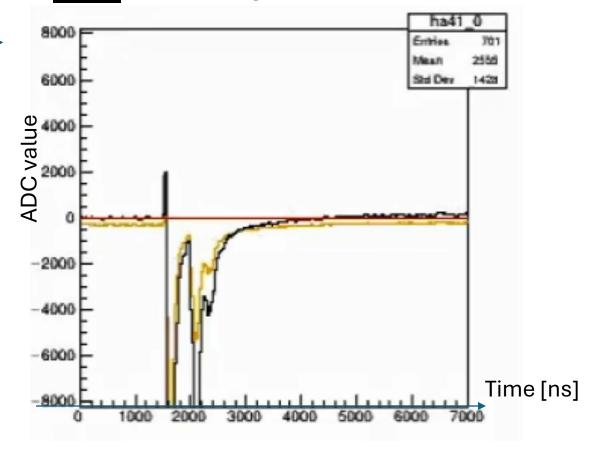

# Data path from the detector to the publication

DAQ in Experimental physics Dealing with equipment from the sensors (analog) ... to electrical analog signals... to digital representation... to the data acquisition and processing... to the data storage... to Analysis... to publications **Detector Physics Electronics** Computers Retention **Physics**

### We need to have some good knowledge of the different elements of the DAQ chain

#### Detector - Sensors

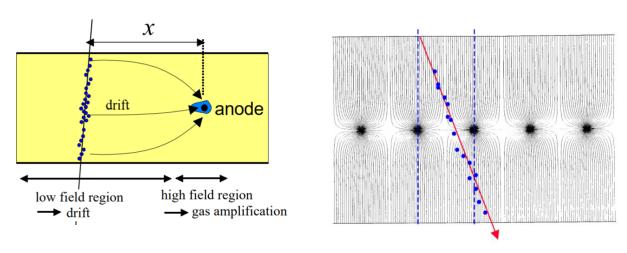

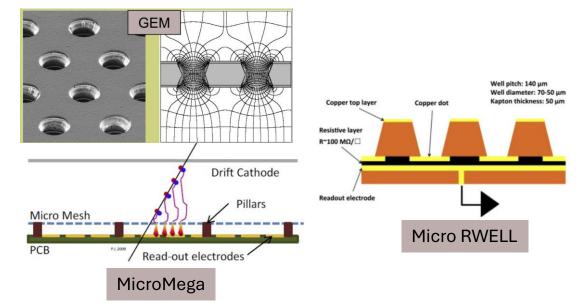

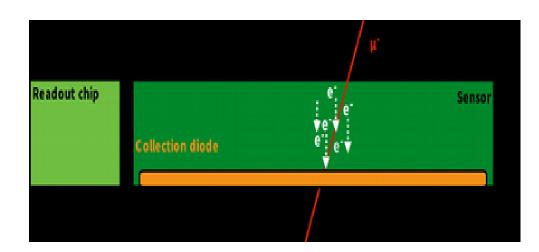

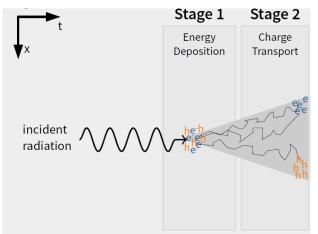

- Gas detector (MWPC, DC, TPC, Micro-Pattern-Gas-Detector [MicroMega, Gems, µ-Rwell, etc.)

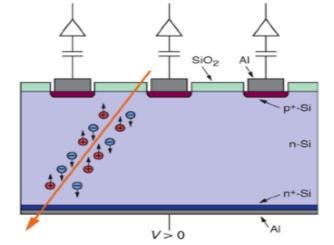

- Silicon based detector (Si-Strip Det., **SiPM**, etc.)

Marco Poli Lener (Frascati, CERN)

Photon based detector (MCP, PMTs, CMOS)

| Detector Type           | Gas Gain                         | Typical Use                 | Detector<br>Type | Position<br>Sensitivity | Energy<br>Resolution | Time<br>Resolution | Typical Use        |  |

|-------------------------|----------------------------------|-----------------------------|------------------|-------------------------|----------------------|--------------------|--------------------|--|

| Proportional<br>Counter | 10 <sup>2</sup> –10 <sup>4</sup> | X-ray/gamma<br>spectroscopy | Silicon<br>Strip | 1D / 2D                 | Good                 | Good               | Tracking           |  |

| MWPC                    | 10 <sup>4</sup>                  | Tracking                    | Silicon          |                         |                      |                    | Imaging, vertex    |  |

| Drift Chamber           | 10 <sup>4</sup>                  | Precision tracking          | Pixel            | 2D                      | Good                 | Good               | detection          |  |

| TPC                     | 10 <sup>4</sup>                  | 3D tracking                 | APD              | No                      | Moderate             | Excellent          | Photon detection   |  |

| GEM/Micromegas          | 10 <sup>3</sup> –10 <sup>5</sup> | High-rate physics           | SiPM             | No                      | Poor                 | Excellent          | Photon counting    |  |

| micro-RWELL             | >104                             | High-rate physics           | CCD/             | 2D                      | Good                 | Poor               | Astronomy, imaging |  |

| RPC                     | 10 <sup>5</sup>                  | Trigger systems             | CMOS             |                         | 2004 1001            |                    | ,,,                |  |

#### **Detector - Sensors**

$100e^{-} * 1E^{6}$  (gain) @  $1\mu s$  @  $50\Omega \sim 0.8$  mV

# We need to have some knowledge of the different elements of the DAQ chain Electronics

- Electrical Signal (pulse)

- Amplification Filtering Shaping

- Threshold Logic Signal

- Pulse conversion from analog to digital

- Counting

- Time, Amplitude, charge measurements

- Electronics instrumentation

- Clock, Trigger

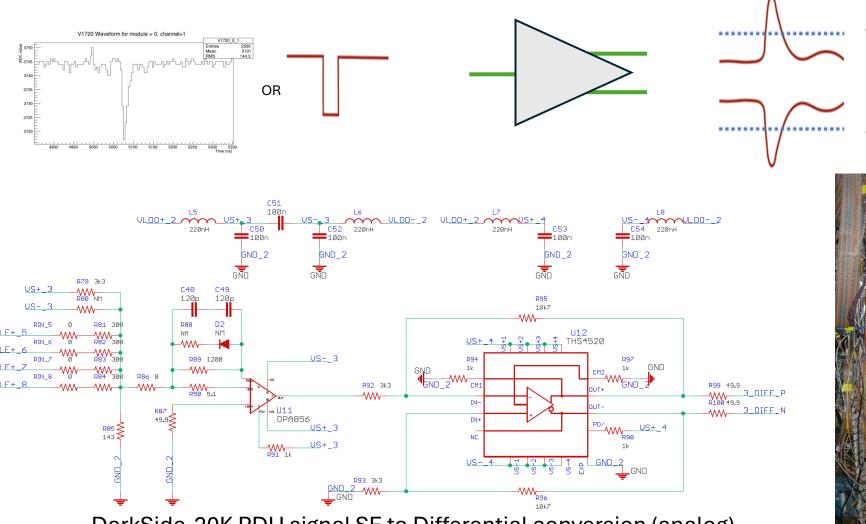

## **Electrical Signal (pulse)**

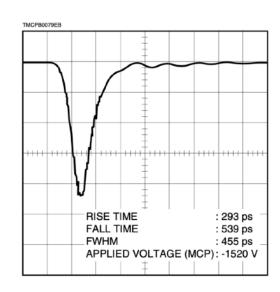

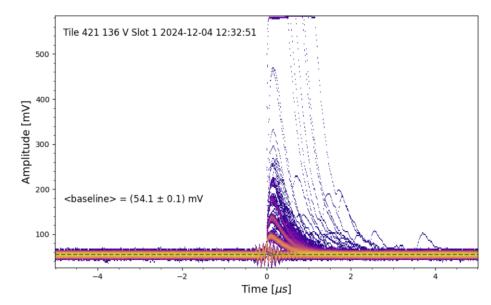

#### TIME RESPONSE (500 ps/div)

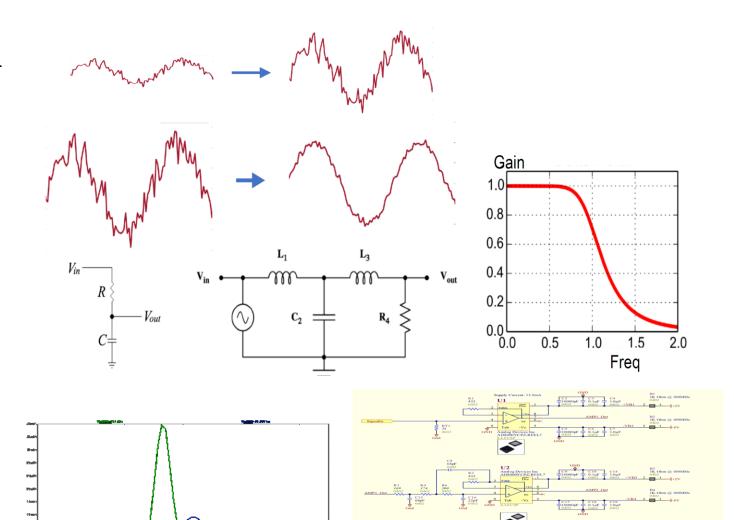

#### **Amplification - Filtering - Shaping**

Signal from the detectors may need to be boosted for transmission to next stage of signal processing (10mV..100mV).

Noise is also amplified!

Noise are mainly high-frequency that can be reduced by signal filtering

RC circuitry such as Butterworth, Low pass filter, High pass filter, Pass band filter, ...

Signal shaping act as filtering, but allows change of shape (timing, and amplitude)

Use to match digitizer characteristics (Nyquist–Shannon sampling theorem, bandwidth)

### **Electronics – Signal manipulation (conversion)**

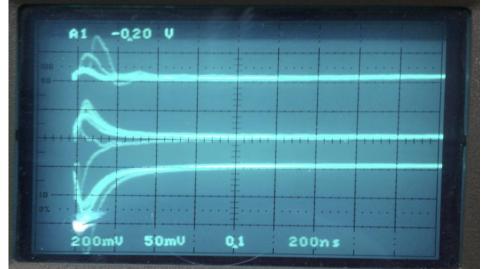

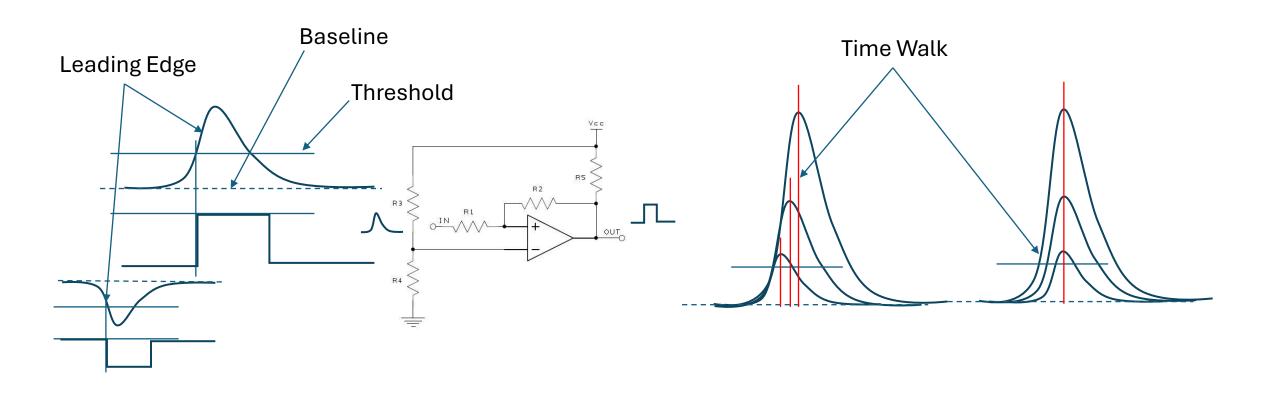

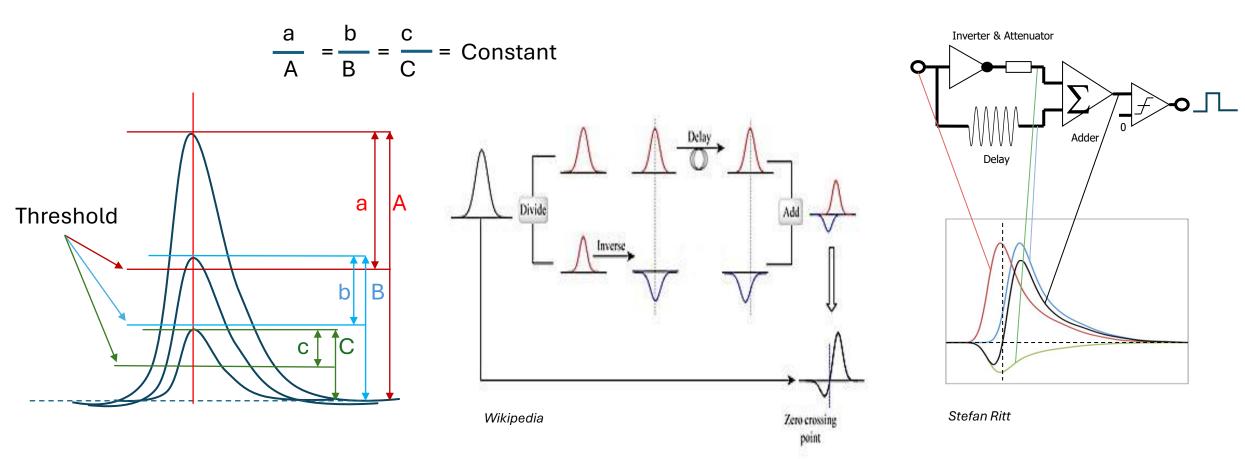

Threshold – Logic Signal

- Produce a new binary signal out of an Analog signal for presence detection or timing purpose

- Leading Edge detection [LE]

### **Electronics – Signal manipulation (conversion)**

Threshold – Logic Signal

- Produce a new binary signal out of an Analog signal for presence detection or timing purpose

- Constant Fraction Discriminator [CFD] dynamic threshold setting based on the signal amplitude

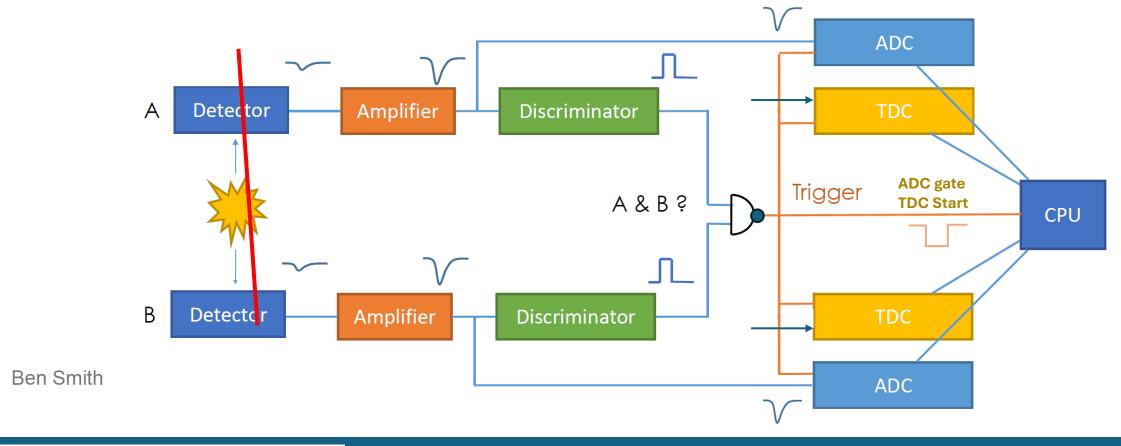

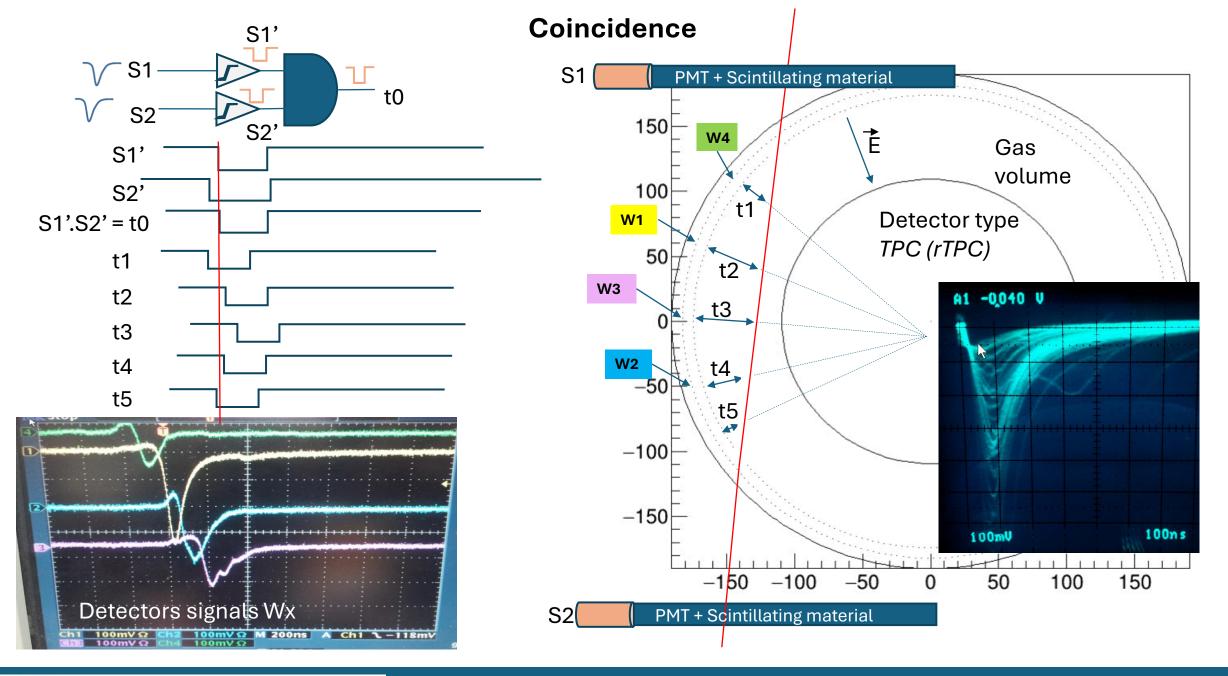

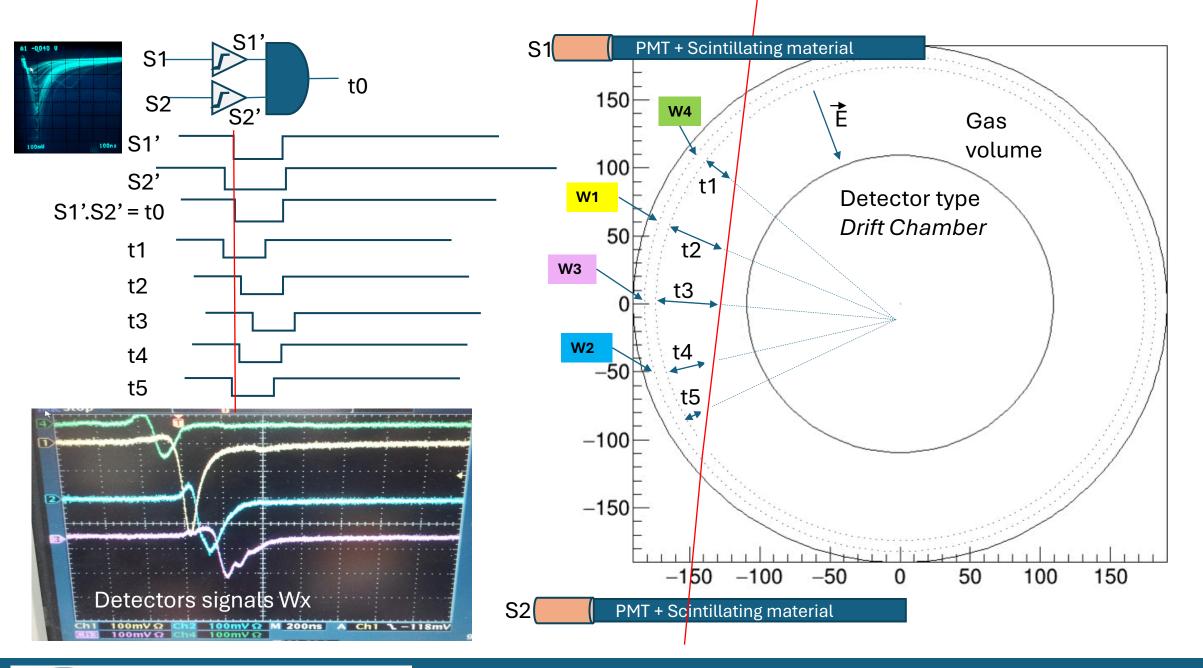

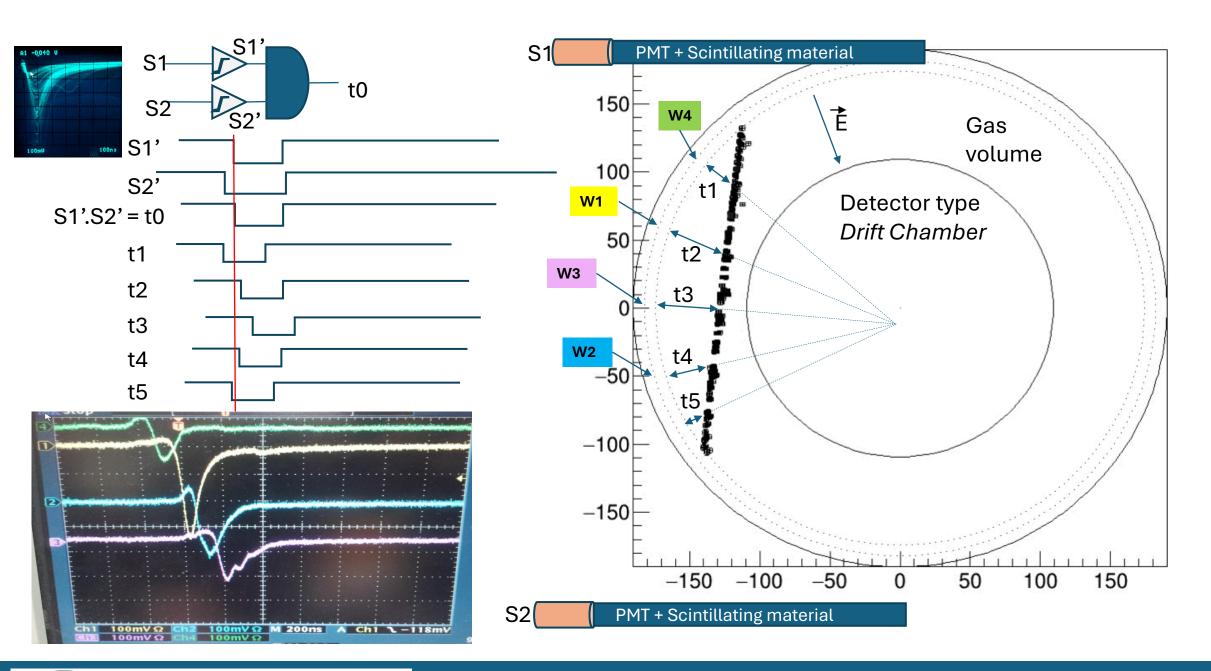

#### Coincidence

#### Logical Signal for Coincidence

Signal from different sensors may define the "event" of interest (EOI) by coincidence Generate a trigger that will initial the "event" recording

The same logic signal can be used as gate to the ADC and/or TDC (start conversion)

### Electronics - signal conversion from analog to digital

• Signal Levels, Transmission

• Counter Just count the pulses (Freq, Multichannel Scalers)

• ADCs measure amplitude / prominence, charge...

• TDCs measure relative time...

### **Electronics - Digital signal levels**

- Different type of digital and analog signals evolved based on:

- Logic Family

- Need for Speed

- Reduce current consumption

- Improve immunity to interference

LEMO00-RG174 MCX connectors and other Coaxial types (SMA, SMB, etc)

TTL (CMOS-TTL) VOL=

$$[0.0:0.4]V$$

, VOH=  $[2.4:5]V$

NIM VOL=0V, VOH=-0.8V, IOH= $[-14:-18]mA$ , IOL= $[-1:+1]mA$  @50 $\Omega$

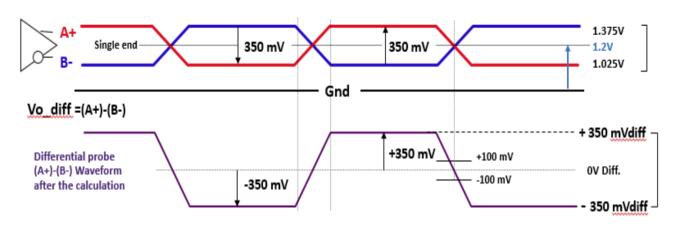

Differential LVDS VOL=1V, VOH=1.4V, VCM=1.2V, (400mV swing) @100 $\Omega$

For analog signal transmission, same type of cable

Pair of pins per signal Flat, Twisted pair cable

| types  | V <sub>ee</sub> | V <sub>bas</sub> | V <sub>haut</sub> | V <sub>diff</sub> | V <sub>cc</sub> | V <sub>cm</sub> |

|--------|-----------------|------------------|-------------------|-------------------|-----------------|-----------------|

| ECL    | -5,2 V          | –1,75 V          | -0,9 V            | -0,85 V           | GND             |                 |

| PECL   | GND             | 3,4 V            | 4,2 V             | 0,8 V             | 5,0 V           |                 |

| LVPECL | GND             | 1,6 V            | 2,4 V             | 0,8 V             | 3,3 V           | 2,0 V           |

#### **Electronics - Signal transmission**

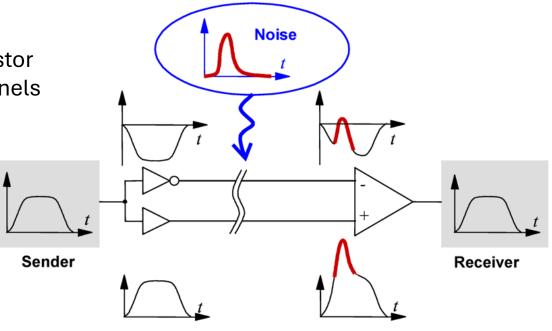

#### Signal disturbance

- Electromagnetic Interference (EMI) surrounding equipment, power supply

- Ground Loop signal return path (IEEE Std: two point intended to be at the same potential are in fact at a different electrical potential)

- Signal shielding cable bundle extra shielding

- Media transmission (electric cable coax, twisted pair, optical)

- Transmission path signal degradation

- Attenuation signal loss

- Impedance reflection, matching Z, termination resistor

- Cross-talk interference between neighbouring channels

### **Electronics - Signal transmission (Cables)**

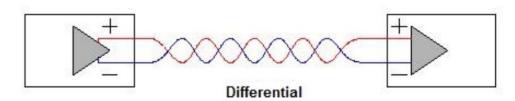

#### Single Ended versus Differential

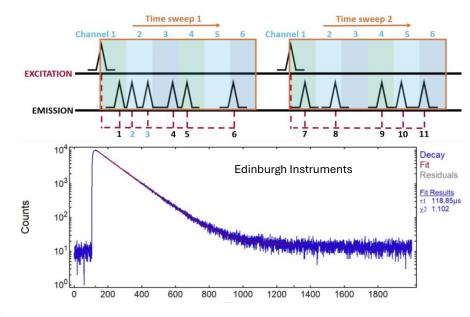

#### **Electronics - Counter**

Simplest thing you can do with digital signals - count! Visual / blind versions available

- Multi-channel scaler (MCS) "histogramming scaler"

- Counts pulses in each time bin (dwell time)

#### Struck SIS3820:

- 24/32-bit channel depth

- 250 MHz (ECL inputs) / 50 MHz (SE)

- ECL/TTL/LVDS or NIM inputs

- Flat cable/LEMO mixed input

- configurations

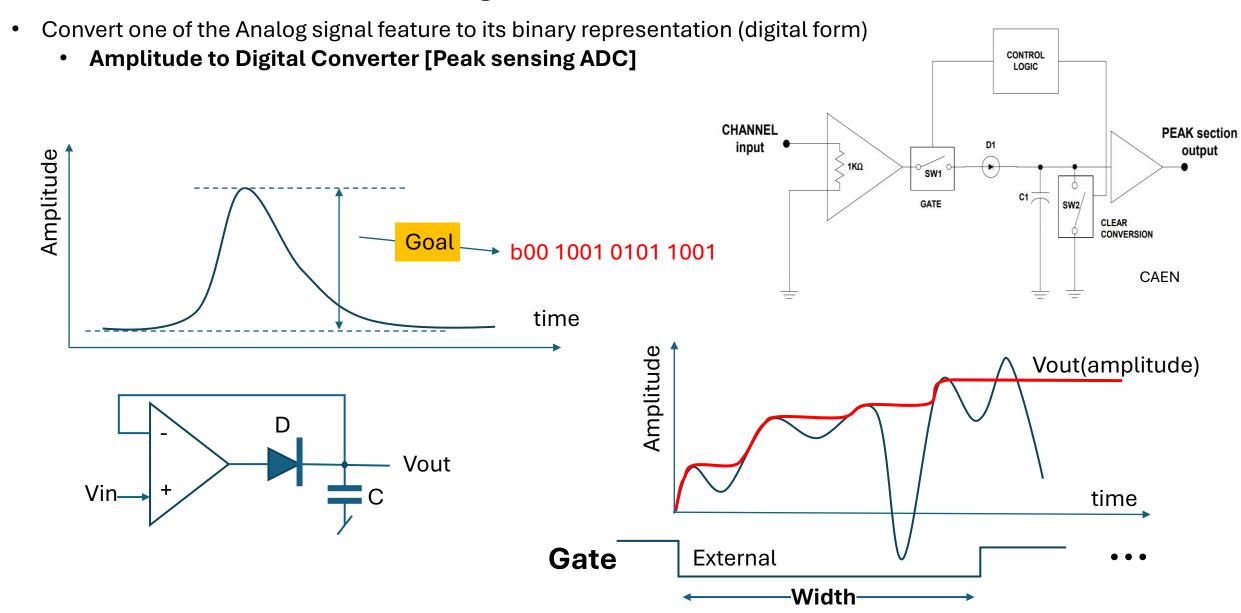

### Signal feature conversion

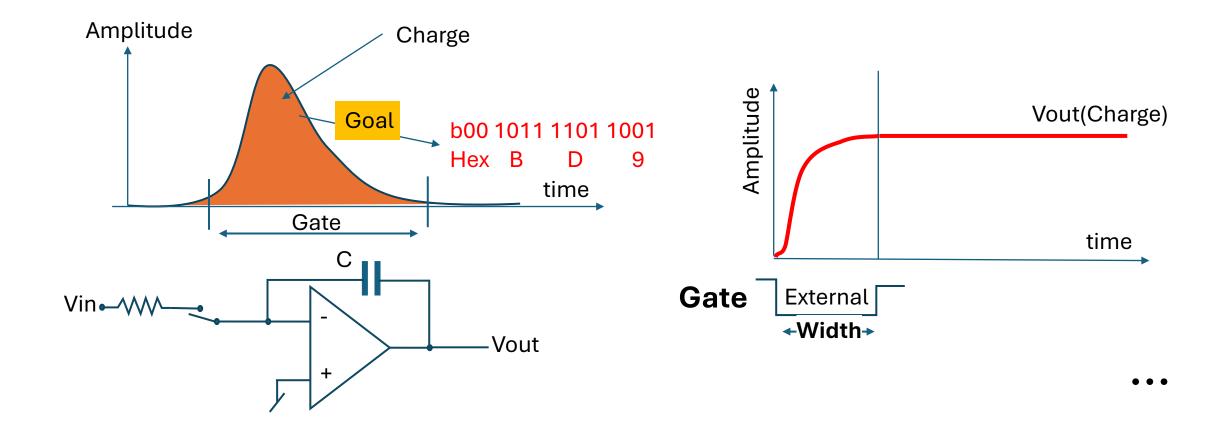

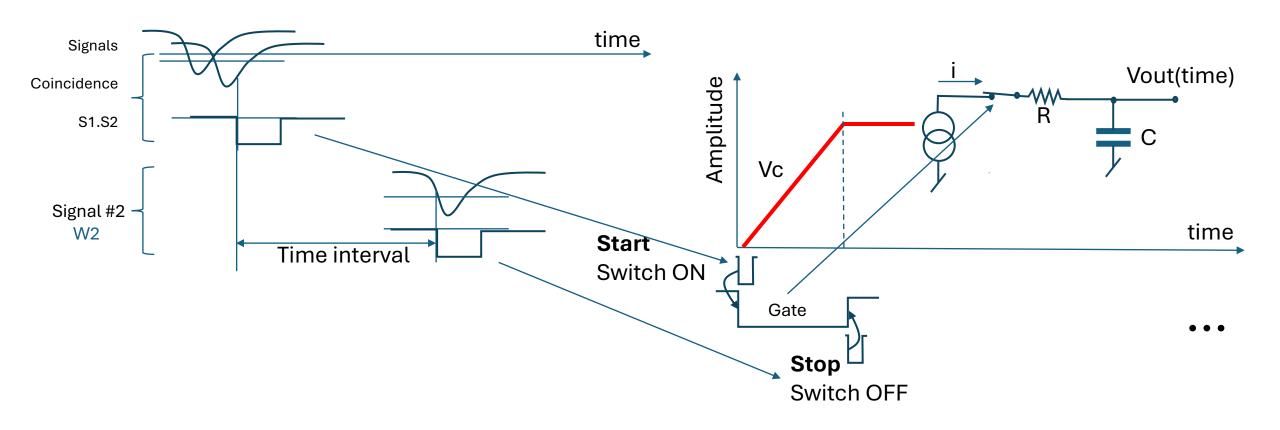

### Signal feature conversion

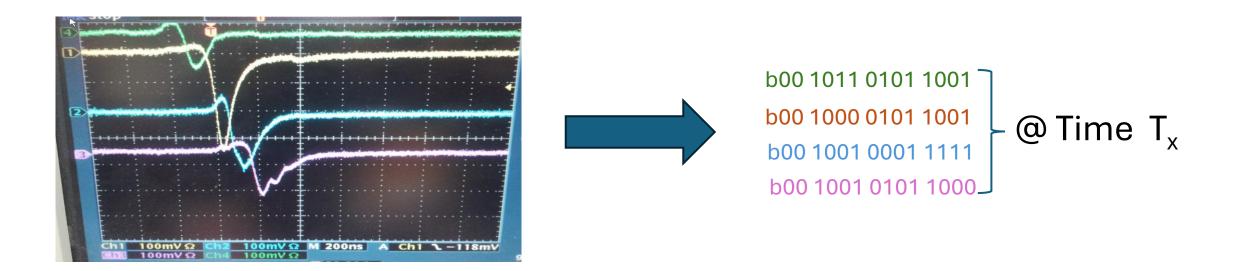

- Convert one of the Analog signal feature to its binary representation

- Charge to Digital Converter [QDC, or ADC (A to D)]

### Signal feature conversion

- Convert one of the Analog signal feature to its binary representation

- Time to Digital Converter [TDC]

### **Signal Digitization**

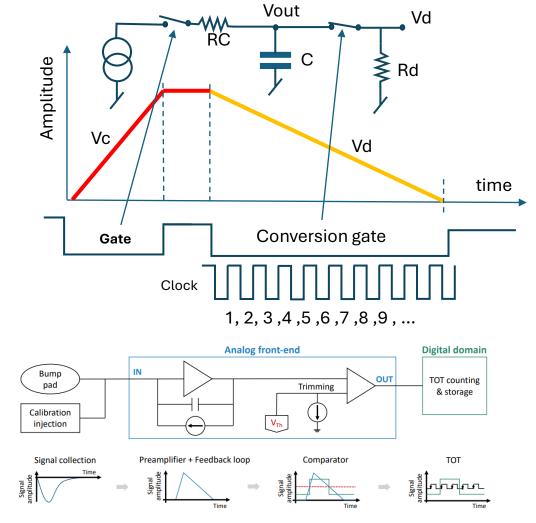

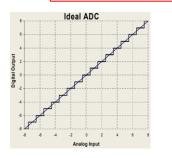

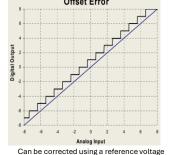

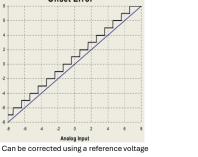

# **Electronics – Analog to Digital Converter**

- ADC translate the analog signal amplitude to its digital representation

- How fast can I convert a voltage level to its binary representation?

- Different methods

- Wilkinson ADC, dual-slope, etc.

Time of discharge proportional to Vout

Time measured in number clock period

Time over Threshold (TOT)

Limited by the clock rate for Hi-Resolution Conversion time dependent on the amplitude range Excellent linearity

Tradeoff: Speed versus Precision

The Tracker Group of the CMS Collaboration et al 2021 JINST 16 P12014

### **Signal Digitization**

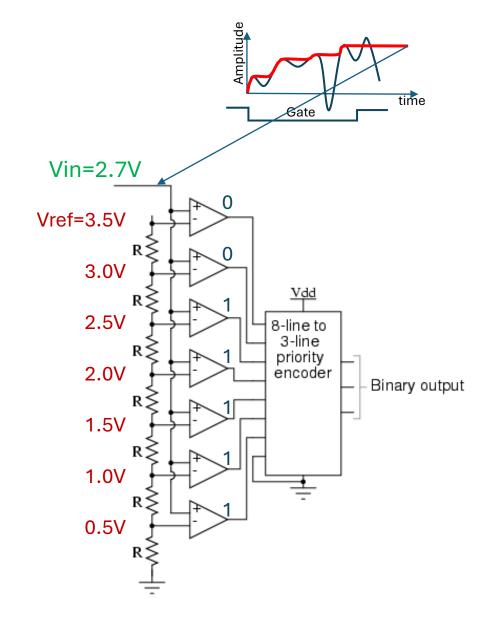

### **Electronics – AD Converter**

- ADC translate the analog signal to its digital representation

- Different methods

- 1, 2, n-bit Flash ADC (thermometer code)

Requires 2<sup>n</sup> Comparators for n output bits!

Requires calibrated "resistor chain"

Fastest conversion time – for small number of bits –

Possible to keep converting the input signal

#### **Electronics – AD Converter**

- ADC translate the analog signal to its digital representation

- Different methods

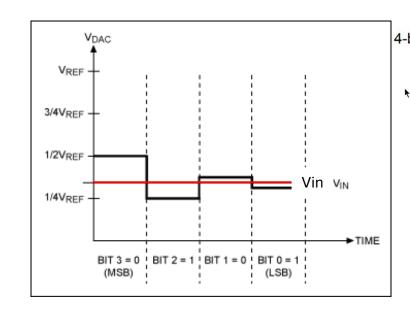

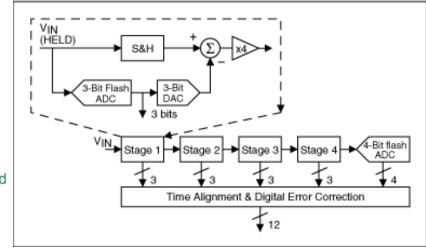

- Successive Approximation (SAR), Pipeline,

Combination of SAR and Flash.

####

Ideal 2-step Flash ADC

#### **Electronics – AD Converter**

- ADC translate the analog signal to its digital representation

- Different methods

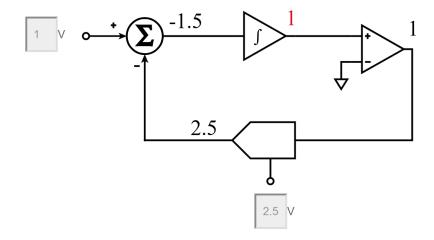

- Sigma-Delta ADC (oversampling, slow converter, high resolution)

Analog.com

Bit Stream: 1011101101101101101101101101101

Mean Output: 1

The integrator (sigma) output becomes 1V.

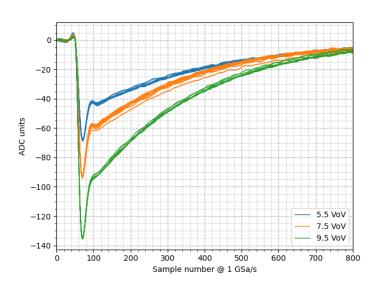

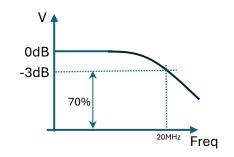

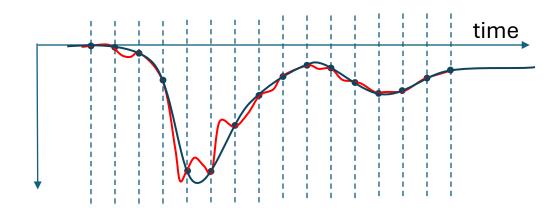

- Digitize the signal waveform

- But does this WF shape fits the real signal?

- Are you sampling the signal fast enough?

- What is the bandwidth of the incoming signal? <

V1740: 12 bit 62.5 MS/s ADC V2740: 16 bits 125MHz/s ADC

VX2745: bandwidth of 20 MHz (-3dB) VX2740: bandwidth of 50 MHz (-3dB)

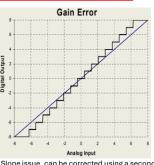

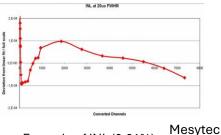

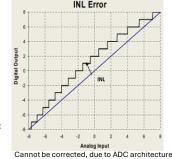

#### Amplitude, Charge, timing measurement errors!

Signal features can be extracted/improved in the digital world (DSP) only if the digital representation is faithful -> High sampling, good conversion characteristics

Example of INL (0.01%)

Cypress

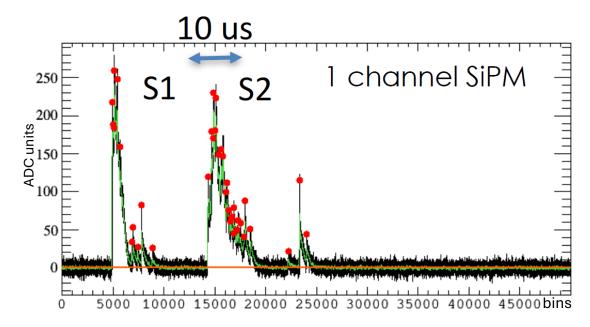

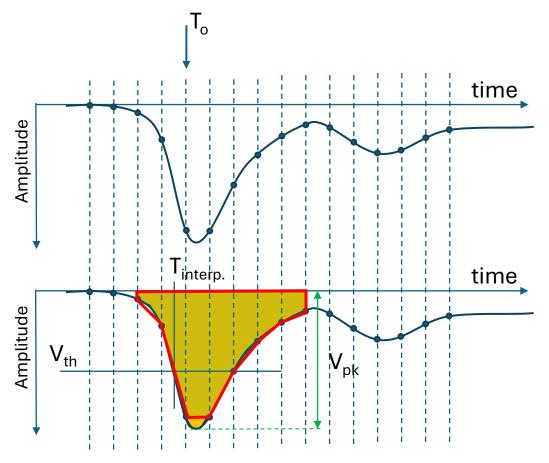

- Digitize the signal waveform, WaveForm Digitizer (WFD)

- Collect amplitude values at fix time interval in "real time"

- Extract signal features within the digital world, Digital Signal Processing (DSP)...

- Good representation of the WF out of the collected data (Q,  $V_{pk}$ , Time)

| Type of ADC              | Resolution (max. bits) | Conversion rate (max.) |

|--------------------------|------------------------|------------------------|

| Dual slope               | 12-20                  | 100 samples/s          |

| Successive approximation | 8-18                   | 10 Msamples/s          |

| Flash                    | 4-12                   | 10 Gsamples/s          |

| Pipeline                 | 8-16                   | 1 Gsample/s            |

| Delta-sigma              | 8-32                   | 1 Msample/s            |

Electronicdesign

8 channels Flash ADC 14-bit @ 500Msps (2ns) CAEN Meaning every 2ns, 14-bit data can be recorded. No deadtime!

**AD9653** (AD, 4ch., 16-bit, 125MS/s,  $2V_{p2p}$ , Pwr 0.7W, ~USD0.5K). **ADC12DJ5200RF** (TI, 2ch., 10-bit, 5.2 GS/s, 0.825  $V_{p2p}$ , Pwr 4W, USD3K) **AD9208** (AD, 2ch., 14-bit, 3 GS/s, 1.7 $V_{p2p}$ , Pwr 1.7W, ~USD1.4K).

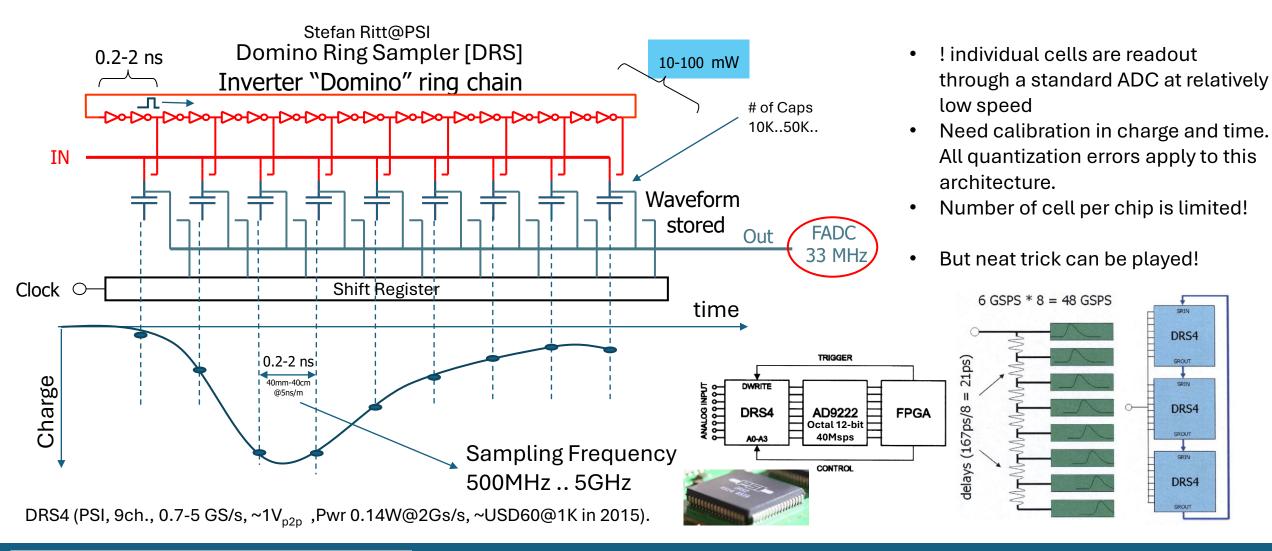

#### ASIC (Application Specific Integrated Circuit) – FIXED function - WFD chip

Yet another Waveform Digitizer architecture: Switched-Capacitor Array [SCA], an Ultra-Fast ADC ASIC

#### **Data Format**

#### Digitizer binary output data block (CAEN)

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17               | 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |

|------------------------------------------------------------|------------------------------------------|--|--|--|--|

| 1 0 1 0 EVENT SIZE                                         |                                          |  |  |  |  |

| BOARD ID BF RES 0 PATTERN / TRG OPTIONS CHANNEL MASK [7:0] |                                          |  |  |  |  |

| CHANNEL MASK [15:8] EVENT COUNTER 0x987f 39039             |                                          |  |  |  |  |

|                                                            | ER TIME TAG                              |  |  |  |  |

| 0 0 SAMPLE [1] - CH[0]                                     | 0 0 SAMPLE [0] - CH[0]                   |  |  |  |  |

| 0 0 SAMPLE [3] - CH[0]                                     | 0 0 SAMPLE [2] - CH[0]                   |  |  |  |  |

|                                                            |                                          |  |  |  |  |

|                                                            |                                          |  |  |  |  |

| 0 0 SAMPLE [N-1] - CH[0]                                   | 0 0 SAMPLE [N-2] - CH[0]                 |  |  |  |  |

| 0 0 SAMPLE [1] - CH[1]                                     | 0 0 SAMPLE [0] - CH[1]                   |  |  |  |  |

| 0 0 SAMPLE [3] - CH[1]                                     | 0 0 SAMPLE [2] - CH[1]                   |  |  |  |  |

|                                                            |                                          |  |  |  |  |

|                                                            | •••                                      |  |  |  |  |

| 0 0 SAMPLE [N-1] - CH[1]                                   | 0 0 SAMPLE [N-2] - CH[1]                 |  |  |  |  |

|                                                            |                                          |  |  |  |  |

|                                                            | •••                                      |  |  |  |  |

| 0 0 SAMPLE [1] - CH[15]                                    | 0 0 SAMPLE [0] - CH[15]                  |  |  |  |  |

| 0 0 SAMPLE [3] - CH[15]                                    | 0 0 SAMPLE [2] - CH[15]                  |  |  |  |  |

|                                                            |                                          |  |  |  |  |

|                                                            | •••                                      |  |  |  |  |

| 0 0 SAMPLE [N-1] - CH[15]                                  | 0 0 SAMPLE [N-2] - CH[15]                |  |  |  |  |

Binary format: 0000 0010 1101 0111

Hex format: 0x02D7

0xa0007d14 Header[0]

0x000002ff Header[1]

0xff00987f Header[2]

0x13a291b7 Header[3]

0x3c173c19 Data[n+1, n]

0x3c1a3c1a Data[n+3, n+2]

0x3c183c1b Data[n+5, n+4]

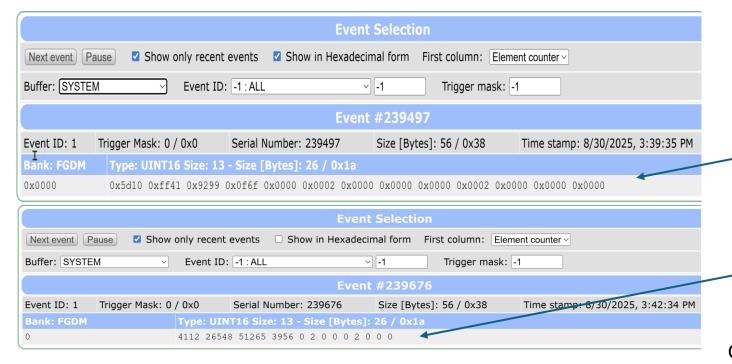

#### **Data Format**

GDM data block

Hexadecimal representation

Decimal representation

CAEN V1725: 14-bit@250Msps (Time bin = 4ns)

What about those data?

In Decimal format they make no sense!

1-> 0xa0007d14 0x000002ff 0xff00987f 0x13a291b7 0x3c1807d1 0x3c183c1c 0x3c1a3c19 0x3c1b3c18

9-> 0x3c1c3c16 0x3c193c12 0x3c1a3c19 0x3c163c18 0x3c183c1a 0x3c163c17 0x3c1f3c17 0x3c193c18

17-> 0x3c183c19 0x3c183c1a 0x3c193c1b 0x3c173c19 0x3c193c14 0x3c1b3c18 0x3c183c16 0x3c183c16

25-> 0x3c173c19 0x3c1a3c19 0x3c183c19 0x3c183c12 0x3c183c1a 0x3c193c19 0x3c1c3c14 0x3c173c19

33-> 0x3c193c14 0x3c193c16 0x3c153c1a 0x3c1b3c15 0x3c183c16 0x3c163c19 0x3c193c17 0x3c1c3c19

41-> 0x3c1a3c18 0x3c193c17 0x3c193c15 0x3c173c1b 0x3c183c17 0x3c163c18 0x3c173c15 0x3c163c1a

49-> 0x3c1c3c14 0x3c173c1c 0x3c193c16 0x3c183c19 0x3c193c16 0x3c173c1a 0x3c173c1a 0x3c173c17 0x3c1b3c18

57-> 0x3c163c13 0x3c193c17 0x3c163c19 0x3c1d3c15 0x3c1b3c18 0x3c163c19 0x3c1b3c1a 0x3c153c1c

65-> 0x3c183c1b 0x3c1c3c16 0x3c193c17 0x3c193c18 0x3c183c1a 0x3c193c1a 0x3c173c1b 0x3c173c1b

81-> 0x3c173c18 0x3c183c1b 0x3c173c17 0x3c163c19 0x3c183c18 0x3c163c19 0x3c153c17 0x3c153c15

89-> 0x3c183c15 0x3c183c19 0x3c13c13 0x3c173c1a 0x3c163c1a 0x3c173c1b 0x3c153c19 0x3c153c15 0x3c153c15

97-> 0x3c163c15 0x3c183c17 0x3c183c1b 0x3c173c1a 0x3c163c1a 0x3c173c19 0x3c153c19 0x3c153c15 0x3c153c15

97-> 0x3c163c1b 0x3c163c18 0x3c173c1a 0x3c163c1a 0x3c173c19 0x3c153c17 0x3c193c18 0x3c153c15

0x3c163c1b 0x3c163c18 0x3c183c1b 0x3c183c1d 0x3c183c15 0x3c153c17 0x3c193c18 0x3c153c15

### **Data Format R/W**

| Offset       | R/W | Mode | Function/Register                                                                |

|--------------|-----|------|----------------------------------------------------------------------------------|

| 0x0          | R/W | D32  | Control/Status register                                                          |

| 0x4          | R   | D32  | Module Id. and firmware revision register                                        |

| 0x8          | R/W | D32  | Interrupt configuration register                                                 |

| 0xC          | R/W | D32  | Interrupt control/status register                                                |

| 0x10         | R/W | D32  | Acquisition preset register                                                      |

| 0x14         | R   | D32  | Acquisition count register                                                       |

| 0x18         | R/W | D32  | LNE prescale factor register                                                     |

| 0x20         | R/W | D32  | Preset value register counter group 1 (1 to 16)                                  |

| 0x24         | R/W | D32  | Preset value register counter group 2 (17 to 32)                                 |

| 0x24<br>0x28 | R/W | D32  | Preset value register counter group 2 (17 to 32)  Preset enable and hit register |

|              |     |      | 8                                                                                |

| 0x100        | R/W | D32  | (Acquisition) Operation mode register                                            |

| 0x104        | R/W | D32  | Copy disable register                                                            |

| 0x108        | R/W | D32  | LNE channel select register (1 of 32)                                            |

| 0x10C        | R/W | D32  | PRESET channel select register ( 2 times 1 out of 16)                            |

| 0x110        | R/W | D32  | MUX_OUT channel select register (firmware 01 0B, 1 of 32, note 2)                |

|              |     |      |                                                                                  |

| 0x200        | R/W | D32  | Inhibit/count disable register                                                   |

| 0x204        | W   | D32  | Counter Clear register                                                           |

| 0x208        | R/W | D32  | Counter Overflow read and clear register                                         |

| 0x210        | R   | D32  | Channel 1/17 Bits 33-48                                                          |

| 0x214        | R/W | D32  | Veto external count inhibit register (firmware 01 09, note 2)                    |

| 0x218        | R/W | D32  | Test pulse mask register (firmware 01 0A, note 2)                                |

VME Multichannel Scaler SIS 3820

From base address (32 bits address)

Address offsets list for R//W functions

Offset: 0x10c

| - | Bit | Function                              |

|---|-----|---------------------------------------|

| _ | 31  | no function, read as 0                |

| _ | ••• |                                       |

|   | 20  | no function, read as 0                |

| = | 19  | bit 3 of PRESET channel select group2 |

|   | 18  |                                       |

| _ | 17  |                                       |

| _ | 16  | bit 0 of PRESET channel select group2 |

|   | 15  | no function, read as 0                |

|   |     |                                       |

|   | 4   | no function, read as 0                |

| _ | 3   | bit 3 of PRESET channel select group1 |

| _ | 2   |                                       |

| - | 1   |                                       |

| _ | 0   | bit 0 of PRESET channel select group1 |

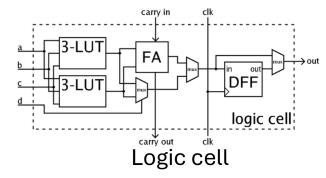

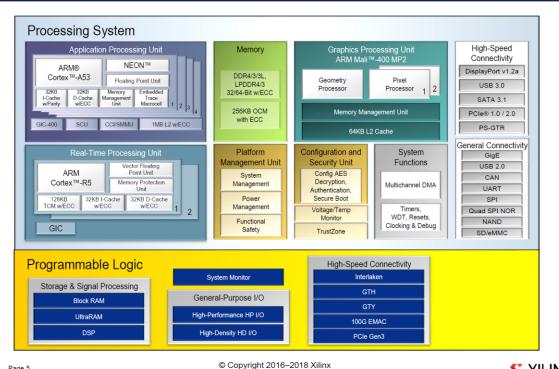

### Field Programmable Gate Array (FPGA)

Integrated circuit that can be configured for a specific purpose by a customer. It is a matrix of configurable logic blocks connected by programmable interconnects and therefore it is reprogrammable.

#### Zynq® UltraScale+™ MPSoCs: EG Block Diagram

### Zynq® UltraScale+™ MPSoCs: EG Devices

|                      | Device Name <sup>(1)</sup>                                                                            | ZU2EG                                                               | ZU3EG                                                            | ZU4EG | ZU5EG | ZU6EG    | ZU7EG   | ZU9EG     | ZU11EG | ZU15EG | ZU17EG | ZU19EG |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------|-------|-------|----------|---------|-----------|--------|--------|--------|--------|--|--|

| Application          | Processor Core                                                                                        | Quad-core ARM® Cortex™-A53 MPCore™ up to 1.5GHz                     |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Processor Unit       | Memory w/ECC                                                                                          |                                                                     | L1 Cache 32KB I / D per core, L2 Cache 1MB, on-chip Memory 256KB |       |       |          |         |           |        |        |        |        |  |  |

| Real-Time            | Processor Core                                                                                        | Dual-core ARM Cortex-R5 MPCore™ up to 600MHz                        |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Processor Unit       | Memory w/ECC                                                                                          | L1 Cache 32KB I / D per core, Tightly Coupled Memory 128KB per core |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Graphic & Video      | Graphics Processing Unit                                                                              | Mali™-400 MP2 up to 667MHz                                          |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Acceleration         | Memory                                                                                                | L2 Cache 64KB                                                       |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Furtament Management | Dynamic Memory Interface x32/x64: DDR4, LPDDR4, DDR3, DDR3L, LPDDR3 with ECC                          |                                                                     |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| External Memory      | Static Memory Interfaces                                                                              | NAND, 2x Quad-SPI                                                   |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Connectivity         | High-Speed Connectivity PCIe® Gen2 x4, 2x USB3.0, SATA 3.1, DisplayPort, 4x Tri-mode Gigabit Ethernet |                                                                     |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Connectivity         | General Connectivity 2xUSB 2.0, 2x SD/SDIO, 2x UART, 2x CAN 2.0B, 2x I2C, 2x SPI, 4x 32b GPIO         |                                                                     |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

|                      | Power Management Full / Low / PL / Battery Power Domains                                              |                                                                     |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Integrated Block     | Security                                                                                              | RSA, AES, and SHA                                                   |                                                                  |       |       |          |         |           |        |        |        |        |  |  |

| Functionality        | AMS - System Monitor                                                                                  |                                                                     | 10-bit, 1MSPS – Temperature and Voltage Monitor                  |       |       |          |         |           |        |        |        |        |  |  |

| to PL Interface      |                                                                                                       |                                                                     |                                                                  |       |       | 12 x 32/ | 64/128b | AXI Ports | ;      |        |        |        |  |  |

| Programmable         | System Logic Cells (K)                                                                                | 103                                                                 | 154                                                              | 192   | 256   | 469      | 504     | 600       | 653    | 747    | 926    | 1,143  |  |  |

| Functionality        | CLB Flip-Flops (K)                                                                                    | 94                                                                  | 141                                                              | 176   | 234   | 429      | 461     | 548       | 597    | 682    | 847    | 1,045  |  |  |

| Functionality        | CLB LUTs (K)                                                                                          | 47                                                                  | 71                                                               | 88    | 117   | 215      | 230     | 274       | 299    | 341    | 423    | 523    |  |  |

|                      | Max. Distributed RAM (Mb)                                                                             | 1.2                                                                 | 1.8                                                              | 2.6   | 3.5   | 6.9      | 6.2     | 8.8       | 9.1    | 11.3   | 8.0    | 9.8    |  |  |

| Memory               | Total Block RAM (Mb)                                                                                  | 5.3                                                                 | 7.6                                                              | 4.5   | 5.1   | 25.1     | 11.0    | 32.1      | 21.1   | 26.2   | 28.0   | 34.6   |  |  |

| Clocking             | UltraRAM (Mb)                                                                                         | -                                                                   | -                                                                | 13.5  | 18.0  | -        | 27.0    | -         | 22.5   | 31.5   | 28.7   | 36.0   |  |  |

| Clocking             | Clock Management Tiles (CMTs)                                                                         | 3                                                                   | 3                                                                | 4     | 4     | 4        | 8       | 4         | 8      | 4      | 11     | 11     |  |  |

|                      | DSP Slices                                                                                            | 240                                                                 | 360                                                              | 728   | 1,248 | 1,973    | 1,728   | 2,520     | 2,928  | 3,528  | 1,590  | 1,968  |  |  |

|                      | PCI Express® Gen 3x16                                                                                 | -                                                                   | -                                                                | 2     | 2     | -        | 2       | -         | 4      | -      | 4      | 5      |  |  |

| Integrated IP        | 150G Interlaken                                                                                       | -                                                                   | -                                                                | -     | -     | -        | -       | -         | 1      | -      | 2      | 4      |  |  |

| Integrated IP        | 100G Ethernet MAC/PCS w/RS-FEC                                                                        | -                                                                   | -                                                                | -     | -     | -        | -       | -         | 2      | -      | 2      | 4      |  |  |

|                      | AMS - System Monitor                                                                                  | 1                                                                   | 1                                                                | 1     | 1     | 1        | 1       | 1         | 1      | 1      | 1      | 1      |  |  |

| Transceivers         | GTH 16.3Gb/s Transceivers                                                                             | -                                                                   | -                                                                | 16    | 16    | 24       | 24      | 24        | 32     | 24     | 44     | 44     |  |  |

|                      | GTY 32.75Gb/s Transceivers                                                                            | -                                                                   | 16 -                                                             |       |       |          |         | -         | 28     | 28     |        |        |  |  |

| Speed Grades         | Extended <sup>(2)</sup>                                                                               | -1 -2                                                               | -1 -2 -2L -1 -2 -2L -3 -1 -2 -2L -3                              |       |       |          |         |           |        |        |        |        |  |  |

| - Francis            | Industrial                                                                                            |                                                                     | -1 -1L -2                                                        |       |       |          |         |           |        |        |        |        |  |  |

For full part number details, see the Ordering Information section in <u>DS891</u>, Zynq UltraScale+ MPSoC Overview 2.-2LE (Ti = 0°C to 110°C). For more details, see the Ordering Information section in DS891, Zyng UltraScale+ MPSoC Overview © Copyright 2016-2018 Xilinx

**E** XILINX

**E** XILINX

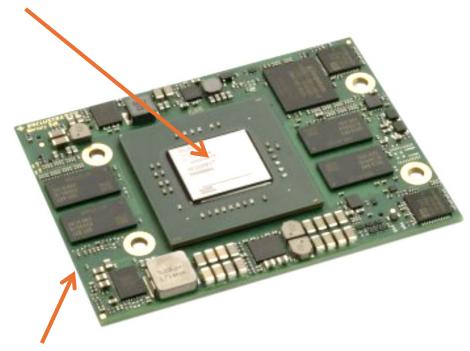

### FPGA, SoC, SoM

**SoC chip (System on a Chip)** is an integrated circuit that consolidates all or most of the essential electronic components of a device onto a single chip

A **system on a module** (**SoM**) is a board-level circuit that integrates a system function in a single module. It may integrate digital and analog functions on a single board.

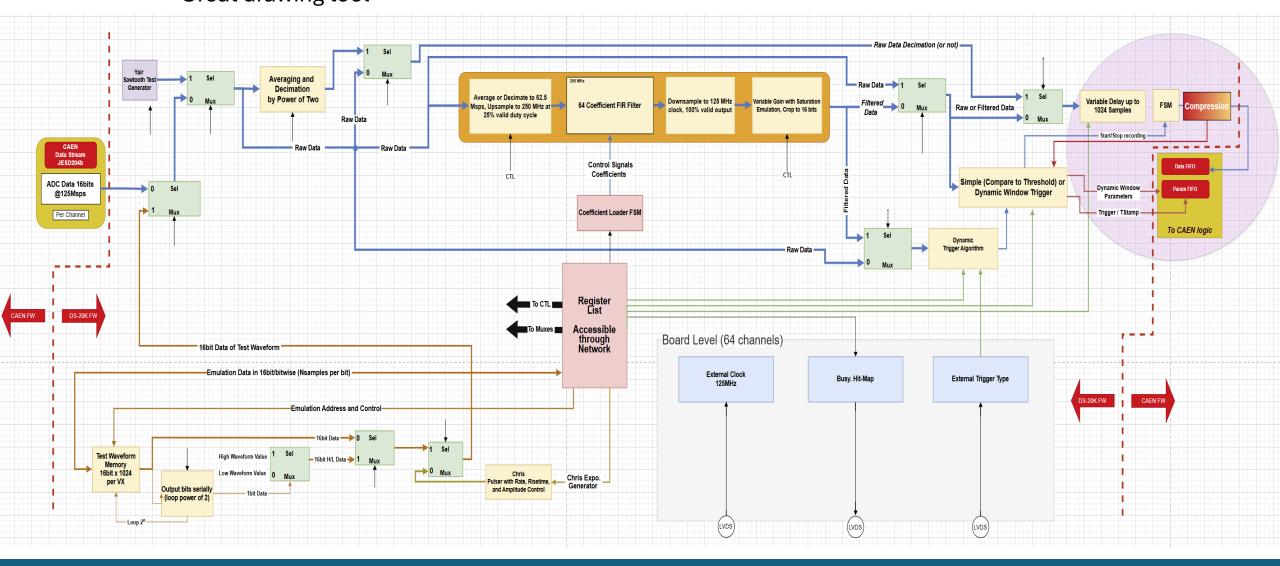

### **Data Processing in FPGA**

https://www.drawio.com/ Great drawing tool

### Languages for Data Processing in FPGA

```

152

always@(posedge int_rst, posedge clk_wr) begin

153

if(int_rst) begin

154

r_trigger

<= 1'b0;

Hardware Description Languages

155

<= {SZ_DELAY{1'b0}};

delay_cnt

(HDLs) VHDL and Verilog

156

trig_accepted_cnt

<= {32{1'b0}}:

... but now you can find:

157

trig_dropped_cnt

<= {32{1'b0}};

158

ts_start

<= {SZ_TIME{1'b0}};

159

<= {SZ_TIME{1'b0}};

ts_triq

High-Level Languages: C, C++,

160

end else begin

OpenCL, Python (via MyHDL, Migen,

161

ts_start

<= ts_start;

PyRTL, etc.), Scala (Chisel), Haskell

162

ts_trig

<= ts_trig;

(Clash), MATLAB

163

trig_accepted_cnt

<= trig_accepted_cnt;

164

trig_dropped_cnt

<= trig_dropped_cnt;

165

<= 1'b0:

r_trigger

166

// Don't touch timestamp on run start, a packet may still be being finished assembling

167

if(run_os) begin

168

<= 1'b0:

r_trigger

169

<= {SZ_DELAY{1'b0}};

delay_cnt

170

trig_accepted_cnt

<= {32{1'b0}};

171

trig_dropped_cnt

<= {32{1'b0}};

172

<= {SZ_TIME{1'b0}};

ts_start

173

<= {SZ_TIME{1'b0}};

ts_triq

174

end else begin

if(triq_in && run) begin

175

176

if(!triggered) begin

```

# Data Acquisition - Computers, Chips (CPU, GPU, AI, ...)

- Motorola 6800 microprocessor (introduced in 1974)

- Die size 16.5 mm<sup>2</sup>

- Transistor count **4,100 transistors**.

- 250 transistors per mm<sup>2</sup>

- Clock 1 MHz, 8-bit data bus, 16-bit address bus

- Intel Core i9-13900k (2022)

- Die area 257mm<sup>2</sup>

- Transistor count 20 billions (20x10<sup>9)</sup>

- 75 millions transistors per mm<sup>2</sup>

- AMD Ryzen 7 7700x (2022)

- The Core Complex Die (CCD) + I/O Die (IOD)

- 6.5 billion transistors for **70** mm<sup>2</sup> + 3.4 billion transistors for 122 mm<sup>2</sup>.

- 4.5-5.4 GHz, 64-bit data bus, 52-bit address bus

- 50 millions transistors per mm<sup>2</sup>

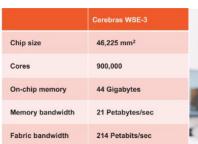

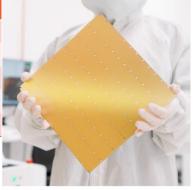

- Cerebras WSE-3 (Wafer Scale Engine) FULL WAFER!

- Die size 220mm x 220 mm (46225 mm<sup>2)</sup>

- 900K cores, 4 trillion transistors  $(4x10^{12})$  on a single chip.

- 86 millions transistors per mm<sup>2</sup>

DarkSide-20K 8" wafer SiPM size: 8mm x 12mm area: 96 mm<sup>2</sup>

Cerebras WSE-3 4 Trillion Transistors 46,225 mm<sup>2</sup> Silicon ~22cmx22cm

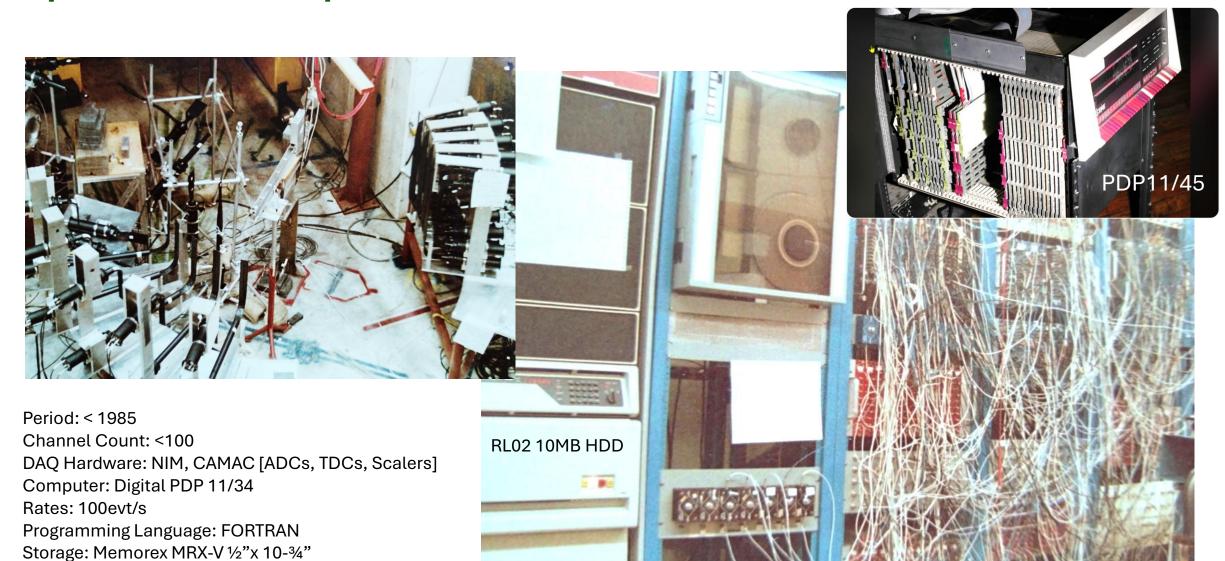

# Electronics instrumentation Where all this electronics plugs in?

### **Electronics Bus standards**

#### NIM (1968): Nuclear Instrument Module

Still in use for standard logic for workbench tests

CAMAC (1972): Computer Automated Measurement and Control, use TTL parallel bus

• Still in use in older system (Triumf Cyclotron Control).

#### VME (1981): Vesa Module Europcard

• Very much in use, as VME modules are still commercially available (parallel backplane bus).

FastBus (1984): To replace CAMAC with ECL parallel bus

Already dead

#### VXI (2004): VME eXtensions for Instrumentation

Was an extension to fit a transition...

#### VXS (2006): VMEBus Switched Serial

• In use due to its serial bus backplane and slot configuration (Full mesh, Dual star). Redundant

### ATCA (uTCA) (2002): Advanced Telecommunications Computing Architecture

- PCI Industrial Computer Manufacturers Group (PICMG)

- New trend for Physics applications, combines VXS, self-managed crate, Single -48V, fully differential connections.

### NIM (1968): Nuclear Instrument Module (still in use)

Basic Analog elements: Delay Splitter Discriminator Attenuator Pre-Amplifier

Basic Logic

elements

Inverter AND, OR

Latch, Timer, Scaler

For

Power

+/- 6V

+/- 12V

+/-24V

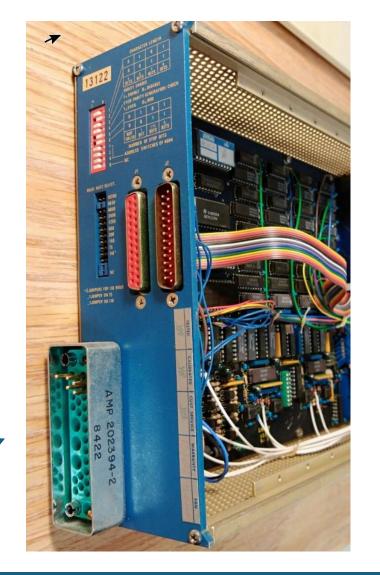

### **CAMAC (1972): Computer Automated Measurement and Control (found in older working systems)**

Analog to Digital converter Programmable... Delays, Discriminators, Attenuators, I/Os, etc... ADC, TDC, Scalers...

#### For Power:

+/- 6V, +/- 12V, +/-24V AC117V

#### For Communication:

Slot Address N5 Module Add A4 Function bus F5 Data bus R24/W24

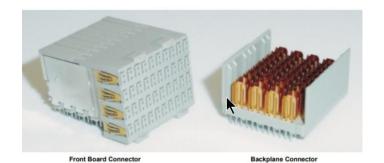

### VME (1981): Vesa Module Europeard (currently used in most physics labs)

#### FPGAs for Logic

Analog to Digital converter Programmable... Delays, Discriminators, Attenuators, I/Os, etc... ADC, TDC, Scalers...

For Power: +/- 5V, +/- 12V, +3.3V

For Communication Address Bus: A32

Data Bus: D32

Control bus: IRQ, AM5, AS, DS0/1, +...

**VMEIO - 2009**

CAEN V1720 8ch, 12bits@250Msps

#### ATCA (uTCA): Advanced Telecommunications Computing Architecture (New large system choice)

**Five nines** means "99.999%", High availability of services system (five-9 / max down time of 5.26 minutes per year.)

#### **Custom Electronics boards**

Alpha-g (custom card)

288 cathode strips readout board

4 AFTER ASICs, 1 Cyclone-V FPGA

DarkSide-20K (VME board)

Clock distribution board16 x 2.5Gbps links

1 SoM Enclustra XU8

### **Data Storage**

- Tapes not used at the DAQ level anymore (Exabyte 8mm)

- Hard Disk Drive used for DAQ due to high storage capacity

- Solid-State Drive used for OS and user applications

- Tape drive robots in use for data backup and long-term data retention (LTO tape)

- Cloud storage (private) in use for data processing

CERN Cray X-MP/48 (1988) 64-bit@80MHz, RAM 8.39MB

# Data Acquisition – A few more points!

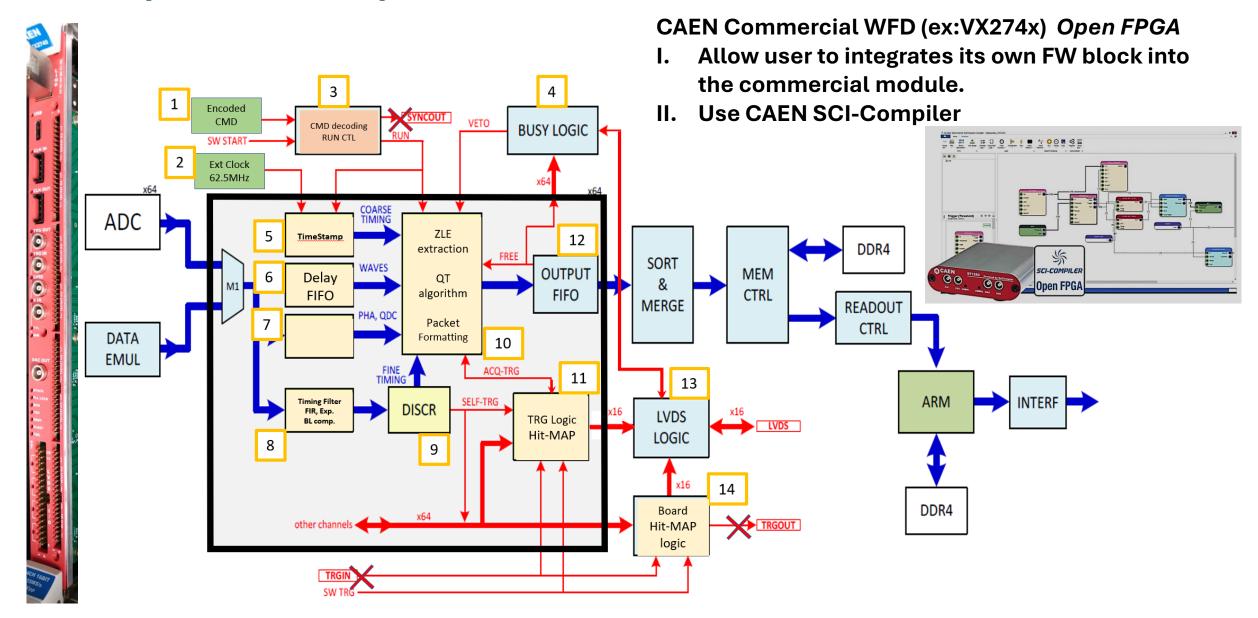

- Today's Acquisition module architecture

- Time reference, Clock, Clock distribution

- Trigger or Triggerless

# Data Acquisition - Acquisition module architecture

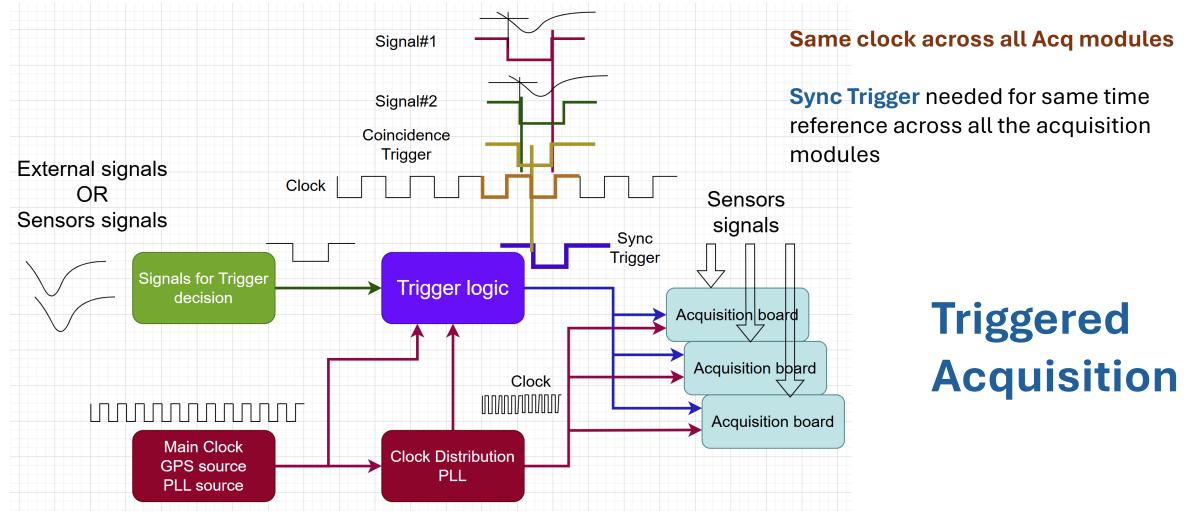

# Data Acquisition - Time reference, Clock, Clock distribution

Main clock GPS (1pps, 10MHz)

Clock distribution (10MHz to sampling Freq.)

# Data Acquisition - Trigger or Triggerless?

In case of large number of channels to build a trigger or too many logic required to make a coincidence trigger or coincidence timing not acceptable for the acquisition modules.

### Triggerless or self-trigger

- Each channel operates with its own trigger method.

- Individual acquisitions are self-triggered by the input signal (requires a threshold).

- Capture and read out every "hit", "pulse" (data rate can reach multiple GB/s).

- Events are reconstructed on a server farm, or a "Level 2 trigger" filters data to determine what to store (reducing the rate to a few MB/s).

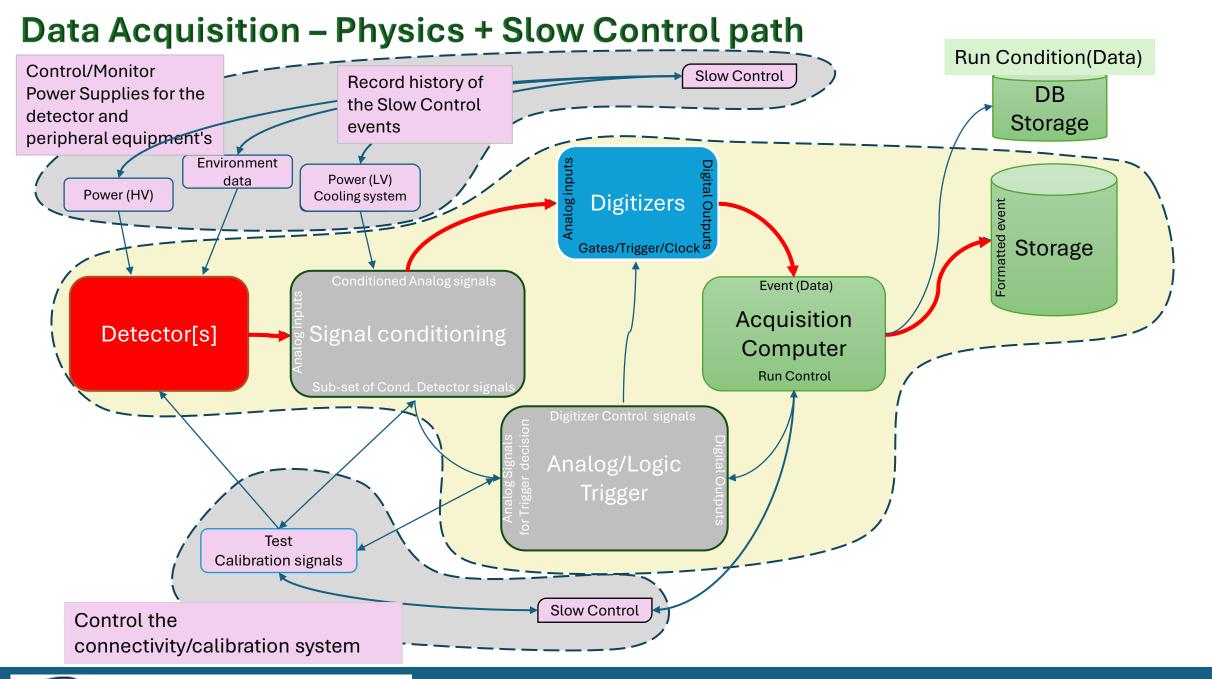

### Couple of more DAQ things to consider...

- "Slow Control" is part of the Data Acquisition System

- Environment parameters, equipment monitoring, calibration system have to be included.

• As the DAQ-SC manage the whole electronic chain, consider to separate the power for slow control from the main acquisition data path. Maintain control of the equipment status (under UPS).

- Don't underestimate thermal effect on the electronics equipment

- Heat dissipation, necessity of a cooling system (air, water)

- High current through contacts (power connectors current rating!)

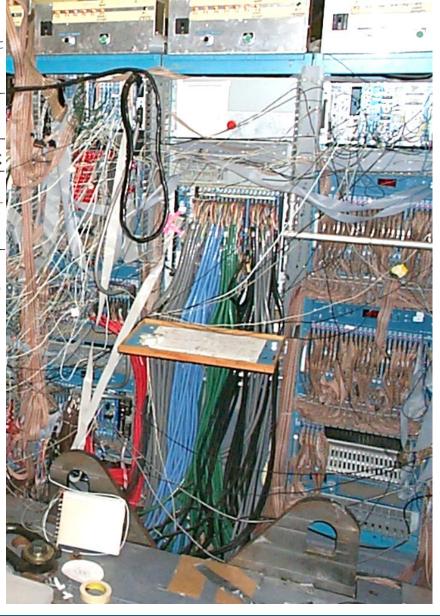

Cable path organization facilitate channel recognition, module extraction (cable tray, please use GOOD label material!)

### Data Acquisition - Software development tips

- Write code that is readable!

"Always code as if the guy who ends up maintaining your code will be a violent psychopath who knows where you live."

- Give your functions sensible names

- Document the why not the what!

Test any code you write!

Just because your code compiles doesn't mean it's correct...

Strongly consider testing frameworks:

unittest module for Python

Catch2/GoogleTest for C++

May want to write a dummy/mock device so you can run tests without talking to real hardware devices

- ChatGPT / CoPilot / Claude / Cursor / Chat.PublicAI can generate code

- May generate working code quickly

- For smaller tasks, okay

- E.g. how to add a label to a plot in matplotlib / ROOT

- Harder to maintain or to explain

- •

Ben Smith (Triumf DAQ group)

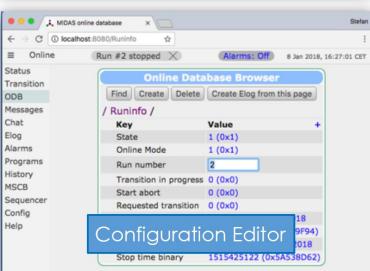

### Data Acquisition - Program Coding (Midas)

### **Function Templates**

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* Callback routines for system transitions These routines are called whenever a system transition like start/ stop of a run occurs. The routines are called on the following occasions: frontend init: When the frontend program is started. This routine should initialize the hardware. frontend exit: When the frontend program is shut down. Can be used to release any locked resources like memory, communications ports etc. begin of run: When a new run is started. Clear scalers, open run gates, etc. end of run: Called on a request to stop a run. Can send end-of-run event and close run gates. When a run is paused. Should disable trigger events. pause run: When a run is resumed. Should enable trigger events. resume run:

### **Programming Languages**

Assembler

Basic

Modula-2

Pascal

COBOL

**FORTRAN**

Java

Erlang

Tcl

Go

C

C++

Rust

**Python**

R

**JavaScript**

Grafana

• • •

# Data Acquisition - Program Code structure (Midas)

```

EQUIPMENT equipment[] = {

Equipment

/* equipment name */

"Object" dealing with the acquisition of a

{"Trigger",

/* event ID, trigger mask */

/* event buffer */

{1, 0,

"SYSTEM",

EQ_POLLED,

block of data composing the final event

/* equipment type */

/* event source */

/* format */

"MIDAS",

/* enabled */

TRUE,

/* read only when running */

RO RUNNING |

/* and update ODB */

RO ODB,

100,

/* poll for 100ms */

Readout Function

/* stop run after this event limit */

/* number of sub events */

/* don't log history */

"", "", "",},

/* create structured ADC2 bank */

read trigger event,

/* readout routine */-

bk create(pevent, "ADC2", TID DWORD, &pdata);

/* Read Event */

/* equipment name */

/* event ID, trigger mask */

"SYSTEM", /* event buffer */

{"Periodic",

v792 EventRead (myvme, VADC2 BASE, pdata, &nentry);

{2, 0,

pdata += nentry;

/* equipment type */

EQ PERIODIC,

bk close (pevent, pdata);

/* event source */

"MIDAS",

/* format */

TRUE,

/* enabled */

RO RUNNING | RO TRANSITIONS | /* read when running and on transitions */

RO_ODB, /* and update ODB */

1000, /* read every sec */

0, /* stop run after this event limit */

0, /* number of sub events */

Specific software driver to acquire

/* log history */

TRUE,

"", "", "", 1,

the data from the hardware module.

read periodic event,

/* readout routine */

VME, Ethernet, GPIB, RS-232

I2C, SPI, CANBus, etc...

```

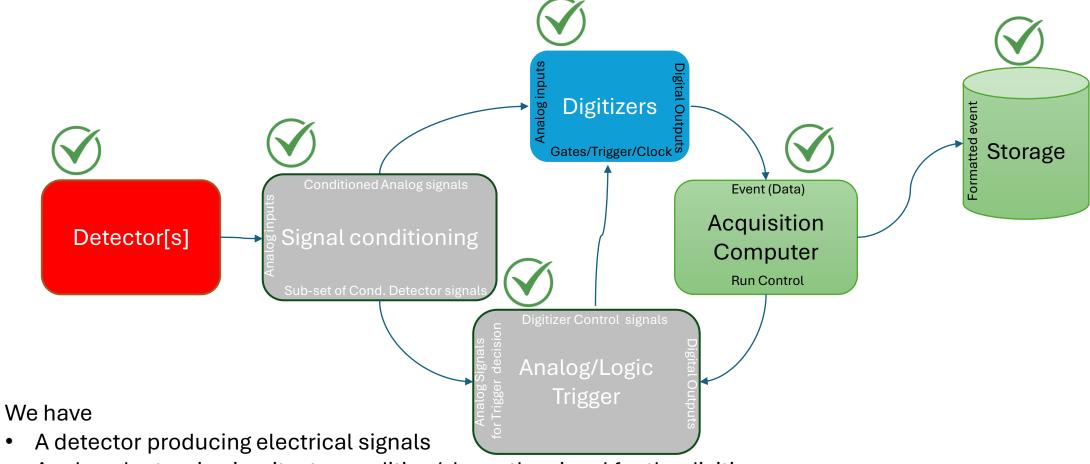

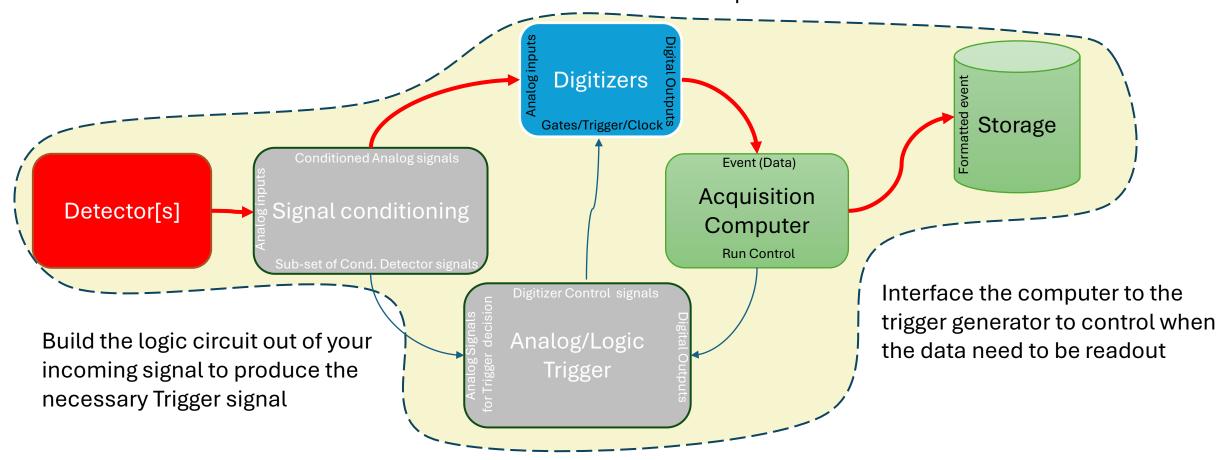

### **Data Acquisition – Data path**

- Analog electronic circuitry to condition/shape the signal for the digitizers

- Trigger circuit for event selection

- Digitizers for Amplitude, Charge, Time conversion, etc...

### Data Acquisition – Physics Data path

Define the type of "event" that you need to record. "event" is a collection of data tagged to a specific run condition

# Experiment - examples - $\pi$ -scat

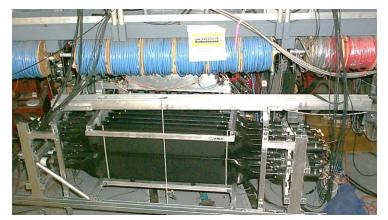

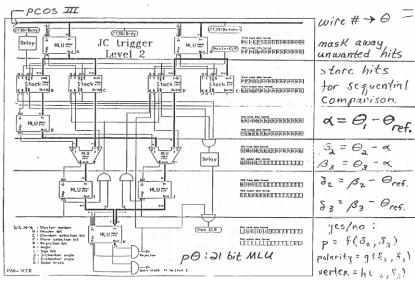

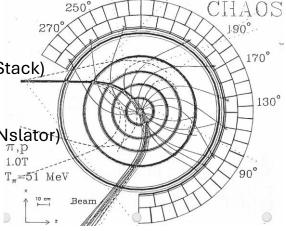

### **Experiment - examples - CHAOS**

Delay Lines (~20m) for ~2000 channels

Period: 1990 - 2000 Channel Count: ~2500

DAQ Hardware: NIM, CAMAC, VME, FastBus

L2-Trigger FPGA Precursor in ECL-logic (CAMAC: ALU, MLU, Stack)

Computer: Digital µVax-3400

Rates: few hundred events per second

Programming Language: FORTRAN (IBM 1957, FORmula TRANslator)

Storage: Sony QG112M 2.5/5GB 8mm D8 Data Cartridge

DLTape IV 80GB (compressed)

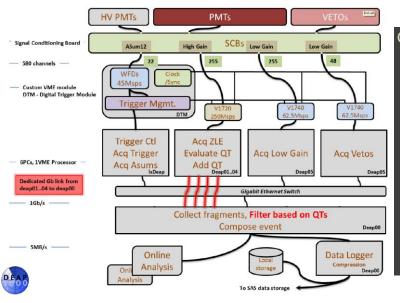

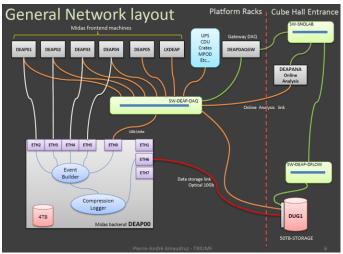

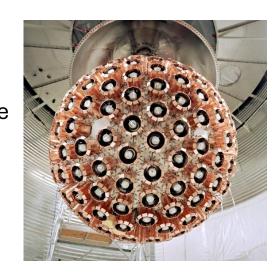

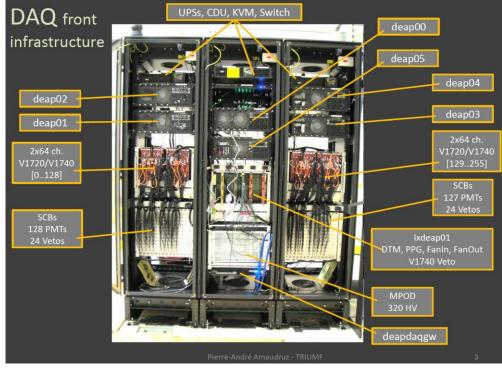

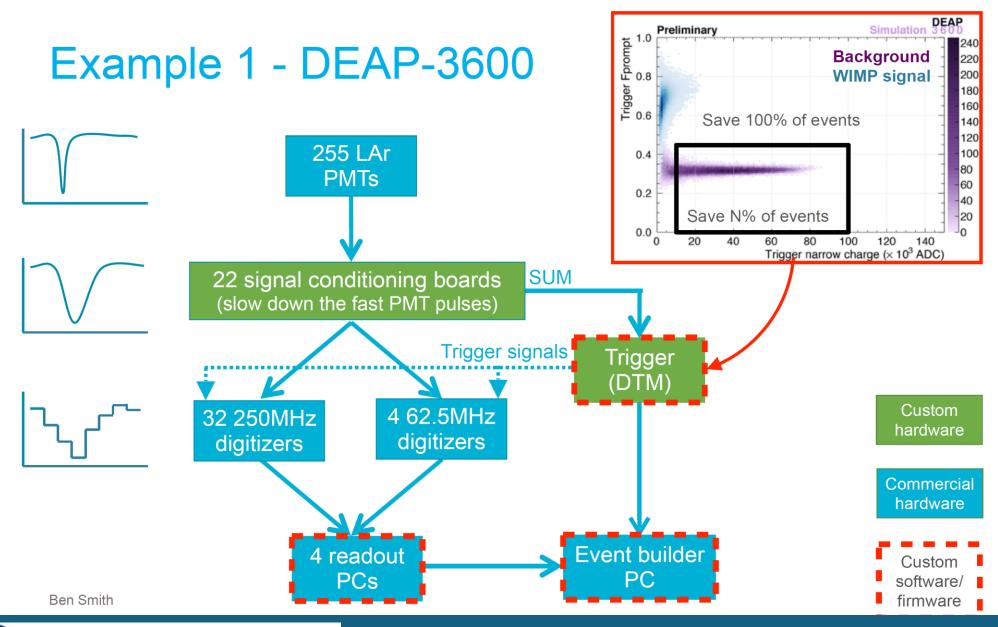

### **Experiment - examples - DEAP**

Period: 2010 -

Channel Count: ~600

DAQ Hardware: VME, PCIe Optical interface

L1 Trigger FPGA-based

Computer: PCs

Rates: ~3KEvt/s, ~12MB/s

Programming Language: C, C++, Web tools

Storage: Local HDD, Cloud

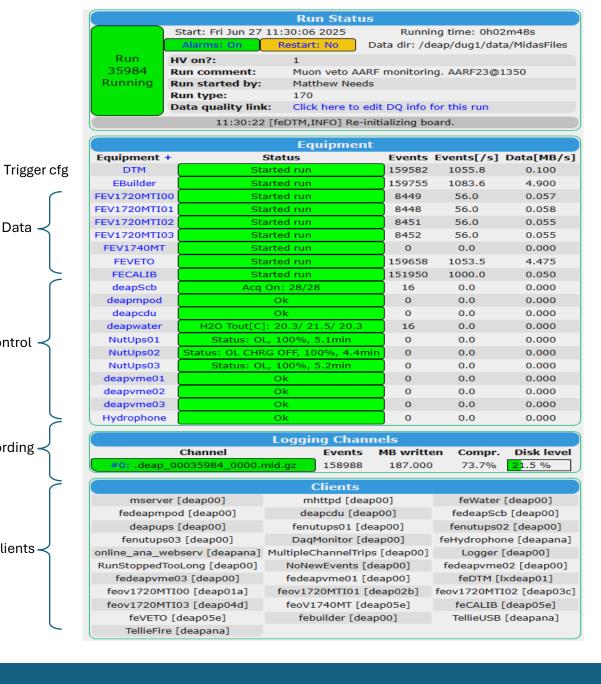

### **Experiment - examples - DEAP**

### **Experiment - examples - DEAP**

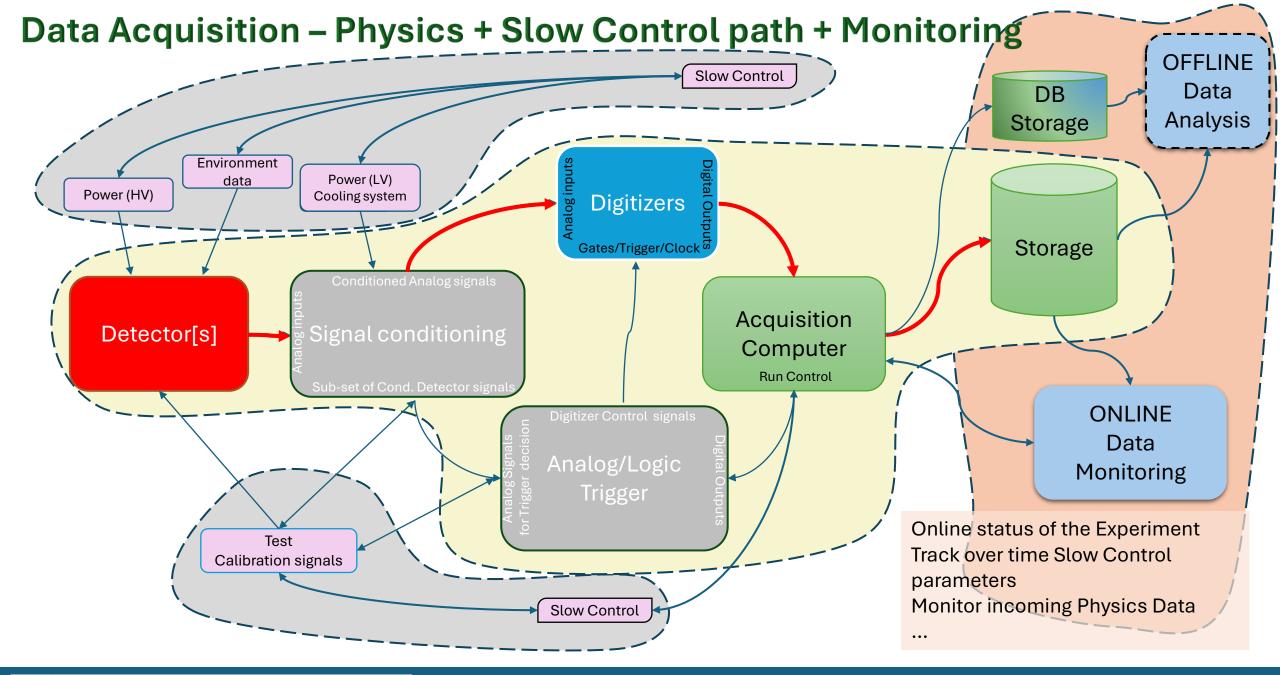

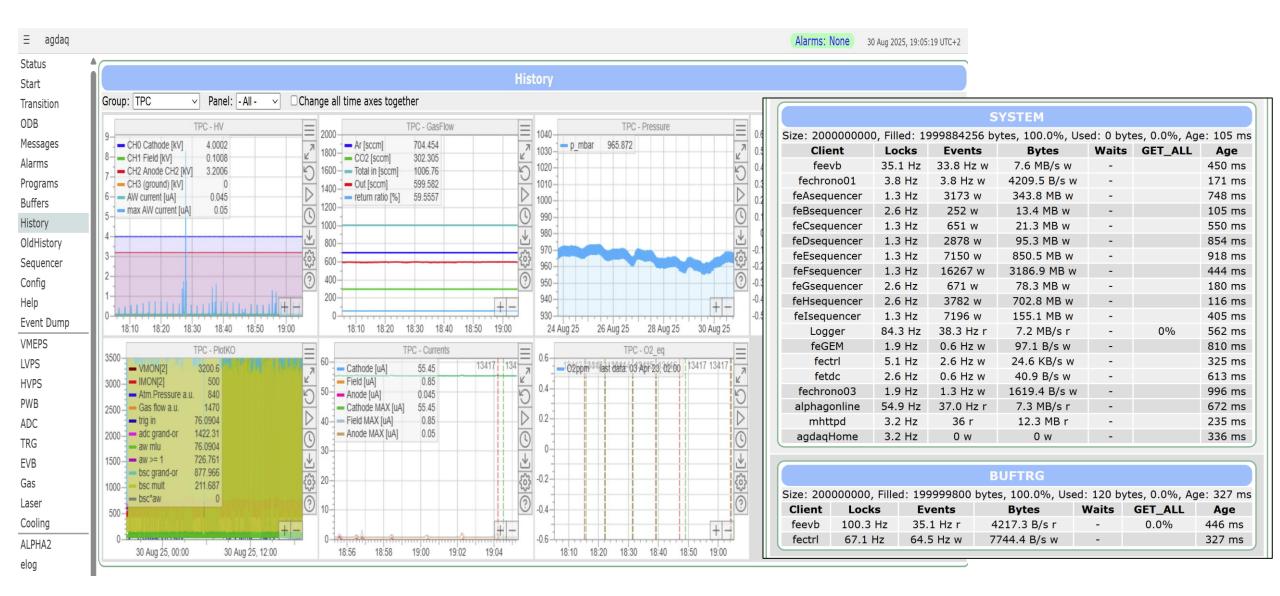

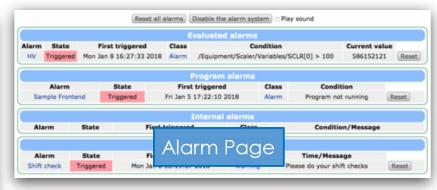

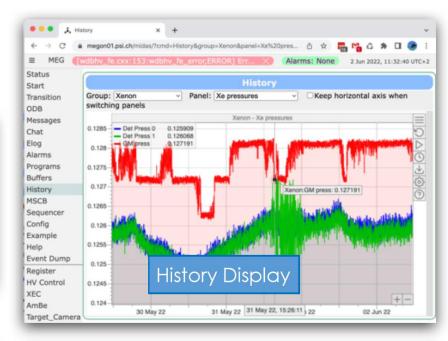

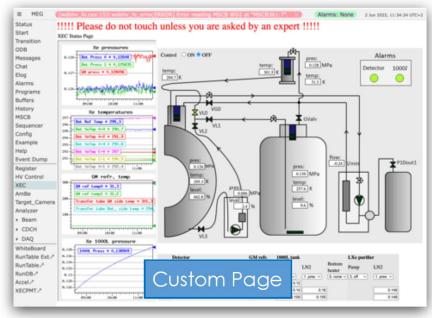

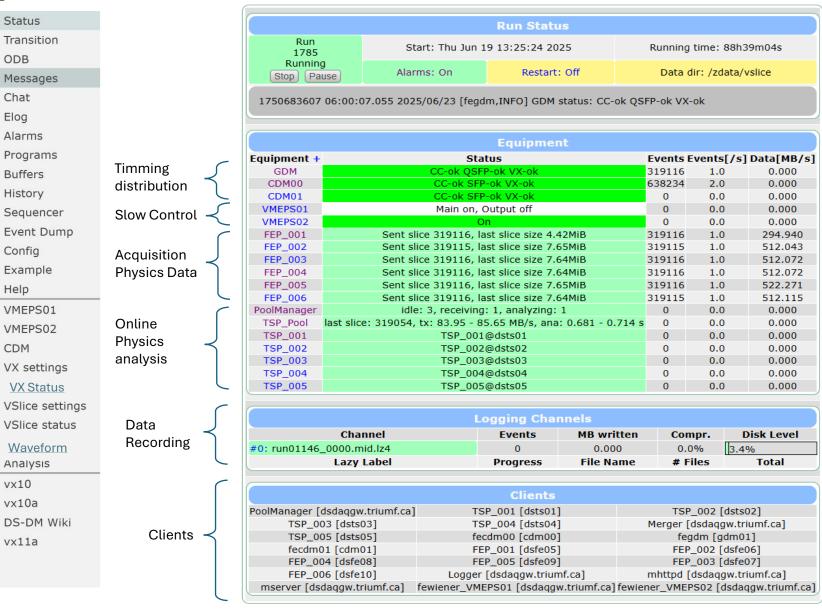

#### What features a DAQ system must provide?

**Run Control**

Define the data acquisition sequence – Run concept (cycle) –

Run: Data set collected with a defined experimental condition

Record the selected Data to storage device

Multiple storage media, event type, etc. (Logger)

**Hardware configuration**

Based on pre-selected configuration

Online status of the Experiment

Real time messages with permanent record (log)

Track over time experimental condition parameters

Chart plot of any experimental variable (History)

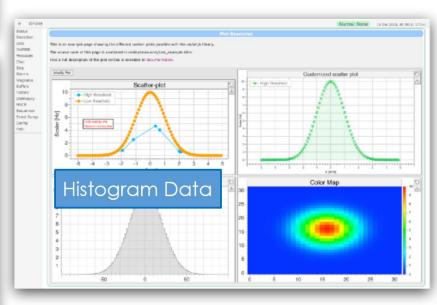

**Monitor incoming Physics Data**

Online Data Analysis mechanism with data display (Rootana)

- **Custom User Parameters/Data display (Custom Web page, script)**

- **Custom alarm and custom action based on Alarm condition (Alarms)**

- And more...

Physics Data

Slow Control

Data Recording

Clients -

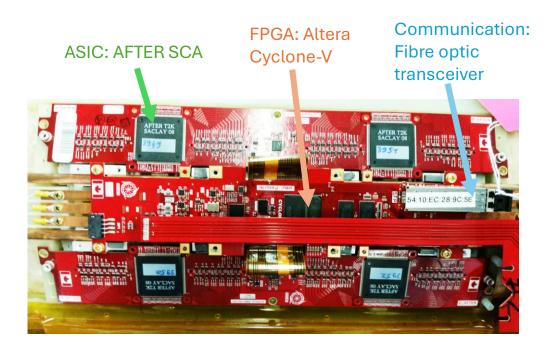

# Experiment - examples - Alpha-g

Period: 2016 -

Channel Count: ~19'000! ... (18'000 of SCAs)

DAQ Hardware: VME (for power only), Ethernet Optical Links

Custom Build Hardware with FPGAs: WFDs, TDCs, Logic

ASICs, SCA AFTER chip (Saclay France)

Computer: PCs

Rates: ~1KEvt/s, ~200MB/s

Programming Language: C, C++, Web tools

Storage: Local HDD, Cloud

Large portion of the frontend electronics including the waveform digitizers reside on the detector (256 ASICs)

# Experiment - examples - Alpha-g

### **Experiment - examples - MEG**

Ben Smith

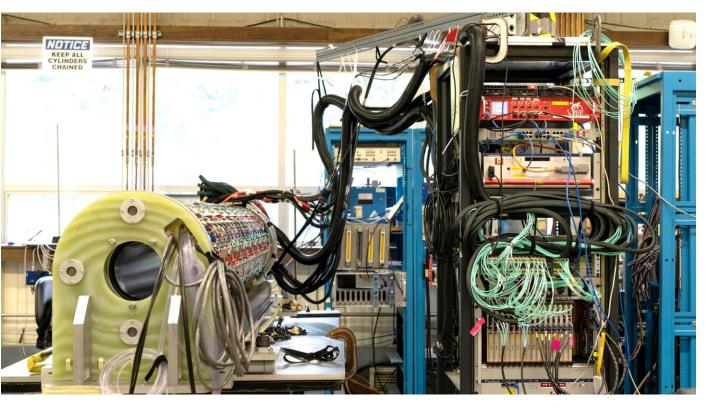

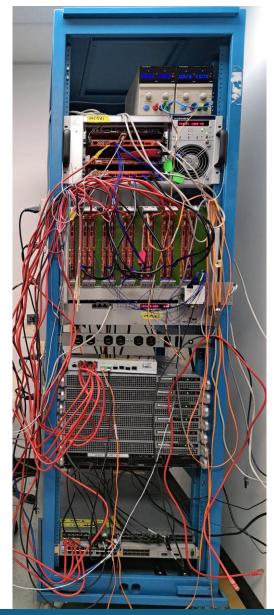

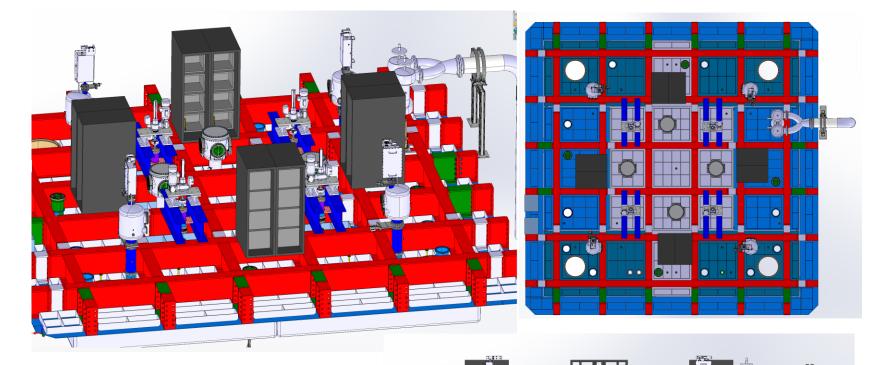

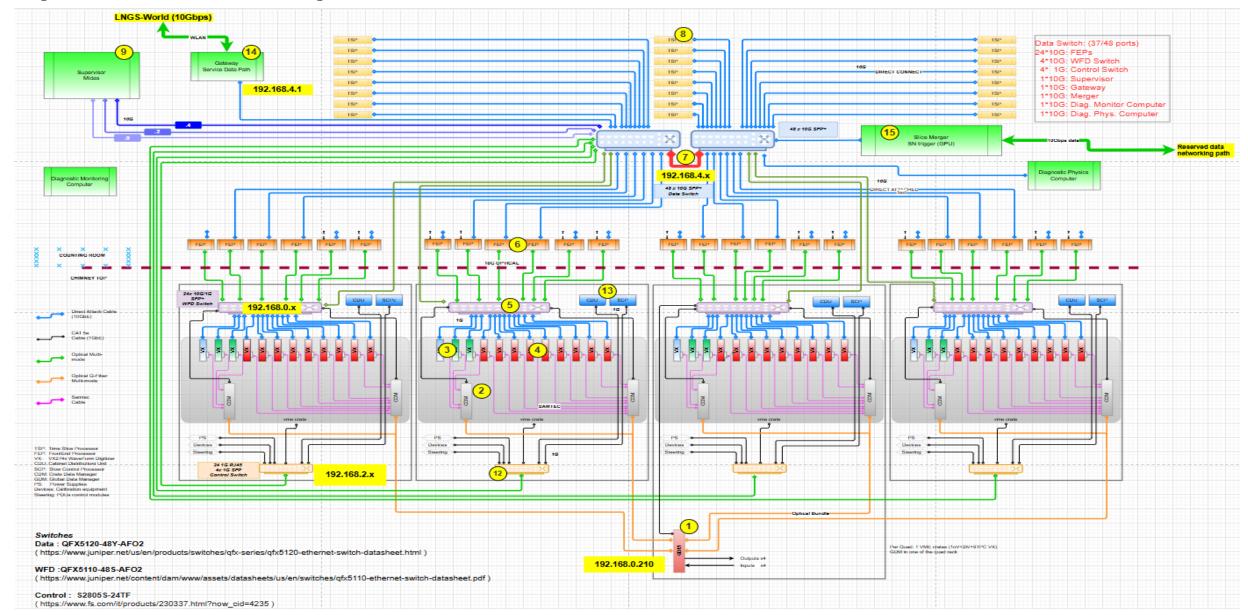

# **Experiment - examples - DarkSide-20K**

DarkSide-20K Rooftop with 4 double DAQ racks #1 DAQ + Network + Slow Control #2 sensors (PDUs) Power+Control

DarkSide-20K

"Quadrant" DAQ rack (12 WFD, 6 PCs, 3 Network switches)

# **Experiment - examples - DarkSide-20K**

# **Experiment - examples - DarkSide-20K**

DarkSide-20K Quadrant

Run Status & Control

### There are other DAQ software packages?

- · Most of the Physics Labs have their own DAQ system and experts.

- Labview: works well for many small setups

- Labview drivers provided for many commercial devices.

- Getting generic device drivers for linux can be tricky.

- ORCA: developed by group at University of North Carolina

- Runs on MacOS

- Experiments: KATRIN, MAJORANA, SNO+

- Artdaq: developed by FNAL

- Based on art offline analysis framework (originally from CMS)

- Experiments: LARiAT, Darkside-50, Mu2E

- Midas-UK: Multi Instance Data Acquisition System (Rutherford STFC)

- CODA: Jefferson Laboratory (formerly CEBAF Online Data Acquisition)

- And many more...

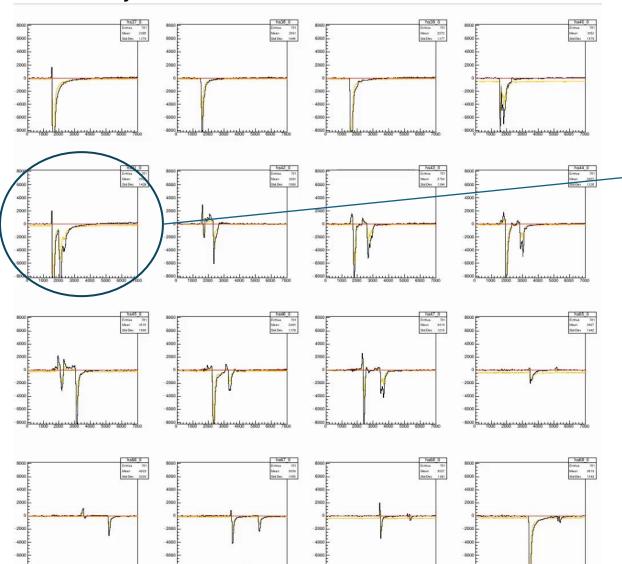

#### Data Analysis - Deconvolution

- Match single avalanche response to signal

- Subtract induction responses from neighbors

<mark>Yellow</mark> : Original signal

: Signal evolution during the deconvolution

Black: Residual signal

#### References...

Gas Detector Effects: Electric field, Diffusion, Lorentz effect

Detectors types: MWPC, TGC, RPC, DCs, Gas, µMega, GEM, Silicon detectors

Fabio Sauli (CERN)

Gaseous Radiation Detectors Fundamental and Applications (2014)

Y. Assran, Archana Sharma

<u>Transport Properties of operational gas mixtures used at LHC</u>

Archana Sharma

Sciencedirect\_articles\_22Oct2015\_04-43-06.230 (collection of NIM-A papers)

...

https://www.analog.com/en/analog-dialogue/articles/understanding-and-eliminating-1-f-noise.html https://www.electronics-tutorial.net/analog-integrated-circuits/data-converters/dual-slope-type-adc/https://www.electronicdesign.com/adc/what-s-difference-between-sar-and-delta-sigma-adcs https://www.analog.com/en/design-center/interactive-design-tools/sigma-delta-adc-tutorial.html Pipelined ADC: https://www.maximintegrated.com/en/app-notes/index.mvp/id/1023

### **Data Acquisition**

# Additional DAQ information

- MIDAS DAQ package

- DAQ Midas Workshop 2025 22–23 Sept 2025

- ISOTDAQ School, CERN

- IEEE: Institute of Electrical and Electronics Engineers

- NPSS: <u>Nuclear & Plasma Sciences Society</u> *IEEE NPSS International Schools*

- CANPS: Computer Applications in Nuclear and Plasma Sciences

25<sup>th</sup> Real Time conference 2026, Elba Italy 25–29 May 2026

### **CANPS Real Time Conferences**

24th IEEE Real Time Conference - ICISE, Quy Nhon, Vietnam

22–26 Apr 2024 Asia/Ho Chi Minh timezone

Enter your search term

\*\*\* See you in Elba, Italy in May 2026 \*\*\*

Overview

Important Dates

CONFERENCE

Timetable

Request Certificate of Attendance

Timetable - List style

Timetable - Week overview

Pre-Conference Program

Scientific Program

Women in Engineering (WIE) Event

Publications

CANPS Award

Student Paper Awards

Local Poster Printing

#### 24th IEEE Real Time Conference

ICISE, Quy Nhon, Vietnam

April 22-26, 2024

A big thank you to all participants for your contributions to a successfull conference. We look forward to seeing everyone again in Elba, Italy (May 25-29, 2026)

### Overview Scientific Program Important Dates

Call for Abstracts

Pre-Conference Program

Industrial Exihibition

Travel information

Accomodation

Visa Information

rt2026@lists.pi.infn.it

Past Real Time

Organizers and

Conferences

Committees

Grants

Front-End Electronics, Fast Digitizers, Fast Transfer Links & Networks (FEnd-FastDig-FastTx)

Hardware specific such as Ultra-fast WFDs, ADCs, TDCs, SCAs in the GHz range and their applications

Data Acquisition and Trigger Architectures (DAQ-TR)

DAQ system architectures as well as conceptual design for future applications.

Real Time Diagnostics, Digital Twin, Control, Monitoring, Safety and Security (CTL-DIA-SAF-SECU)

Design and implementation from small to large scale systems.

Al, Machine Learning, Real Time Simulation, Intelligent Signal Processing (SIM-SigProc-ML-Al)

System architectures dealing with real-time data processing. Machine Learning and Al Acquisition specific. Methods, algorithms, implementation.

Emerging Technologies, New Standards, Feedback on Experience (EMER-STD-EXP)

Hardware standards, software, tools and techniques. Discussion on development or implementation of systems with a focus on the unexpected problems and lessons learned along the way.

Industry and Industry collaboration (INDUSTRY)

Industry product, collaborative work with the physics community

### NPSS is ...

#### **Nuclear & Plasma Sciences Society**

- The Technical Society that covers

- Fusion

- Nuclear Medical and Imaging Sciences

- Particle Accelerator Science and Technology

- Pulsed Power Systems

- Radiation Effects

- Radiation Instrumentation

- Plasma Sciences and Applications

- Standard for Nuclear Instruments and Detectors

- Computer Applications in Nuclear and Plasma Science

Have fun during the hands-on lab projects!

# Enough for today!

**END**

## IEEE is ...

#### **Institute of Electrical and Electronics Engineers**

- The largest technical/scientific professional organization

- The most prolific technical publisher

- International with activities in all regions of the world

- Organizes the greatest number of technical meetings and has the highest aggregate attendance

- The professional organization with the broadest technical scope with 38 Technical Societies

## NPSS is ...

- Organizes and supports many symposia, conferences and workshops each year

- Publishes 4 Transactions (peer reviewed journals)

- Publishes Newsletter to all members

- Presents awards each year to recognize major contributions to the field

- Provides access to publications on-line (IEEE Xplore)

- Members save on conference registration

- Members keep in touch via the Newsletter

- Supports the growth of the profession

- Members can get involved with NPSS and help direct and further promote our profession

- Excellent network!

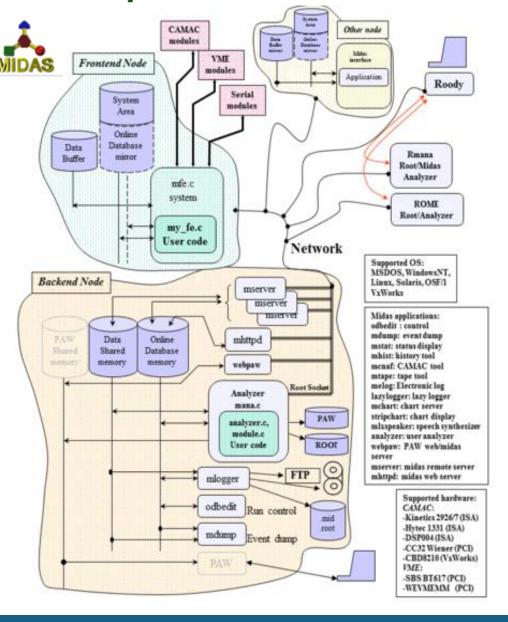

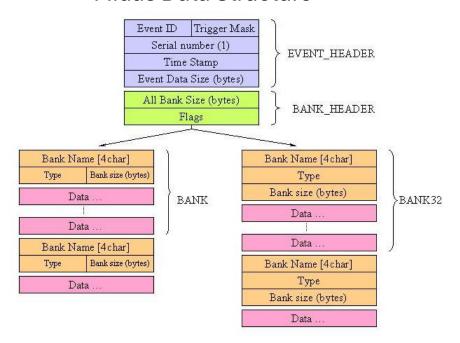

### **Data Acquisition – Software Architecture**

#### Midas Data Structure

```

Evid:0001- Mask:0002- Serial:39036- Time:0x5c5cd9c2- Dsize:512376/0x7d178

#banks:4 - Bank list:-W200W201W202W203-

Bank:W200 Length: 128080(I*1)/32020(I*4)/32020(Type) Type:Unsigned Integer*4

1-> 0xa0007d14 0x000002ff 0xff00987c 0x1bc43d3d 0x3aa707d1 0x3aa33aa6 0x3aa63aa4 0x3aa53aa7

9-> 0x3aa73aa9 0x3aa63aab 0x3aac3aa2 0x3aa63aa7 0x3aa73aa2 0x3aa43aa4 0x3aa73aa9 0x3aa93aa7

17-> 0x3aa63aa1 0x3aab3aa5 0x3aa33aa4 0x3aa83aa5 0x3aab3aa7 0x3aa83aa3 0x3aa53aa6 0x3aa73aa5

25-> 0x3aaa3aa4 0x3aa83aa2 0x3aa63aa5 0x3aa83aa9 0x3aab3aa6 0x3aa3aa3 0x3aa3aa2 0x3aa73aa3

33-> 0x3aa3aa7 0x3aa53aa6 0x3aab3aa6 0x3aa53aa6 0x3aa63aa2 0x3aa53aa5 0x3aa93aa1 0x3aa93aa5

41-> 0x3aa53aa5 0x3aa3aa3 0x3aa53aa1 0x3aa73aa4 0x3aa43aa6 0x3aaa3aa7 0x3aa53aa2 0x3aac3aa7

```