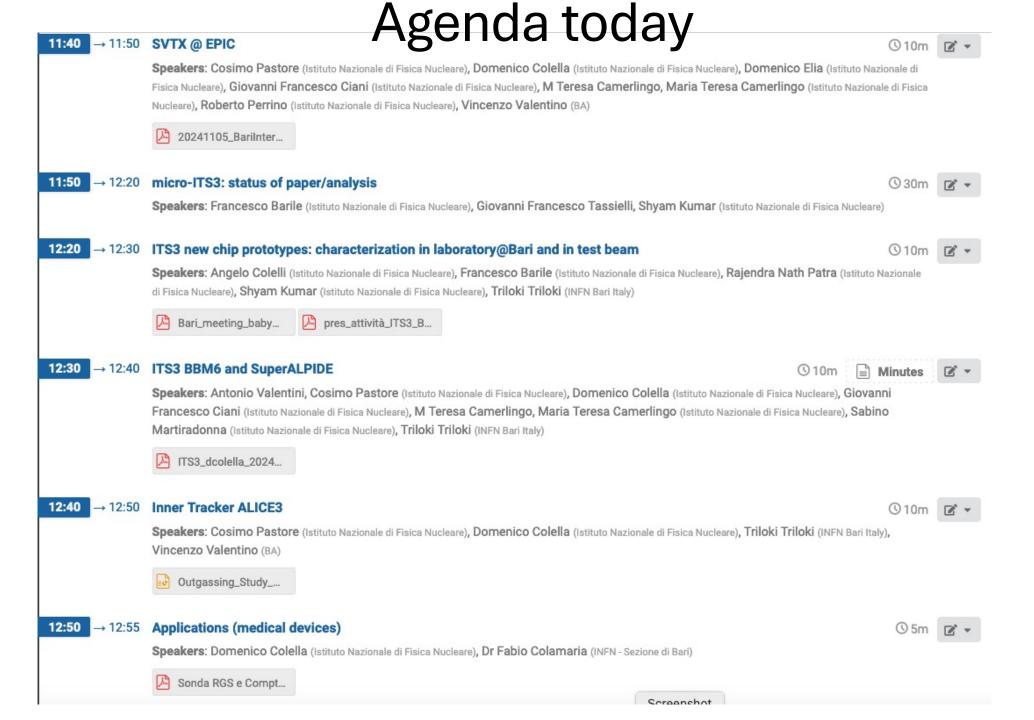

- ITS3

- paper on «microITS3»

- Discussion in Krakow with Bodgan and S.Masciocchi

- Bogdan, Gianfranco and Shyam will call for an internal meeting (after the 18<sup>th</sup> of November), within GSI and Bari teams, to answer the remaining open points.

- · Draft of the paper and material should be circulated in advance

- Characterization of the chip prototypes

- participation to test beams in the last months

- BabyMoss (first weeks of September) → with also training for testing

- Final MLR1 OPAMP test beam (in October)

- Procurement of instrumentations for our lab

- 2 new 55Fe sources (from Progetto Quasimodo) received

- 2 new DAQ boards received

- 1 BabyMoss and 1 raiser board will arrive tomorrow (others eventually later)

- Procurement of new power supplies (with funds from Quasimodo)→ order to be placed

- ITS3 + other projects

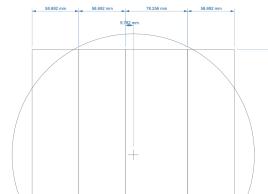

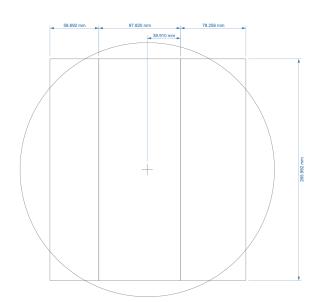

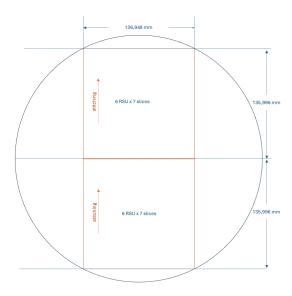

- - Layout «SVT-1» --> ITS3: 3 L0, 3 L1 + SVT: 4 L0, 4 L1

- Layout «SVT-3» --> ITS3: 3 L2

- Layout «NA60+» --> PixelChamber: 16 + Na60+: 4

--> 7 wafers

--> 3 wafers

--> 10 wafers

Layout 1

• Next year we should procure either ER2 pad wafers or dummy chips from blank wafers with Cr/Al metal deposition

- ALICE 3

- - Cosimo should place the order the next week at the latest.

- ALICE 3

- discussion in Krakow (Upgrade week) on how to setup «projects» with Work Pakage substructure

https://indico.cern.ch/event/1415726/timetable/

Inner Tracker

- Chip design (needs two branches, and two WP leaders dedicated to VD/ML)

- Common items:

- Common blocks

- Serial powering

- · Front-end optimisation

- VD-ML optimisation:

- · Development of a small pitch, high radiation tolerance chip

- Adaptation and configuration for ML

- Two independent reticle assemblies (VD and ML)

- Target: submission end of 2025/beginning of 2026

- Characterisation (shared)

- Characterisation of chips and modules in vacuum

- Testing of existing prototypes at high radiation level

- Characterisation of bent chips

- Sensor integration (VD focussed)

- Lightweight module ('MAPS foil')

- 2.5d / 3d integration of powering and data transmission

- ML integration (for lightweight version)

- ALICE 3

- discussion in Krakow (Upgrade week) on how to setup «projects» with Work Pakage substructure

https://indico.cern.ch/event/1415726/timetable/

Inner Tracker

- ML module/stave design (→ will evolve into production)

- Mechanics and integration (two WP leaders dedicated to VD/ML synergy with OT)

- VD: retractable in-vacuum mechanics

- ML: bent or planar module and staves

- Global integration and interfaces to beam pipe and iTOF/OT

- Cooling architectures

- Readout and power supply services (two WP leaders dedicated to VD and ML)

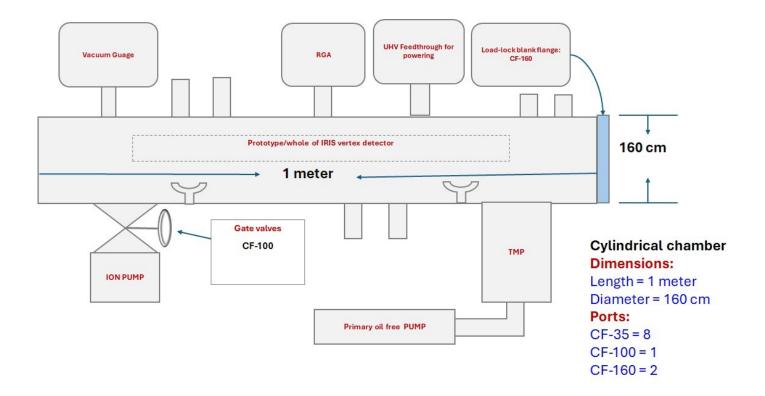

- Vacuum integration

- Radiation hardness

- Serial powering

- Physics performance and response simulation (common to OT)

- Detector Control System (not starting yet)

- Calibration and data quality assurance (VD needs to start first)

- Alignment procedures for the IRIS