# Compact and Scalable Electronics for Sub-10 ps Timing in Particle Physics and Medical Imaging

Yuri Venturini\*,

y.venturini@caen.it

on behalf of

C. Tintori, Dr. A. Abba, Dr. C. Maggio, L. Colombini Dr. D. Ninci, A. Mati, A. Picchi

#### Outline

**FERS-5200**

- FERS-5200 family: project core and architecture

- X5203: picoTDC timing unit

- Timing performances

- Feasibility study for SAND

- X5203 PET application: the Provision scanner

- Conclusions

#### **FERS-5200**

#### Front End Readout System 5200: The Core Idea

Compact and Scalable

Multi-channel

Readout Electronics

High-granularity

Detectors with

Thousands of Channels

Cost-effective Readout Systems

Off-the-shelf **front-end ASIC** for scientific

instrumentation

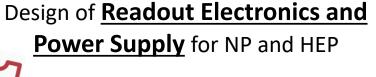

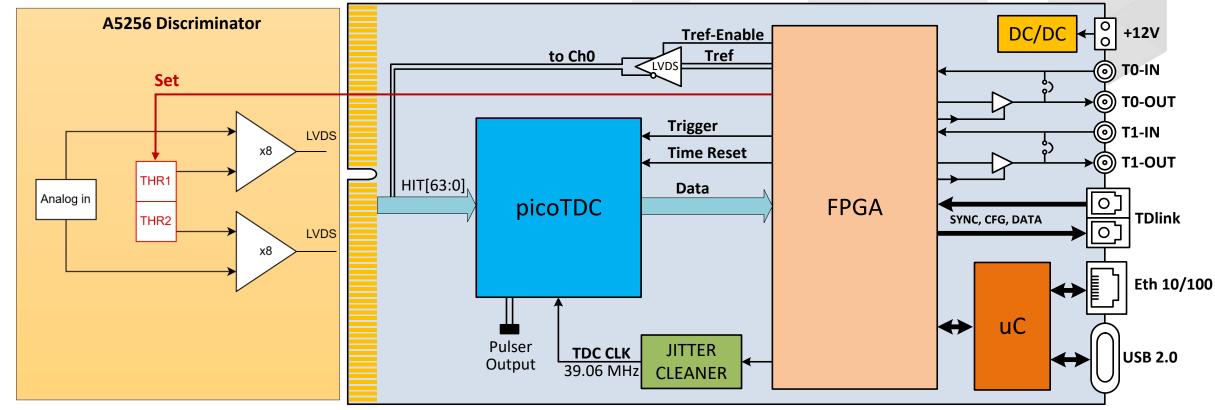

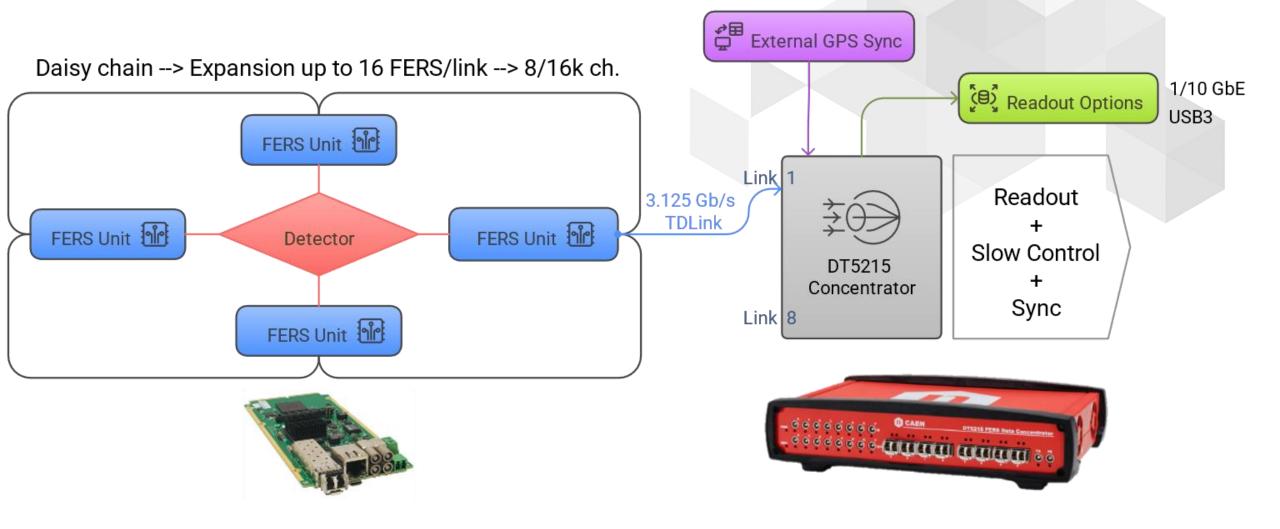

## FERS-5200: block diagram

Sync to ext. GPS

#### FERS-5200 architecture

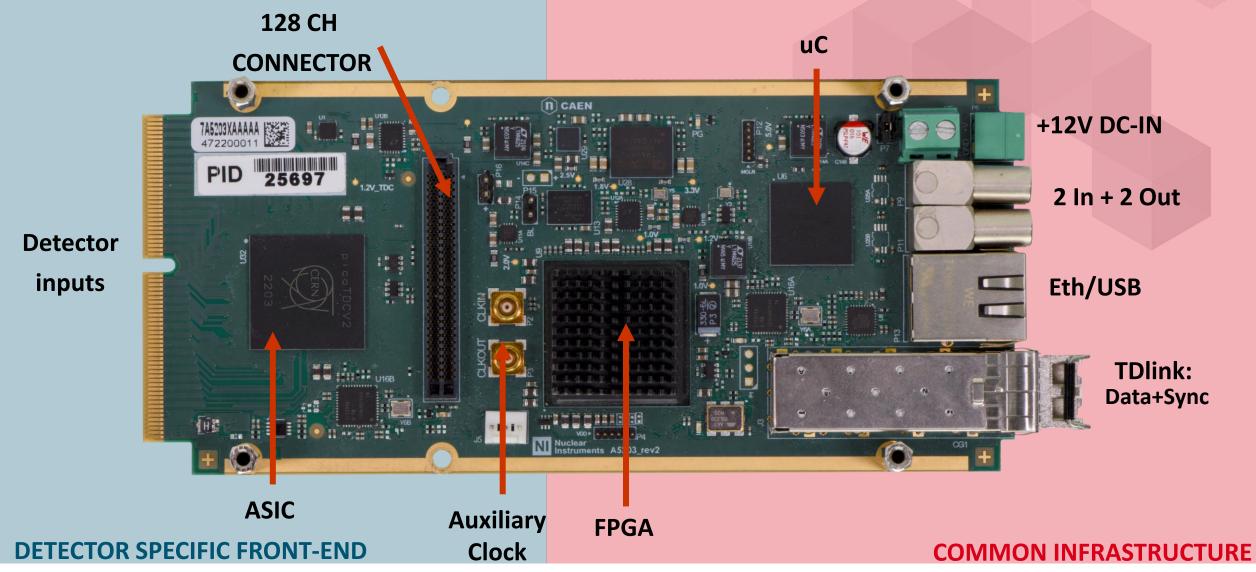

## x5203: 64/128 channel 3.125 ps TDC

- TDC: 64/128 channels (1 picoTDC = 64 ch), LSB = 3.125 ps, dynamic range = 56 bit (extended by FPGA)

- Inputs: digital, LVDS → A5256 Front-End (= 16-ch discriminators)

- Output Data: Time of Arrival (ToA), Time over Threshold (ToT)

- Data throughput: up to ~64 Mcps/board

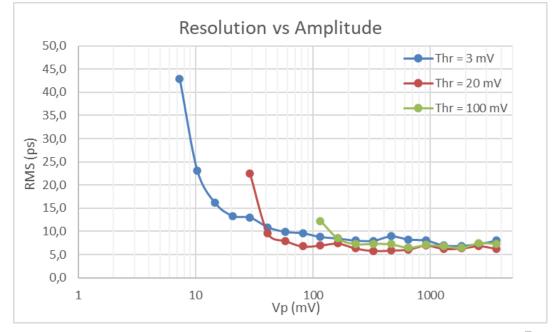

#### X5203 performances

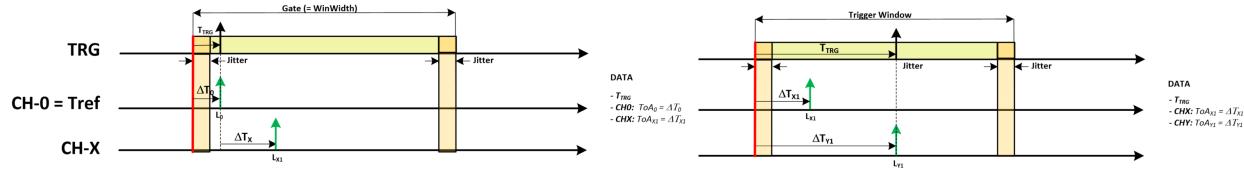

Acquisition modes: Common Start/Stop (Tref=Ch0), Trigger Matching, Streaming

#### **DeltaT Resolution** (\*):

- Same board: typ 5 ps RMS

- Board to board: ~20 ps RMS → Precision of the TDLink sync synchronized by DT5215 Concentrator Board via TDlink

- Board to board: ~8 ps RMS synchronized by DT5215 Concentrator Board via TDlink with auxiliary daisy chain/fan out clock cables

- (\*) Tested with CAEN A5256 discriminator. Pulse: 0.5 Vpp, 0.8 ns rise time

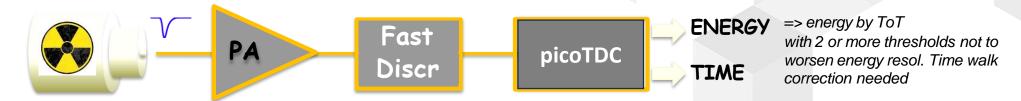

#### **Energy reconstruction**

| x5203 Pros                                                                                                                               | x5203 Cons                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>high timing resolution (~ 5 ps), high channel density, almost no dead time</li> <li>provides ToA and ToT in one word</li> </ul> | <ul> <li>ToA affected by walk effect</li> <li>No energy information (PHA) acquired -&gt; need for a separate ADC readout chain</li> </ul> |

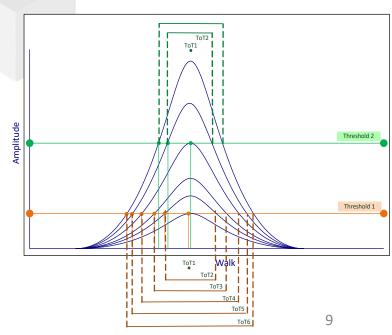

-> ToT-Based Analysis: Walk correction and PHA

- ToT can be used to correct for time walk => no need of Constant Fraction Discriminator in hardware

- ToT can be used to reconstruct pulse amplitude: ToT PHA curve is not linear => need calibration (pulse shape dependent)

- FPGA ToT filter: rejects pulses if ToT < LowCut or ToT > HighCut (remove noise, DCR, saturation...)

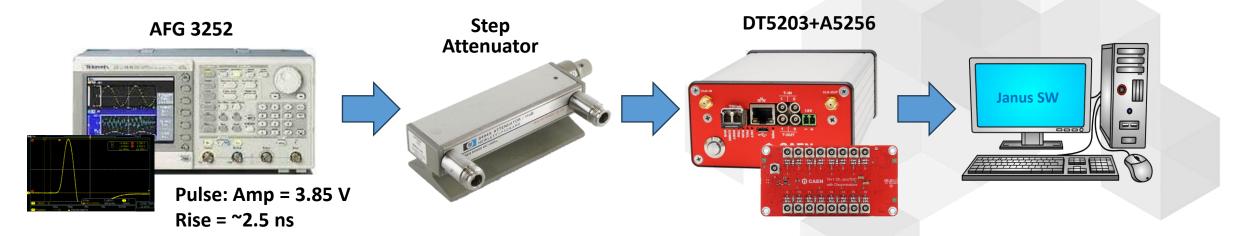

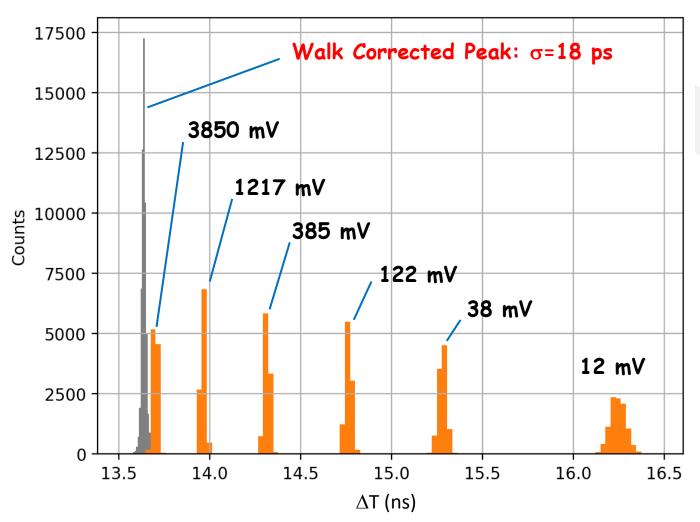

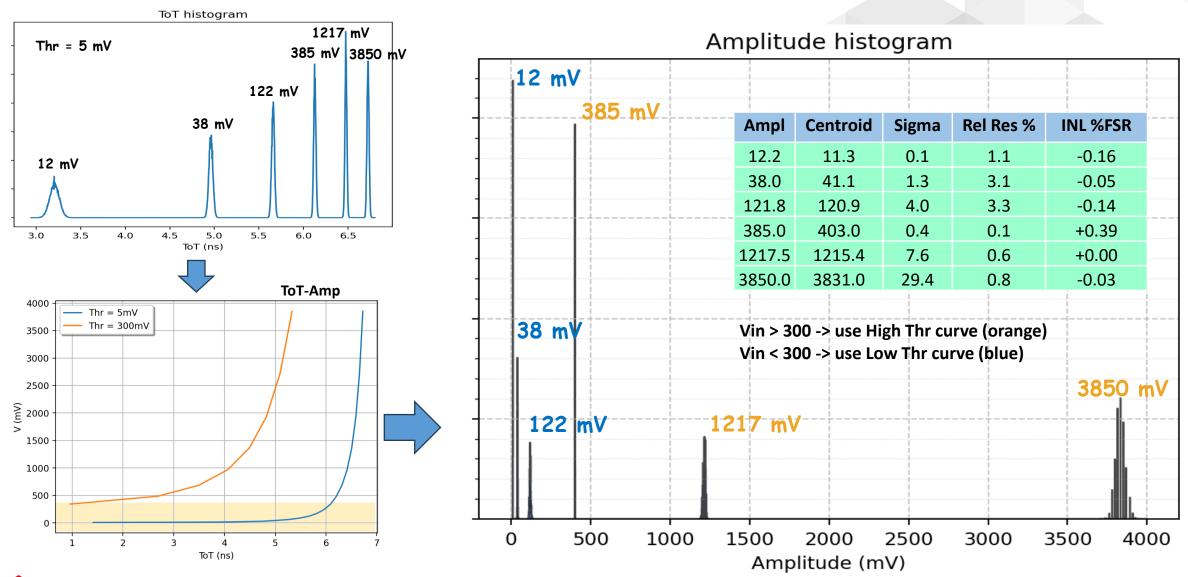

#### **ToT Analysis Setup**

**Common Start Acquisition:** start on Ch0 with fixed amplitude, stop on Ch1 and Ch2 (dual threshold) with variable amplitude (max = 3.85 V). Delay = 13 ns

- 1. Sweep: acquire ToT and  $\Delta$ T (ToA) at different amplitudes (from 0 to 54 dB, 3 dB step)

- 2. Fit points and build **ToT-Walk (ToA)** and **ToT-Ampl** curves

- 3. Use curves to **correct Walk** from ToT (replace CFD)

- 4. Use curves to **get Amplitude** from ToT (make ADC from TDC)

#### ToT calibration curves (double threshold)

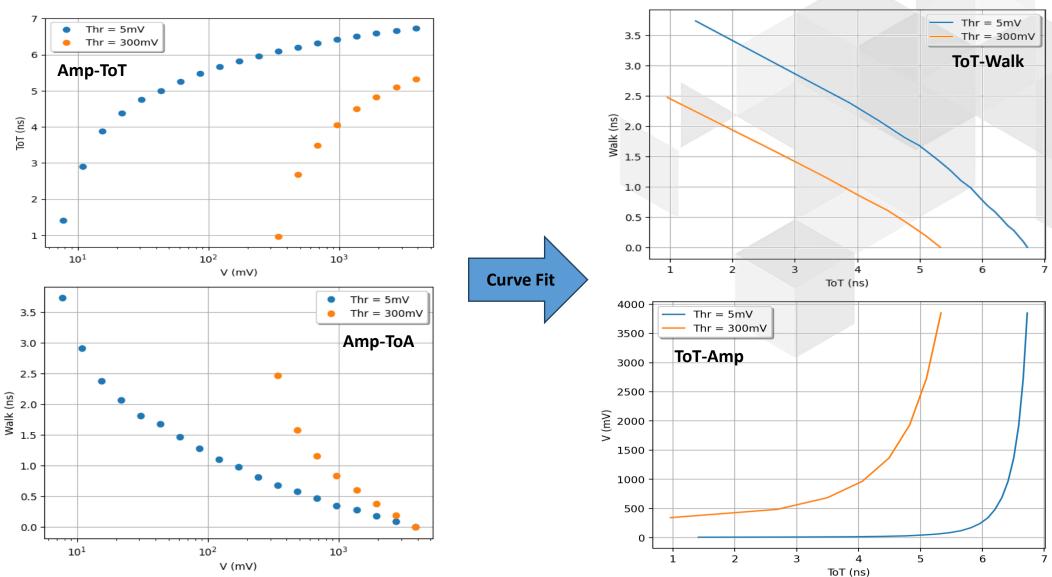

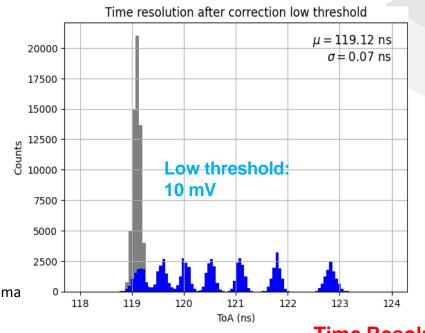

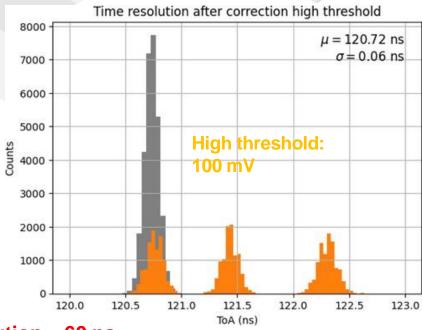

#### Walk Correction

- Pulses at 6 different amplitudes over a 50 dB dynamic range

- ~2 ns spread on  $\Delta T$  (ToA) caused by the walk effect: 6 separate peaks !!

- → timing resolution totally destroyed

- $\Delta T$  corrected by ToT using a 5<sup>th</sup> order polynomial fit of the **ToT-Walk** points taken at threshold = 5 mV

- Corrected  $\Delta T$  histogram presents one single peak:

18 ps RMS over 50 dB dynamic range

#### **Amplitude Reconstruction**

#### **♣ FERS-5200**

## Feasibility study for SAND calorimeter

PMTs + Led Driver

Ongoing feasibility study of the ToT technique for the readout of **5000 PMTs** in SAND (DUNE)

- Led Driver CAEN SP5601 (λ~400 nm) + fiber splitter

- PMT signal → variable amplitude

- DT5203 + A5256 → dual threshold

Courtesy of A. Di Domenico, V. Di Silvestre, P. Gauzzi - INFN Roma

## Feasibility study for SAND calorimeter

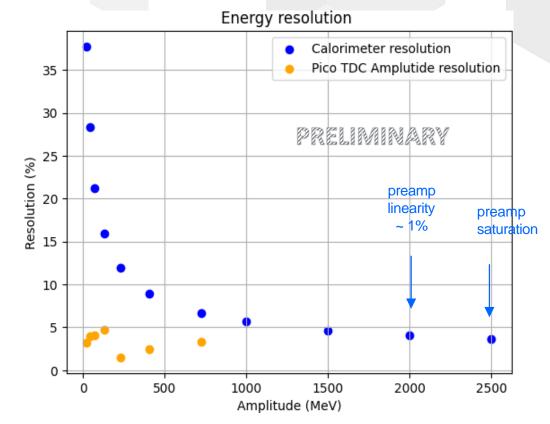

comparison with calorimeter resolution (  $\sigma_E/E \sim 5.7\%/\sqrt{E}$  )

Courtesy of A. Di Domenico, V. Di Silvestre, P. Gauzzi - INFN Roma

Amplitude resolution obtained from ToT is compared with the intrinsic calorimeter resolution (assuming PMT gain 1 mV = 1 p.e. = 1 MeV => 1 V = 1 GeV)

to be done: optimization of the thresholds for the best perfomance in the whole expected dynamic range (2.5-2000 mV)

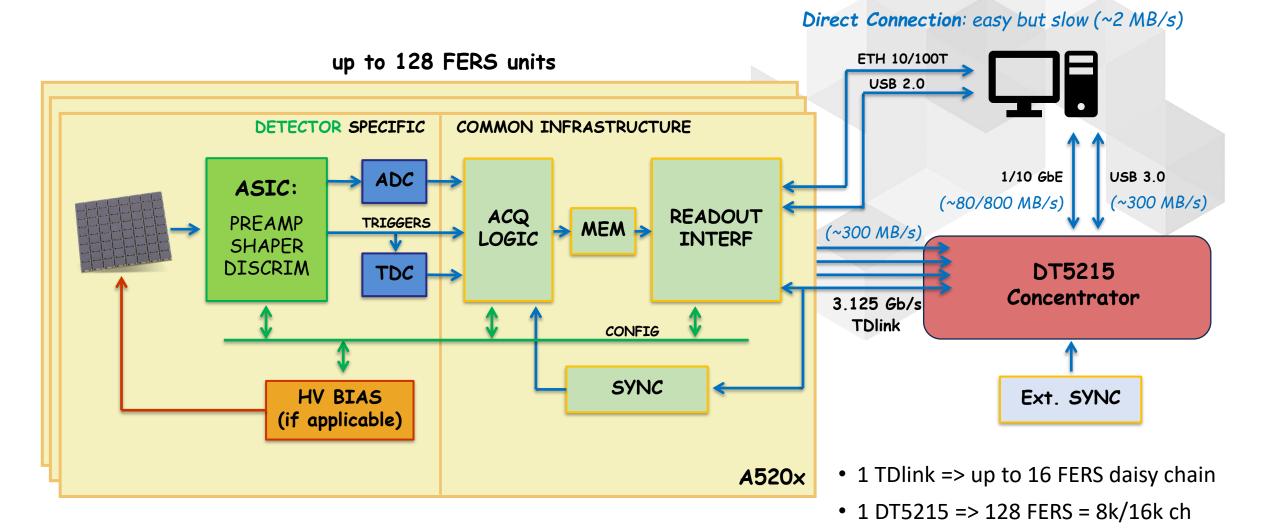

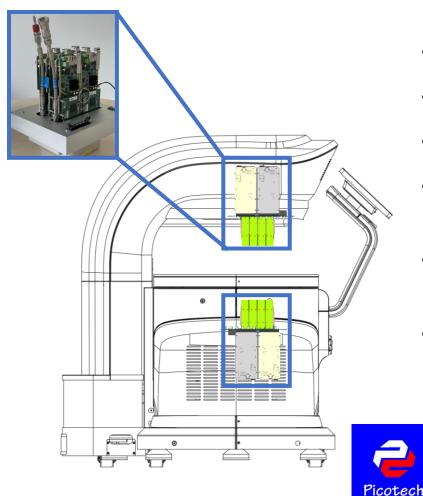

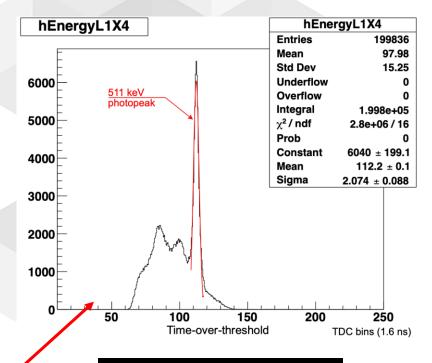

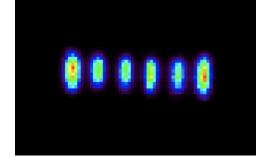

#### The Provision PET Scanner

- 2x768 SiPM channels

- 2x6 A5203Bs (128 ch TDC)

- 1 DT5215 Concentrator

- Precise timing and TOT measurement

- High throughput almost zero deadtime

- ToT cut for Dark Count and noise suppression

'Empty' region thanks to TOT filter

#### Conclusions

- ToA and ToT measurements with a resolution of 5 ps RMS

- Walk correction (mimic CFD) possible with single or double threshold:

18 ps RMS on a 50 dB dynamic range

- Amplitude reconstruction (mimic ADC) requires at least 2 thresholds (2 TDC channels).

Linearity = ~0.4%. Resolution = ~3%. Possible improvement with a more accurate threshold setting

- Optimal results in the Provision PET scanner: **few mm size radioactive sources easily detectable thanks to the excellent x5203 time resolution**

- Challenge: build ToA vs.ToT calibration curves in a real data acquisition case

- → Machine learning ???

- New FERS Units embedding the picoTDC + Radioroc chip: SiPM

Psiroc chip: **GEMs, Si strip**

# Thank you!

## Back-up slides

#### FERS-5200 architecture

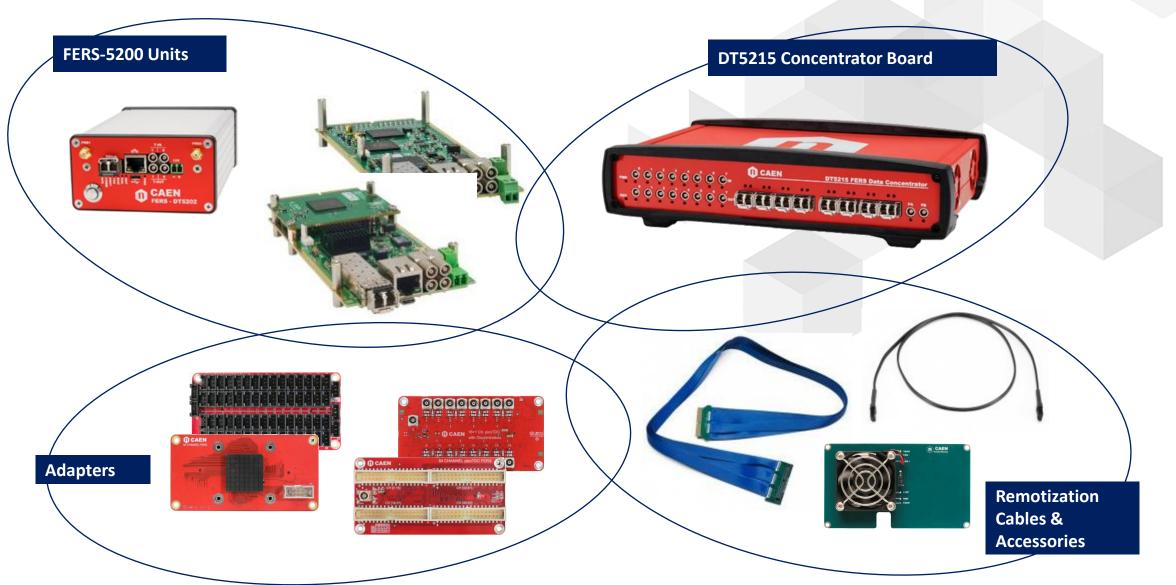

#### FERS-5200 Family

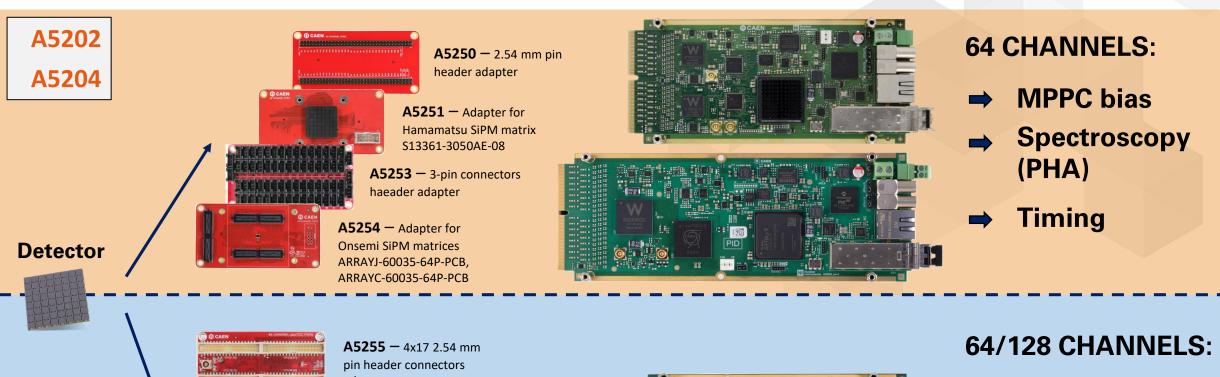

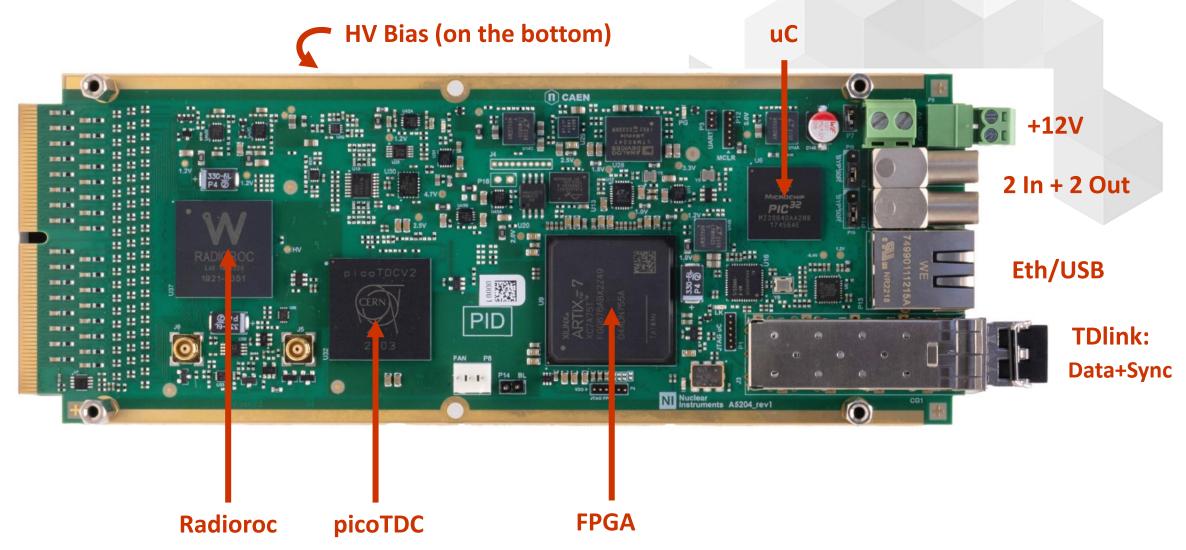

## FERS A5203: 64/128 channel Readout

#### FERS Units: A520X(naked)/DT520X(boxed)

- MPPC bias

- Spectroscopy (PHA)

- Timing

A5205

64 ch – Psiroc+picoTDC

A5204

64 ch – Radioroc+picoTDC

A5203

64/128 ch - picoTDC

A5202

64 ch – Citiroc 1A

**COMING SOON**

- Time Measurements (ToA & ToT)

- Amplitude Estimation

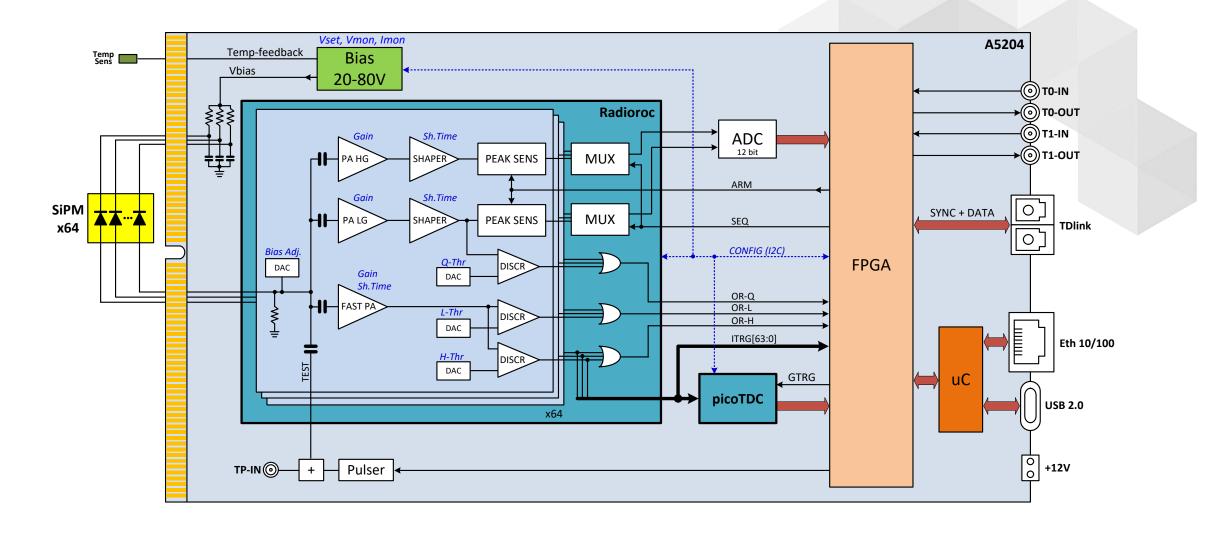

#### Technical Specifications A5204 & A5205

**A5204:** 64 channel SiPM Readout based on Citiroc/Radioroc+picoTDC

- Analog inputs (charge, not voltage)

- All-in-one readout: Preamp + Shaper + Discr + ADC + TDC + HV Bias (20-80 V)

- Dynamic Range: 1 to 2500 p.e.

- Single photon detection (threshold at 1/3 p.e.)

- Timing resolution = 55 ps FWHM (A5204 only)

- Acquisition Modes:Counting, Spectroscopy (PHA), Timing (ToA + ToT), Mixed (PHA + ToA)

**A5205:** 64 channel SSD, GEM, PIN diode readout based on Psiroc + picoTDC

- Pos/Neg inputs. Dynamic range up to 5 pC with PHA, 100 pC with ToT

- Programmable gain: 125 mV/pC up to 4 V/pC. Min trigger threshold = 0.5 fC

- Linearized ToT

**COMING SOON**

#### Different combos for all customers' needs

adapter

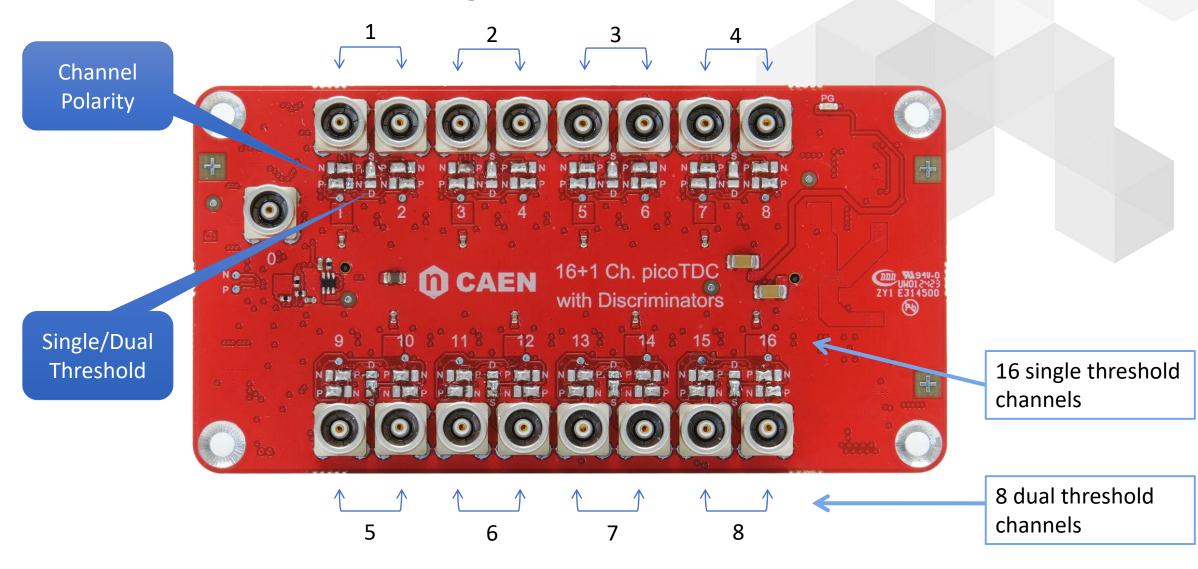

**A5256** — 16+1 channel single threshold, 8+1 channel dual threshold edge discriminator adapter

- Time **Measurements** (ToA & ToT)

- **Amplitude Estimation**

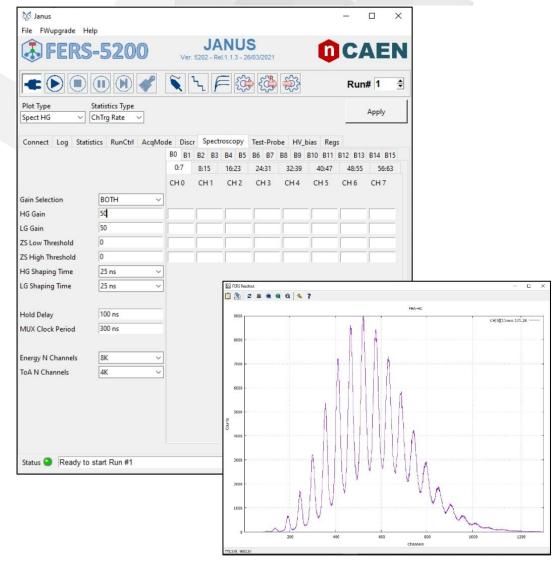

#### Janus Software

- Open source software for multi-board configuration and data readout

- Specific Janus version for each FERS unit (Janus 5202, Janus 5203, ...) with common FERSlib library

- SDK for user customization (lib + demo) [COMING SOON]

- GUI (Python) and console mode based on C/C++ readout programs

- Multi parametric Jobs and Runs with time or counts preset

- Output files: lists in .bin or .csv format, spectra, raw data

- Off-line runs for Post-processing and Event Building

- Live plots (with gnuplot) and statistics monitor

- Up to 300 MB/s data throughput (with DT5215 Concentrator via USB 3.0 or 10 Gb Eth)

## A5203 Technical Specification Table (1)

| MECHANICAL        | Weight 40 g (A5203 with spacers mounted); 163 g (A5203B with spacers mounted)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>Dimension</b><br>73.0 W x 30.0 H x 174.5 L mm <sup>3</sup><br>73.0 W x 25.0 H x 174.5 L mm <sup>3</sup>                                                                                                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDC INPUT         | A5203: 64 channels (1 edge connector type HSEC8-170) A5203B: 128 channels (2 edge connectors type HSEC8-170)  • Mating connector: Samtec HSEC8-170-01-S-DV  • Input Type: reduced LVDS  • Input voltage: Min = -40 mV Max = +1450 mV  • Common Mode: Min = +70 mV Max = +1200 mV  • Differential voltage: Min = +140 mV Max = +450 mV  • Input Termination: 100 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                               |

| TIMING RESOLUTION | $  LSB = 3.125 \ ps $ • $\Delta T_{RMS} = \sim 5 \ ps$ . Tested with LVDS signals, two passive splitters and delay • $\Delta T_{RMS} = \sim 7 \ ps$ . Tested with pulse generator (1 Vpp, 0.8 ns rise/fall), pass • $\Delta T_{RMS} = \sim 20 \ ps$ with variable amplitude pulses (30 mV to 1 V) and walk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | sive splitter and 5 ns cable delay                                                                                                                                                                                                                                            |

| DYNAMIC RANGE     | Time measurement dynamic range in picoTDC:  Leading Edge only: T <sub>LEAD</sub> = 24 bits (FSR = ~ 52 µs)*  Leading + Trailing Edge: T <sub>LEAD</sub> / T <sub>TRAIL</sub> = 24 bits (FSR = ~ 52 µs)*  Leading + ToT8: T <sub>LEAD</sub> = 19 bits, T <sub>TOT</sub> = 8 bits (LSB size and FSR can be  Leading + ToT11: T <sub>LEAD</sub> = 16 bits, T <sub>TOT</sub> = 11 bits (LSB size and FSR can be  Coarse time stamp in FPGA (56 bits @ 12.6 ns) con be combined with pict measurement to a maximum dynamic of 64 bit (streaming acquisition mo 26bits (FSR = ~ 210 µs) optional                                                                                                                                                                                                                                                                                                                                               | programmed) oTDC data to extend the full scale range of the time                                                                                                                                                                                                              |

| ACQUISITION MODES | Common Start: TDC chO is the common start that opens the acquisition gate and represe measurements: $T_{LEAD} = \Delta T_N = T_N - T_0$ . The gate width is programmable by Output Data: $T_{LEAD}$ or $T_{LEAD}$ + ToT  Common Stop: Same as common start, but chO is used as a common stop that closes the Output Data: $T_{LEAD}$ or $T_{LEAD}$ + ToT  Trigger Matching: The trigger signal (typ. from TO/TI inputs) defines an acquisition window window will be recorded. Multi-hit acquisition is supported. All time measures 25.6 ns), while the relative time between the hits keeps the TDC timing is Output Data: $T_{LEAD}$ or $T_{LEAD}$ + $T_{TRAIL}$ or $T_{LEAD}$ +ToT  Streaming: Continuous hit recording, without any gate or trigger windowing. All hit till (minimum LSB = 3.125 ps) and saved in the form of a sorted list.  Output Data: $T_{LEAD}$ or $T_{LEAD}$ + $T_{TRAIL}$ (or $T_{LEAD}$ +ToT, COMING SOON) | y software. Any hit falling outside the gate will be discarded. e acquisition gate: $\Delta T_N = T_0 - T_N$ . with programmable width and offset. All hits falling into the urements are referred to the Coarse Trigger Time Stamp (LSB resolution (minimum LSB = 3.125 ps). |

## A5203 Technical Specification Table (2)

| FPGA TRIGGER TIME STAMP  | <ul> <li>56-bit counter, 25,6 ns step</li> <li>up to 128 boards can be synchronized with the DT5215 FERS-CB by sending a time stamp reset signal via TDlink</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FRONT PANEL I/Os         | <ul> <li>T0-IN, T1-IN: LEMO-00 connector, NIM or TTL (terminated to 50 Ω)</li> <li>T0-OUT, T1-OUT: LEMO-00 connector, TTL (50 Ω termination required)</li> <li>Jumpers for IN-OUT bypass and termination removal (daisy chaining).</li> <li>Functions (SW programmable): Trigger, Acquisition Start/Stop, Sync, Busy, Veto, Signal inspection, etc</li> <li>T0/T1 inputs can be used to drive TDC - Ch0 = Tref (possible degradation of the resolution because of the FPGA temperature dependence)</li> </ul>                |  |

| FRONT PANEL LEDs         | GREEN: Power-ON, Init-Done, Run, Trigger, Data Ready, TO-IN, TI-IN ORANGE: Event Overrun (rejected triggers because received while busy) RED: Failure (missing clock, over-temperature, etc)                                                                                                                                                                                                                                                                                                                                 |  |

| INTERNAL PULSER          | Fast reduced-LVDS output (one signal only) with programmable frequency and width, for debug purposes                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| COMMUNICATION INTERFACES | USB Ethernet  USB2.0: microUSB connector  Bandwidth = ~ 3 MB/s  ■ Ethernet connector, type Rj-45. Supports  10/100 Mbit/s connection to a PC  Bandwidth = ~ 2.5 MB/s  ■ Optical Link  Small Form Factor Pluggable (SFP+) transceiver component for optical connection (3.125 Gbit/s). TDlink CAEN proprietary protocol allows for multi-board synchronization, slow control and data readout  Data Concentrator DT5215 required                                                                                              |  |

| FIRMWARE                 | <ul> <li>Firmware of FPGA upgrade via USB or Ethernet (or TDlink COMING SOON)</li> <li>Firmware of µC upgrade via Ethernet only</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                   |  |

| SOFTWARE                 | Readout SW Fully controlled by the Janus 5203 open source software for Windows* and Linux*. It can run in console mode (C program, with console commands and gnuplot display for plots) or connected to a GUI (Python) that implements user friendly configuration panels and run controls.  Janus 5203 can acquire, plot and save output files with ToA, ToT histograms, as well as list files (trigger timestamp, ToA and ToT for each channel).  Web Interface  Board information and monitoring, Ethernet configuration. |  |

| POWER REQUIREMENTS       | Single power supply: +12 V. Accepted voltage range: MIN +7 V, MAX +15 V  (110 V/220 V AC/DC converter provided with Desktop version only)                                                                                                                                                                                                                                                                                                                                                                                    |  |

| POWER CONSUMPTIONS       | 700 mA @ +12 V, i.e ~ 8.4 W (A5203 - 64 channels)<br>tbd (A5203B - 128 channels)                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

## A5256 Focus

## A5256 Hardware Configuration

## A5256 Technical Specification Table

| Inputs                | Single Threshold: 16+1 inputs positive/negative polarity, 50 $\Omega$ impedance Double Threshold: 8+1 inputs positive/negative polarity, 50 $\Omega$ impedance                                                                                                               |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Min/Max Input Voltage | - 4 V / +3 V                                                                                                                                                                                                                                                                 |

| Min Detectable Signal | 1.5 mV                                                                                                                                                                                                                                                                       |

| Threshold Range       | -1.2 V / +1.2 V                                                                                                                                                                                                                                                              |

| Threshold Step        | 0.61 mV                                                                                                                                                                                                                                                                      |

| Timing Resolution     | A5256 mounted on A5203: $\Delta T_{RMS} = ~7 \text{ ps. Tested with a pulse generator (1 Vpp, 0.8 ns rise/fall pulses), one passive splitter and delay cables.}$ $\Delta T_{RMS} = ~20 \text{ ps. with variable amplitude pulses (30 mV to 1V) and walk correction by ToT.}$ |

| Non-Linearity         | ≤ 0.18 % typ.                                                                                                                                                                                                                                                                |

| Efficiency            | <2 mV typ. (3 mV max)  Measured with 150 mV signal, with 1.6 ns rise time                                                                                                                                                                                                    |

## A5204 Focus

#### FERS A5204: 64 channel SiPM Readout

#### **FERS-5200**

## A5204: block diagram

## A5204 Technical Specification Table (1)

| MECHANICAL                        | Weight 161 g (A5204 with spacers mounted);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Dimension</b><br>72.8 W x 22.0 H x 208.5 L mm <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUTS                            | 64 channels Input edge connector type Samtec HSEC8-170 Mating connector: Samtec HSEC8-170-01-S-DV Signal polarity: Positive Each SiPM input has two pins:  Cathode with HV bias (min = +20V, max = +80V)  Anode closed to -100 ohm, feeding the Radioroc inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HIGH VOLTAGE (SiPM Bias)          | HV module for SiPM biasing (A7585D) HV Range: +20V/+80V, Max 10 mA Individual bias adjustment on channel basis (8 bit DACs, LSB = -2 mV, a Automatic temperature feedback for SiPM gain stabilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | djust range = 550 mV)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ACQUISITION MODES                 | Spectroscopy:  The common trigger initiates the peak sensing detection and A/D conv-10 µs. Output Data: Trigger time stamp, Trigger ID, PHA (Low and/or H Counting:  32 bit counters, up to 200 MHz. Common trigger defines dwell time (i.e windows. Internal period trigger from 16 ns to -34 s. Output Data: Trigg available. Counters are automatically reset after each trigger.  Timing (Common Start):  The Tref signal (TO, T1 inputs) is a common start that opens the acquisit acquired as and treft and, optionally, as ToT for PHA estimation. Out Timing (Common Stop):  Same as common start, with Tref used as a common stop that closes the the trigger (look back acquisition).  Timing (Trigger Matching):  The common trigger signal defines an acquisition window with program recorded. Multi-hit acquisition is supported. Output Data: Trigger time some standard of the form of a sorted list. Output Data: ToA or ToA+ToT | igh Gain). Zero suppression with programmable threshold.  c. counting window). No dead-time between subsequent er time stamp, Trigger ID, channel counts. Zero suppression  tion gate with programmable width. Channel self-triggers are trut Data: Trigger (=Tref) time stamp, Trigger ID, MT or MT+ToT  the acquisition gate. Acquired events are those ones arrived before  mable width and offset. All hits falling into the window will be stamp, Trigger ID, ToA or ToA+ToT |

| SENSITIVITY (GAIN) - SPECTROSCOPY | High Gain: Min = 5, Max = 80, 16 steps (1 step = 5)  Low Gain: Min = 0.5, Max = 8, 16 steps (1 step = 0.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SHAPING TIME - SPECTROSCOPY       | <b>Short Range:</b> Min = 20 ns, Max = 300 ns, 16 steps (1 step = 20 ns) <b>Long Range:</b> Min = 80 ns, Max = 1200 ns, 16 steps (1 step = 80 ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## A5204 Technical Specification Table (2)

| DYNAMIC RANGE - SPECTROSCOPY          | Up to 2000 photo-electrons @ 10 <sup>6</sup> SiPM gain                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SELF TRIGGERS - TIMING & COUNTING     | Dedicated fast preamps + discriminator for SiPM pulse detection. Trigger down to 1/3 p.e.  Fast Preamp Gain: Min = 15 (BW = 480 MHz), Max = 100 (BW = 55 MHz), 32 steps Discriminator Dual Threshold: Range = 278 mV; 1024 steps, 1 step = 0.27 mV                                                                                                                                                                                                                                                     |

| TIMING RESOLUTION - TIMING & COUNTING | 55 ps FWHM on a single p.e.  Time Stamp Range: 64 bit  Intrinsic timing resolution of picoTDC = 3.125 ps LSB                                                                                                                                                                                                                                                                                                                                                                                           |

| ToT - TIMING & COUNTING               | Time over Threshold (ToT): 1% linearity energy measurement up to 2000 p.e.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| COUNTING - TIMING & COUNTING          | Photon counting up to 200 Mcps per channel  MCS mode with programmable dwell time: from 16 ns to -34 s                                                                                                                                                                                                                                                                                                                                                                                                 |

| TRIGGER LOGIC                         | Global trigger common to 64 channels: used in Spectroscopy mode to start Peak acquisition, in Timing mode to generate the acquisition windows (Gate). Trigger-less acquisition only in Streaming mode.  Global Trigger Sources:  OR of self-triggers = OR(063)  Plane coincidence: OR(031) AND OR(3263)  Paired channels: AND(01) OR AND(23) OR AND(6263)  Majority with programmable threshold  External trigger (TO-IN, TI-IN, LEMO, TTL/NIM)  Internal periodic trigger with programmable frequency |

| TIME STAMP & SYNCHRONIZATION          | Acquisition Trigger Time Stamp: 56 bit, step = 8 ns  Two synchronization modes:  • TO or TI IN-OUT daisy chain: max jitter = 100 ns  • fiber optic (TDlink) and DT5215 Concentrator: up to 128 boards, max jitter 50 ps                                                                                                                                                                                                                                                                                |

| FRONT PANEL I/Os                      | <b>T0-IN, T1-IN:</b> LEMO-00 connector, NIM or TTL (terminated to 50 $\Omega$ ) <b>T0-OUT, T1-OUT:</b> LEMO-00 connector, TTL (50 $\Omega$ termination required)  SW selectable IN-OUT bypass and termination removal for daisy chaining <b>Functions</b> (SW programmable):  Trigger, Acquisition Start/Stop, Sync, Busy, Veto, Signal inspection, etc                                                                                                                                                |

| FRONT PANEL LEDs                      | GREEN: Power-ON, Init-Done, Run, Trigger, Data Ready, TO-IN, TI-IN  ORANGE: Event Overrun (rejected triggers because received while busy)  RED: Failure (missing clock, over-temperature, etc)                                                                                                                                                                                                                                                                                                         |

## A5204 Technical Specification Table (3)

| INTERNAL PULSER          | Radioroc provides a test input pin that can be internally connected to the pre-amplifier inputs, channel by channel. The test signal can come from an external signal (MCX connector on the PCB) or generated by an internal pulser with programmable amplitude. The internal pulser can be trigger by TO/TI IN or by the internal periodic trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| COMMUNICATION INTERFACES | USB Ethernet USB2.0: microUSB connector Bandwidth = ~ 3 MB/s  Bandwidth = ~ 2.5 MB/s  Ethernet connector, type Rj-45. Supports 10/100 Mbit/s connection to a PC  Bandwidth = ~ 2.5 MB/s  Bandwidth = ~ 2.5 MB/s  TDlink CAEN proprietary protocol allows for multiboard synchronization, slow control and data readout  Data Concentrator DT5215 required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| FIRMWARE                 | Firmware of FPGA be upgraded via USB or Ethernet Firmware of µC can be upgraded via Ethernet only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| SOFTWARE                 | Readout SW Fully controlled by the Janus 5204 open source software for Windows* and Linux*. It can run in console mode (C program, with console commands and gnuplot display for plots) or connected to a GUI (Python) that implements user friendly configuration panels and run controls.  Janus 5204 can perform multiple board acquisition of PHA energy spectrum (Low and High Gain). ToT spectrum (represents PHA in timing mode) DT spectrum, with event building based on trigger ID or time stamp.  Live Display: channel hit count and rate, trigger rate, lost triggers, data throughput, acq. time, etc Plots: PHA, DT, ToT, hit rate, 2-D heat map with channel hit rates or PHA.  Output Files: histograms (spectra), list files (PHA, ToA, ToT, DT), Run Info, Sync file.  Web Interface Board information and monitoring, Ethernet configuration. |  |

| POWER REQUIREMENTS       | Single power supply (+12 V). Regularly working in a range between +7 V and +15 V 110V/220V AC/DC converter provided with Desktop version only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| POWER CONSUMPTIONS       | t.b.d.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |