# Tecnologie di elettronica per il futuro

Speaker: Riccardo Travaglini

Workshop di Sezione per la discussione della Strategy Europea sulla Fisica delle Particelle

7/11/2024 Bologna

### Argomenti e contributi

- cosa viene fatto in Sezione per l'elettronica dei futuri rivelatori, possibilmente nel contesto delle attività INFN italiane

- quali settori/tecnologie sono quelle più promettenti per i rivelatori del futuro

- di cosa avrebbe bisogno un laboratorio di elettronica INFN per affrontare le sfide dello sviluppo e R&D di tali tecnologie

- Contributo sostanziale alla preparazione della presentazione: RT, Gabriele Balbi, Davide Falchieri, Luigi Rignanese

- Attivita' mostrate nella presentazione sono lavori sviluppati dal personale afferente al Servizio di Elettronica

## Microelettronica

Attivita': Arcadia, Ignite, Aspides

Temi: IP block development, pixel chip monolitici, verification, FPGA, link veloci, radiation tolerance studies

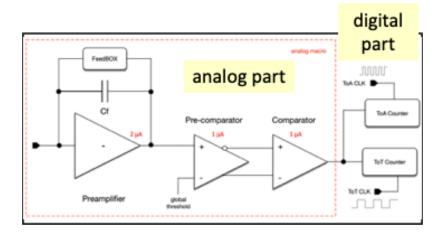

## Ignite

- INFN BO designed the digital part of this ASIC:

- 32x8 pixel matrix with an area of 25x100 μm2 each

- ToT based front-end architecture

- technology: TSMC 28 nm HPC+

- deadline: July 2024

- mini@sic (~1 mm2)

- EDA tool: Cadence

- in collaboration with Alberto Stabile (MI), Luigi Gaioni (BG)

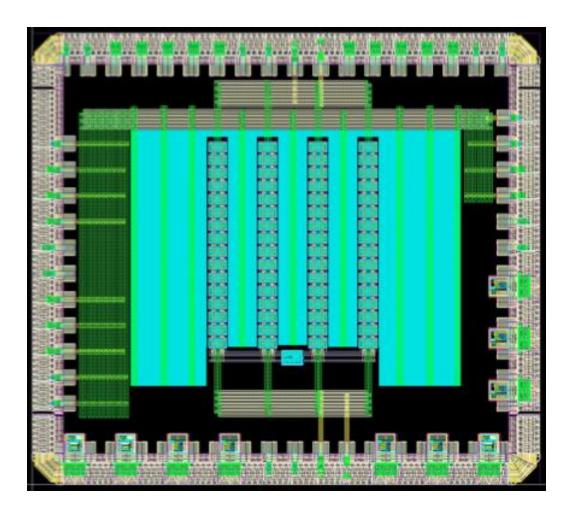

#### Arcadia

- rivelatori pixel monolitici full depleted

- il progetto EIC Pathfinder Open "1MICRON", al quale l'INFN parteciperà per lo sviluppo di un nuovo sensore basato sulla tecnologia ARCADIA ed ottimizzato per la lettura di raggi-X, è stato approvato

- Tecnologia papabile per InnerTrackingSystem FCC

- Bologna: Verification della parte digitale, sviluppo del sistema di read-out (320 MHz DDR)

- LFoundry 110 nm

- Continuera' in DRD 7.6

- EDA tool: Synopsys

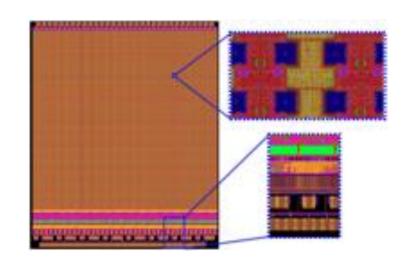

### Aspides

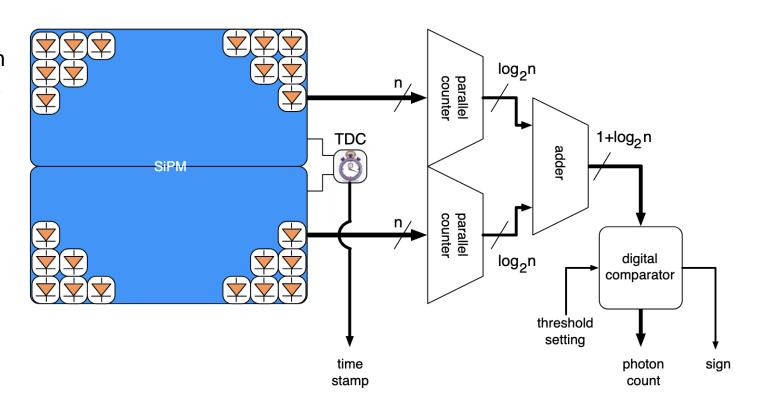

A CMOS SPAD and **Digital SiPM** Platform for High Energy Physics

Mainly for dual readout calorimetry but interests in single photon applications (RICH and Neutrino physics) LFoundry 110 nm

#### Bologna:

- ASIC design and verification (digital)

- Testing and data acquisition integration

- Radiation tolerance studies

all integrated in a single ASIC with both analog and digital functionalities

#### Goal of the project:

the development of a technology platform for the design, production and commissioning of <u>digital silicon photomultipliers</u> (dSiPMs), detectors with single-photon sensitivity and embedded functionalities

# Circuiti Stampati

Attivita': Hidra2, Dune,

Temi: SiPM, FPGA, rigido-flex, geometrie inusuali, alto numero di canali compatti

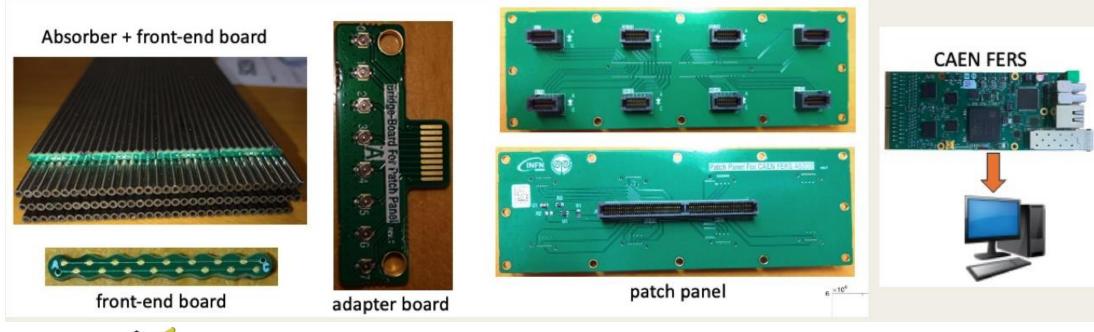

#### Hidra2

Prototipo calorimetro dual-readout

Bologna: schede readout FE, adattatore e patch-panel, sviluppo sistema di read-out con schede FERS di CAEN

#### Dune

• Abbiamo realizzato schede per i test dei SiPM in azoto liquido

- In previsione:

- o PCB Alcor 1k channel in LAr

- Elettronica digitale di Backend (Forse Xilinx Ultrascale+)

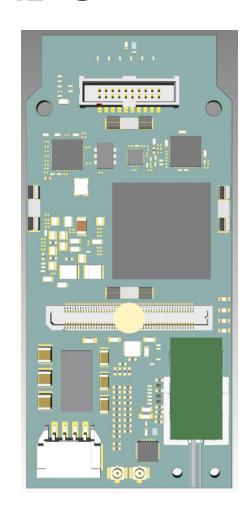

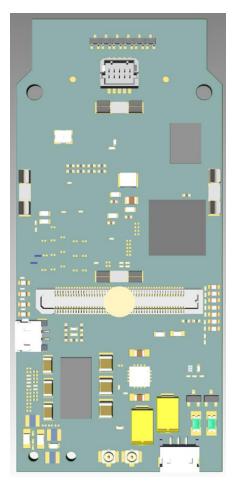

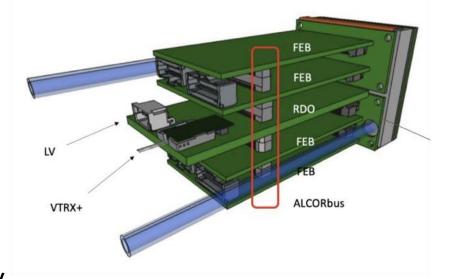

#### EPIC - Scheda RDO

Scheda di read-out per ePIC (EIC)

IN: 32 lanes di dati a 400

MHz (DDR)

OUT: VTRx+ (10 Gb/s)

FPGA AMD Artix Ultrascale+ (16 nm FinFET)

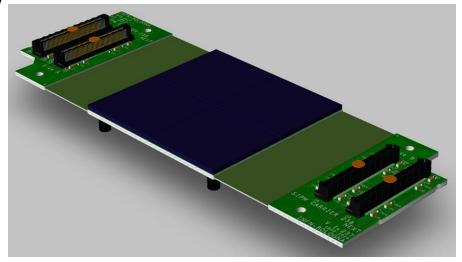

#### EPIC – photo detection unit

Bologna: Rigido flessibile Scheda SiPM carrier

Oltre che test, integrazione sensori e studi di radiation damage recovery (annealing)

# Timing

Attivita': Km3, Einstein Telescope, Virgo

Temi: DRD 7.3 timing distribution technology

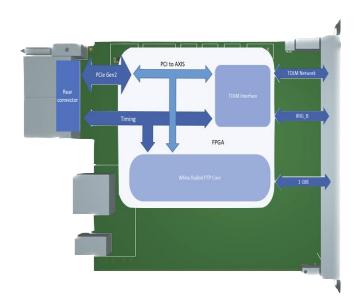

#### White Rabbit

- DAQ e timing system ufficiale in KM3

- Possibile upgrade per Virgo e interesse in Einstein Telescope

- INFN sta per diventare membro della WR collaboration

2x SPEC

1 Server dedicated to White Rabbit (WR) and DAQ

# Convertitori analogico-digitali

Attivita': Atlas, Alice

Temi: FPGA, link veloci, alto numero di canali compatti

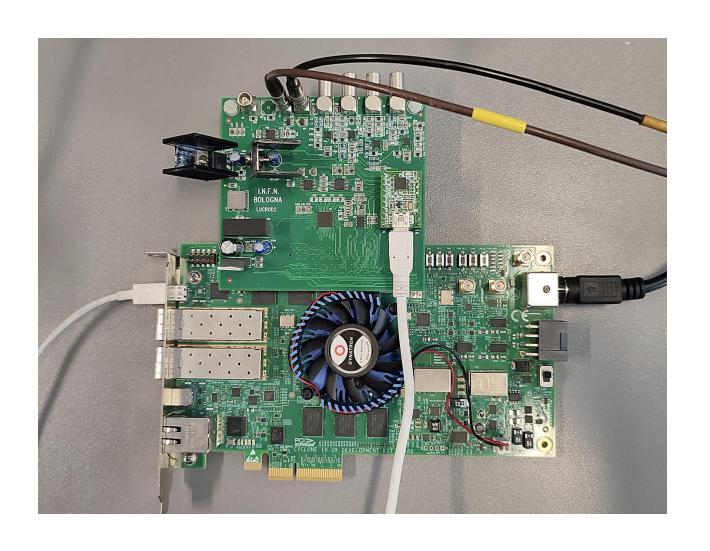

#### Atlas - Lucid

Prototipo per la validazione

ADC (un canale a 12 bit a 650 Msps), amplificatori e

DAC, per la scheda

Lucrod2 per Atlas-Lucid

(collegato ad una demo board della FPGA Intel

Cyclone 10GX - 10 nm)

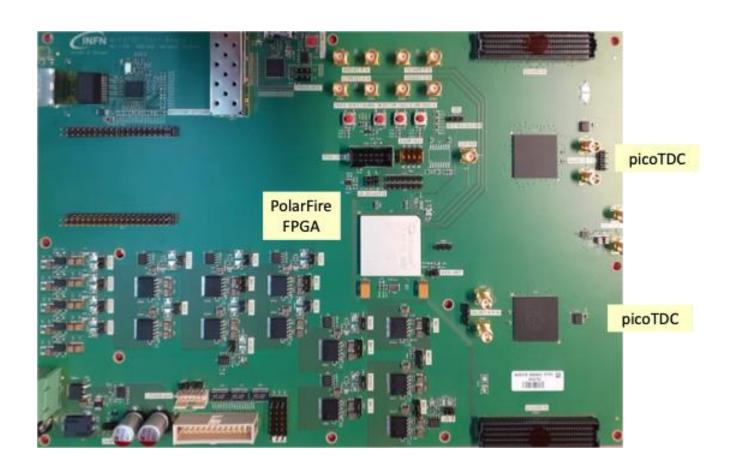

#### **ALICE**

Scheda per la lettura di due ASIC CERN picoTDC (65 nm, 3 ps resolution) tramite FPGA "nonvolatile" Microchip PolarFire per ALICE TOF

#### Al con FPGA

Tecniche Di Machine Learning Con Dispositivi FPGA per Gli Esperimenti Di Fisica Delle Particelle

2–4 Nov 2022 Infn

Europe/Formulimexxxx

Enter your search term

Q

#### Overview

Scientific Programme

Timetable

Contribution List

Author List

My Conference

My Contributions

Registration

Participant List

#### Resume'

- Microelettronica

- IP block development in tech up to 28 nm (DRD7 7.3a)

- DRD 7.6 (idea continuazione Arcadia, pixel chip monolitici

- Verification

- Link digitali veloci

- FPGA

- Elettronica per SiPM

- o Aspides (digital SipM) DRD4.1

- o Integrazione sensori

- Radiation studies (annealing, ....)

- Circuiti stampati:

- o Rigido-flessibile

- o Geometrie inisuali

- o Alta densita' (canali, potenza, banda)

- Radiation Hardness

- Timing

- DRD 7.3 timing distribution tech (interesse come observer)

- White rabbit

- Conversione analogica digitale

- o Alti rate di campionamento

- o TDC al ps

# Di cosa avrebbe bisogno un laboratorio di elettronica INFN per affrontare le sfide dello sviluppo e R&D di tali tecnologie? (½)

- Problema: limitato numero di persone nelle attivita'di microelettronica

- o Proposta: sottogruppo (trasversale agli esperimenti) più nutrito che fa microelettronica (come formarlo?)

- Prob: poco tempo per approfondire nuove tecnologie aggiornamento;

- o proposta: se si vuole investire su sviluppi elettronici visto che i commitment negli esperimenti sono già alti e pressanti si dovrebbe pensare ad aumentare il personale, tecnico e tecnologo

- Importante avere dottorandi e laureandi in laboratorio. Prob: pochi giovani in laboratorio forse perche' pubblicano meno e piu' in la nel tempo, gruppo 5 vengono in pochi a lavorare.

- Proposta: più giovani in gruppo 1 che lavorano su HW e che sia riconosciuto come altre attività per la loro carriera, rendere appetibile lavoro tecnologico per giovani fisici, esempio noi "staff" elettronici-fisici avevamo alle spalle esperimenti grandi

- Prob: laboratorio di elettronica poco conosciuto tra gli studenti.

- Proposta: per sviluppi tecnologici importanti e lunghi nel tempo i gruppi devono investire giovani a supporto delle attività del laboratorio (es: se gruppo vuole fare scheda con FPGA che va nell'esperimento e richiede manutenzione/supporto per anni, deve investire su giovani che il servizio può formare)

Di cosa avrebbe bisogno un laboratorio di elettronica INFN per affrontare le sfide dello sviluppo e R&D di tali tecnologie? (2/2)

- Problema: pochi ingegneri giovani

- Proposta: diventare appetibili per giovani ingegneri (da capire come...)

- Strumentazione problema: molti strumenti per tecnologie spinte sono molto costosi , potrebbero essere investimenti a livello di sezione

- o proposta: pensare a strategia di richiesta/finanziamento multi-esperimento (uno lo compera, lo gestisce il lab ed e'per tutti, oppure gli esperimenti uniti lo chiedono alla commissione; passare dalla sezione/direttore?)

- Prob.: parte eccessiva del tempo lavoro del personale tecnico/tecnologo altamente specializzato impiegato per ordini e acquisti dove ormai il 90% dei compiti non prevedono conoscenze specialistiche

- Proposta: potenziare personale "amministrativo" con ruoli di "punto istruttore" (mepa, acquisto su convenzioni e a catalogo)

## Grazie

Commenti? Integrazioni?