# ePIC TOF barrel demonstrator

Dr. Simone M. Mazza (UCSC) for the SCIPP group

Dr. Simone M. Mazza - University of California Santa Cruz

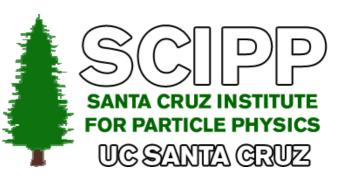

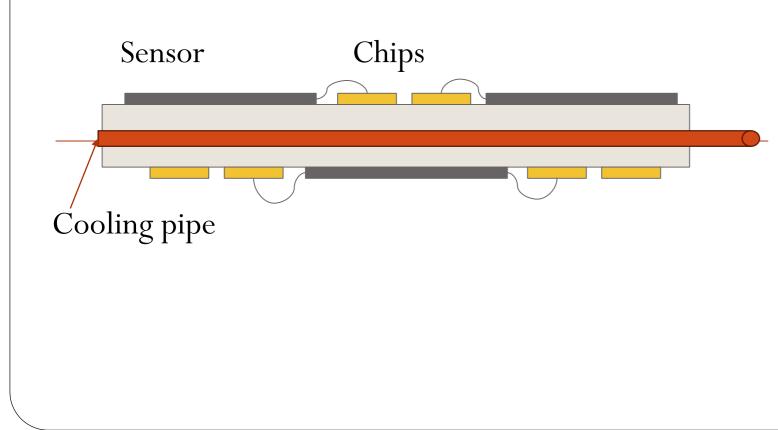

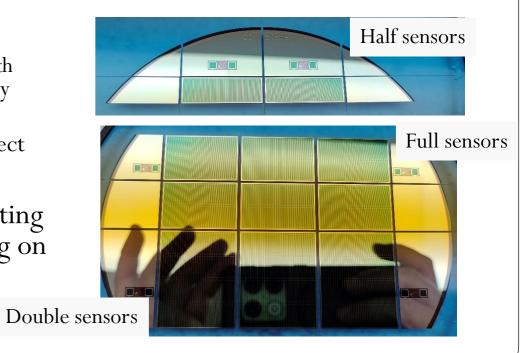

# Double-sided design

- "Original": 2 ASIC per sensor originally, now 1 ASIC per sensor

- 1 ASIC service two half sensor

## **Demonstrator project**

- Goal: build a thermo-mechanical stave demonstrator to:

- Test assembly procedure

- Test thermal proprieties of the stave, e.g. temperature gradient

- Project flow:

- Purdue and ORNL will fabricate two half staves co-cured with Flex

- UCSC will glue, verify positioning (metrology) and wirebond sensors (HPK new production) and silicon heaters (<u>https://www.topline.tv/PST.html</u>).

- Heathers (1x1cm) have embedded temperature sensor and a series of bond pads to be paired with sensor.

- Purdue or ORNL will assemble the two half staves with cooling pipe

- UCSC will perform electric and thermal tests with a custom setup to be built (dry box with connection). The component will be controlled by a board to be designed by UCSC (mostly Arduino or RasPi)

- HPK sensors arrived at UCSC, many are NOT working, so ok to be used in this project

- Envisioned size:

- 4 sensors + 1 half sensor, or longer (6+1 sensors) to match the existing mini-staves that are being produced by the Purdue group (depending on the availability of sensors).

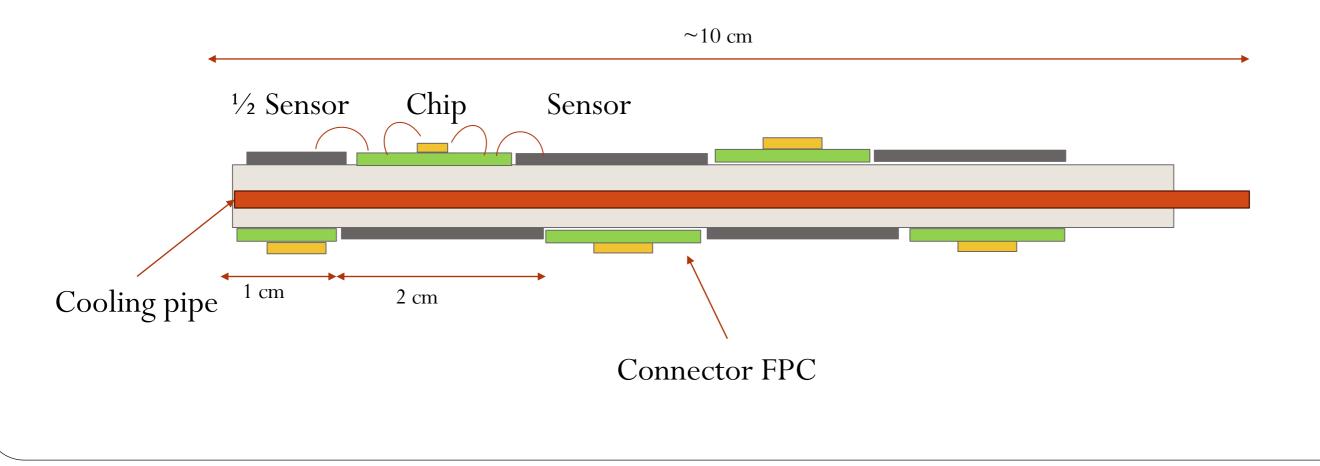

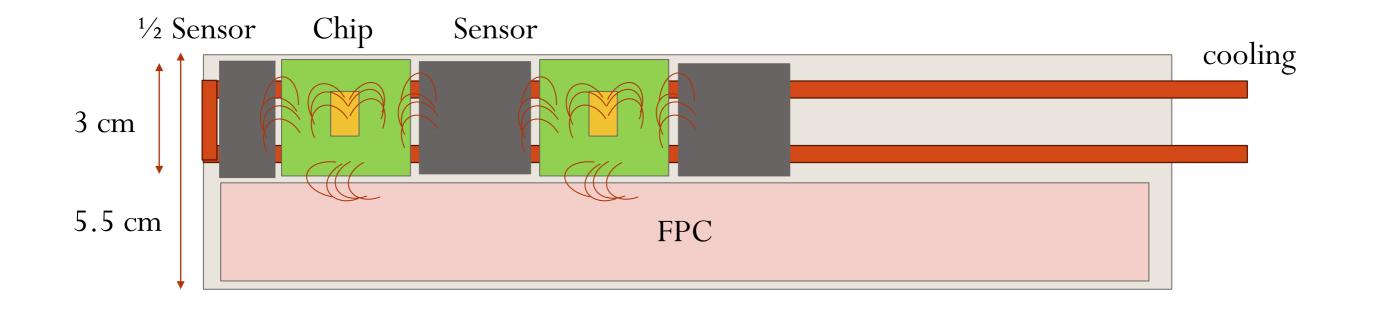

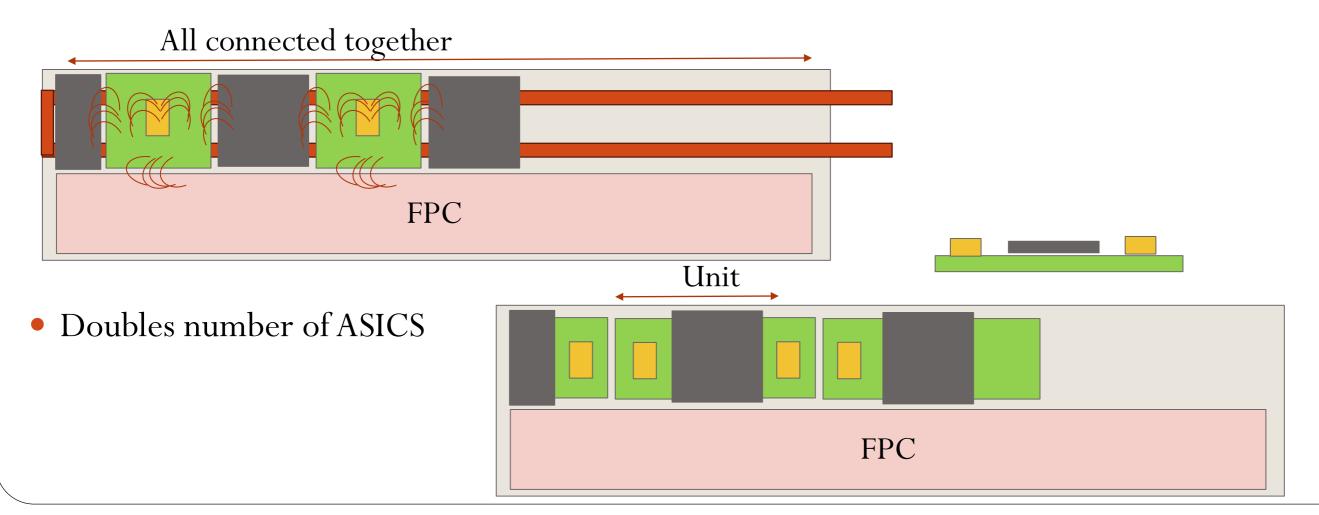

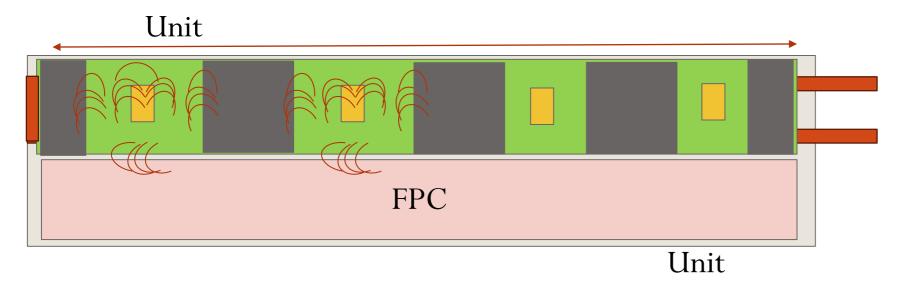

## Double-sided design

- Since last discussion two changes:

- 1 chip between two sensors

- "Connector" board to match sensor/chip pitches, sensor and chip wire bonded to it and the connector is wire bonded to the FPC

- Since last discussion two changes:

- 1 chip between two sensors

- "Connector" board to match sensor/chip pitches, sensor and chip wire bonded to it and the connector is wire bonded to the FPC

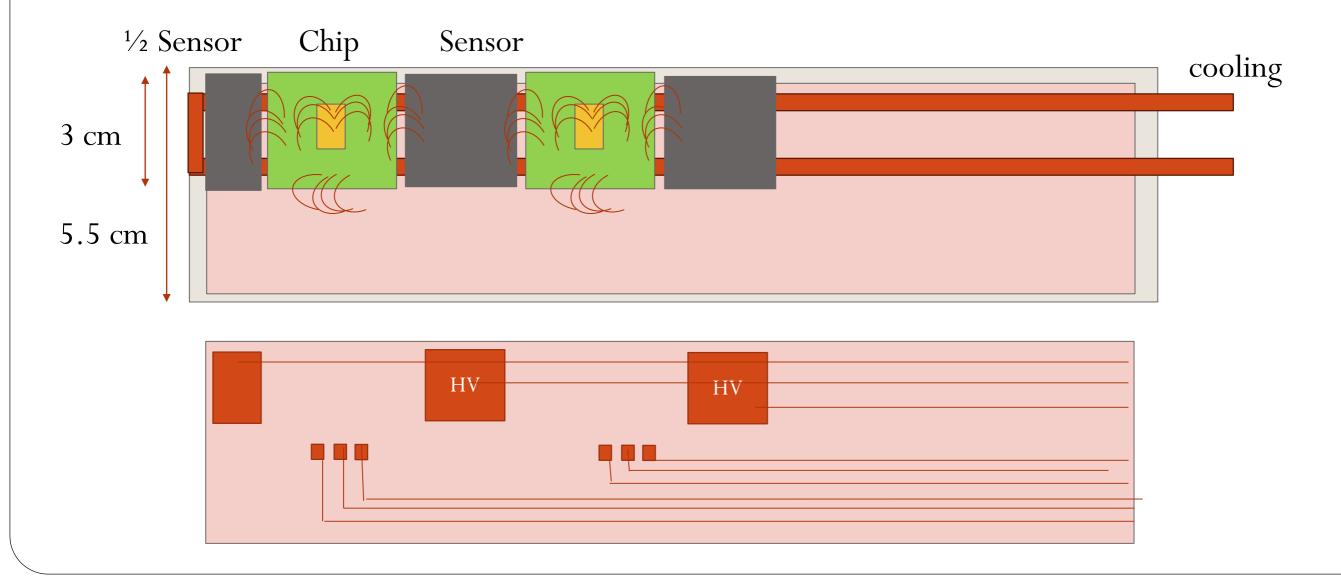

- FBC carries traces, likely multi-layer but for demo can be simple

- Wide as the stave, carrying HV under sensors/chips

- Issue with long stave with this design: it's all stitched together as a single piece

- Hard for fabrication!

- Better if we split it in 'units' that are assembled and then mounted on FPC

- Issue with small units: doubles the number of ASIC

- I we do large units with half-sensors at the edges the number of ASICs would stay the same and it can be assembled 'stand-alone'

- Demonstrator can be one unit length ~16cm

- Same number of ASIC but introduces small 'gaps' (~1mm) between units

- Other stave side will have an ASIC in that position