# WP3 Electrical Interfaces

20250124

M.Borri

on behalf of WP3

# **Outline**

- WP3 general updates

- Update on Inner barrel

- Update on Outer Barrel

- Update on Disks

- Conclusion

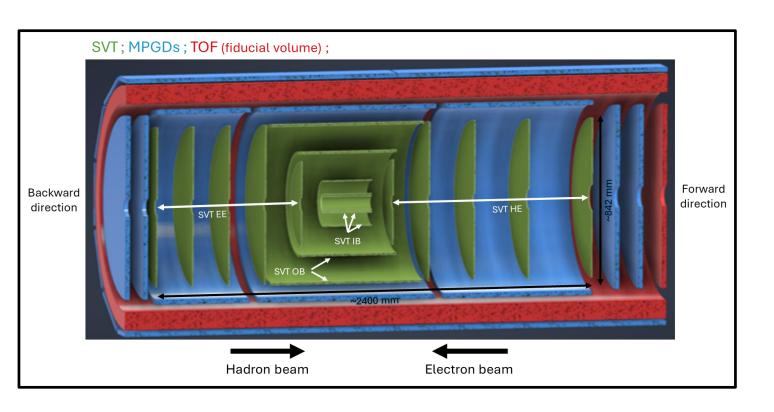

# **General updates 1**

Zhenyu Ye appointed as co-coordinator

Monthly meetings since 05/2024

IT: Trieste

US: BNL, LANL, LBNL

UK: DL, Oxford

UA: LTU

WP3: Electrical Interfaces

Coordinators: Marcello Borri, TBC

✓ Zhenyu Ye (LBNL)

V1.7

| WP3: Ele | ctrical Interfaces                                                                      |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------|--|--|--|--|

| 3.1      | Electrical interfaces IB (L0-2)                                                         |  |  |  |  |

| 3.1.1    | Definition of specifications for FPCs & electrical interconnection                      |  |  |  |  |

| 3.1.2    | Design & supplier evaluation                                                            |  |  |  |  |

| 3.1.3    | Prototyping & testing of module, FPCs & electrical interconnection                      |  |  |  |  |

| 3.1.4    | Iterative improvements of FPC design & electrical interconnection                       |  |  |  |  |

| 3.1.5    | FPC design complete & electrical interconnection validated                              |  |  |  |  |

| 3.1.6    | Pre-production of FPCs for system test, including QC                                    |  |  |  |  |

| 3.1.7    | Production of FPCs for production detector, including QC                                |  |  |  |  |

| 3.2      | OB HIC (L3-4)                                                                           |  |  |  |  |

| 3.2.1    | Definition of specifications for module, FPCs & electrical interconnection              |  |  |  |  |

| 3.2.2    | Design & supplier evaluation                                                            |  |  |  |  |

| 3.2.3    | Prototyping & testing of module, FPCs & electrical interconnection                      |  |  |  |  |

| 3.2.4    | Iterative improvements of module design, FPC & electrical interconnection               |  |  |  |  |

| 3.2.5    | OB module design complete                                                               |  |  |  |  |

| 3.2.6    | Pre-production of FPC for system test, including QC                                     |  |  |  |  |

| 3.2.7    | Production of FPCs for detector grade modules, including QC                             |  |  |  |  |

| 3.3      | Disks HIC (ED0-4, HD0-4)                                                                |  |  |  |  |

| 3.3.1    | Definition of specifications for module, FPCs & electrical interconnection & back plate |  |  |  |  |

| 3.3.2    | Design & supplier evaluation                                                            |  |  |  |  |

| 3.3.3    | Prototyping & testing of module, FPC, electrical interconnection & back<br>plate        |  |  |  |  |

| 3.3.4    | Iterative improvements of module design, FPC, electrical interconnection & back plate   |  |  |  |  |

| 3.3.5    | Disk module design complete                                                             |  |  |  |  |

| 3.3.6    | Pre-production of FPCs for system test, including QC                                    |  |  |  |  |

| 3.3.7    | Production of detector grade FPCs, including QC                                         |  |  |  |  |

marcello.borri@stfc.ac.uk

# **General updates 2**

- WP3 contribution to PDR:

- Part of Chap.8, Experimental Systems:

- Complete

- Appendix:

- in progress

|       | lectron Ion Collider        | DRAFT                       |

|-------|-----------------------------|-----------------------------|

| Pro   | iminary Design Report       | EIC PDR<br>December 9, 2024 |

| 8.3.3 | racking                     | 59                          |

|       | .3.3.1 The silicon trackers | 62                          |

|       | Requirements                |                             |

|       | Justification               | 64                          |

|       | Implementation              |                             |

| 4 | Modules |                                              |    |  |  |  |

|---|---------|----------------------------------------------|----|--|--|--|

|   | 4.1     | Overview                                     | 11 |  |  |  |

|   | 4.2     | OB module concept                            |    |  |  |  |

|   |         | 4.2.1 Tooling and assembly                   | 11 |  |  |  |

|   | 4.3     | Disks module concept                         | 11 |  |  |  |

|   |         | 4.3.1 Tooling and assembly                   | 11 |  |  |  |

|   | 4.4     | Characterization and production testing (QC) |    |  |  |  |

|   | 4.5     | Prototype studies                            | 12 |  |  |  |

| 5 | Ele     | ctrical interfaces                           | 13 |  |  |  |

|   | 5.1     | Overview and specifications                  | 13 |  |  |  |

|   | 5.2     | FPC design                                   | 13 |  |  |  |

|   | 5.3     | Technology selection                         | 13 |  |  |  |

|   | 5.4     | FPC production and QC                        |    |  |  |  |

|   | 5.5     |                                              |    |  |  |  |

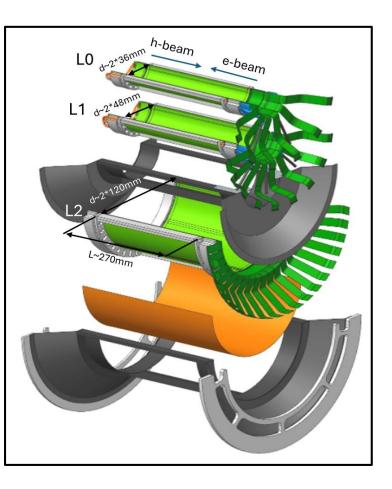

# Inner barrel

# **Overview**

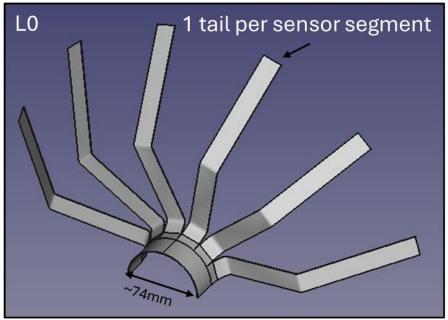

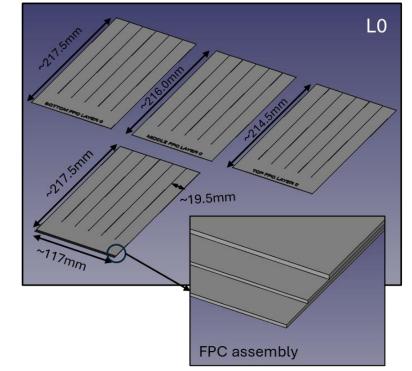

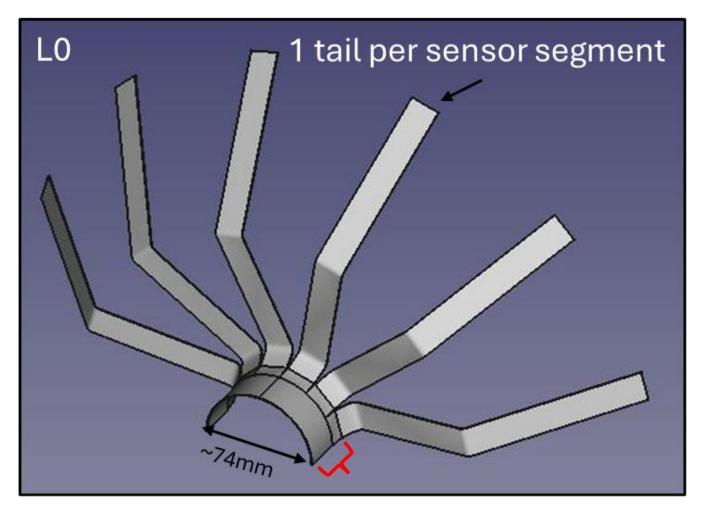

- Initial activity on the Forward-side FPCs:

- Mainly L0&L1;

- IB FPCs (forward-side):

- Assembly of 3 FPCs (2 layers each);

- FPC length ~ 22cm;

- 1 tail per sensor segment;

- Design of mechanical mock-ups the L0&L1 FPC;

- STP files provided by INFN Padova;

- Ported into Allegro;

- Reviewed, and now waiting for final approval from INFN Padova.

- Then procure in Cu technology (cheaper faster)

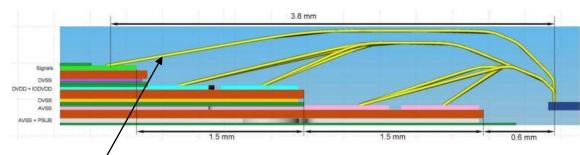

# Forward side: detail

Inactive region for SVT, but **active region** for EPIC.

To keep material budget low.

## Furter details from ITS3 TDR

## Wire-bonds profile

The longest wire bonds include high speed data (up to 10Gb/s)

Note:

ALICE ITS3 originally planned to manufacture this FPCs in Cu technology, now planning to do it Al technology?

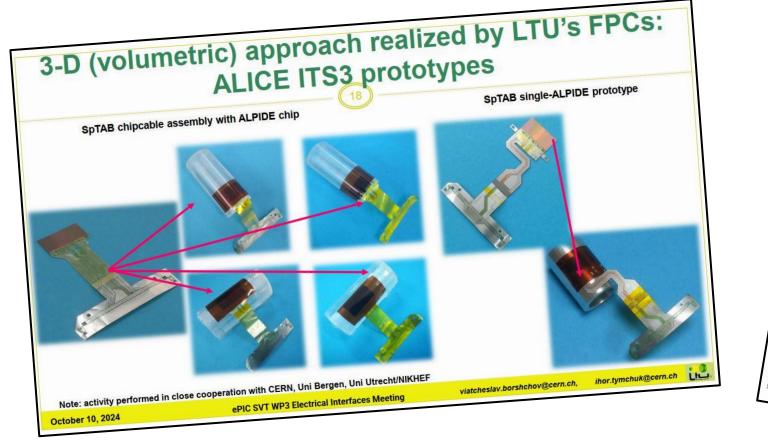

# LTU contribution to ITS3

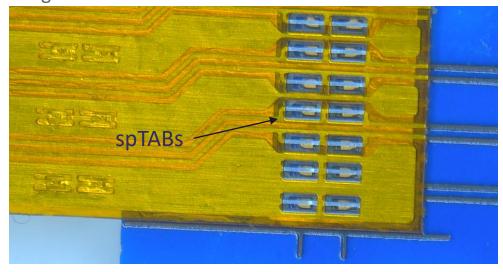

## 4.8.3 Fall-back options Sp-TAB technique

The Single-point Tape Automated Bonding (SpTAB) technique has been considered as an al-The Single-point Tape Automated Bonding (SpTAB) technique has been considered as an alternative option to interconnect the ITS3. The main features of this technique and approach

- adhesiveless aluminum-polyimide thin single-layered and multi-layered flexible printed cir-

- amesiveless aummun-polyminge ruin single-layered and multi-layered nexible print cuits to interconnect the chip to the external data and power transmission buses, conductive aluminum layer thicknesses ranging from 15 to 100 μm to realize low-mass

- SpTAB direct connections of ribbon aluminium leads to chip pads providing uniform, welded joint encapsulation after SpTAB;

- possibility to perform quick repair weld joints during manufacture of the pixel module;

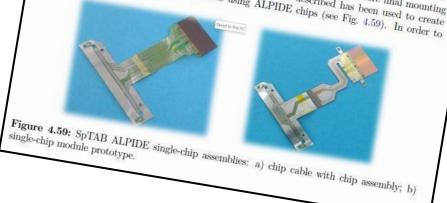

• possibility of using standard industrial automated equipment for basic assembly processes The SpTAB technique allows interconnection of the curved chip to the flexible circuit as well The Sp1AB technique allows interconnection of the curved crip to the nexible circuit as well as for bending the pre-interconnected assembly. Using thin single layered circuits for sensor-toas for bending the pre-interconnected assembly. Using tim single layered circuits for sensor-to-bus interconnections allows electrical functional testing to be performed before final mounting bus interconnections allows electrical functional testing to be performed before final mounting on support structures or further assembly. The approach described has been used to create on support structures or nurther assembly. The approach described has been used to create and characterise single-chip test assemblies using ALPIDE chips (see Fig. 4.59). In order to

LTU presented at the WP3 meeting their idea for FPCs proposed for the ALICE ITS3

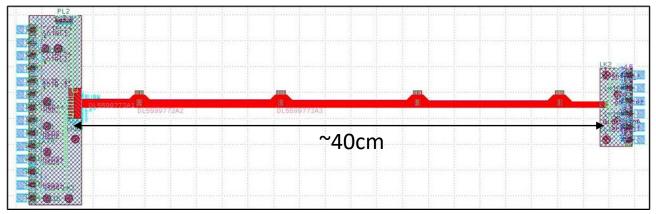

# **Testing FPCs for IB**

Planning to send to INFN Trieste a stand-alone M-FPC & interface cards.

INFN Trieste will test signal propagation as a function of bending radii.

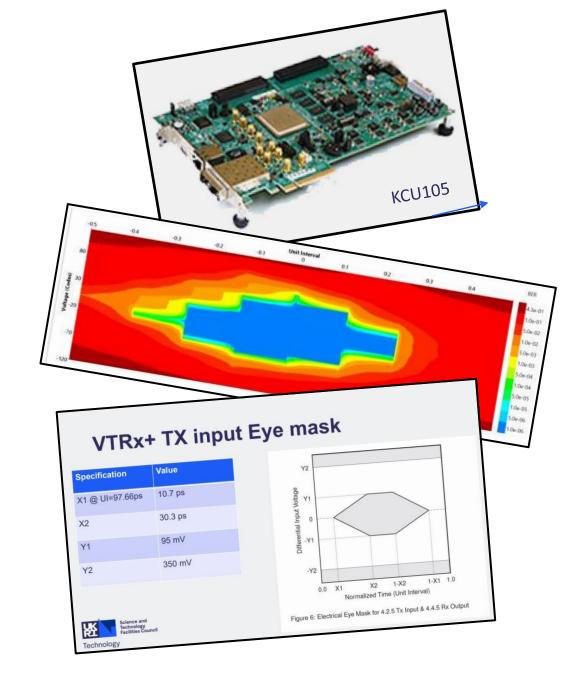

To procure ad-hoc FPGA development board to perform these tests.

## Sketch of the main FPC (M-FPC) to interconnected to interface cards

# **Next steps:**

To clarify/define a target supplier: LTU(baseline) or CERN?

To design an FPC with representative length to test signal propagation with selected supplier;

To practice interconnection related to selected supplier;

# Outer barrel

# Low TRL OB L4 prototypes: time-line

- Defined requirements:

- **18/03/2024**

- Design review:

- **1**6/05/2024

- Prototypes delivery:

- **08/10/2024**

- Testing:

- To assemble to interface cards;

- To distribute and test;

Issue so far:

1.3. For each order of Goods within this contract a Quotation needs to be sent by the Seller to the Buye

and then a Purchase Order needs to be sent by the Buyer to the Seller as a confirmation of quotatio

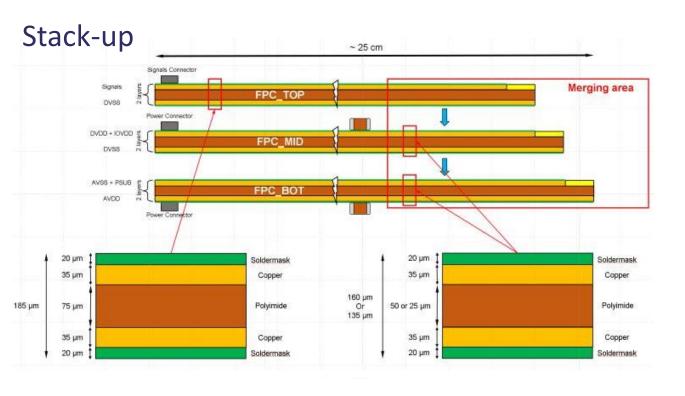

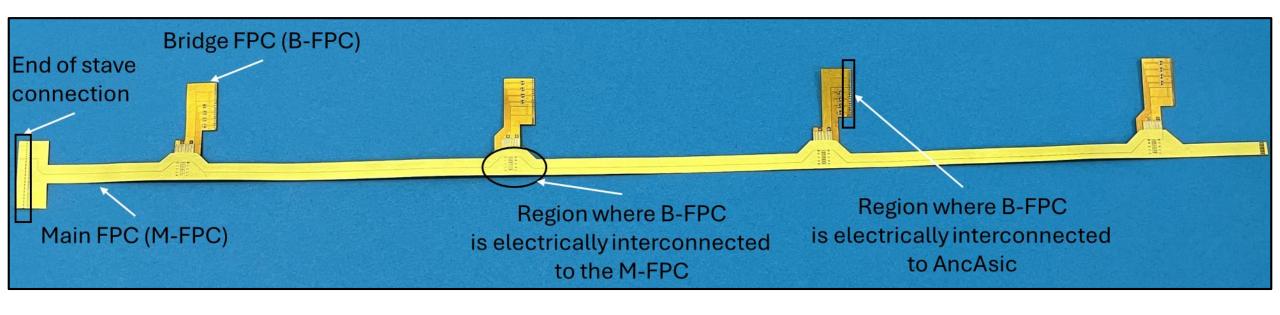

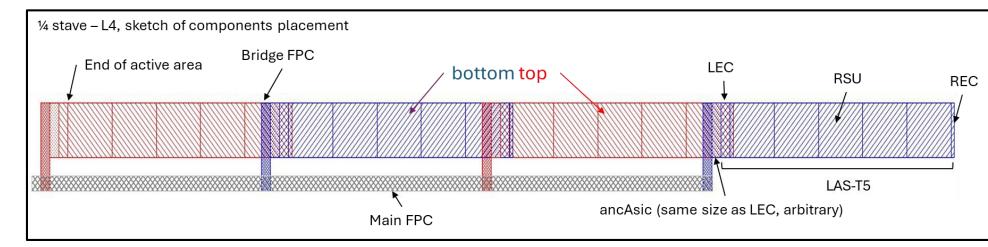

# Design recap 1

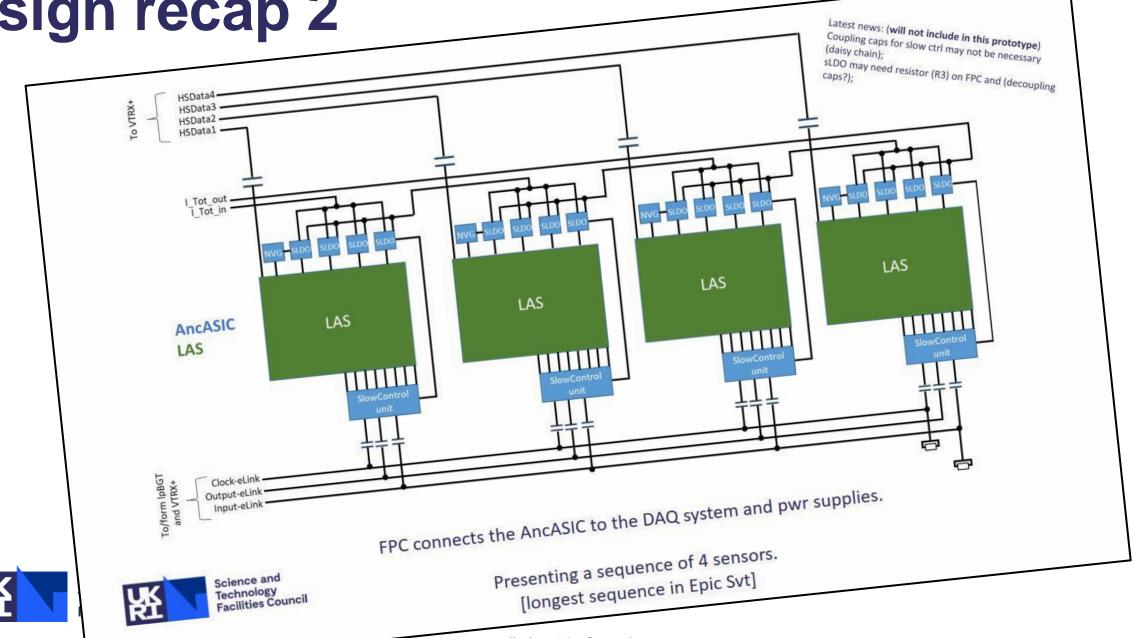

# Design recap 2

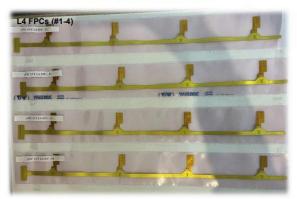

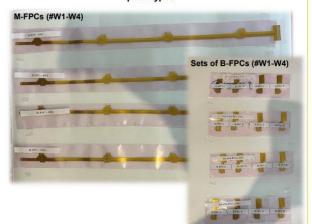

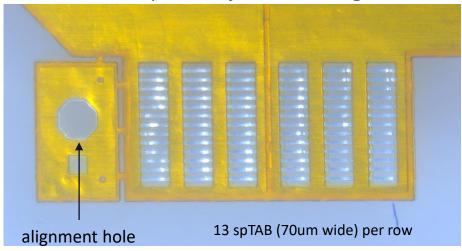

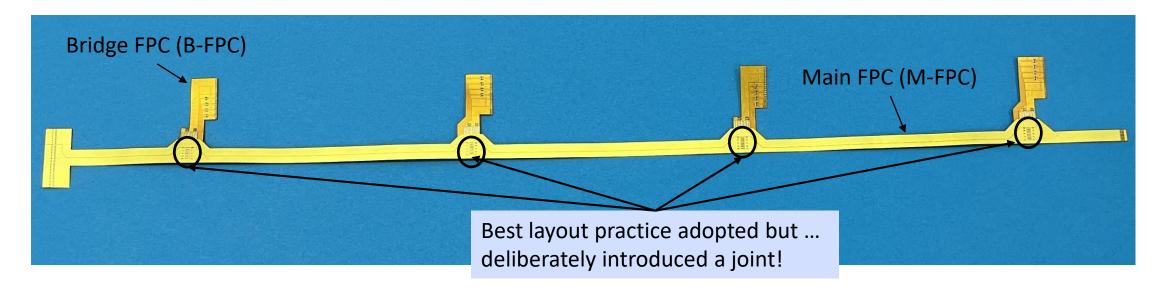

# Low TRL OB L4 prototypes: LTU delivery

## **ePIC SVT L4 FPC prototypes** and sets of FPCs shipped to STFC DIL

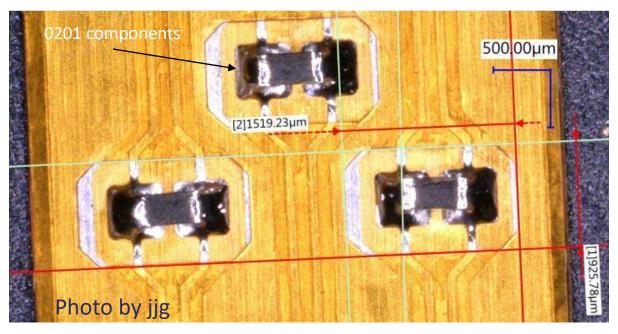

Assembled multilayered multicomponent ePIC SVT L4 FPC prototypes

Sets FPCs for ePIC SVT L4 FPC prototypes

- 4 prototypes of assembled ePIC SVT-L4 FPC

- 4 sets of FPC prototypes for ePIC SVT-L4 FPCs (4 M-FPCs+ 16 B-FPCs)

October 10, 2024 ePIC SVT WP3 Electrical Interfaces Meeting viatcheslav.borshchov@cern.ch, ihor.tymchuk@cern.ch

Note: all FPCs are packed in ESD protective film packages

Science and Technology **Facilities Council**  A lot of details in the design...

## I.Tymchuk:

30 masks in total were required for M-FPC & B-FPC-A & B-FPC-B;

i.e. 10 photomasks for each FPC were required;

(usually a 2 layer FPC requires up to 6 masks)

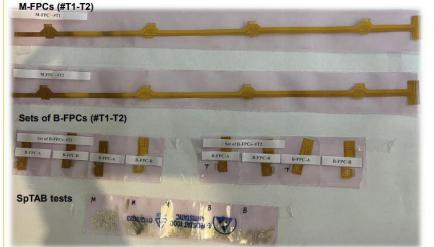

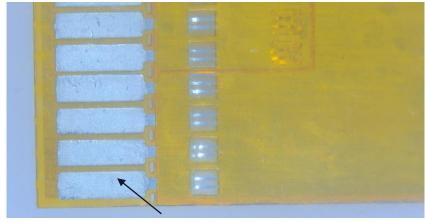

## Additional (test) FPCs shipped to STFC DIL

Additional Test FPCs delivered for SpTAB tunning, test procedure/fixture tunning etc.

#### Additionally delivered:

- ✓ M-FPC

- √ B-FPCs

- 2 sets (4x2 B-FPCs)

- 2pcs

√ SpTAB test elements – (~70pcs)

#### Important notes:

- ✓ M-FPC OK (only a bit imperfectness in interlayer aligning presents)

- ✓ B-FPCs 6 pcs are OK, only 2pcs are NOK (marked by letter T)

# Visual inspection 1

Alignment of FPC to interface PCB

Probe pads and perforated area

perforated area

Current in/out spTABs at joint with bridge FPC

marcello.borri@stfc.ac.uk

# Visual inspection 2

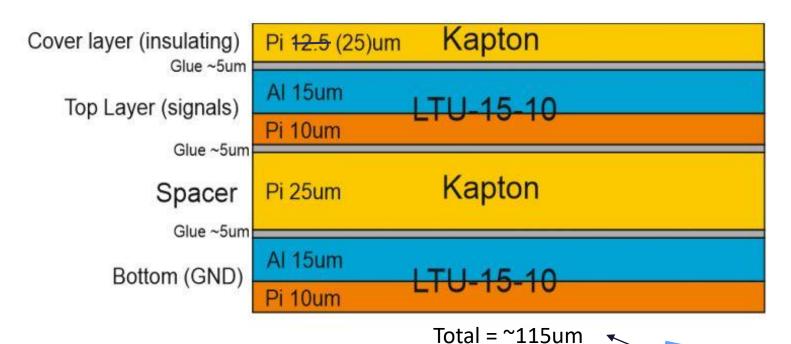

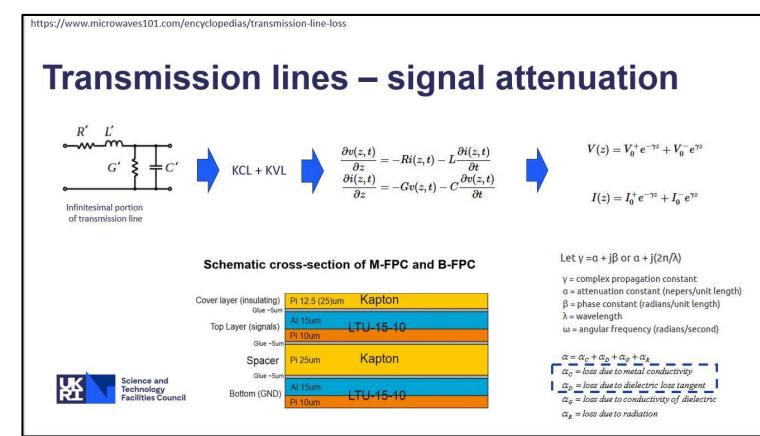

## Schematic cross-section of M-FPC and B-FPC

Difference ~3.6um

Measured 111.4um

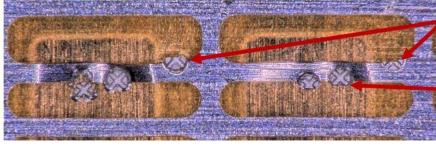

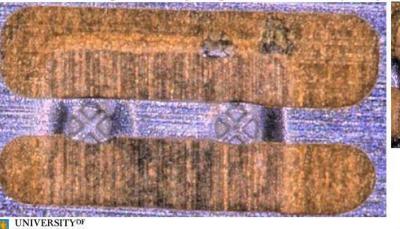

# **spTAB**

## Initial bonds

Bond machine was set up with the general 25 µm wire bonding settings:

Bondforce (BF): 20 cN Ultrasonic power (US): 20%

Deformation: 35 µm Duration: 70 ms

Initial bond position calibration needed work.

Uncentred due to Z-axis offset (movement of foil as it is pushed through the Kapton window).

UNIVERSITYOF BIRMINGHAM

06 January 2025

OB module: ad-hoc meeting

... components also sent to the University of Liverpool.

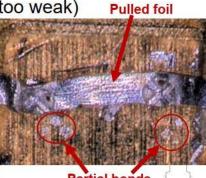

## SpTAB test element

Bonds look good, only slight foil breaks (likely too weak)

Partial bonds remained

UNIVERSITYOF BIRMINGHAM

06 January 2025

OB module: ad-hoc meeting

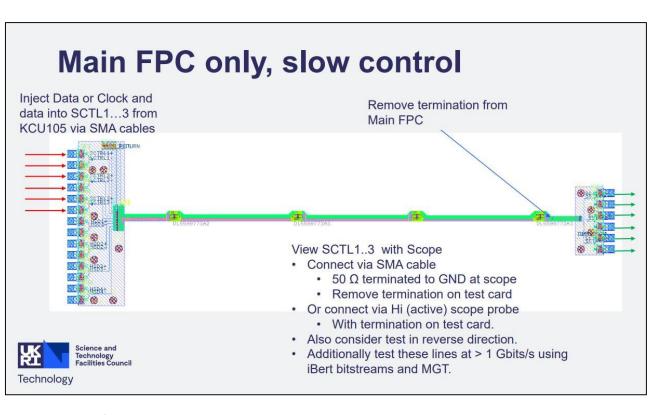

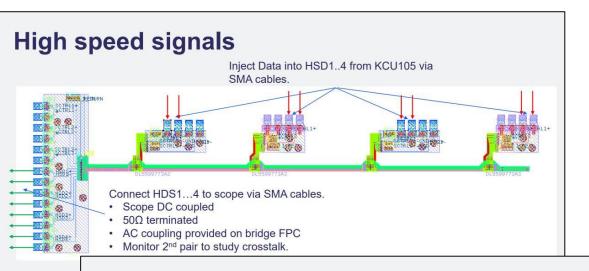

# Test plan 1

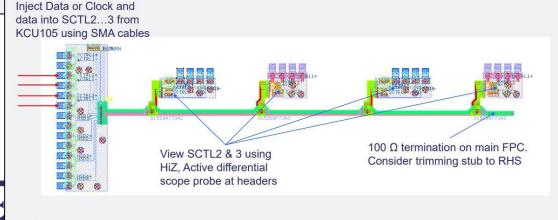

• Step 1: to test stand-alone M-FPC with interface cards

# Test plan 2

#### Clarity3d layout simulations of 100 mm pair Strategy: measure first, simulate after ++ ++ 1 to the total channel View ▼ S ▼ Amplitude ■ -0.076 dB at 10 MHz Diff - Diff ▼ B Sdiff0 - SIMULATION ▶ @ Mode Definitions ■ = 0.99 transmission SDD(1.11 - Sdiff(D1:Diff(Por SDDI2 21 - Sdiff(D2-Diff(Por expect 0.97 at DC SDD[1,2] - Sdiff(D1:Diff(Por. ■ -8.4 dB @ 10 GHz Predicted -4.23 SDCI1 21 - Sdiff/D1-Diff/Por SDC(2,11 - Sdiff(D2:Diff(Por. Explained by Comm - Diff different values of SDD[1.2] SDD[2,1] Clarity material: Df= solated Curves 0.035 @ 10 GHz Technology Technology

Technology

## Slow Control Clock and TX data SCTL2 & 3

## Equipment:

- Higher spec oscilloscopes & TDR available at RAL (accessed via Oxford)

- DL to rent similar equipment

### DUT:

Assembly of M-FPC & B-FPC is in progress

stfc.ac.uk

# What do we test for: signal and pwr integrity

- Signal integrity.

- The ability to propagate signals without distortions

- Factors that contribute to signal integrity degradation:

- Reflections

- Impedance discontinuities

- Cross talk

- Mutual parasitic capacitance & inductance

- Skew

- Propagation delays

- Jitter

- Non-uniform impedance, crosstalk, interference, and power supply noise

- Signal attenuation

- Losses caused by conductive and dielectric energy dissipation.

- Power integrity

- Reduced Noise pick up

- Decoupling capacitors (Equivalent Series Resistor)

- Coherent grounding strategy over the Power Distribution Network

- Acceptable IR drop (and related FPC power consumption)

# Signal integrity: layout dependent

The most important cause of signal integrity issues in a PCB is faster signal rise times.

| Signal name            | Туре | Comment                                     | Coupling   | Standard                          | lpGBT eLink  | Rate          |         |

|------------------------|------|---------------------------------------------|------------|-----------------------------------|--------------|---------------|---------|

| slow ctrl clk (down)   | AC   | from IpGBT to AncASIC                       | Capacitive | CERN Low Powering Signal (CLPS)   | clock-eLink  | 80 Mb/s       |         |

| slow ctrl write (down) | AC   | from IpGBT to AncASIC                       | Capacitive | CERN Low Powering Signal (CLPS)   | output-eLink | 80 Mb/s       |         |

| slow ctrl read (up)    | AC   | from AncAsic to IpGBT                       | Capacitive | CERN Low Powering Signal (CLPS)   | input-eLink  | 160 Mb/s      |         |

| data                   | AC   | from AncAsic to VTRX+ (1 diff line/AncASIC) | Capacitive | CERN Low Powering Signal (CLPS)   | N/A          | 5.12 Gb/s (or | 10Gb/s) |

| voltage supply         | DC   | Max: (2.5V/AncASIC) * (4 AncASIC)           | Direct     | 10% Vdrop for 2.5V/LAS, is it OK? | N/A          | N/A           |         |

| current                | DC   | 2.5 A (total per AnASIC)                    | Direct     |                                   | N/A          | N/A           |         |

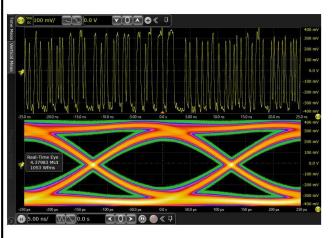

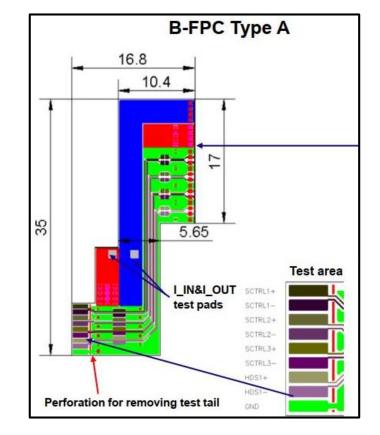

# **Q-flex**

LANL ordered a copy of the B-FPC (type A) via Q-flex.

To be delivered;

Q-flex compromised on several features of the original design:

- mounting of passive components;

- surface finish;

- differential tracks impedance changed to 150 Ohm;

Test setup: available

## Results from 4Gbps PRBS generate by KC705

|                | 12um polyimide    | Top Coverlay                 |  |

|----------------|-------------------|------------------------------|--|

|                | 25um adhesive     |                              |  |

|                | L1 17um Aluminium |                              |  |

|                | 12um adhesive     | 0.7mil Aluminium with Kapton |  |

|                | 12um Polyimide    |                              |  |

|                | 25um adhesive     |                              |  |

|                | 25um polyimide    | Bondply                      |  |

|                | 25um adhesive     |                              |  |

|                | 12um Polyimide    |                              |  |

|                | 12um adhesive     | 0.7mil Aluminium with Kapton |  |

|                | L2 17um Aluminium |                              |  |

|                | 25um adhesive     | Battana Cavanlau             |  |

|                | 12um polyimide    | Bottom Coverlay              |  |

| Flex Thickness | ~233um +/-10%     |                              |  |

ello.borri@stfc.ac.uk

# **Next steps**

- To start ASAP the electrical characterization of Low TRL OB L4 prototypes;

- To perform comparative interconnection test between wire-bonding and spTAB bonding via ad-hoc daisy chain structures from LTU;

- To complete evaluation of Q-flex;

- Design the next iteration of OB prototypes, in progress (linked to module design).

# **OB** module

# OB module electrical test

Jian Liu (University of Liverpool) 6 January 2025

## OB module: development increments and planning horizon

20241204 M.Borri, M.Buckland, K.Davis

James Glover & Eve Tse

UNIVERSITYOF BIRMINGHAM

ePIC SVT FPC,

ancillary ASIC placement, and bonding

Ken Davies

Mechanical Design Engineer

PME Group, Technology Department

STFC Daresbury Laboratory

3<sup>rd</sup> December 2024

OB module: ad-hoc mee...

marcello.borri@stfc.ac. James Julian Glover (University of Birmingham (UK)), Marcello Borri (staff@stfc.ac.uk)

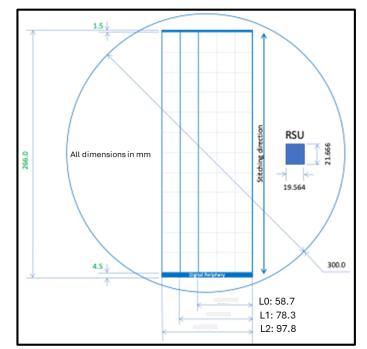

# Disks

# Overview

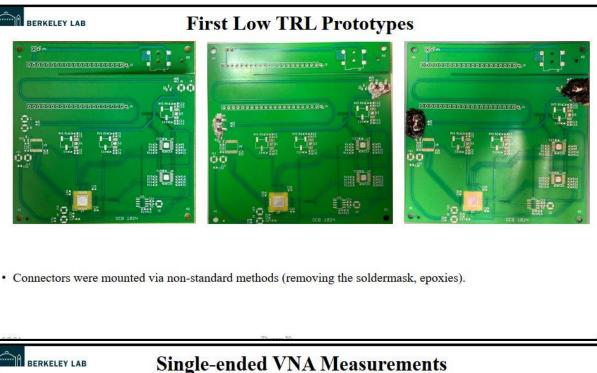

LBNL progressing prototyping with Omni Circuit Boards (CA);

Two iterations completed with supplier;

A third iteration under development;

# 1st iteration

• Maximum load: 11.570 g

• Standard Deviation: 1.2471 g

• Mean: 9.5195 g

- Design based on a PCB from another project;

- Pads were OK for wire-bonding, not for soldering

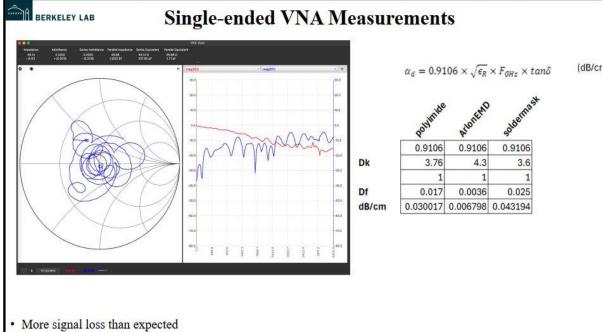

- Significant signal loss was measured

# BERKELEY LAB Wire-bonding and Pull Tests Number of tests: 39 Mean - 3 \* standard deviation: 5.7782 g Minimum load: 6.9011 g

Zhenyu Ye

## Al-based FPC (Yuan Mei)

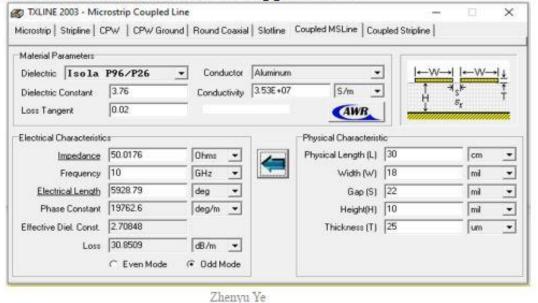

## Constraints from vendor

- Prefer 1mil thick Polyimide-fiber glass substrate (Isola);

- Prefer 20μm Al 8μm Cu Polyimide stack. Can be without Cu, but Al Polyimide adhesion is weak.

- Prefer burying traces between substrates for added strength. 5mil/5mil width/spacing in small area, 7mil/7mil for long traces.

- Not support SMD soldering. Al in a few small places can be plated with 5μm copper for solder.

- 0.016" wide (minimum) cutout. Plated vias must be copper based.

5/9/24

3

## 2nd iteration

- Dedicated to signal transmission investigation:

- understand and improve signal losses: different substrate materials, different width/pitch, with and without soldering mask;

- Use of selective Cu plating for soldering

- Make plated-thru holes in an all-aluminium stack

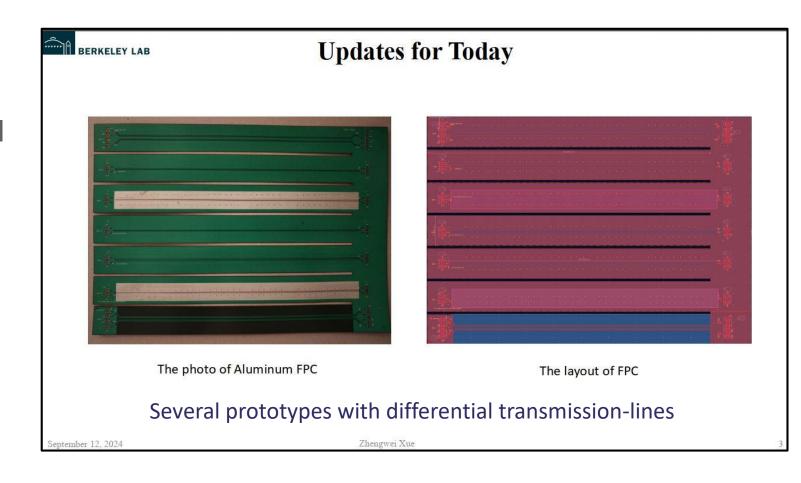

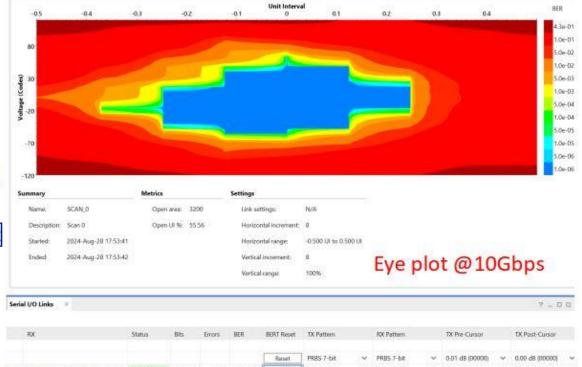

## **Updates for Today**

- · Received a 2nd set of Al-based FPC prototypes from OMNI.

- Double metal layer with 25 cm long differential lines for high-speed data transmission

- Improvements compared to the previous set

- · Soldering and vias facilitated by selective Cu plating

- Improved high frequency signal transmission property based on S21 measured up to 4 GHz

- IBERT test done with FPGA suggests that these FPC support GTY communication @10Gbps

- · Questions to follow up:

- Check the mechanical properties of the FPC

- 2 out of 36 connector pads detached from the FPC when disconnecting the cable

- Total material budget of the FPC is 0.136% X<sub>0</sub> (TBC), with dominant contribution from dielectrics. Can this be reduced

- · Plan:

- Manufacture FPC based on LTU/STFC design but modified to be consistent with vendor's design rules if there is no objection.

\*Dielectric substrate is ArlonEmd

September 12, 2024 Zhengwei Xue

## **Updates for Today**

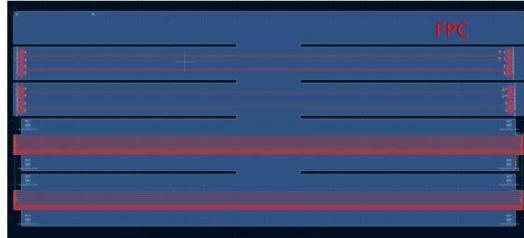

- The 3<sup>rd</sup> set of FPC is still under design:

- Discussing with OMNI about the plan to optimize material budget (in progress);

- Two strips have interface pins that share the same structure as the LTU/STFC design;

- Corresponding interface board;

- Two strips are used to test the effect of AC coupling on the signal;

- One strip for the physical property test;

- No spTAB bonding;

- Minimum trace width/distance is 6/6 mil.

(150/150 µm)

- · Plan:

- Manufacture FPC and interface board as soon as we confirm the material budget optimization plan.

# Conclusion

# Conclusion

Prototyping of FPCs for IB, OB and disks in progress.

WP3 community active and engaged.

Key questions to data transmission Vs fabrication technologies to be fully assessed.

# Thank you