### MOSAIX & EIC-LAS Modifications

ePIC Collaboration Meeting 20-24 Jan. 2025

João de Melo - BNL jmelo@bnl.gov

January 21, 2025

MOSAIX / EIC-LAS

### Outline

□ Monolithic Stitched Sensor (ER1 Submission )

Introduction

#### □ MOSAIX (ER2 Submission)

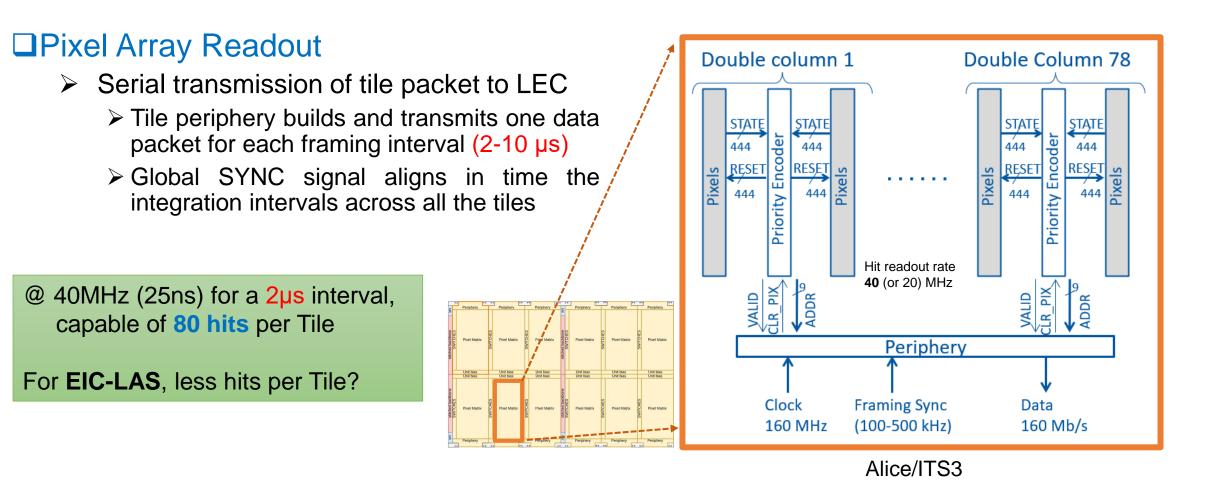

- Architecture (Alice/ITS3 upgrade)

- Design Status

#### □ MOSAIX to EIC-LAS

- Modifications

- Timeline & Resources

- Further Improvements!?

### Introduction

- Chip size is traditionally limited by CMOS manufacturing ("reticle size")

- Typical sizes of few cm<sup>2</sup>

- modules are tiled with chips connected to a flexible printed circuit board

Principle of photolithography

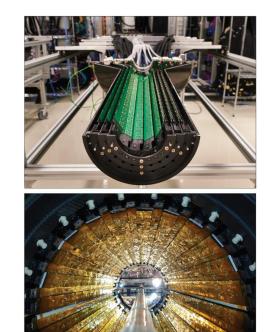

Alice/ITS2

#### □Wafer-scale sensors: stitching

- New option: stitching, i.e. aligned exposures of a reticle to produce larger circuits

- wafer-size chip

**Motivation**: Reduction of the material budget

**Challenges:** Power supply, cooling, and design/yield

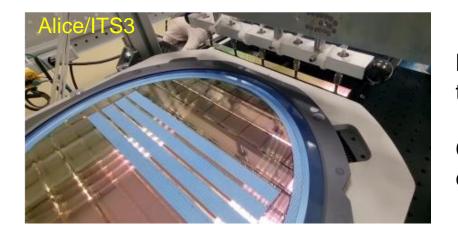

### **ER1** Submission

Learn and prove stitching

- □Two large stitched sensor chips (MOSS, MOST)

- Different approaches for resilience to manufacturing faults

- □Small test chips (Pixel **Prototypes**)

End caps

chips

Е

1

Core of MOSS stitched chip

of stitched

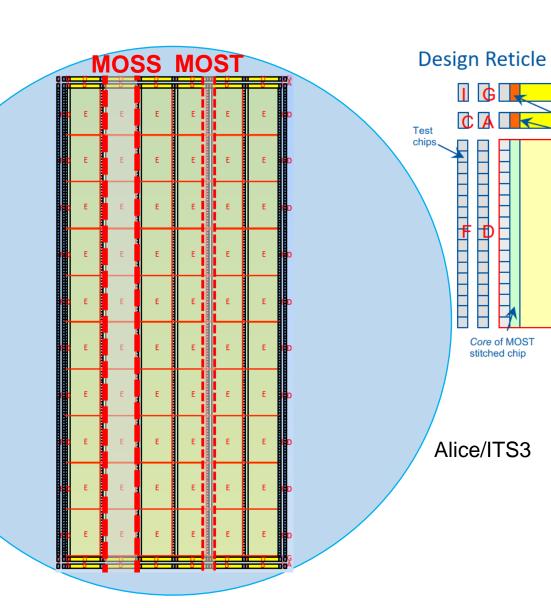

### ER1 Dicing and Test System

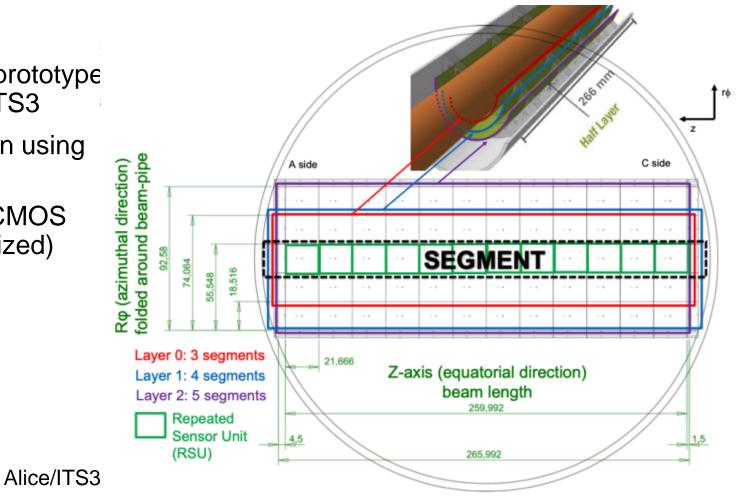

### MOSAIX (ER2) - Sensor Dimensions

MOSAIX is a full feature prototype of the sensor for ALICE ITS3

Wafer scale sensor design using the stitching technique

Process: TPSCo 65 nm CMOS Imaging Sensors(customized)

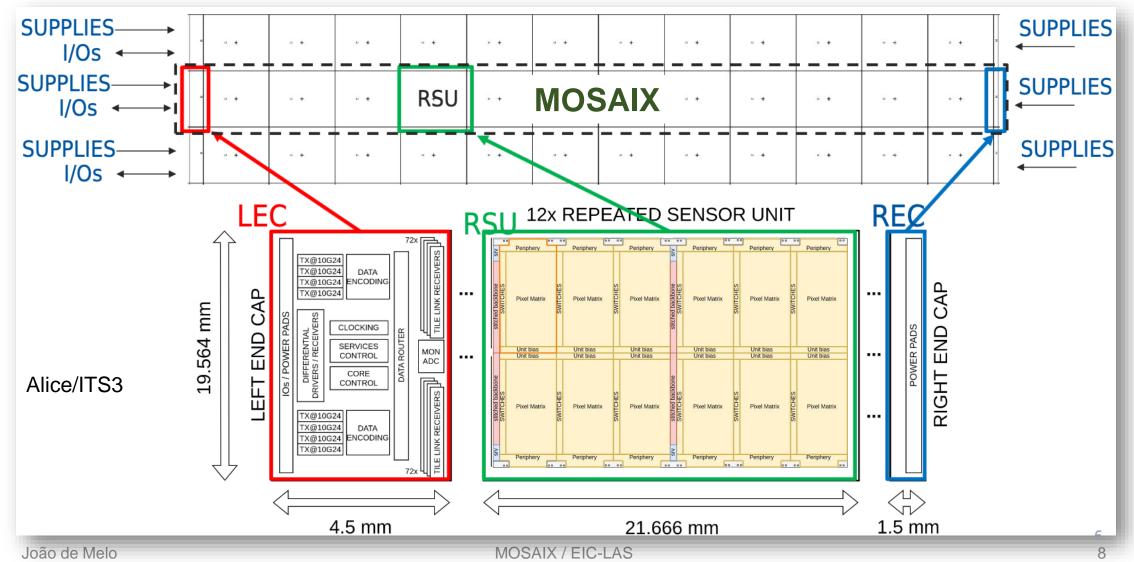

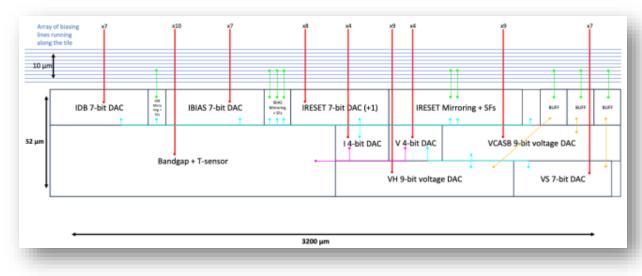

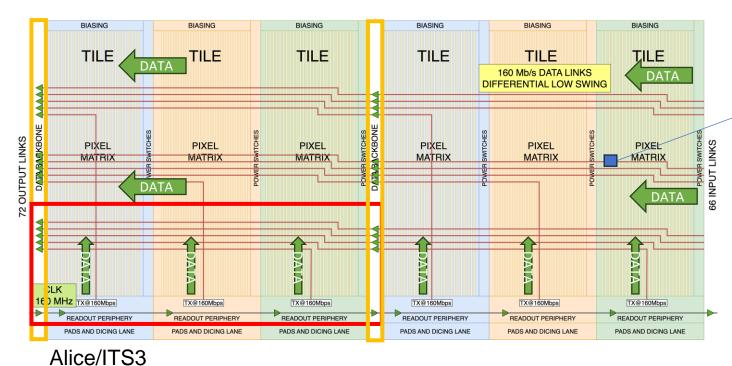

### **MOSAIX (ER2) - Top Integration Diagram**

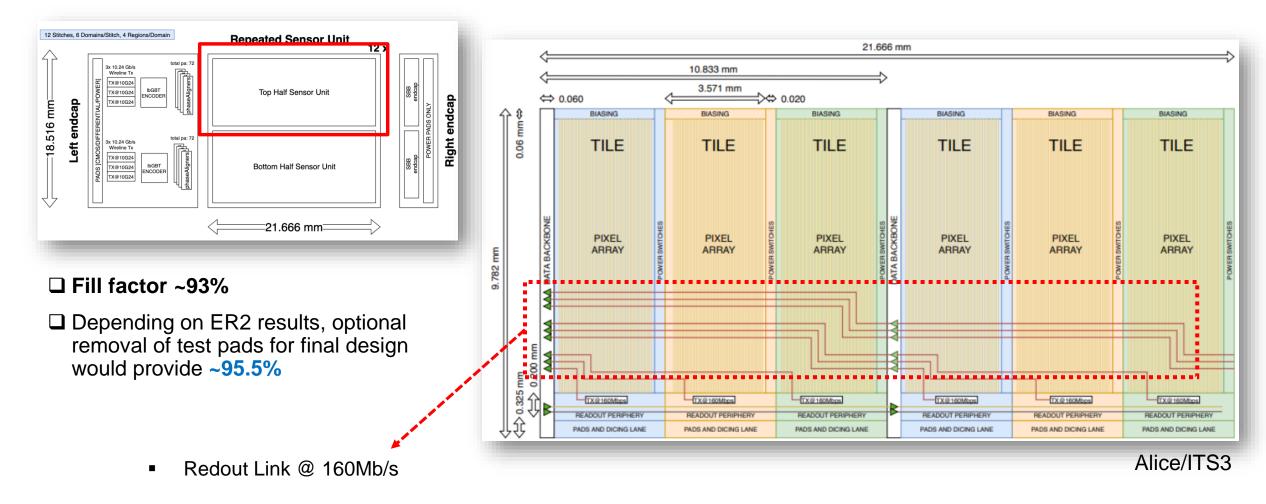

### **ER2 Stitched Sensor (MOSAIX)**

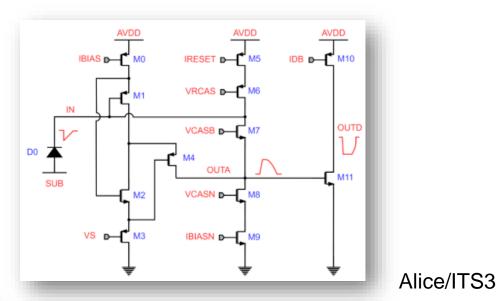

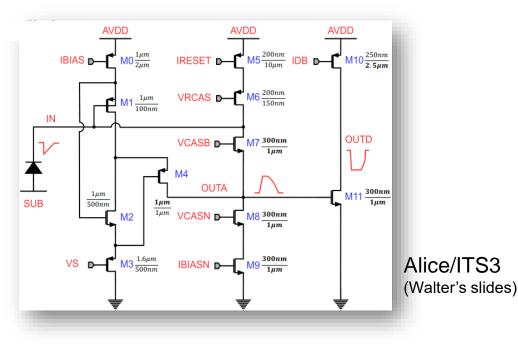

### **Front-End and Biasing**

#### **DEvolution path**

□ DPTS -> MOSS -> MOSAIX

✓ Improving transistor sizing and new layout

#### Unit Biasing (per Tile)

| Specification                           | Value                  | Comment                                     |

|-----------------------------------------|------------------------|---------------------------------------------|

| Current consumption                     | $< 30 \mathrm{nA}$     | IBIAS + discriminator standby current       |

| Dynamic energy (@ 600 e)                | $\leq 10  \mathrm{pJ}$ | No hard spec. as negligible wrt total power |

| Nominal threshold                       | $\approx 150 e$        | 1/4 of MIP                                  |

| Equivalent Noise Charge                 | < 18 e                 |                                             |

| Threshold mismatch                      | < 18 e                 |                                             |

| Gain (@ threshold)                      | $> 400 \mu V/e$        | Simulated avoiding discriminator kick-back  |

| Phase margin                            | $> 45^{\circ}$         | -                                           |

| Time of Arrival                         | $< 1  \mu s$           | 7                                           |

| Time over Threshold (@ 600 e)           | $\ll 1  \mathrm{ms}$   | For lost hit probability $< 1\%$            |

| Threshold sensitivity vs<br>supply drop | $<2\;e/{\rm mV}$       | Supply drop on AVDD and AVSS                |

| Detection efficiency                    | >99%                   |                                             |

Table 3.5: Analog front-end characteristics.

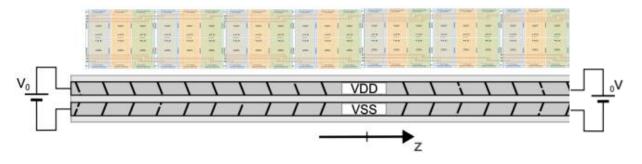

### Power Domains, Currents and IR Drops

| Supply purpose | Nets        | Voltage [V]   | Current [mA] | Pads on LEC | Pads on REC |

|----------------|-------------|---------------|--------------|-------------|-------------|

| Services       | SDVDD-SDVSS | 1.2 to 1.32   | 227          | Yes         | Yes         |

| Global analog  | GAVDD-GAVSS | 1.2  to  1.32 | 540          | Yes         | Yes         |

| Global digital | GDVDD-GDVSS | 1.2 to 1.32   | 1369         | Yes         | Yes         |

| Serializers    | TXVDD-TXVSS | 1.8           | 200          | Yes         | No          |

| Substrate bias | PSUB        | -1.2 to $0$   |              |             |             |

#### Alice/ITS3

Increases complexity and power dissipation

#### **Estimates of IR drops**

- Simple model, one global domain

- With the *new* metal stack (thick metal)

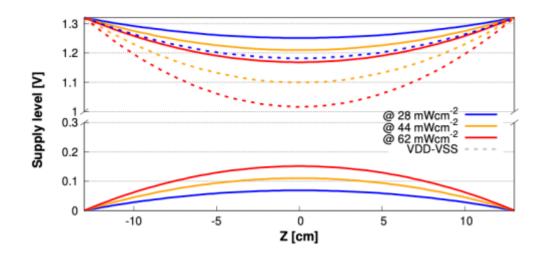

## Data Readout / SBB

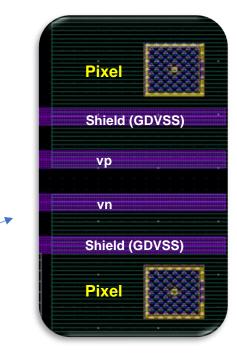

Differential transmission scheme with low voltage swing

Power efficiency, immunity to supply noise, reduction of noise injection into sensing analog nodes

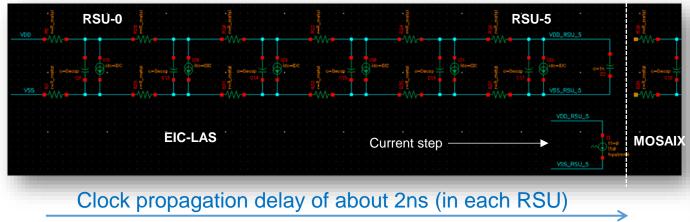

- Distribute 160 MHz clock from LEC to TILES

Long range (25 cm) on-chip 160 Mb/s point

- Long range (25 cm) on-chip 160 Mb/s point to point serial data links, clock synchronous

From 144 tile peripheries to the data aggregation in the Left End Cap

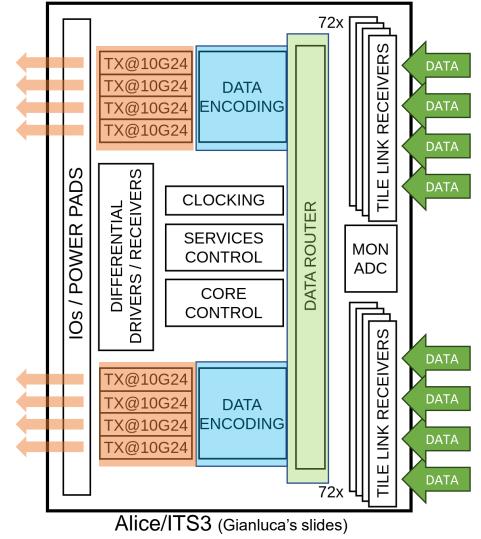

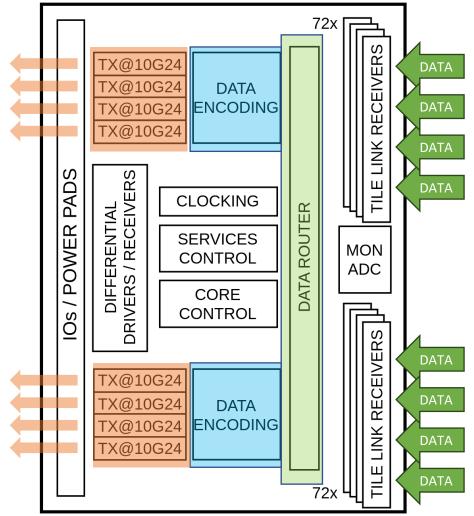

### LEC (Left End Cap) Architecture

Interfaces and peripheral data hub Input capacity 144×160 Mb/s = 23 Gb/s No data processing in LEC Data Router allows to reroute data from the 144 Tile Links to different serializers

#### □8 High Speed Serializers

Redundancy to mitigate the risk of failures of off-chip optical link components

Two operating modes (digitally controlled)

10.24 Gb/s line rate: 3 serializers are used

5.12 Gb/s line rate: 6 serializers are used

Unused serializers can be switched off

MOSAIX shall drive directly electro-optical transceivers (VTRX+)

Data Encoding logic ported from the IpGBT chip

### **MOSAIX Status**

# **REC Design Status**

| LO  | L1       | L2                | Туре         | Status 8 October          | Status 1 Novembre | Next milestone (30 November) |

|-----|----------|-------------------|--------------|---------------------------|-------------------|------------------------------|

|     |          |                   |              |                           |                   |                              |

| REC |          |                   |              | Correcting DRC violations |                   | SIGN OFF                     |

|     |          |                   |              |                           |                   |                              |

|     | Stitched | Backbone REC      | MIXED-SIGNAL | DONE                      | DONE              |                              |

|     | Pad Ring | g                 | ANALOG       | DONE                      | DONE              |                              |

|     | Clock m  | onitoring outputs | MIXED-SIGNAL | DONE                      | DONE              |                              |

|     |          |                   |              |                           |                   |                              |

Alice/ITS3 (Gianluca's slides)

## **RSU Design Status**

| .0 | L1 L2                        | Туре        | Status 8 October   | Status 1 Novembre             | Next milestone (30 November)    |

|----|------------------------------|-------------|--------------------|-------------------------------|---------------------------------|

|    | 1                            |             |                    |                               |                                 |

| SU |                              |             |                    |                               |                                 |

|    |                              |             |                    |                               |                                 |

|    | Pixel Matrix                 | DIGITAL     | CHECKING           | CHECKING                      | FULL MATRIX SUBMISSION CANDIDAT |

|    | Digital Pixel                | DIGITAL     | DONE               | DONE                          |                                 |

|    | Digital Column Basic         | DIGITAL     | DONE               | DONE                          |                                 |

|    | Digital Column Decoder       | DIGITAL     | DONE               | DONE                          |                                 |

|    | Analog Pixel Baseline        | ANALOG      | DONE               | DONE                          |                                 |

|    | Analog Pixel Variants        | ANALOG      | DONE               | DONE                          |                                 |

|    | Biasing Unit DACs, Mon, Temp | ANALOG      | DONE               | DONE                          |                                 |

|    | Power Switches               | ANALOG      | DONE               | DONE                          |                                 |

|    | Stitched Backbone RSU Block  | ANALOG      | SIGNOFF SIMS       | DONE                          |                                 |

|    | Service Node                 | DIGITAL     | POWER ANALYSIS     | REDUCING POWER                |                                 |

|    |                              |             |                    | <b>REDUCING POWER. TIMING</b> |                                 |

|    | Periphery                    | DIGITAL     | TIMING CLOSURE     | SIGNOFF. BUG FIXES            |                                 |

|    | SBB Tile (Pico Island)       | MIXED-SIGNA | L DONE             | DONE                          |                                 |

|    | <b>Readout and Control</b>   | DIGITAL     | DONE               | REDUCING POWER                |                                 |

|    | RSU Floorplan and Powerplan  | DIGITAL     | DONE               | DONE                          |                                 |

|    |                              |             | Routed, LVS OK.    | FULL FLOW. LVS OK.            |                                 |

|    | RSU Integration              | DIGITAL     | DRC fixes ongoing. | DRC and DFM fixes ongoing     | FULL RSU SUBMISSION CANDIDATE   |

Alice/ITS3 (Gianluca's slides)

| LO  | L1     | L2                      | Туре         | Status 8 October                  | Status 1 Novembre                 | Next milestone (30 November)    |

|-----|--------|-------------------------|--------------|-----------------------------------|-----------------------------------|---------------------------------|

|     |        |                         |              |                                   |                                   |                                 |

|     |        |                         |              |                                   |                                   |                                 |

| LEC |        |                         |              |                                   |                                   | Complete design and implement   |

|     |        |                         |              |                                   |                                   |                                 |

|     | Stitch | ed Backbone LEC         | MIXED-SIGNAL | Integration waiting LEC floorplan | Integration waiting LEC floorplan | Integrated in LEC and validated |

|     |        |                         |              |                                   |                                   |                                 |

|     | Monit  | oring ADC               | ANALOG       | REVISITING COMPARATOR             |                                   | SIGN OFF                        |

|     |        | Analog Blocks Schematic | ANALOG       | Revisiting comparator             | DONE                              |                                 |

|     |        | Analog Blocks Layout    | ANALOG       | Revisit comparator                | COMPLETING                        |                                 |

|     |        | Digital core            | DIGITAL      | DOING                             | COMPLETING                        |                                 |

|     |        |                         |              | Decoupling and filters added.     |                                   |                                 |

|     |        | Top integration         | ANALOG       | Routing finished.                 | COMPLETING                        |                                 |

|     |        |                         |              |                                   |                                   |                                 |

|     |        |                         |              |                                   |                                   |                                 |

Serializer GWT-PSI Complete design and implementation MIXED-SIGNAL Layout done. Analog Blocks Setting-up signoff simulations Timing signed-off ANALOG ANALOG Signed-off Regulators Revisited stability. DONE Digital Blocks DIGITAL Revisiting. Fixing timing. Complete block level design Top Integration MIXED-SIGNAL Flow in-place Full and clean implementation LEC Core Design and PnR ongoing Design and PnR ongoing Complete design and implementation DIGITAL Resetting and clocking DIGITAL To revise To revise Data Router DIGITAL **RTL done. Needs PnR** RTL done. Needs PnR High Speed Channel DIGITAL Revisiting, re-designing DONE DIGITAL DONE Data Encoder RTL done. Needs PnR GWT-PSI controller RTL done. Needs PnR DIGITAL RTL done. Needs PnR Slow Control DIGITAL RTL done. Needs PnR RTL done. Needs PnR Testability features DIGITAL Completing RTL entry RTL done. Needs PnR **Differential Transceivers** MIXED-SIGNAL DONE DONE SIGN OFF ANALOG DONE DONE SIGN OFF Pad Ring LEC Floorplan and Powerplan DIGITAL DOING Complete design and implementation DOING

Alice/ITS3 (Gianluca's slides)

Complete design and implementation

LEC Integration

DIGITAL

DOING

LEC

MOSAIX / EIC-LAS

DOING

## **MOSAIX: Work ahead**

**DOING** Completion of block level designs

- Completion of the ADC imminent

- Completion of the GWT-PSI Serializer, work needed

- **DOING** Completion of REC, RSU, LEC top designs

- REC completed

- RSU integration well advanced. Dependency on re-spin of components for bug fixes, power reduction, timing closure

- LEC behind, work needed

**DOING** Verification and validation phases of the integrated design

- Execution of physical integrity and manufacturability checks (DRC, DFM) ongoing

- Need of systematic block level power integrity analysis work needed

- Functional verification by simulations work needed

**DOING** Wafer scale integration ongoing

Alice/ITS3 (Gianluca's slides)

## **MOSAIX to EIC-LAS**

#### Main Tasks

## EIC-LAS: Reducing from 12 to 5-6 RSUs

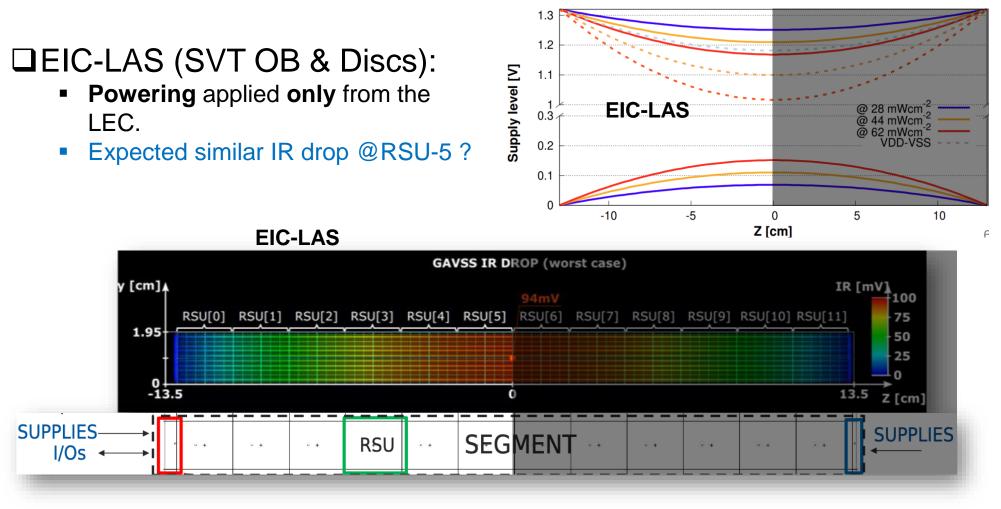

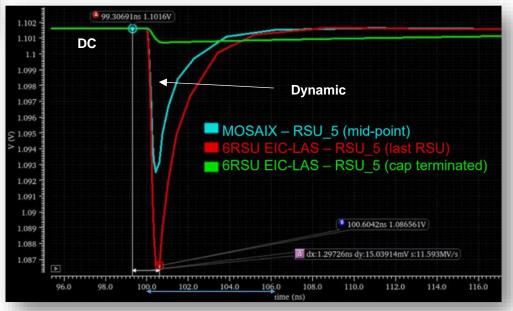

## EIC-LAS vs MOSAIX: Same IR Drop?

Simple model including supply resistivity, constant DC current, and local decaps.

- Local supply drop/noise are expected to be worse in the case EIC-LAS (case of dynamic activity).

- Possible improvements:

- I. REC internal decaps (limited area and REC modification).

- II. REC external decaps.

- III. Also powered from the REC.

João de Melo

MOSAIX / EIC-LAS

## MOSAIX to EIC-LAS : LEC Modifications

#### Reduce LEC to one channel

- Bypass Serializer LDOs

- Study on the performance before and after removing LDOs.

- Dedicated decap cells, star routing (supply), and functional adjustments (no LDO controls).

- Data Encoding and Router (serialization of the data to a single channel)

- Challenge to adapt/change

- SC control needs to be modified

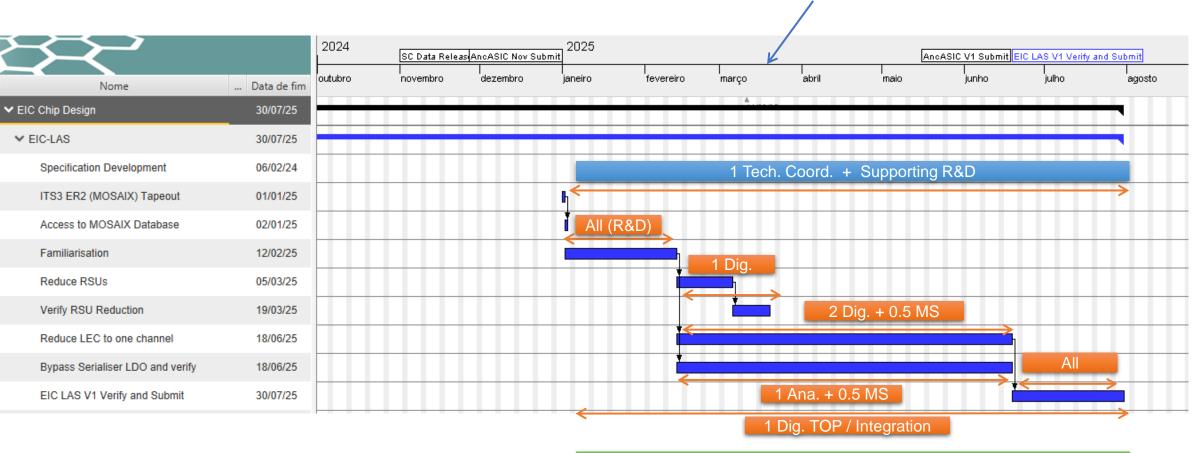

## **Preliminary Resources**

EIC\_LAS\_Sensor\_Dev\_Total = 1TL + 3.5 Dig. + 1 Ana. + 1 MS =~ 3.8 FTE

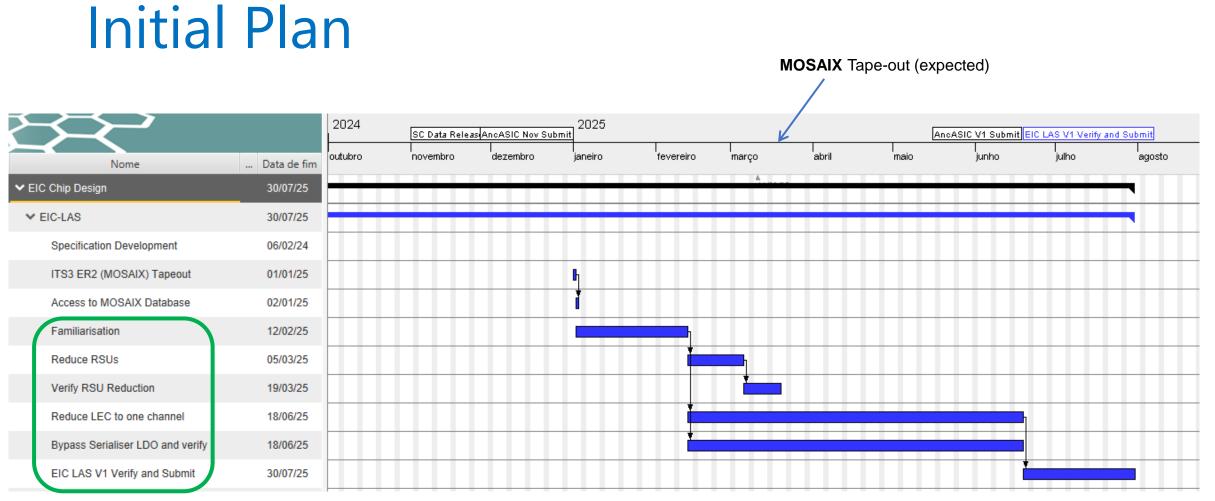

**MOSAIX** Tape-out (expected)

## Preliminary Resources and Tasks

### EIC-LAS Senor Development (~7 months)

- □1 Technical Lead that also supports R&D / Design

- □1 Digital engineer for Top / Integration

- □Reduce the number of RSUs

- 1 Digital engineer (half period) to reduce RSUs and to validate the signal/data integrity (of each RSU).

#### Reduce LEC to one channel

2 Digital engineers plus 0.5 mixed signal engineer. SC control needs to be modified as well as the serialization of the data to a single channel.

#### Bypass Serializer LDOs

1 Analog engineer plus 0.5 mixed signal engineer. Study on the performance before and after removing LDOs. Dedicated decap cells, star routing (supply), and functional adjustments (no LDO controls).

□ Final checks and tap-out

• All team. Functionality, filling, final DRC checks, and submission.

## **MOSAIX to EIC-LAS**

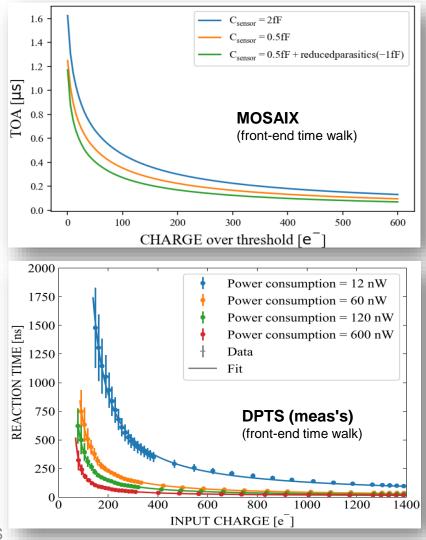

## Further Modifications? Timing Improvement!?

## **MOSAIX to EIC-LAS: Timing Improvement**

## **MOSAIX to EIC-LAS: Timing Improvement**

#### □Front-end Improvements

- Decreasing sensor's capacitance

- Increasing the power consumption (adjusting the BIAS)

João de Melo

MOSAIX / EIC-LAS

### **Thanks!**