# Radiation tolerance tests of key electronic components of the dRICH RDO

#### The PDU radiation environment

The dRICH-PDUs are in a moderately hostile radiation environment, which causes:

- SiPMs degradation.

- Lower reliability on Electronic component functioning.

**Expected radiation exposure, including a 5 safety factor** (ref data: <a href="https://wiki.bnl.gov/EPIC/index.php?title=Radiation Doses">https://wiki.bnl.gov/EPIC/index.php?title=Radiation Doses</a>):

$TID_5 \cong 2.3 \text{ krad}$  (for 1000 fb<sup>-1</sup>)

$\varphi_5(p+n>20 MeV)\cong 700~Hz/cm^2$

- Cumulative effects: during the component life, the integrated TID increases the power consumption up to a final damage.

- Single Event Effects (FEE): localized event induced by a single particle producing ionization through nuclear collision:

**Transient (SET):** spurious signals propagating in the circuit.

**Static (SEU):** errors overwriting memory location.

**Permanent (SEL, ...):** destructive events (permanent damage).

#### The PDU radiation environment

The dRICH-PDUs are in a moderately hostile radiation environment, which causes:

- SiPMs degradation.

- Lower reliability on Electronic component functioning.

**Expected radiation exposure, including a 5 safety factor** (ref data: https://wiki.bnl.gov/EPIC/index.php?title=Radiation Doses):

$TID_5 \cong 2.3 \ krad$   $(for 1000 \ fb^{-1})$

$\phi_5(p + n > 20 MeV) \cong 700 Hz/cm^2$

- Cumulative effects: during the component life, the integrated TID increases the power consumption up to a final damage.

- Single Event Effects (FEE): localized event induced by a single particle producing ionization through nuclear collision:

**Transient (SET):** spurious signals propagating in the circuit.

**Static (SEU):** errors overwriting memory location.

**Permanent (SEL, ...):** destructive events (permanent damage).

It is IMPORTANT to estimate SEE (SEU and SEL) and TID sensitivities for both RDO card and ALCOR FEBs!

9.0 cm

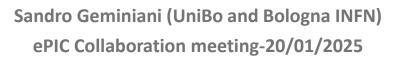

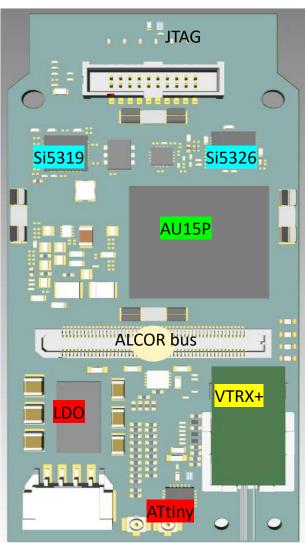

#### The RDO Board

**TOP**

**BOTTOM**

Ref: <a href="https://indico.bnl.gov/event/24127/">https://indico.bnl.gov/event/24127/</a>

#### **FPGAs**

- **AU15P**: **AMD Artix Ultrascale+** main FPGA interfacing with ALCORs.

- MPF50T: Microchip PolarFire FPGA responsible for the AU15P configuration (see later ...).

#### **Clock multiplier**

Si5319 and Si5326 from Skyworks Solutions.

#### **Power management**

- 2 LDOs LTM4709 for different power rails.

- **Microchip ATtiny417** μcontroller, controlling power consumption.

#### **Data link**

• VTRX+: optical transceiver.

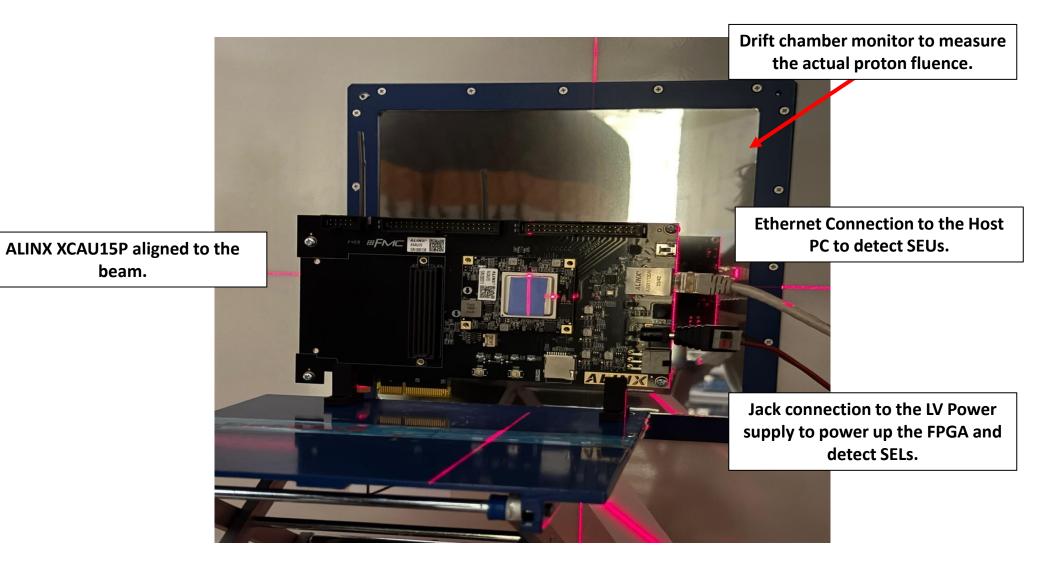

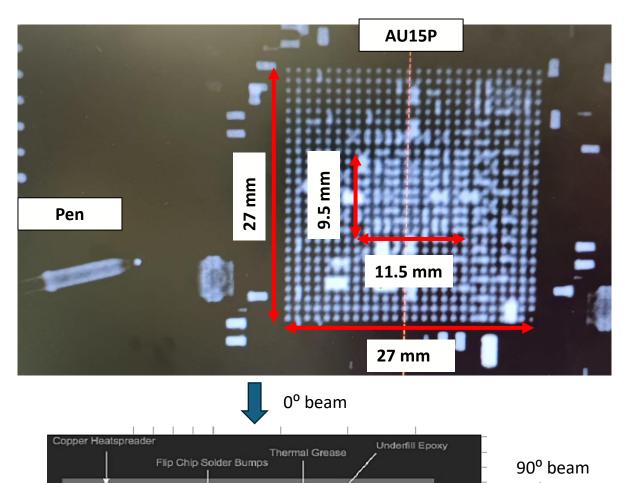

#### **ALINX XCAU15P**

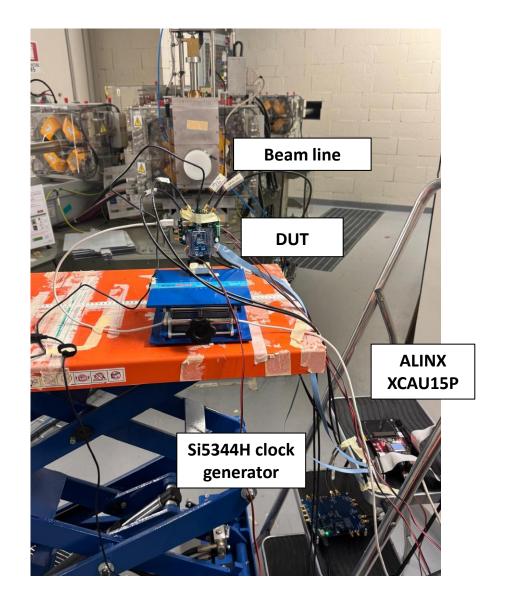

# Proton irradiation campaign (@Proton Irradiation facility in Trento)

### Waiting for the RDO...

#### Irradiation session:

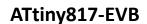

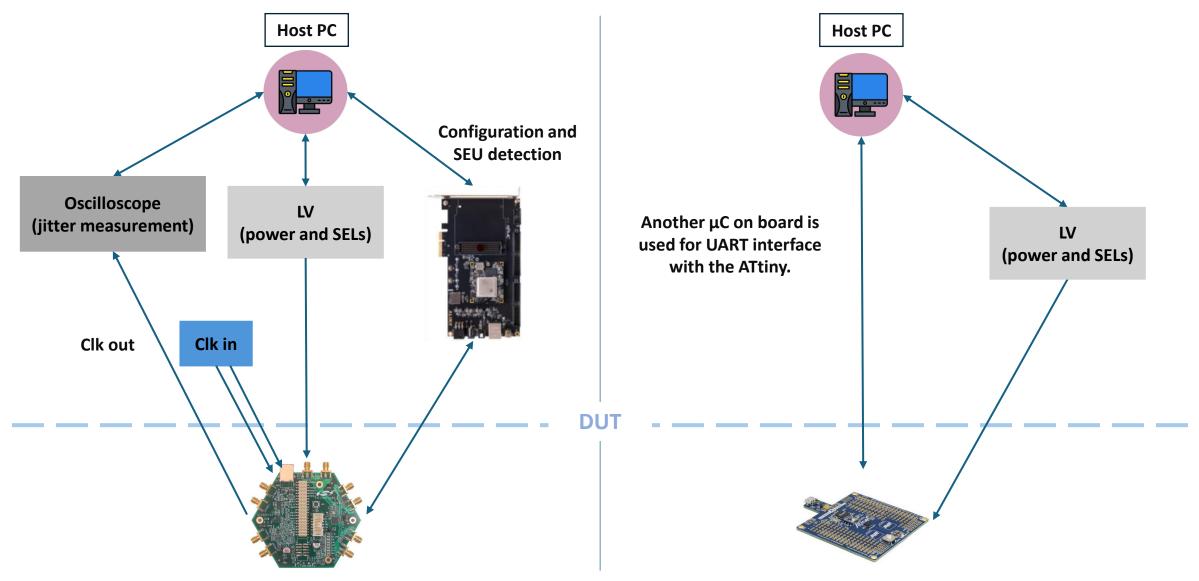

- Si5326 and ATtiny EVBs on a proton beam at 100 MeV kinetic energy (using a 10<sup>8</sup> Hz/cm<sup>2</sup> flux).

- ALINX XCAU15P board on a proton beam at 70 MeV kinetic energy (using a 10<sup>6</sup>/10<sup>7</sup> Hz/cm<sup>2</sup> flux).

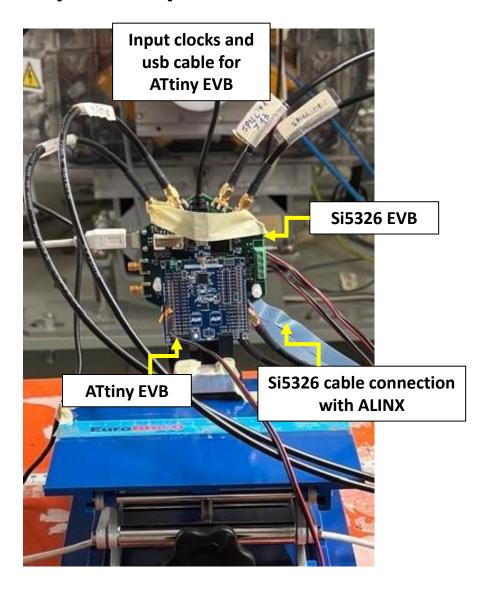

# Si5326 and ATtiny setup

# Si5326 and ATtiny setup

#### Results

#### **ATtiny817** μcontroller

- Monitored memory: 6.6/8 KB of FLASH (53 Kb) and 450/512 B of SRAM (3.6 Kb).

- 21 SEUs detected on SRAM, while 0 SEUs on FLASH memory after 1026 s.

- TID = 23 krad (dose rate = 1-2 krad/min)

- The ATtiny stopped working at TID = 23 krad.

- **SRAM**:  $\sigma_{\text{SEU}} = (3.89 \pm 0.54) \cdot 10^{-14} \frac{\text{cm}^2}{\text{bit}}$

- FLASH memory (limit @ 95% C.L.):  $\sigma_{SEU} < 3.83 \cdot 10^{-16} \frac{cm^2}{bit}$

MTBF in the dRICH system (1248 RDOs) for ATtiny417:

SRAM (256B): 4.0 h FLASH (4kB): > 26 h

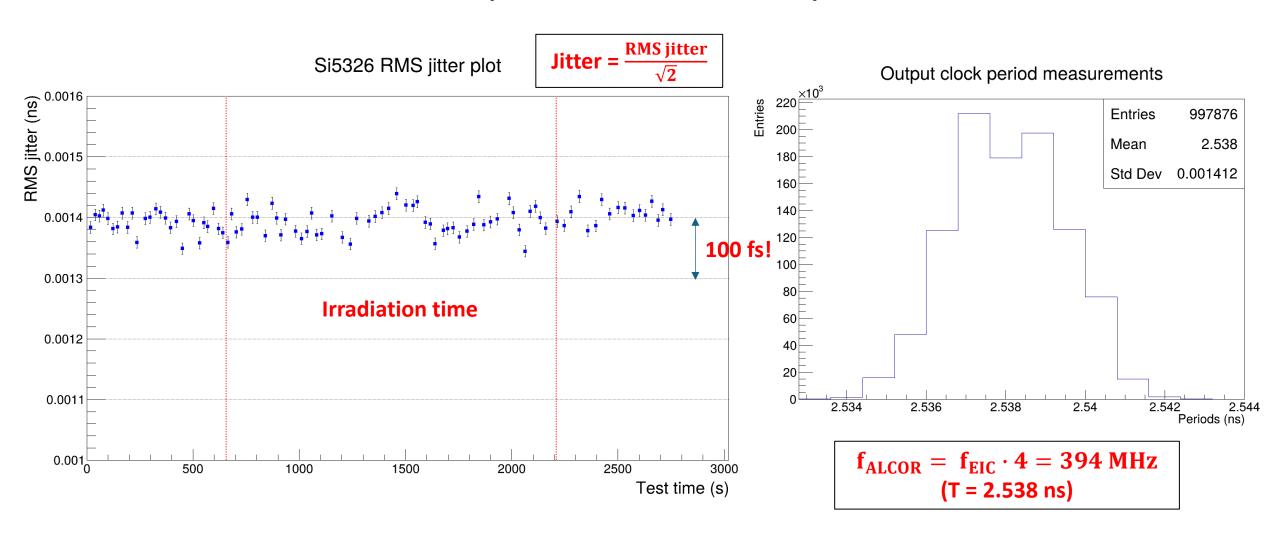

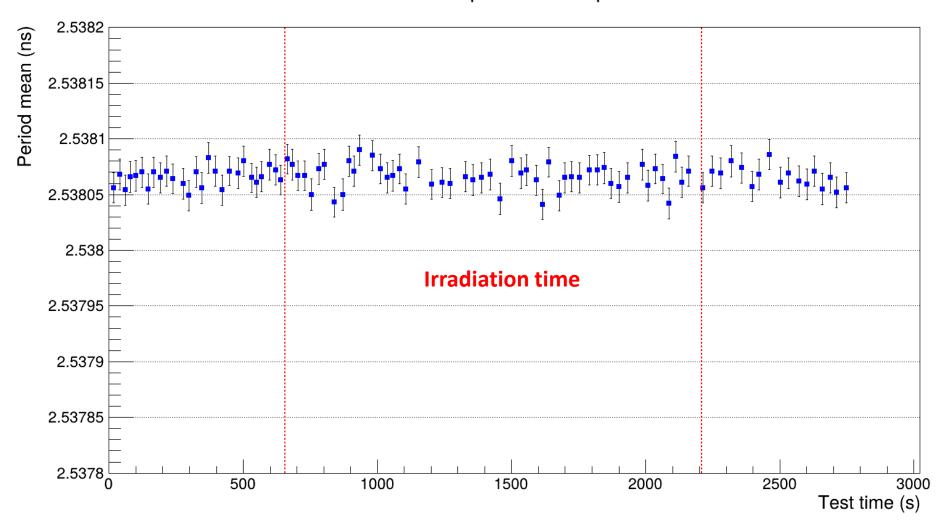

#### Si5326 clock multiplier

- Monitored memory: 2007/2048 bits of configuration memory.

- 19 SEUs and 0 SELs detected after 1553 s.

- TID = 42 krad (dose rate = 1-2 krad/min)

- Besides the SEUs, the device did not lose the PLL lock keeping the output clock period stable.

•

$$\sigma_{\text{SEU}} = (2.11 \pm 0.50) \cdot 10^{-14} \frac{\text{cm}^2}{\text{bit}}$$

MTBF in the dRICH system (1248 RDOs) for each Si5319 and Si5326:

3.8 h

### Jitter and period of the output clock

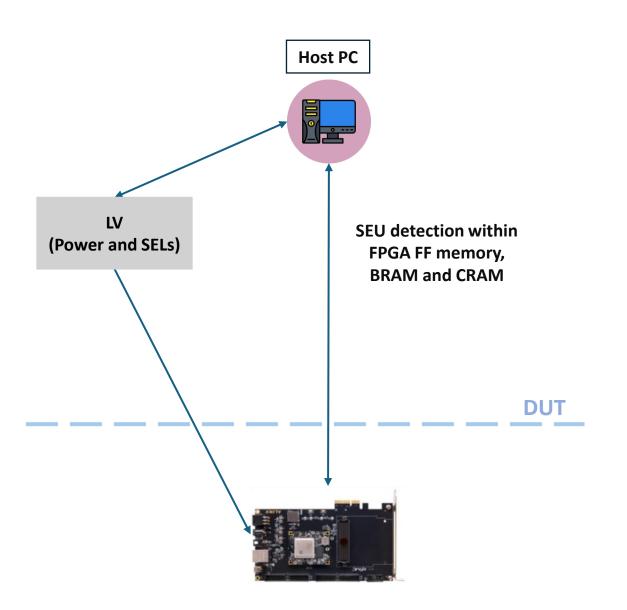

### ALINX XCAU15P setup

The AU15P checks its own memory (communication via IPbus over Ethernet link):

- FF chains and Block RAM buffer were configured with a fixed pattern and checked continuously.

- Configuration RAM was checked by the Soft Error Mitigation (SEM) IP core by AMD (ref: <a href="https://www.xilinx.com/products/intellectual-property/sem.html">https://www.xilinx.com/products/intellectual-property/sem.html</a>).

The SEM IP is configured in **«mitigation and testing»** mode:

- It locates the errors through ECC and CRC approaches.

- It corrects the error if the location is identified.

- It checks all the configuration memory.

# ALINX XCAU15P setup

#### Results

- Monitored memory: 8/156 Kb of FF memory, 3.6/5.1 Mb of BRAM and 33/33 Mb of CRAM.

- **0 SEUs** detected on **FF memory** and **69 SEUs** on **BRAM** after 2560s.

- 70 corrected SEUs, 11 uncorrected SEUs and 1 dead link detected on CRAM after 2560 s.

- No SEL detected after 3706 s.

- TID = 6.36 krad (dose rate = 10-500 rad/min) after 3706 s.

**FF memory** (limit @ 95% C.L.):  $\sigma < 3.5 \cdot 10^{-14} \frac{\text{cm}^2}{\text{bit}}$  MTBF (156 Kb) in the dRICH system (1248 RDOs): > 3.6 min

BRAM:

$$\sigma_{SEU}=(1.78\pm0.21)\cdot10^{-15}\frac{cm^2}{bit}$$

MTBF (5.1 Mb) in the dRICH system (1248 RDOs): 2.1 min

# SEU cross sections and MTBFs (33 Mb) in the dRICH system (1248 RDOs) for CRAM:

|       | $\sigma_{\text{SEU}} \left( 10^{-16} \frac{\text{cm}^2}{\text{bit}} \right)$ | MTBF<br>(min) |

|-------|------------------------------------------------------------------------------|---------------|

| COR   | $(1.96 \pm 0.25)$                                                            | 2.9           |

| UNCOR | $(3.09 \pm 0.94) \cdot 10^{-1}$                                              | 18            |

| TOTAL | $(2.30 \pm 0.28)$                                                            | 2.5           |

#### Conclusions and outlook

1. We integrated  $TID \sim 2.8 \cdot TID_5$  for the AU15P,  $TID \sim 10 \cdot TID_5$  for the ATtiny and  $TID \sim 18 \cdot TID_5$  for the Si5326.

No significative cumulative effect or SEL for Si5326 and AU15P, while the **ATtiny stopped working at TID = 23** krad.

Devices tested up to a TID largely exceeding expected TID @dRICH: no destructive effects seen for TID  $\leq$  TID<sub>5</sub>

2. **Si5326:** MTBF = **3.8** h (for **1248** RDOs) and the jitter analysis showed the **output clock is very stable.**

The RDO AU15P will control the chip configuration every t ≪ 3.8 h.

3. ATtiny: SRAM MTBF = 4 h and FLASH MTBF > 26 h (for 1248 RDOs).

The FLASH MTBF is a safety limit and key RAM registers will be implemented with TMR checks.

#### Conclusions and outlook

#### 4. Ultrascale+ FPGA SEUs cross sections estimated by AMD:

• BRAM:  $\sigma_{SEU} = (9.82 \pm 1.77) \cdot 10^{-16} \frac{\text{cm}^2}{\text{bit}}$

• CRAM:  $\sigma_{\text{SEU}} = (2.67 \pm 0.48) \cdot 10^{-16} \frac{\text{cm}^2}{\text{bit}}$

Our CRAM estimate is compatible with the AMD one while our BRAM estimate differs for a factor  $\sim 2$ . Then, our estimates for MTBFs (for 1248 RDOs) are:

|                                             | Our estimates | $\sigma_{SEU}\left(\frac{\mathrm{cm}^2}{\mathrm{bit}}\right)$ |

|---------------------------------------------|---------------|---------------------------------------------------------------|

| <b>BRAM</b> $(1.78 \pm 0.21) \cdot 10^{-}$  |               | $(1.78 \pm 0.21) \cdot 10^{-15}$                              |

| <b>CRAM</b> $(2.30 \pm 0.28) \cdot 10^{-1}$ |               | $(2.30 \pm 0.28) \cdot 10^{-16}$                              |

FF MTBF > 3.6 min and BRAM MTBF = 2.1 min

They are manageable at the AU15P firmware level using TMR,CRC and reset features.

**CRAM MTBF = 2.5 min**

The RDO MPFT50 as a FLASH based FPGA will work as scrubber, ensuring fast SEU correction.

#### Conclusions and outlook

4. Ultrascale+ FPGA SEUs cross sections estimated by AMD:

• BRAM:

$$\sigma_{\text{SEU}} = (9.82 \pm 1.77) \cdot 10^{-16} \frac{\text{cm}^2}{\text{bit}}$$

• CRAM:

$$\sigma_{\text{SEU}} = (2.67 \pm 0.48) \cdot 10^{-16} \frac{\text{cm}^2}{\text{bit}}$$

Our CRAM estimate is compatible with the AMD one while our BRAM estimate differs for a factor  $\sim$  2. Then, our estimates for MTBFs (for 1248 RDOs) are:

| Our estimates | $\sigma_{SEU}\left(\frac{cm^2}{bit}\right)$ |  |

|---------------|---------------------------------------------|--|

| BRAM          | $(1.78 \pm 0.21) \cdot 10^{-15}$            |  |

| CRAM          | $(2.30 \pm 0.28) \cdot 10^{-16}$            |  |

FF MTBF > 3.6 min and BRAM MTBF = 2.1 min

They are manageable at the AU15P firmware level using TMR,CRC and reset features.

**CRAM MTBF = 2.5 min**

The RDO MPFT50 as a FLASH based FPGA will work as scrubber, ensuring fast SEU correction.

No showstoppers identified for tested RDO components. SEU mitigation strategies are needed in firmware design, as expected!

# Thank You for Your attention!

# Backup slides

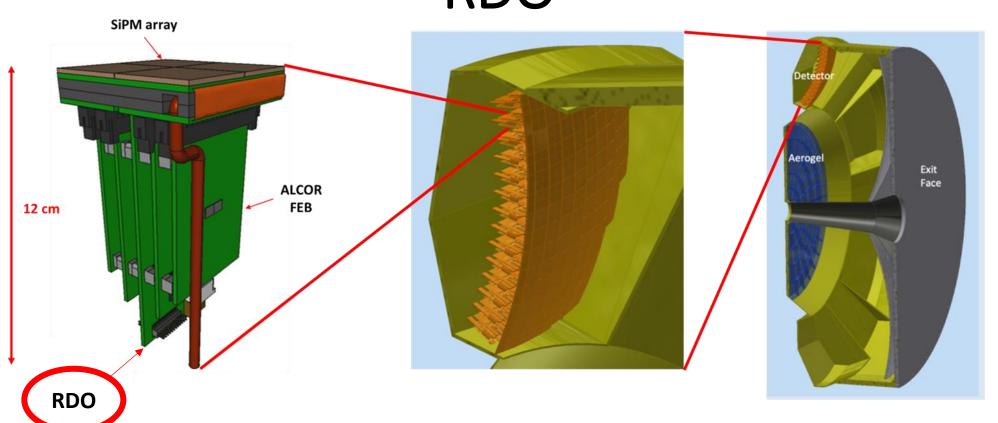

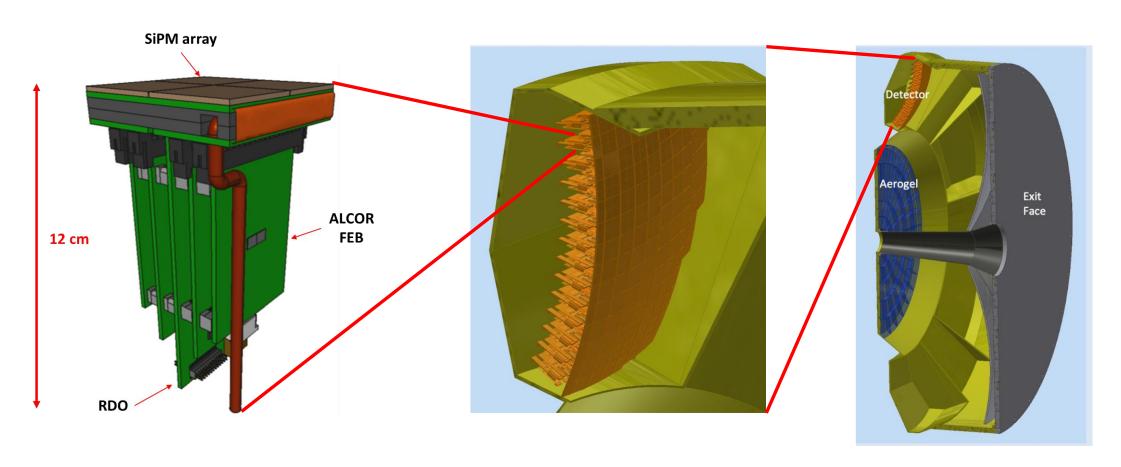

# The RDO within the dRICH

#### **Photon Detection Unit (PDU):**

- 4 matrices (64SiPMs each)

- 4 ALCOR64 FEBs

- 1 RDO board

#### **Detector Box:**

• 208 PDUs

#### dRICH detector:

6 sectors for 1248 PDUS

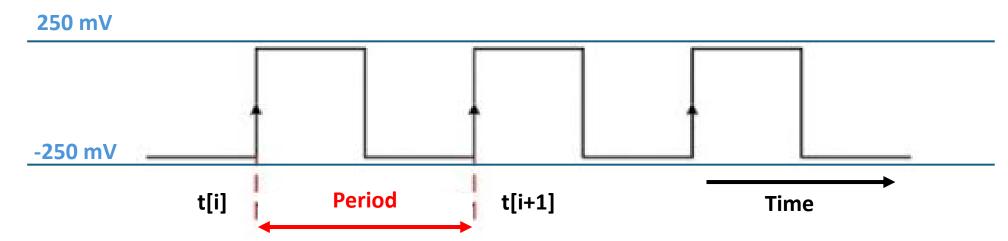

# Period jitter measurement

The period jitter measurement was performed as follows:

- 1. The **0.0 mV transition point** at **each rising edge** was estimated.

- 2. The period was measured as t[i+1] t[i].

- 3. Steps 1. and 2. were repeated after a random number of clock cycles.

- 4. A gaussian fit was applied to estimate the RMS (RMS jitter).

As the period measurement is the **difference** of two consecutive transition time values:

$$Jitter = \frac{RMS \, jitter}{\sqrt{2}}$$

# Period mean plot

#### Si5326 period mean plot

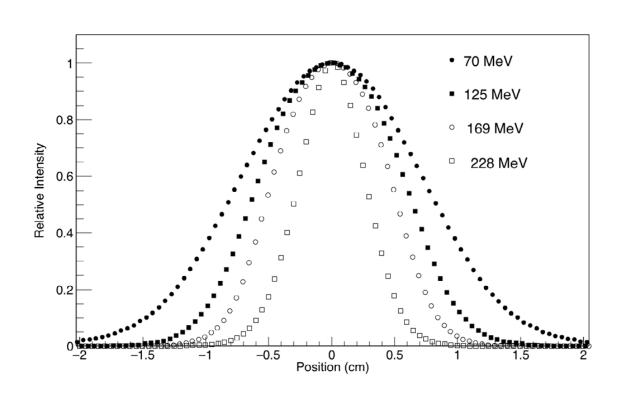

# Devices and TIFPA beam

Ref: <a href="https://www.sciencedirect.com/science/article/pii/S">https://www.sciencedirect.com/science/article/pii/S</a> <a href="https://www.sciencedirect.com/science/article/pii/S">0168900217306654</a>

| DUT       | Area (cm²)                     |  |

|-----------|--------------------------------|--|

| ATtiny817 | 0.16                           |  |

| Si5326    | 0.36                           |  |

| AU15P Die | $\sim \frac{7.29}{6.67} = 1.1$ |  |

| E (MeV) | $\sigma_{_X}$ (mm) | $\sigma_y$ (mm) | Asymmetry (%) |

|---------|--------------------|-----------------|---------------|

| 70.2    | 6.93               | 6.91            | 0.1           |

| 73.9    | 6.63               | 6.74            | 0.8           |

| 82.7    | 6.28               | 6.41            | 1.0           |

| 90.8    | 6.04               | 6.15            | 0.9           |

| 100.0   | 5.63               | 5.73            | 0.8           |

| Energy<br>[MeV] | Range<br>[g/cm²] | FWHM<br>[mm] | Intensity<br>[p/s] |

|-----------------|------------------|--------------|--------------------|

| 70              | 4.1              | 16.2         | 3.83E+06           |

| 74              | 4.5              | 15.9         | -                  |

| 83              | 5.5              | 15.2         | 7.50E+06           |

| 91              | 6.5              | 14.6         | 9.94E+06           |

| 100             | 7.72             | 13.7         | 1.19E+07           |

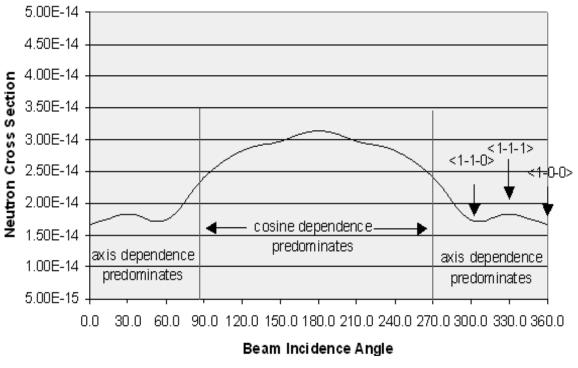

## The AU15P die and Flip-Chip package effect

Organic Buildup Substrate

Is the  $\sim$ 2 factor for the BRAM SEU cross section due to the effect of the FPGA package?

Such an effect was shown for CRAM bits for a Virtex-II FPGA (ref: <a href="https://www.researchgate.net/publication/3430143">https://www.researchgate.net/publication/3430143</a>).

Silicon Die

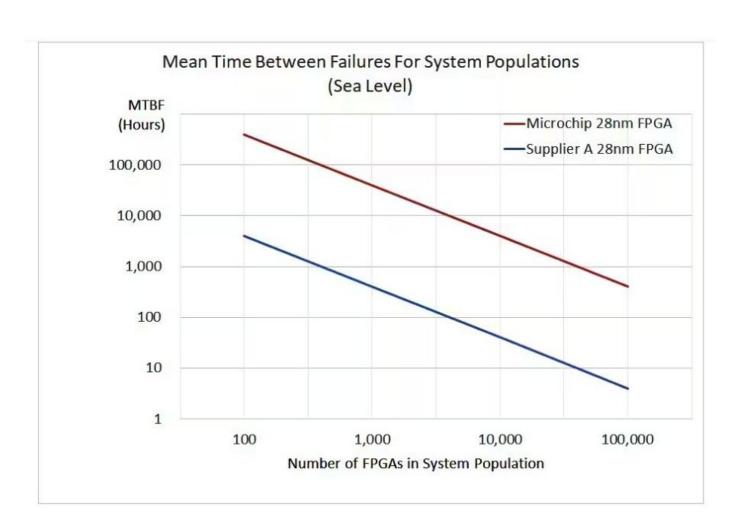

# Configuration memory MTBF for Microchip FPGAs

**Ref:** <a href="https://www.microchip.com/en-us/products/fpgas-and-plds/reliability#seus">https://www.microchip.com/en-us/products/fpgas-and-plds/reliability#seus</a>

In this case the **failure** is not the occurrence of a SEU, but it is the **real failure of the FPGA DAQ system**.