#### Schema di Readout e DAQ

Nicolò Tosi

**DUNE Italia** 29/11/2024

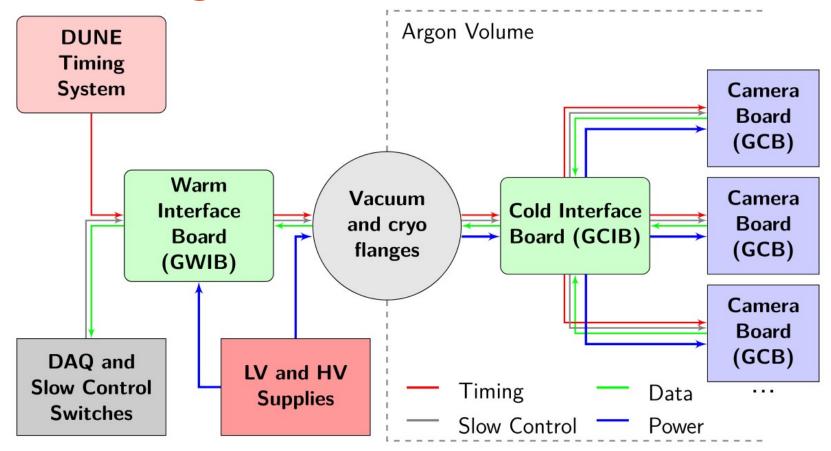

# Schema generale

## Ma non è tutto, la lista è lunga

- Molti sistemi di sviluppo e test: una lista provvisoria

- Sistema di test ASIC proto Camera Board

- Mock-up termo-meccanico per test criogenia/bolle ad LNF

- Sistema di test e caratterizzazione dei SiPM

- Lista provvisoria

- Stilata in una riunione tra Genova e Bologna

- Aperta ad altri contributi

- Approssimativamente in ordine di periodo di sviluppo

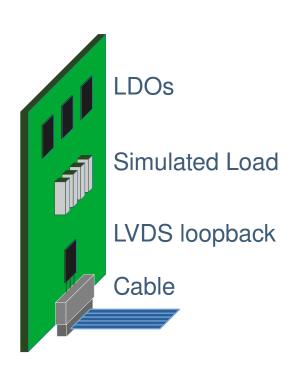

## Mock up e test connettori

PCB per test "Multifunzione"

- Studi su connettori

- Candidato: D-SUB HD 44 o 78 pin

- Studi su cavi o flex

- Validazione componenti in criogenia

- Buffer LVDS, LDO, ...

- Test Termico

- Resistenze simulano potenza ASIC

- Attività avviata a Bologna, 24/25

500€ l'uno!

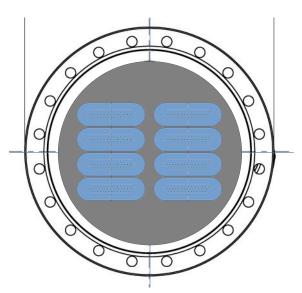

Flangia CF160 con otto DB44

## Mock up e test connettori

PCB per test "Multifunzione"

- Studi su connettori.

- Candidato: D-SUB HD

- Studi su cavi o flex

- Validazione componenti in criogenia

- Buffer LVDS, LDO, ...

- Test Termico

- Resistenze simulano potenza ASIC

- Attività avviata a Bologna, 24/25

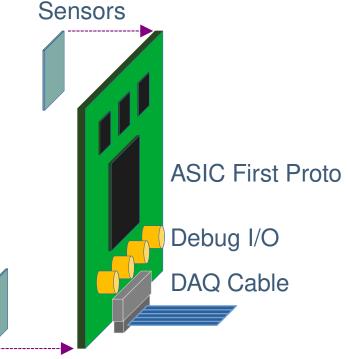

### Sistema di test ASIC

- Proto Camera Board

- ASIC, con tutti gli I/O di test e debug necessari

- Qualche SiPM rappresentativo dei vari tipi

DAQ standalone, derivata da cold demonstrator

Sviluppo comune BO/GE/TO 25/26

### Sistema di test SiPM

- Caratterizzazione simile a quanto fatto per PDS

- Test in criogenia, curve IV, mappe efficienza...

- Ma c'è una differenza importante: SiPM non ancora saldati

- Difficile fare IV con ASIC già connesso

- Probe station cryo? (NOA a Gran Sasso?)

- Oppure socket BGA con microsprings?

Task disponibile per volenterosi, 2026

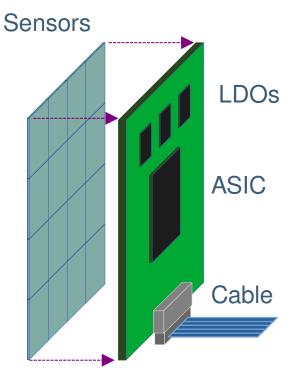

#### **GRAIN Camera Board - GCB**

- Camera Board Finale

- ASIC definitivo

- 1024 SiPM del tipo scelto (2x2, 3x3)

- Layout di notevole complessità

- Sviluppo comune a livello schematico

- Sviluppo individuale del layout BO 3x3, GE 2x2, 2026+

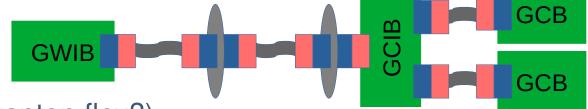

### Interconnessione - GCIB

Versione definitiva cablaggio

Air Insulation Argon Vacuum GCB

- Decisione su GCIB:

- No GCIB, un connettore per GCB

- GCIB con buffer: un connettore per 2-4 GCB

- Cablaggio in crio (kapton flex?)

- Sviluppo principalmente a Bologna

#### **Readout - GWIB**

- Ruolo primario: interfaccia tra ASIC e DAQ/timing

- FPGA/Zynq, una gestisce fino ad 8 GCB

- Sviluppo principalmente di Genova

**GRAIN Warm Interface Board**

- Ruoli secondari

- Acquisizione output analogico calibrazione/test (BO)

- Driver/impulsatore per calibrazione (scoperto)

### Alimentazione e Bias SiPM

- Bias relativamente semplice, O(100) canali a O(30) V

- GRAIN richiede correnti alte O(100A) a tensioni basse (<2V)</li>

- Riduce potenza dissipata nel criostato da regolatori LDO

- Si può fare con il classico mainframe CAEN

- fuori da magnete, cavi lunghi, noise, ...

- Si può ipotizzare anche una soluzione custom

- convertitori vicino a GRAIN, dentro magnete

- Task disponibile per volenterosi

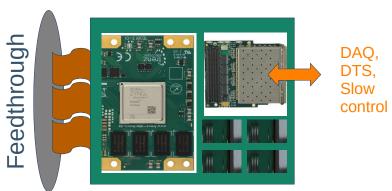

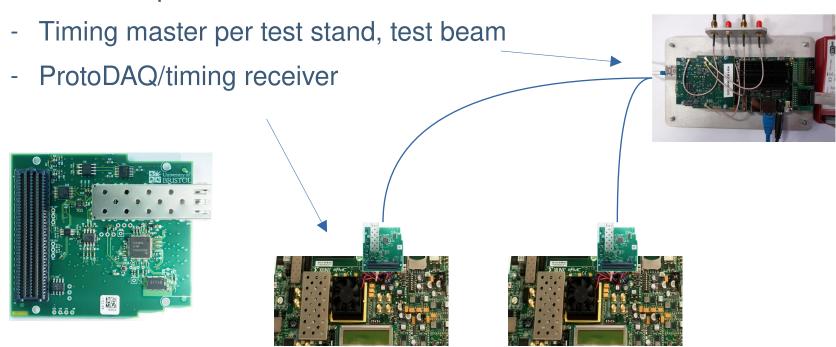

#### **Addendum: Proto DAQ**

Ci servono per GRAIN, ma servono a tutti

Bristol Timing reference:

Ordinati alcuni pezzi, chi ne vuole? FMC, Compatibili con varie demo Xilinx, FW con IPbus