# **ASIX** (Analog spectral Imager for X-rays)

Proposta di Esperimento

Area di ricerca: Detectors

**Principal Investigator:** Massimo Minuti (INFN Pisa)

**Responsabile locale:** Luigi Gaioni (INFN Pavia)

### ASIX at a glance

Ø

Goal of the project: establish new X-ray detection systems with optimal imaging and spectral capabilities, combined with an event-driven readout logic to enhance system rate capability

- The position and energy resolutions are targeted to be better than 10 µm and 350 eV (@8 keV), respectively, with a maximum global readout rate of up to 10<sup>8</sup> hits/cm<sup>2</sup>/s

- INFN Units: Milano, Pisa, Pavia, Torino

- External Units: TIFPA, Unimi, Unipi, Unipv, Unibg, Polito

- Duration: 3 years

#### State of the art

- X-ray radiation is widely used in medical, industrial, scientific, artistic, and security applications

- Detection techniques typically leverage electronic devices that provide information about photon absorption point, energy, and arrival time

- Key point is the balancing of spatial and energy resolution, the latter being typically limited by charge-sharing issues in small-pixel detectors (<100µm)</li>

|                                               | <u>Medipix4/</u><br><u>Timepix4</u> | <u>Eiger</u>          | <u>PIXIE-III</u>   | <u>XPOL-III</u>    | <u>This</u><br>Proposal |

|-----------------------------------------------|-------------------------------------|-----------------------|--------------------|--------------------|-------------------------|

| Pixel pitch                                   | 55 <b>μ</b> m                       | 75 <b>μ</b> m         | 60 <b>µ</b> m      | 50 <b>µ</b> m(hex) | 50 μm(hex)              |

| Pixel density<br>[px/mm <sup>2</sup> ]        | 330                                 | 180                   | 280                | 470                | 470                     |

| Pixel noise [rms]                             | 65 e-                               | 120 e-                | 50 e-              | 50 e-*             | 20-30 e-*               |

| Minimum<br>Threshold                          | 450 e-                              | 700 e-<br>(@2.5 keV)* | 1.5 keV            | 250 e-*            | 100-150 e-*             |

| Energy Resolution<br>(FWHM) Si-<br>equivalent | 1.5 keV<br>(@2ke- Qin)*             | 1 keV<br>(@8keV)*     | 2 keV<br>(@20keV)* | 450 eV*            | 250-350 eV*             |

| Technology                                    | 65 nm                               |                       | 130 nm             | 180nm              | 65nm                    |

## Design goals

- The ultimate goal is to achieve energy resolutions at the Fe, Cu, Mo, and Ag K-lines comparable to the best-in-class X-ray detectors dedicated to spectroscopy. This will be matched with excellent imaging resolution provided by the ASIC granularity and high data throughput.

- As the final outcome, we propose to develop, in a 65 nm CMOS technology, a small-scale demonstrator (~5 x 5 mm<sup>2</sup>) of a pixel hybrid sensor

| Characteristic              | Design goals                              |

|-----------------------------|-------------------------------------------|

| Energy range                | 2–10 keV                                  |

| Energy resolution           | 350 eV FWHM @ 8 keV                       |

| Pixel size                  | 50 μm                                     |

| Spatial resolution          | 10 μm                                     |

| Front-end noise (ENC)       | < 30 e <sup>-</sup>                       |

| Dynamic Range               | 20000 e <sup>-</sup>                      |

| Active area                 | $\geq 5 \times 5 \text{ mm}^2$            |

| Trigger mode                | Self-triggering                           |

| Readout mode                | event driven, full readout                |

| Maximum global readout rate | 10 <sup>8</sup> hits/cm <sup>2</sup> /sec |

| Power Consumption           | $\leq 1 \text{ W/cm}^2$                   |

#### The ASIX detector

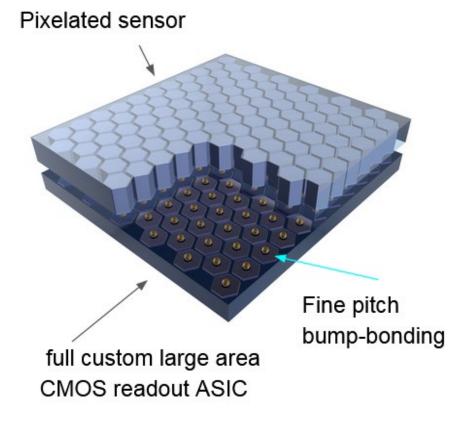

The ASIX detector units will implement a hybrid structure combining:

- a full-custom readout ASIC in 65 nm CMOS, equipped with low-noise front-end electronics, on chip A/D conversion, readout and configuration logic

- a customized edgeless Silicon sensor fabricated with advanced processing techniques aiming at minimizing the leakage current and the dead space at the device edges

- a simple and robust electro-mechanical integrated assembly on chip carrier boards aiming at providing a fully functional hybrid sensor module

- a compact and portable FPGA based DAQ system capable of supporting test and performance evaluation activities in the relevant test environment

## **ASIX Readout Chip**

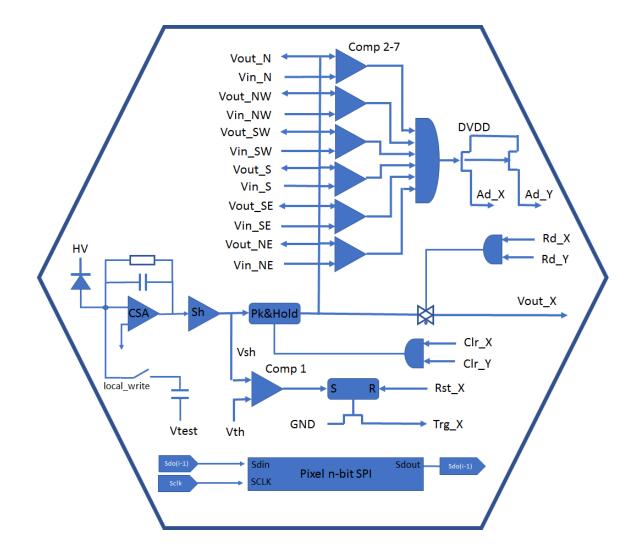

- A key point of the project is the development of pixel electronics with ultra-low noise, combined with fast readout and high-speed data output interfaces

- For the pixel electronics, we envision a full spectroscopy chain with an ultra-low-noise front-end (< 30 e rms), followed by a peak detector circuit, local discriminators, and readout and configuration logic

- On-chip A/D conversion will build upon a 10-bit SAR ADC capable of 5-10 MSPS, which was previously developed for earlier experiments. This ADC will serve as our baseline for customization in the ASIX context

- Pavia group will be involved in the design of pixel electronics + ADC

#### WP Structure

| WP   | Name                                                      | Responsible        | Contributors   |

|------|-----------------------------------------------------------|--------------------|----------------|

| WP 1 | Project management & dissemination                        | Massimo Minuti     | MI, PI, PV, TO |

| WP 2 | 2 Readout ASIC design,<br>verification and<br>development |                    | MI, PI, PV, TO |

| WP 3 | 3 Sensor design,<br>verification and<br>development       | Maurizio Boscardin | TIFPA          |

| WP 4 | 4 Detector Module<br>Assembly, Test equipment<br>and DAQ  |                    | PI             |

| WP 5 | 5 Test and validation                                     |                    | MI, PI, PV, TO |

#### Task timeline breakout

| WP                                         | Task                                  | start | duration | end |

|--------------------------------------------|---------------------------------------|-------|----------|-----|

| 1:Project<br>management &<br>dissemination | 1: Coordination                       | 0     | 36       | 36  |

|                                            | 2.1: proto-chip design                | 0     | 6        | 6   |

| 2:Readout ASIC                             | 2.2: proto-chip<br>fabrication        | 6     | 3        | 9   |

| 2.1100000171010                            | 2.3: final-chip design                | 10    | 8        | 18  |

|                                            | 2.4: final-chip<br>fabrication        | 18    | 3        | 21  |

| 3:Sensor design, verification and          | 3.1: sensor design and process review | 12    | 2        | 14  |

| development                                | 3.2: sensor fabrication               | 14    | 7        | 21  |

| 4:Detector                                 | 4.1: hybrid assembly                  | 21    | 8        | 29  |

| Module<br>Assembly, Test<br>equipment and  |                                       |       |          |     |

| DAQ                                        | 4.2: DAQ setup                        | 7     | 3        | 10  |

| 5:Test And<br>Validation                   | 5.1: proto-chip test                  | 9     | 3        | 12  |

|                                            | 5.2: final-chip test                  | 21    | 3        | 24  |

| Validation                                 | 5.3: ASIX sensor test                 | 29    | 7        | 36  |

Two deliverables expected in WP2 D2.1 proto-chip ASIC D2.2 final-chip readout ASIC

## Budget

| WP                                                           | ltem                                               | Sede  | Capitolo | 2025<br>(keu)* | 2026<br>(keu)* | 2027<br>(keu)* | Tot 3<br>anni(keu)* |

|--------------------------------------------------------------|----------------------------------------------------|-------|----------|----------------|----------------|----------------|---------------------|

|                                                              | Missioni                                           | PI    | Miss     | 1,5            | 1,5            | 1,5            | 4,5                 |

|                                                              | Missioni                                           | PV    | Miss     | 1,5            | 1,5            | 1,5            | 4,5                 |

|                                                              | Missioni                                           | MI    | Miss     | 1,5            | 1,5            | 1,5            | 4,5                 |

| 1. "Project Office"                                          | Missioni                                           | TIFPA | Miss     | 1,5            | 1,5            | 1,5            | 4,5                 |

|                                                              | MIssioni                                           | то    | Miss     | 1,5            | 1,5            | 1,5            | 4,5                 |

|                                                              | Totale WP                                          |       |          |                |                |                | 18                  |

| 2. "Readout ASIC<br>design, verification<br>and development" | prototipo 1 di piccola scala<br>2 X 2 mm^2 mi@asic | PV    | Cons     | 18             |                |                | 18                  |

|                                                              | chip finale 5 X 5 mm^2<br>MPW                      | PV    | Cons     | 90             |                |                | 90                  |

|                                                              |                                                    |       |          |                |                |                |                     |

|                                                              | Totale WP                                          |       |          |                |                |                | 108                 |

|                                                           | i                            |    |      |       |       |      |       |

|-----------------------------------------------------------|------------------------------|----|------|-------|-------|------|-------|

| 3. "Sensor<br>design,<br>verification and<br>development" | Sensore finale               |    | Cons |       | 30    |      | 30    |

|                                                           | Totale WP                    |    |      |       |       |      | 30    |

|                                                           | assemblaggio<br>ASIC/sensore | PI | Cons |       | 98    |      | 98    |

|                                                           | PCB sensor carrier           | PI | Cons | 1,5   | 4     |      | 5,5   |

| 4. "Sensor<br>Module<br>Assembly, test                    | Test station PC              | PI | Inv  | 2     |       |      | 2     |

| equipment and DAQ"                                        | DAQ Boards                   | PI | Cons | 2,5   |       |      | 2,5   |

|                                                           | Mechanics                    | PI | Cons |       | 2     | 5    | 7     |

|                                                           | Totale WP                    |    |      |       |       |      | 115   |

| 5. "Test and validation"                                  |                              |    |      |       |       |      |       |

|                                                           | Totale WP                    |    |      |       |       |      | 0     |

| Totale                                                    |                              |    |      | 121,5 | 141,5 | 12,5 | 275,5 |

### Participant list for PV group

| Name               | Role              | FTE |

|--------------------|-------------------|-----|

| Luigi Gaioni       | Local coordinator | 0.4 |

| Andrea Galliani    | Participant       | 0.5 |

| Massimo Manghisoni | Participant       | 0.3 |

| Lodovico Ratti     | Participant       | 0.1 |

| Gianluca Traversi  | WP2 leader        | 0.3 |

TOT FTE 1.6

#### **INFN** Pavia services requests

NONE