# Report on the FPGA flagships

S. Gennai & B. Spisso

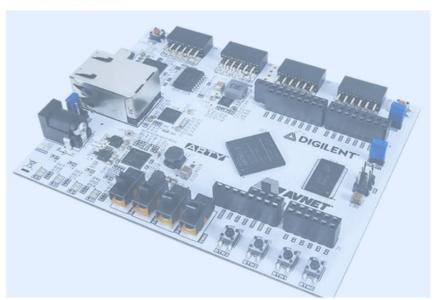

#### **FPGA** programming courses

Two courses (from Spoke2) were taken:

Introductory course to HLS FPGA programming.

From the 27<sup>th</sup> to the 30<sup>th</sup> of November <a href="https://agenda.infn.it/event/38191/">https://agenda.infn.it/event/38191/</a>

Introductory course to VHDL

From the 4th to the 6th of March <a href="https://agenda.infn.it/event/39721/">https://agenda.infn.it/event/39721/</a>

Introduction to EPGA programming

ntroduction to FPGA programming

# **Update from ATLAS Group**

- On the L0 work (AI on FPGA all-in-fpga for phase-2 RPC trigger), the model has been updated to reconstruct two muons per RPC semi-sector, allowing up to four muons per sector as required by the subsequent MDT trigger. This includes predicting the muons' charge, in addition to their Pt and eta, and the network has been optimized to use information from only four merged RPC planes due to complications with RPC information encoding/decoding.

- From a manpower perspective, Giuliano Gustavino from Rome-1 has expressed interest in contributing to both the L0 and HLT projects, especially for triggers for long-lived particles/displaced jets and Anomaly Detection

- We expect some results in the near furure from toy-simulation data tested on various types of FPGA (U50, U250, U55c) and compared to GPU (V100, A100) and CPU (Xenon and AMD).

# **Update from POKER/NA64 Group**

The status of this activity was on hold as it depended on the actual start of the Open Calls.

Dead line: 29 MAR

The purchased hardware resources MUST BE DEPRECIATED (meaning only the percentage of use over 12 months or whatever it is, over the total life of the item is reimbursed. This obviously makes it less advantageous to acquire hardware resources)."

Alberto Celentano was aware, so we are waiting for the procedure to acquire manpower for the use case

### **Update from TeRABIT FPGA clusters**

- The tender procedure has ended, we have winners.

- INFN has sealed the deal with the winner, it is about to (matter of days) start the actual orders.

- We are significantly behind schedule, but at this point, there should no longer be any hitches or problems.

- We can estimate that the delivery of the machines will not be before the fall.

# **Status KPIs**

#### Link to the flagship document

| KPI ID     | Description                                                                      | Acceptance threshold                                 | Status up to today                           |

|------------|----------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|

| KPI2.2.3.1 | Development of triggering algorithms, on-line analyses, data acquisition on FPGA | 1                                                    | 1 paper already accepted                     |

| KPI2.2.3.2 | Online scouting                                                                  | Submission of 1 paper to a peer-<br>reviewed journal |                                              |

| KPI2.2.3.3 | Development of tools to integrate several FPGAs together                         | Submission of 1 paper to a peer-<br>reviewed journal |                                              |

| KPI2.2.3.4 | Organizing courses about FPGA programming on low and high level                  | At least two courses organized                       | 2 course already taken (2/2 of the KPI done) |