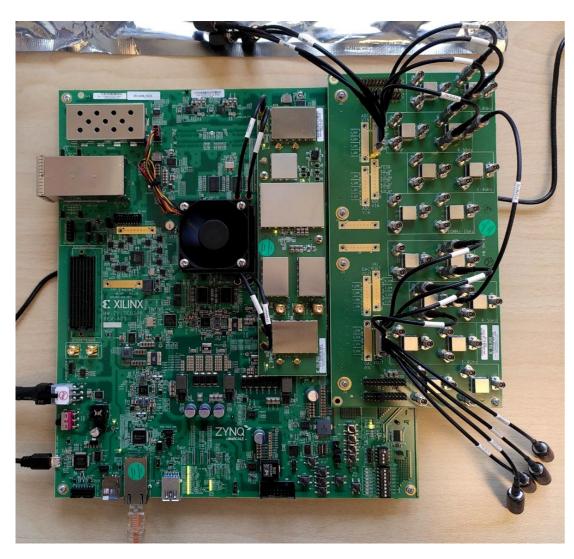

Xilinx ZCU208 RFSoC

### In the context of the QUB-IT Project:

- Procurement of the ZCU208 board

- Installation of PYNQ 3.0.1

- Signals generation and reading tests with PYNQ

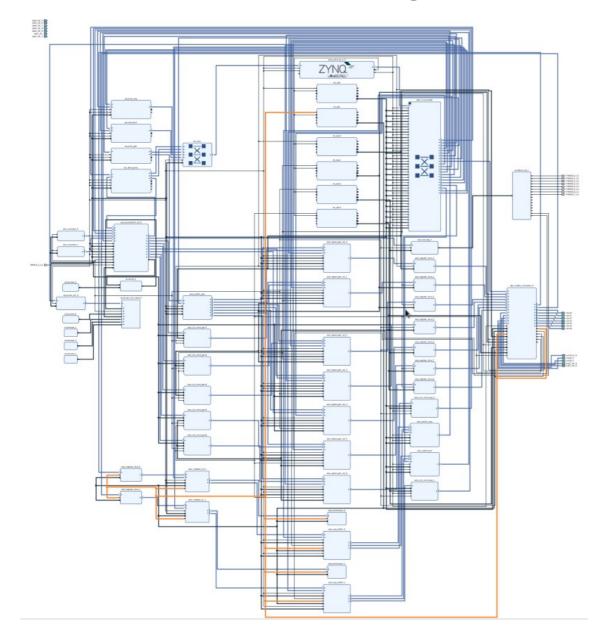

- QICK (0.2.165) firmware and code porting to ZCU208

- Essential interaction with QICK developers

- Most modifications required on the firmware side

-200

Send/receive a pulse with pulse style = const [49]: config={"res ch":6, # --Fixed "ro chs":[0], # --Fixed "reps":1. # -- Fixed Pulse generation seemed to work as expected: 100 clock ticks with a 430MHz "relax\_delay":1.0, # --us "res\_phase":0, # --degrees clock, give a 232ns pulse length with the expected frequency (i.e. 100MHz). "pulse\_style": "const", # --Fixed "length":100, # [Clock ticks] # Try varying length from 10-100 clock ticks "readout length": 100, # [Clock ticks] # Try varying readout length from 50-1000 clock ticks "pulse\_gain":10000, # [DAC units] # Try varying pulse gain from 500 to 30000 DAC units Acq Complete M Pos: 114.0ns MEASURE! "pulse freq": 100, # [MHz] CH1 # In this program the signal is up and downconverted digitally so you won't see any frequency # components in the I/Q traces below. But since the signal gain depends on frequency, Freq # if you lower pulse freq you will see an increased gain. 99,92MHz "adc trig offset": 100, # [Clock ticks] CH1 # Try varying adc trig offset from 100 to 220 clock ticks Period # Try varying soft\_avgs from 1 to 200 averages 10.01ns CH1 None # Try it yourself ! prog =LoopbackProgram(soccfg, config) CH1 iq\_list = prog.acquire\_decimated(soc, load\_pulses=True, progress=True, debug=False) None CH1 [35]: # Plot results plt.figure(1) None for ii, iq in enumerate(iq list): plt.plot(iq[0], label="I value, ADC %d"%(config['ro chs'][ii])) plt.plot(iq[1], label="Q value, ADC %d"%(config['ro chs'][ii])) plt.plot(np.abs(iq[0]+1j\*iq[1]), label="mag, ADC %d"%(config['ro\_chs'][ii])) plt.ylabel("a.u.") plt.xlabel("Clock ticks") plt.title("Averages = " + str(config["soft\_avgs"])) plt.legend() plt.savefig("images/Send\_recieve\_pulse\_const.pdf", dpi=350) Averages = 1 I value, ADC 0 The same signal acquired from ADC on the other hand seemed to be much shorter, Q value, ADC 0 mag, ADC 0

and also the "adc\_trig\_offset" setting seemed not to affect the signal as expected.

GitHub Issue describing some of the important steps for the hardware design porting:

https://github.com/openquantumhardware/qick/issues/57

Further support on the Unitary Fund QICK Discord Channel:

https://discord.com/channels/764231928676089909/103 6774653479362630

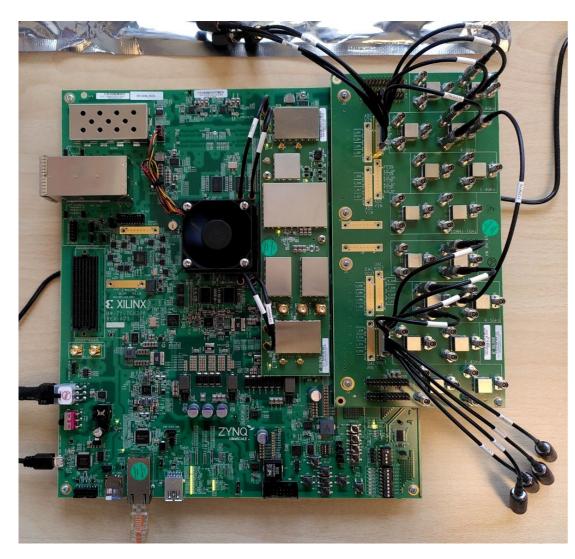

Xilinx ZCU208 RFSoC

### In the context of the QUB-IT Project:

- Procurement of the ZCU208 board

- Installation of PYNQ 3.0.1

- Signals generation and reading tests with PYNQ

- QICK (0.2.165) firmware and code porting to ZCU208

- Essential interaction with QICK developers

- Most modifications required on the firmware side

- Integration of QiboSoq + QICK

- Initially supporting QICK 0.2.135, but 0.2.165 installed... now solved.

- Validation of the QiboSoq + QICK installation

```

[8]: import json

import socket

from qibosoq.client import execute

from qibosoq.components.base import (

OperationCode,

Config

from qibosoq.components.pulses import Rectangular

HOST = "127.0.0.1"

PORT = 6000

pulse 1 = Rectangular(

frequency = 5400, #MHz

amplitude = 0.05,

relative_phase = 0,

start delay = 0,

duration = 0.04.

name = "drive pulse",

type = "drive",

dac = 3,

adc = None

pulse 2 = Rectangular(

frequency = 6400, #MHZ

amplitude = 0.05,

relative phase = 0,

start_delay = 0.04,

duration = 2,

name = "readout_pulse",

type = "readout",

dac = 6,

adc = 0

sequence = [pulse_1, pulse_2]

config = Config()

qubit = Qubit()

server commands = {

"operation code": OperationCode.EXECUTE PULSE SEQUENCE,

"cfg": config,

"sequence": sequence,

"qubits": [qubit],

i, q = execute(server_commands, HOST, PORT)

print(f"{i} + 1j * {q}")

[[20.116858072916667]] + 1j * [[26.813575520833332]]

```

Tests performed both at LNF and Ferrara

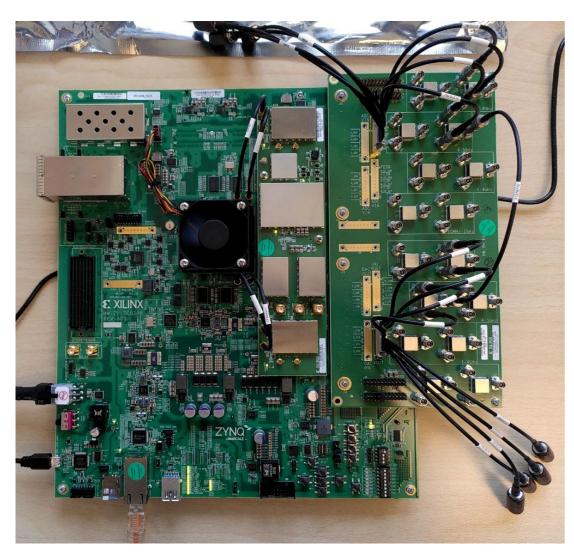

Xilinx ZCU208 RFSoC

### In the context of the QUB-IT Project:

- Procurement of the ZCU208 board

- Installation of PYNQ 3.0.1

- Signals generation and reading tests with PYNQ

- QICK (0.2.165) firmware and code porting to ZCU208

- Essential interaction with QICK developers

- Most modifications required on the firmware side

- Integration of QiboSoq + QICK

- Initially supporting QICK 0.2.135, but 0.2.165 installed... now solved.

- Validation of the QiboSoq + QICK installation

**TODO:** Code cleanup and push to a git repository