# **Testing and Integration** in SR1

Susanne Kühn (CERN), **INFN** Marianna Testa (Frascati), **Benedikt Vormwald** (CERN)

Istituto Nazionale di Fisica Nucleare

DI GENOVA

Andreas Korn

(University College London)

Andreas.Korn@cern.ch

# Disclaimer

- I am by no means an expert on integration

- My view is rather DAQ centric

- Many thanks to Benedikt, Marianne and Susanne for material and suggestions

- Work is due to their efforts, errors are all mine

Andreas Korn

# Overview

- SR1 at CERN

- Major staging and test area

- Slice test

- Prep ongoing, first parts expect this summer

- First test of large scale system

- Integration

- EC to arrive 04/2027

- Bringing the detector together

- Essential health and reception test

- First test of "real" system

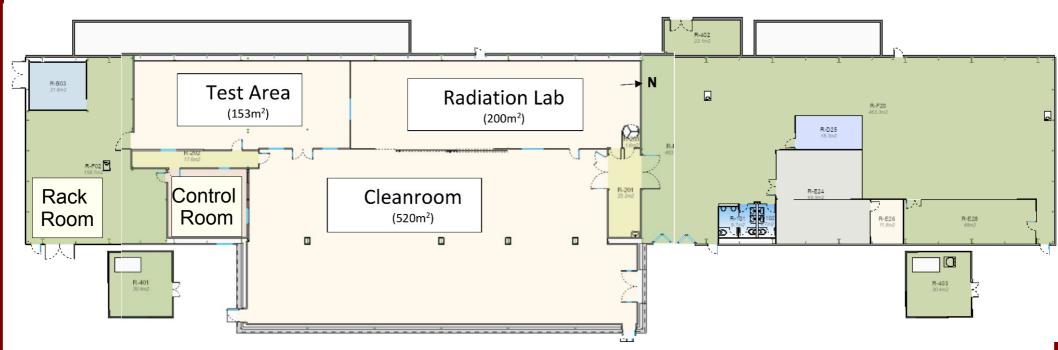

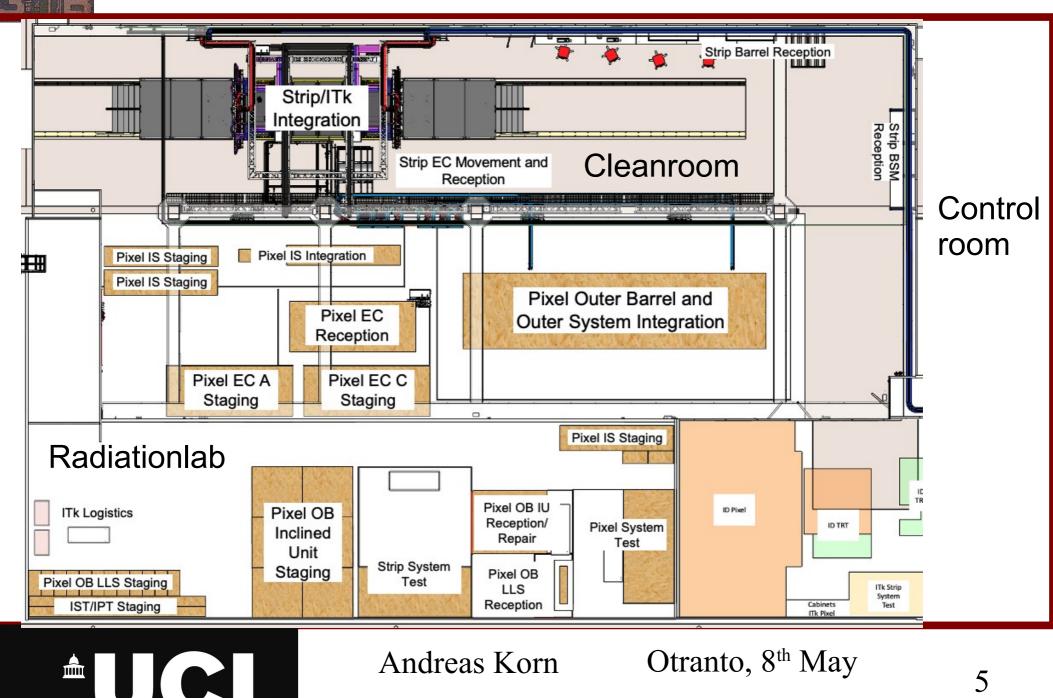

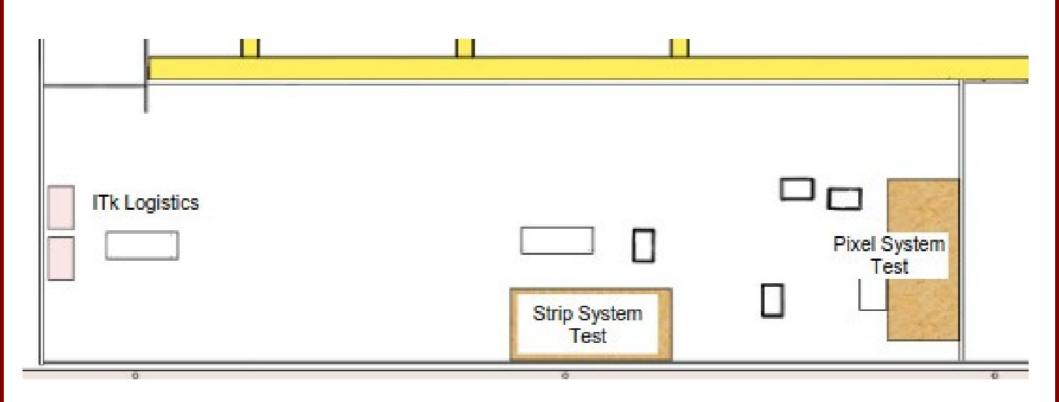

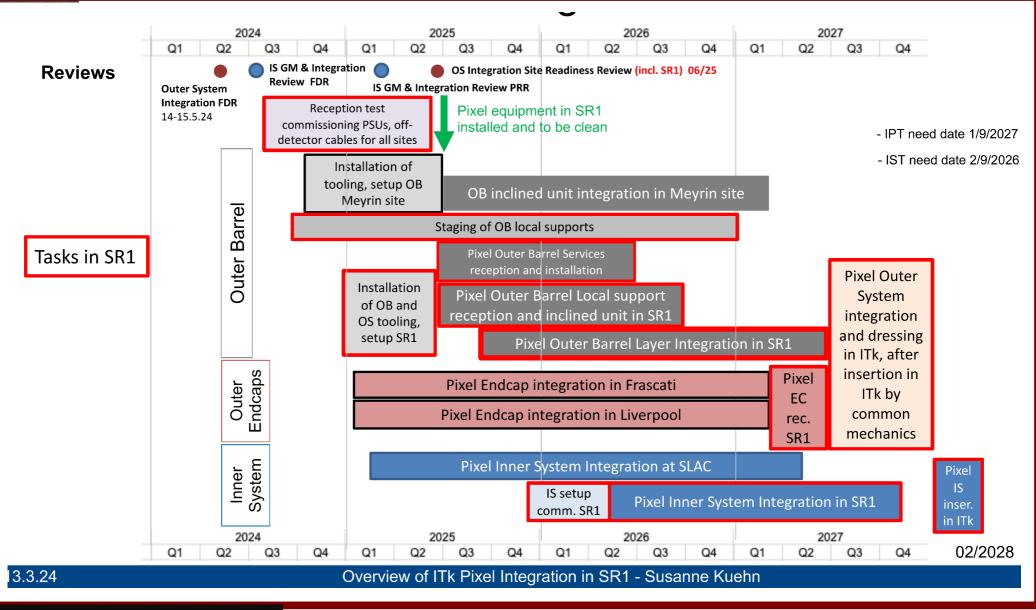

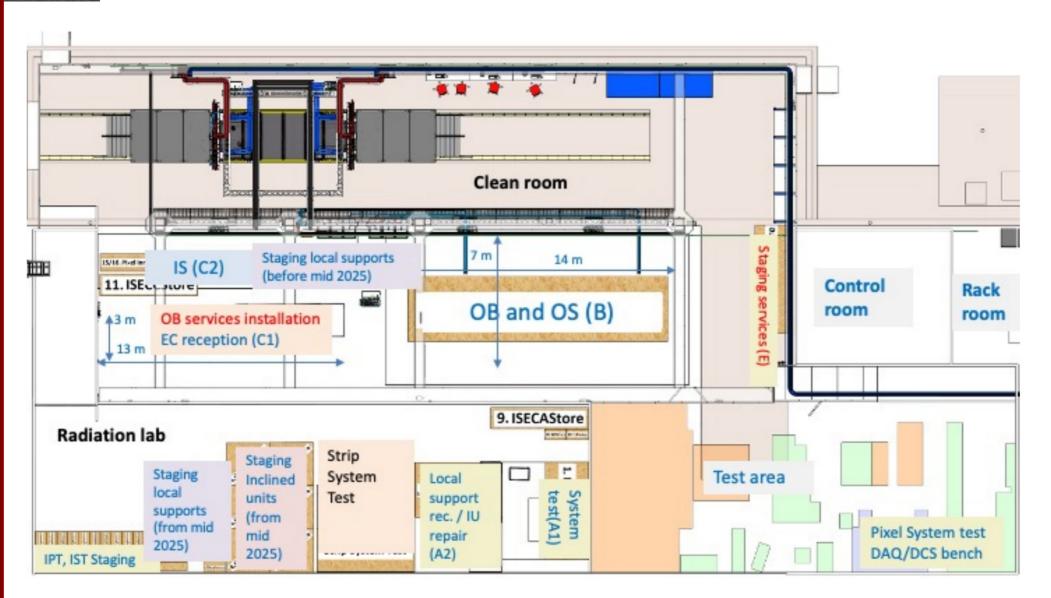

# SR1 Layout

### SR1 Layout

# Slice Test

- In the SR1 Radiationlab at CERN

- Timescale: ongoing, first items expected summer24

- First time to test larger scale system

- First time to test different systems together

- Important testing ground for all systems

- especially DAQ

- "realistic PP1 and on/off-detector cables"

- Very tight timescale  $\rightarrow$  need to use existing systems

- Pre-production power supplies

- pre phase-2 DAQ

# SR1 Radiation lab layout

Andreas Korn

# **Expected Loaded Local Supports**

| LLS type       | modules | SP<br>chains | HV<br>channels | MOPS<br>chips | Tiloc<br>NTCs | power<br>[W] |

|----------------|---------|--------------|----------------|---------------|---------------|--------------|

| EC<br>L2       | 16      | 2            | 4              | 2             | 2             | 163          |

| OB<br>L2 flat  | 36      | 4            | 8              | 4             | 4             | 414          |

| SR1 slice<br>∑ | 52      | 6            | 12             | 6             | 6             | 577          |

- 52 pixel modules (EC: "Ring2")

- Potentially + strip systems

Î

Possibly explore data emulators

#### Overview

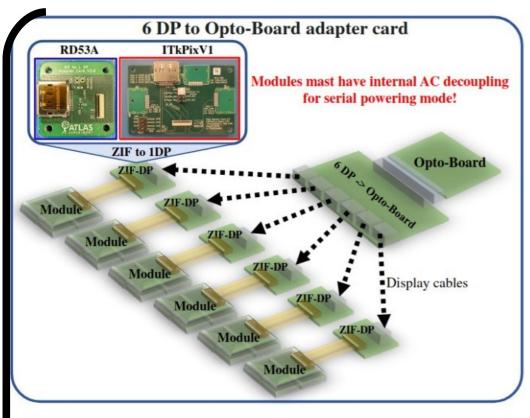

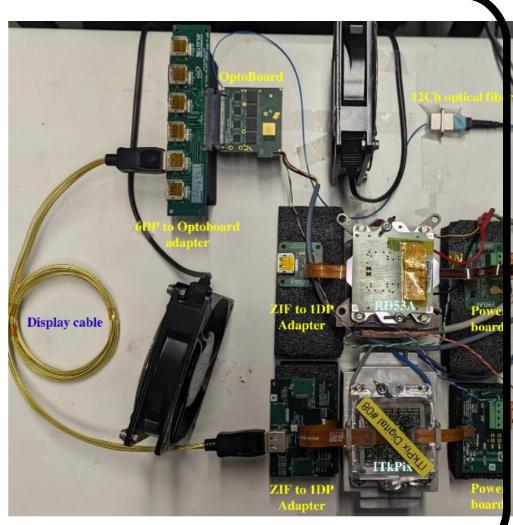

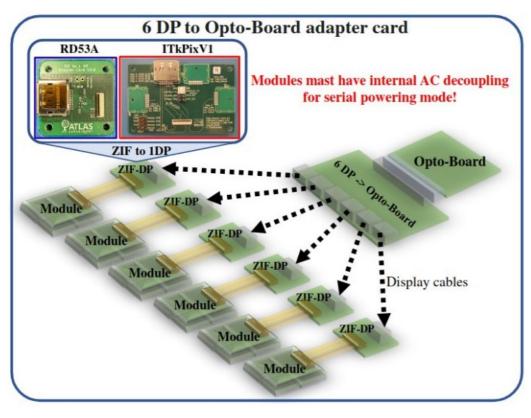

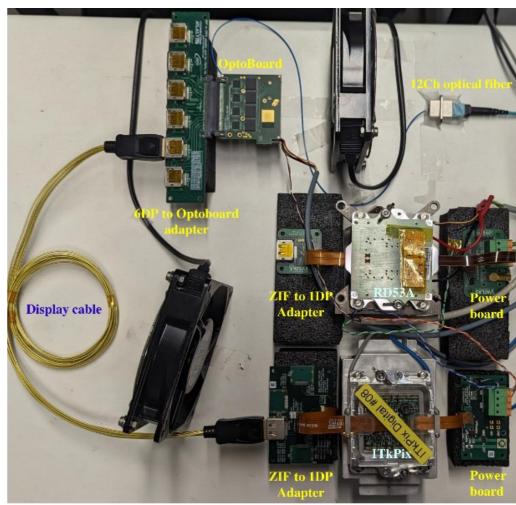

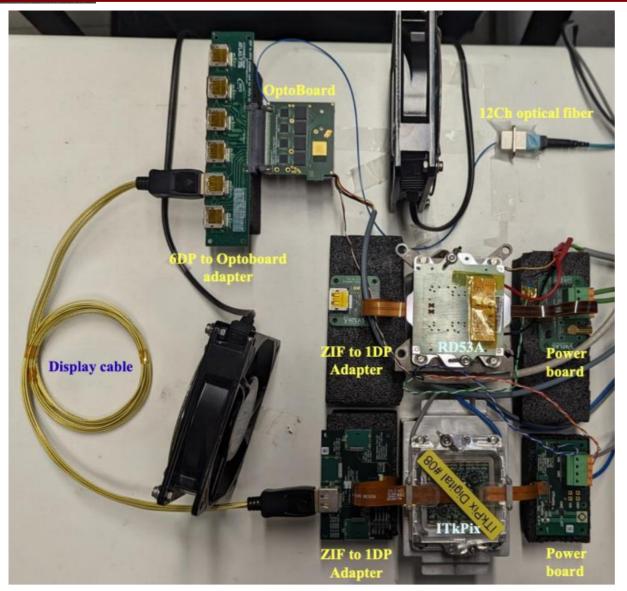

# Zazaboard to Optoboard

Andreas Korn

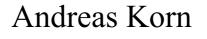

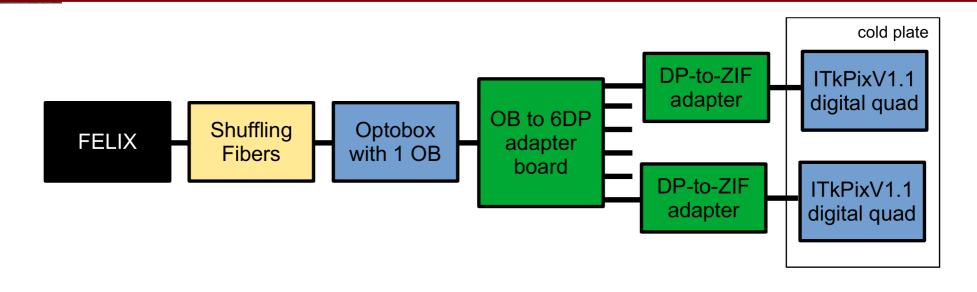

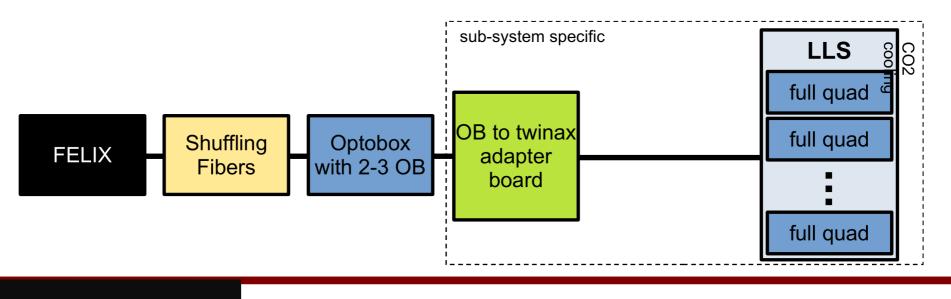

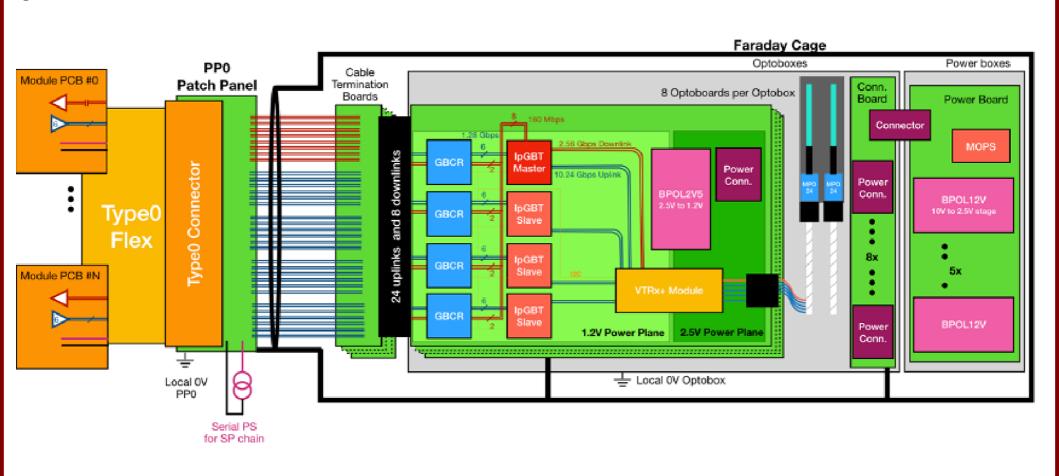

# **Overview: Slice Test Setup**

Hardware Chain – Production

4

# **Readout Overview**

Andreas Korn

12

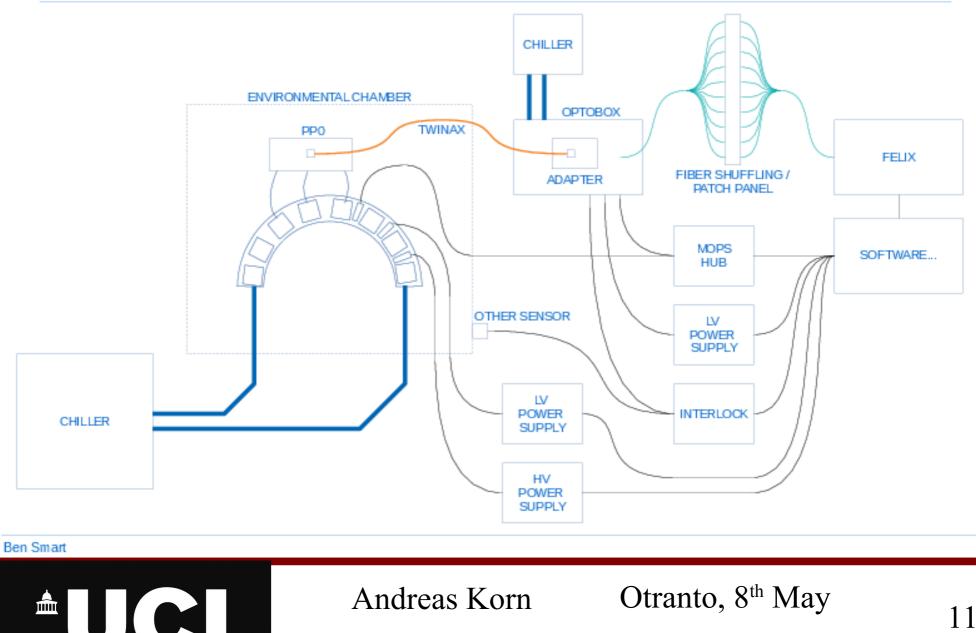

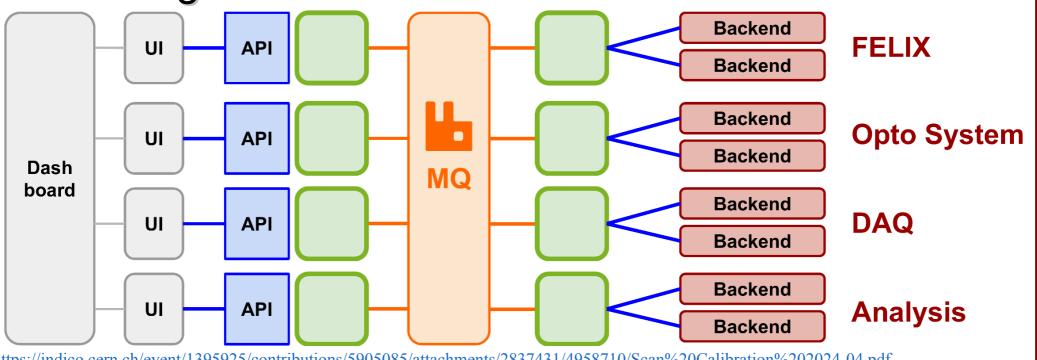

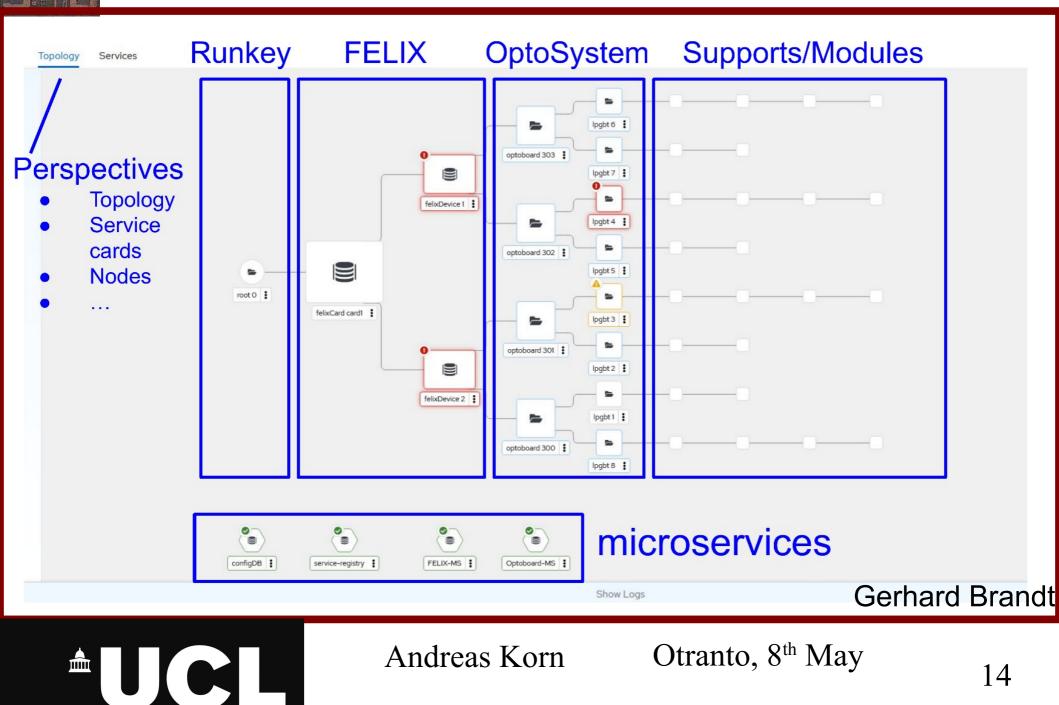

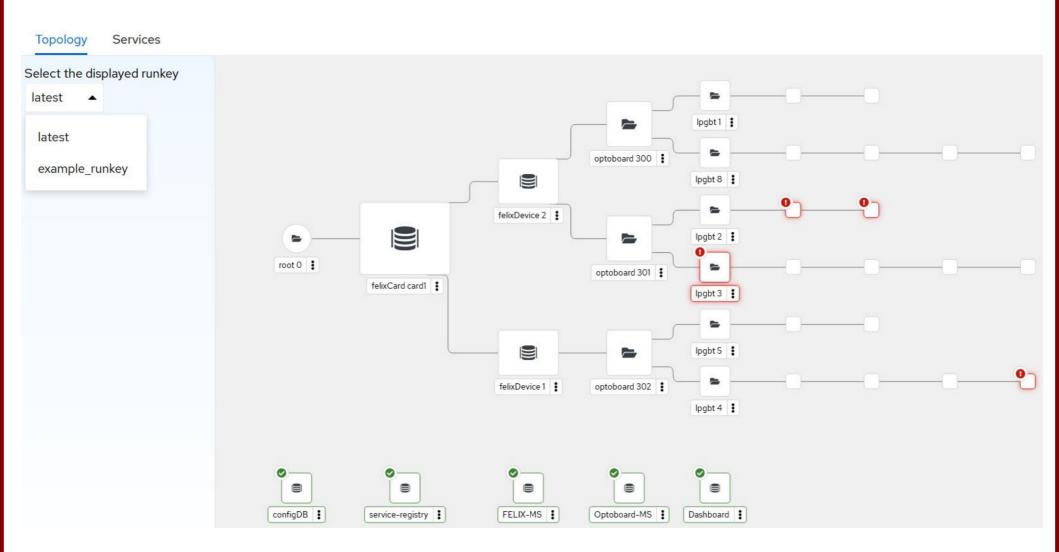

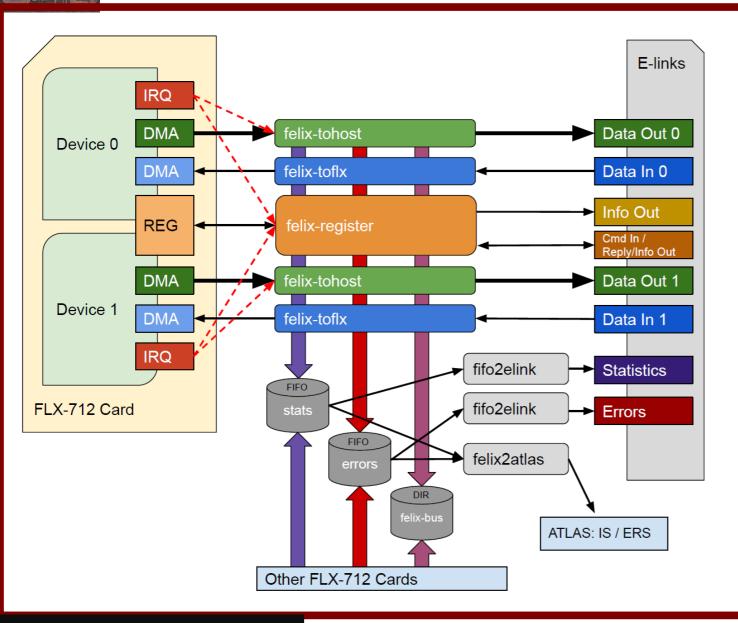

# DAQ Sketch

- Current phase 1 DAQ plan very module QC centric

- Need to scale to multi modules

- Microservices being deployed

- $\rightarrow$  testing and feedback crucial

Gerhard Brandt

https://indico.cern.ch/event/1395925/contributions/5905085/attachments/2837431/4958710/Scan%20Calibration%202024-04.pdf

Andreas Korn

# DAQ/Calibration GUI Sketch

Andreas Korn

# **Expert Panel Example**

| Optoboard GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |                                                                             |                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Configure all Optoboards Edit GUI Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LLSQC-OB7 -                                                                                                                            | Health Celery health                                                        |                                                                                                  |

| OB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                        |                                                                             | 0                                                                                                |

| Select device: Read register Read back:   Ipgbt1 • Select a register •   Write register Read back: •   Select a register • •   Value to be written •   Perform BERT BER limit:   Ublick 0 Mass Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Set Equalization<br>Med Frequency<br>High Frequency<br>Swap polarity<br>Link (Rx/Tx)                                                   | 0 ▼ lpg<br>0 ▼ gb<br>0 ▼ lp<br>gb                                           | Configure<br>Manual selection<br>bt to configure<br>cr to configure<br>Read Status<br>GBT status |

| Uplink         O▼         Meas Time         12▼           2024-04-24         01:57:58,662         - WARNING - CommWrapper.py - ICN           2024-04-24         01:58:00,780         - INFO - celeryTasks.py - Execut           2024-04-24         01:58:00,784         - INFO - celeryTasks.py - Execut           2024-04-24         01:58:00,786         - INFO - celeryTasks.py - run_st           2024-04-24         01:58:00,786         - INFO - celeryTasks.py - Loadin           2024-04-24         01:58:00,788         - WARNING - InitOpto.py - Using           2024-04-24         01:58:00,789         - INFO - InitOpto.py - Current w           2024-04-24         01:58:00,790         - INFO - InitOpto.py - No config           2024-04-24         01:58:00,790         - INFO - InitOpto.py - No config | ing run_startup_task at<br>artup_task executed!<br>g<br>lpgbt-com for IC communi<br>orking directory: /root<br>path provided, using de | worker_ready signal<br>cation with optoboard OB<br>fault configuration file | "debug"<br>"flx_G"<br>"flx_d"<br>"config:<br>"test_me                                            |

Andreas Korn Otranto, 8<sup>th</sup> May

# **Expert Panel Example**

| Home Monitoring FelixOff       |         |              |        |   |                                                                                                                  |   |   |   |   |   |   |    |

|--------------------------------|---------|--------------|--------|---|------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|----|

|                                | Links : | 0            | 1      | 2 | 3                                                                                                                | 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| <b>Optical Power</b>           | тх:     | 4            | ~      | 1 | 1                                                                                                                | ~ | 1 | 1 | 1 | 1 | 1 | ~  |

| Read Advanced                  | RX:     | ~            |        |   |                                                                                                                  |   |   |   |   |   |   |    |

| Optical link alignment<br>Read |         | $\checkmark$ | a<br>o |   | and the second |   |   |   |   |   |   |    |

|                                | 0:      |              |        |   |                                                                                                                  |   |   |   |   |   |   |    |

|                                | 4:      |              |        |   |                                                                                                                  |   |   |   |   |   |   |    |

|                                | 8:      |              |        |   |                                                                                                                  |   |   |   |   |   |   |    |

| lectrical link alignment       | 12 :    |              |        |   |                                                                                                                  |   |   |   |   |   |   |    |

| Read                           | 16:     |              |        |   |                                                                                                                  |   |   |   |   |   |   |    |

|                                | 20:     |              |        |   |                                                                                                                  |   |   |   |   |   |   |    |

|                                | 28 :    | ~            |        |   |                                                                                                                  |   |   |   |   |   |   |    |

|                                | 29:     | ~            |        |   |                                                                                                                  |   |   |   |   |   |   |    |

**L**

Andreas Korn

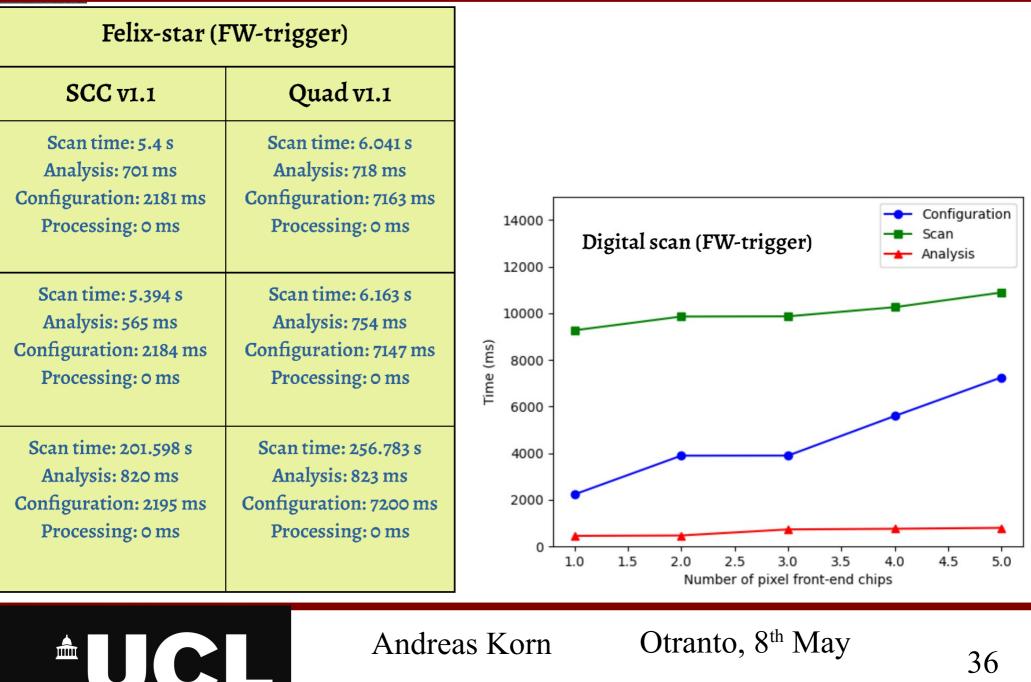

# **DAQ Status**

- A lot of development ongoing, still a lot more needed

- Very limited experience with multi-modules

- Need DB infrastructure

- Need calibration and analysis system

- $\rightarrow$  that can handle larger structures

- Need reliable and fully functional DAQ backend

- Eventually will need optimisation (scan time)

- Slice test is crucial testing ground

- Without thorough testing: DAQ & system will not be ready

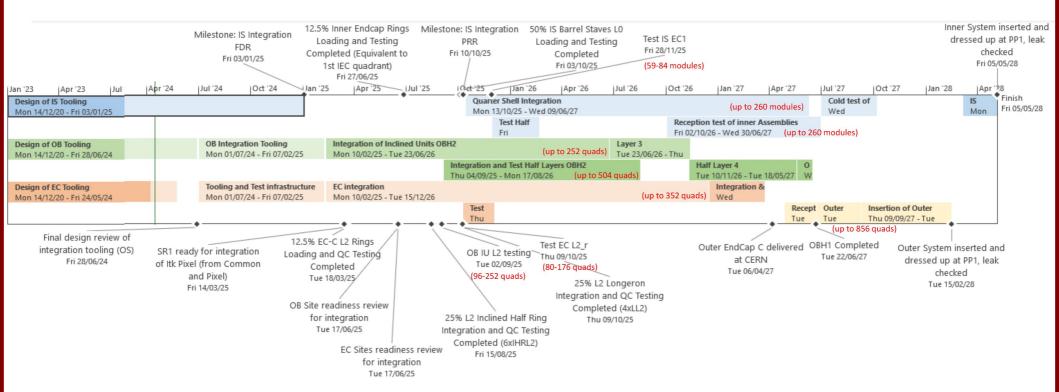

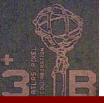

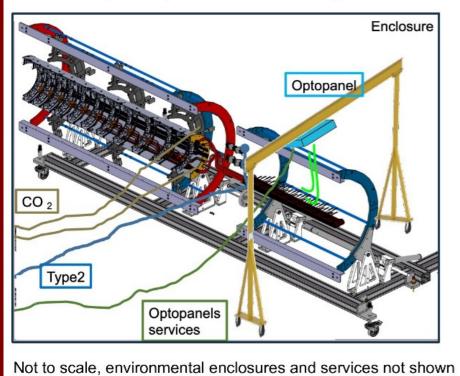

# **Integration Setup**

- Integration in SR1 at CERN

- Installation summer 2024-2025

- Start with Outer Barrel Integration

- Split between bldg. 161 (OB IU) and SR1 (layer)

- Up to 504 quads!

- EC testing in Frascati and Liverpool from 2025

- EC expected to arrive in SR1 ~04/2027

- EC: up to 352 quads

- First EC will be EC C, second EC A

Andreas Korn

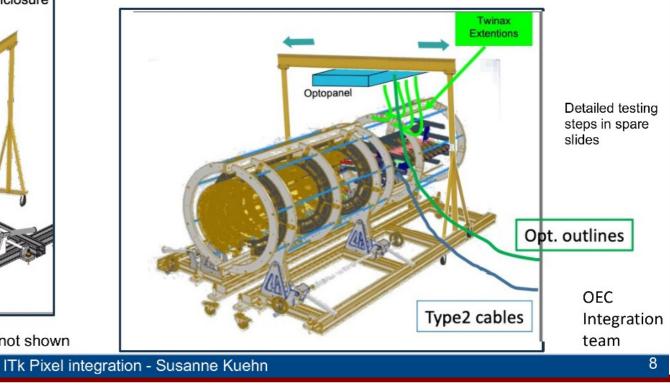

#### Testing timeline in ITk Pixel Integration

Validated DAQ and scan and analysis framework for testing needed to run electrical tests.

Scans are IV, VI, MinHealth<sup>1</sup>, ReducedPixelFailure<sup>1</sup>, Thermaltest based on register read information, some in low power mode.

# **Detailed Timeline**

Andreas Korn

21

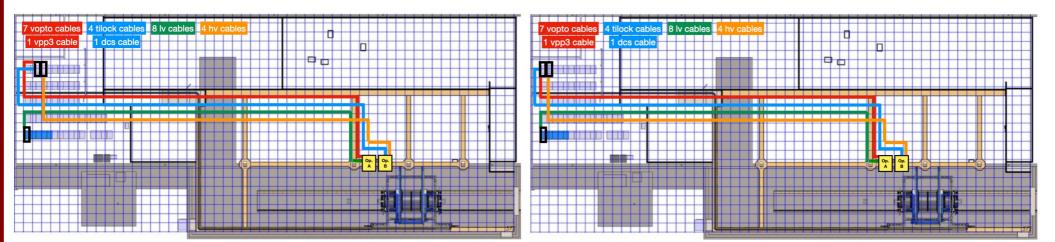

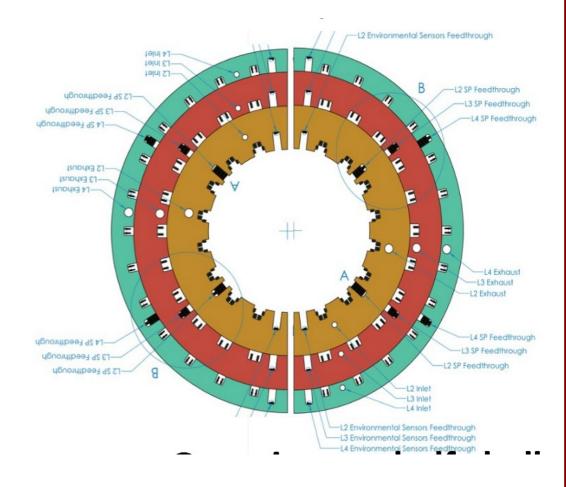

### SR1 Layout

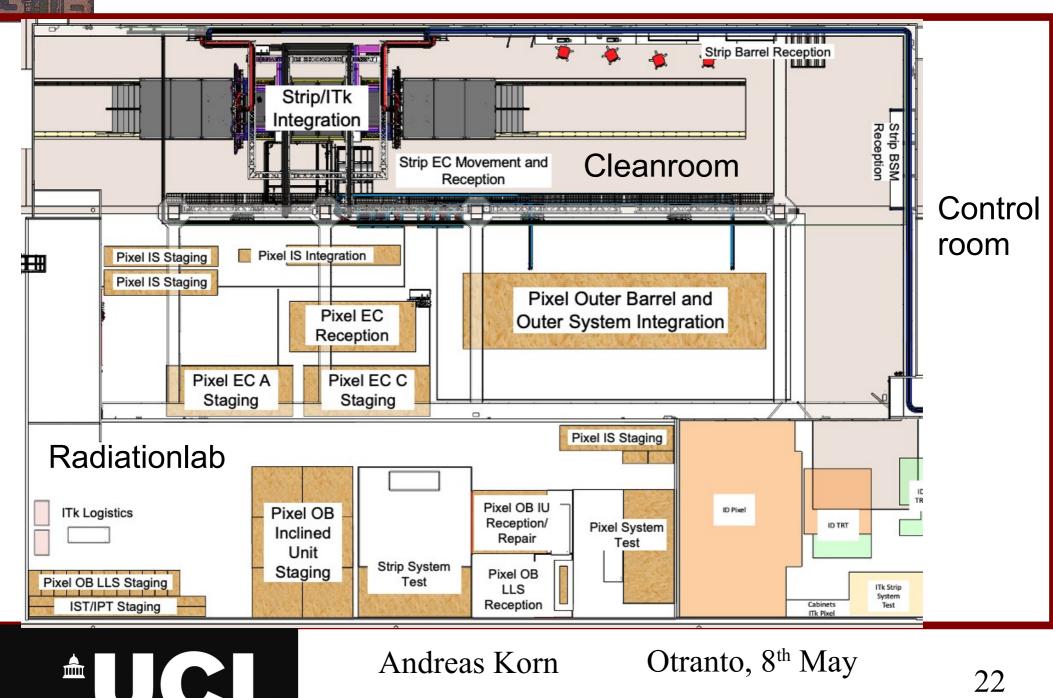

## Services Summary

## **Services Routing**

EC-1

EC-2

Andreas Korn

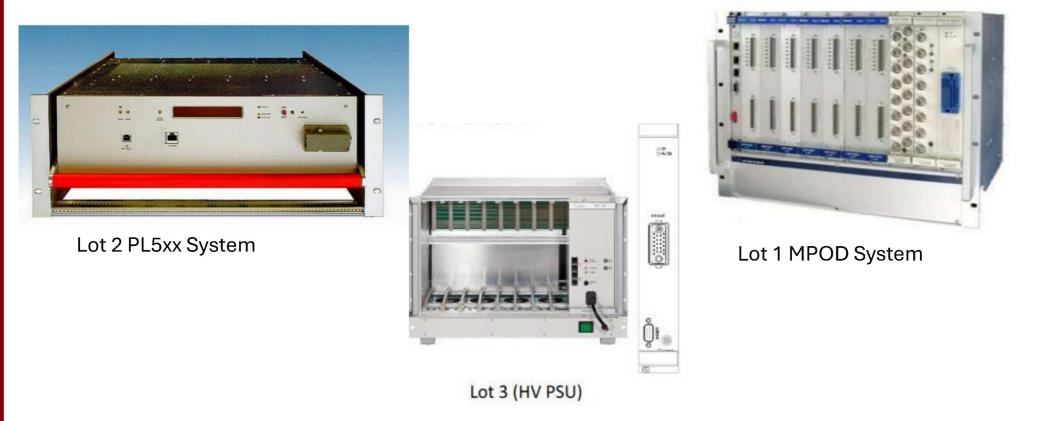

# **Power Supplies**

https://edms.cern.ch/document/2931241/1

Andreas Korn

# Integration Tests

- Performance Test

- Check against existing scan data from LLS tests (https://gitlab.cern.ch/atlas-itk/pixel/module/itkpix-electrical-qc)

- Needs CO2 cooling

- Electrical Low Power Tests with limited cooling

- LP scans, noise

- Read V,T from chip registers

- $\rightarrow$  DAQ register reads essential!

- BER/eye tests

- Ping Test

IIIII

- LV/NTC resistance, Leakage current

- data links resistance/capacitance

.04.2024

#### Electrical Testing Stages in Outer Endcap Integration

Andreas Korn

CERN

- 1. Loaded local support (half-ring) reception test (up to 26 quads)

- 2. Half-rings in half-layer shell all layers in 5 testing steps (in one testing step up to 16 SP-chains, 352 up and 176 down links)

- Testing in normal power and in low power mode foreseen

- 3. Full endcap all layers in 10 testing steps (in one testing step up to 16 SP-chains, 352 up and 176 down links)

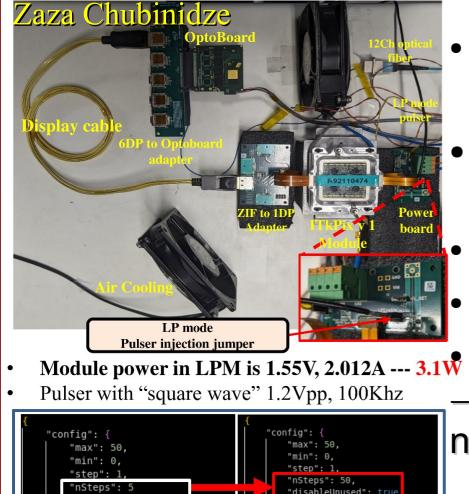

# Low Power Mode Testing

- Half-rings need testing without

CO2 cooling → Low Power mode

- Scan with one enabled CoreColumn at a time

- Analog scans needed?

- 3 Watts can be dissipated by Fans

Limited experience with LP scans → further testing and investigation needed

Chip config: EnCoreCol0/1/2/3 = 0/0/0/0

Modify Scan console config (std analogscan.json)

"loopAction":

"loopAction": "Rd53bCoreColLoop

IIIII

Andreas Korn

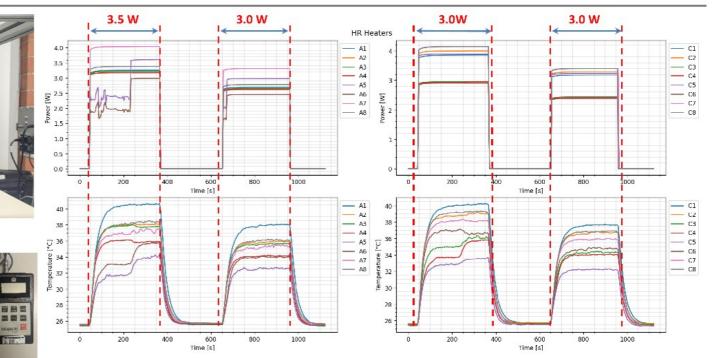

# Low Power Mode Testing

#### Dummy thermal Half Ring on LPM with convection

FAN

HR setup with active Fans

Measure air flow rate near to HR surface

Air velocity >= 4 m/s is enough to maintain T

C1

C2

2.8 5.3 4.2

**C7**

3.3

**C**8

3.2

A5

5.7

A7

3.6

Heaters with P>=3W

Air velocity m/s

- Thermal Half Rings was tested with heaters under **avg 3W and 3.5W** with **active convection**.

- Air flow was vertical directed to HR, where was measured flow rate for **different points of HR by flow meter**.

Otranto, 8<sup>th</sup> May

• The avg heaters temperature are under 40°C.

Zaza Chubinidze

WA I LAJ

https://indico.cern.ch/event/1353986/contributions/5866686/attachments/2823320/4931112/LP%20mode%20testing%20for%20integration%20and%20LLS.pdf

Andreas Korn

- Slice Test in SR1

- crucial testing ground

- Need to use the time to develop large scale system

- Without it we will not be ready for integration

- Integration at SR1

- installation/preparation progressing

- Site readiness review in summer 2025

- Will rely on DAQ and systems being ready

- Need to ensure all functionality (low power, large scale views) available

# Bonus Slides

Andreas Korn

Andreas Korn

#### **Provisions OptoBoards**

Andreas Korn

# Zazaboard to Optoboard

Andreas Korn

**UC**

Andreas Korn

- Grouping per half-shell and per layer

- L2: 11, L3: 8, L4: 9 half-rings

- Manifolding inside PP1: exhausts and supplies of two half-shells combined in one cooling feed-through

- Type-1 services exit per layer

| Testing steps | Detector section |  |  |  |

|---------------|------------------|--|--|--|

| Step 1,6      | 6 HR L2          |  |  |  |

| Step 2,7      | 5 HR L2          |  |  |  |

| Step 3,8      | 8 HR L3          |  |  |  |

| Step 4,9      | 9 HR L4 / 2      |  |  |  |

| Step 5,10     | 9 HR L4 / 2      |  |  |  |

#### Susanne Kühn

Andreas Korn

| Test step | Detector Tested<br>Section           | Number<br>of Serial<br>Power<br>Chains | Number<br>Data<br>(Up/Down<br>) Links | Number<br>of<br>Modules |

|-----------|--------------------------------------|----------------------------------------|---------------------------------------|-------------------------|

| 1/6       | 5 HR L2 (0.5<br>link/FE) left/right  | 10                                     | 160/80                                | 80                      |

| 2/7       | 6 HR L2 (1<br>link/FE) left/right    | 12                                     | 384/96                                | 96                      |

| 3/8       | 8 HR L3 (0.5<br>link/FE) left/right  | 16                                     | 352/176                               | 176                     |

| 4/9       | 4 HR L4 (0.25<br>link/FE) left/right | 8                                      | 104/104                               | 104                     |

| 5/10      | 5 HR L4 (0.5<br>link/FE) left/right  | 10                                     | 182/130                               | 130                     |

Andreas Korn

### SR1 Layout

Andreas Korn

# A Side Step

#### A tool to easily manipulate module and chip configs in python:

python pixel-config-viewer/scripts/manipulate\_config.py -h

usage: manipulate\_config [-h] [-o OUTPUT\_FILE] [-f {Y,YARR,I,ITK}] [-c {0,1,2,3} [{0,1,2,3} ...]] [-e CHIPSENABLED]

[-s {0,1,2,3,7}] [-I {0,1,2,3}] [--enableColumn CORECOLUMN] [--enableAllPix ALL\_PIX]

[--enableColPix startCol endCol value] [--enableRowPix Col startRow endRow value]

connectivity\_file

Easy access, manipulation and conversion of pixel configs

Example:

python pixel-config-viewer/scripts/manipulate\_config.py CONFIGS/L2\_warm\_YARR.json -o itkttest.json --enchips "1001"

https://gitlab.cern.ch/akorn/pixel-config-viewer

Andreas Korn

# A Side Step

#### optional arguments:

-h, --help show this help message and exit -o OUTPUT FILE, --out OUTPUT FILE output file to be written -f {Y,YARR,I,ITK}, --format {Y,YARR,I,ITK} set output file format -c {0,1,2,3} [{0,1,2,3} ...], --chip {0,1,2,3} [{0,1,2,3} ...] apply command to chips -c 0 2 3 -e CHIPSENABLED, --enchips CHIPSENABLED enable only chip 4: --enchips "0001"  $-s \{0,1,2,3,7\}, --speed \{0,1,2,3,7\}$ set readout speed (1280MHz = 0, 640MHz = 1, 320MHz = 2, 160MHz = 3) to all modules -1 {0,1,2,3}, --laneout {0,1,2,3} set lane outtype (HALFCLK = 0, AURORA = 1, PRBS7 = 2, OFF = 3) to all modules --enableColumn CORECOLUMN --enableAllPix ALL PIX set all pixels: --enableAllPix 1 --enableColPix startCol endCol value set pixels in col: --enableColPix startCol endCol 1 --enableRowPix Col startRow endRow value set pixels in row: --enableColPix Col startRow endRow 1

Andreas Korn