# dRICH SiPM bias distribution

## Roberto Preghenella INFN Bologna

ePIC Electronics & DAQ WG meeting 14 March 2024

preghenella@bo.infn.it

#### **Topics of interest**

- <u>Topology</u> of the Bias distribution

- a diagram/schematic illustrating the approach

- <u>Granularity</u> of the Bias supplies

- how many SiPMs (or groupings of) are to be fed from a single Bias supply channel?

- Bias Channel counts and need for distribution chassis

- Temperature dependencies

- Bias compensation, measurement and compensation, etc.

- Bias supply/gain <u>stability and noise requirements</u>

- Configuration controls with reference to SiPM serial numbers

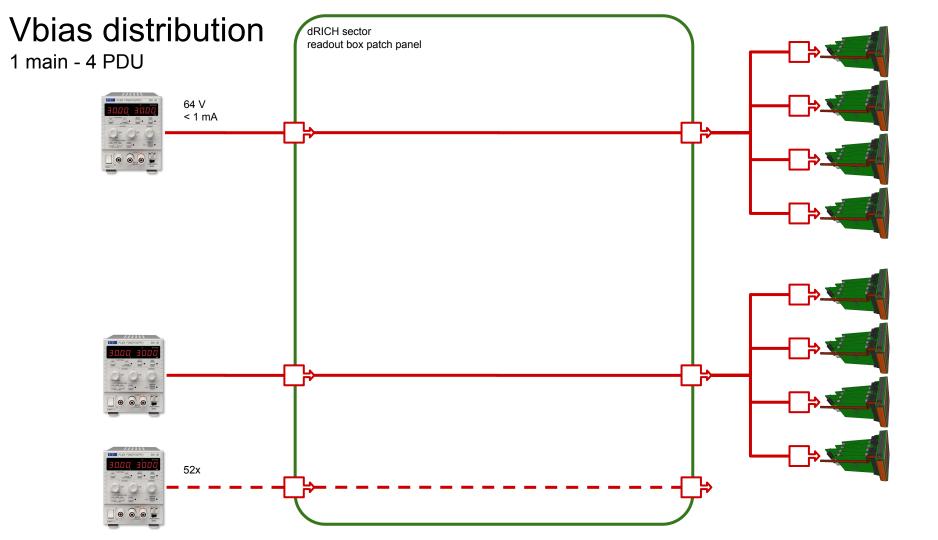

### dRICH bias voltage distribution

#### bias voltage to SiPM sensors we have two bias voltages to distribute to SiPM

#### • HIGH VOLTAGE (Vbias)

- this is the normal operation mode for Physics

- reverse bias to SiPM

- < 55 V

- $\circ$  < 1  $\mu$ A / sensor

#### • ANNEALING VOLTAGE (Vann)

- when doing annealing recovery of radiation damage

- forward bias to SiPM

- <12 V

- o < 150 mA / sensor</p>

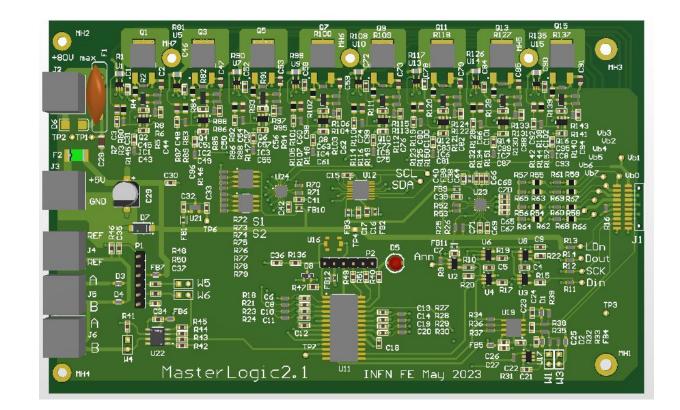

## The Masterlogic v2

we developed and operated in the dRICH beam test in October 2023 the MasterLogic v2 card (evolution of the MasterLogic v1 card).

the card hosts

- 8 channels made of identical circuits for linear regulation of Vbias from 0 to Vin (80 V max)

- a microcontroller (PIC) for external communication (RS485)

- voltage & current monitor

the MasterLogic v2 card hosts more features that are needed for beam test operations. Some of them will be delegated to the RDO, other might be included or dropped.

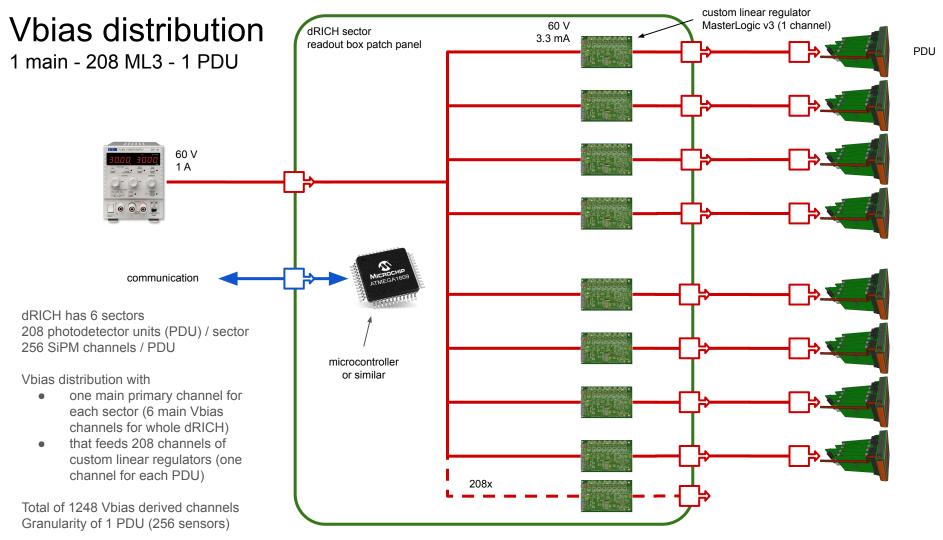

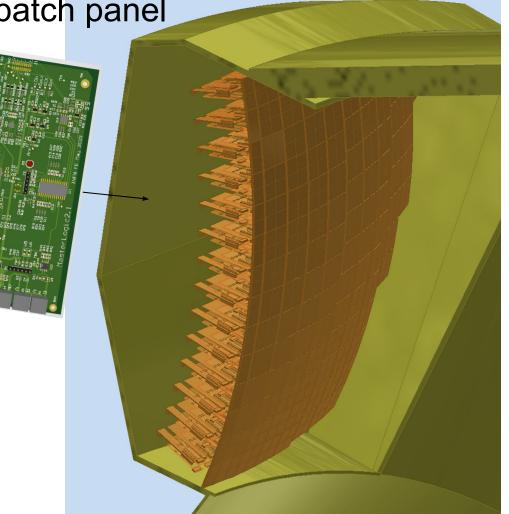

#### The Masterlogic v3 and the patch panel

we developed and operated in the dRICH beam test in October 2023 the MasterLogic v2 card (evolution of the MasterLogic v1 card).

the card hosts

- 8 channels made of identical circuits for linear regulation of Vbias from 0 to Vin (80 V max)

- a microcontroller (PIC) for external communication (RS485)

- current monitor?

- something else?

the MasterLogic v2 card hosts more features that are needed for beam test operations. Some of them will be delegated to the RDO, other might be included or dropped.

a future evolution might be a MasterLogic v3 card to plug onto the dRICH readout box patch panel for Vbias and Vann control and distribution (and perhaps more features).

7

summary table

|                               | 1 main<br>1 PDU | 1 main<br>4 PDU | 1 main<br>52 ML3<br>4 PDU | 1 main<br>208 ML3<br>4 PDU |

|-------------------------------|-----------------|-----------------|---------------------------|----------------------------|

| N <sub>primary</sub>          | 1248            | 312             | 6                         | 6                          |

| N <sub>primary</sub> / sector | 208             | 52              | 1                         | 1                          |

| V <sub>primary</sub> (V)      | 60              | 60              | 60                        | 60                         |

| I <sub>primary</sub> (A)      | < 1 mA          | < 1 mA          | 250 mA                    | 1                          |

| Granularity                   | 256             | 1024            | 1024                      | 256                        |

| uController                   | no              | no              | yes                       | yes                        |

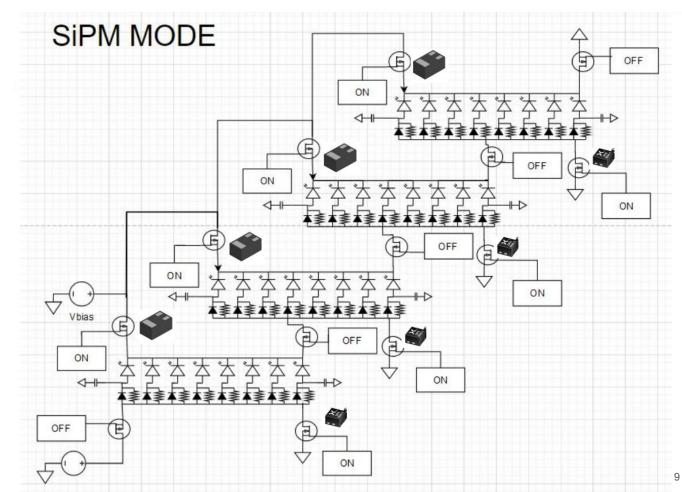

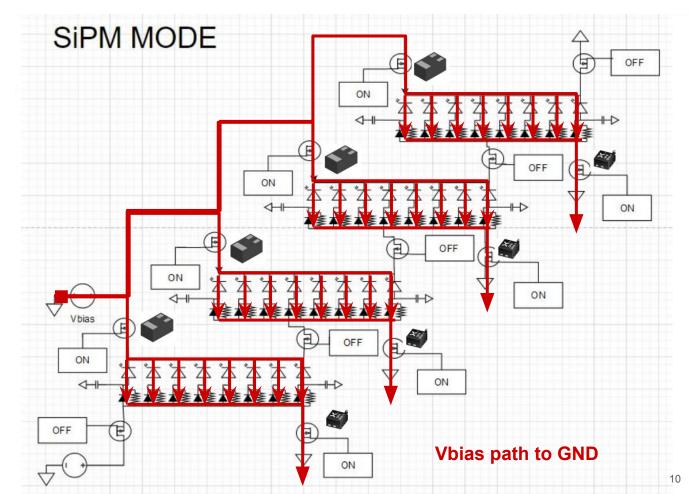

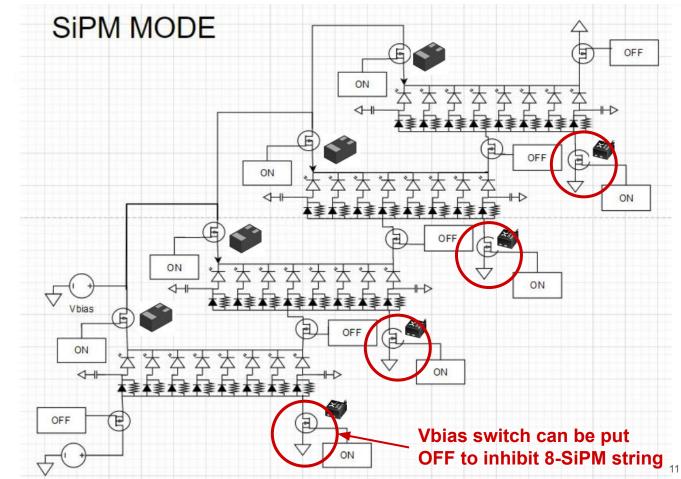

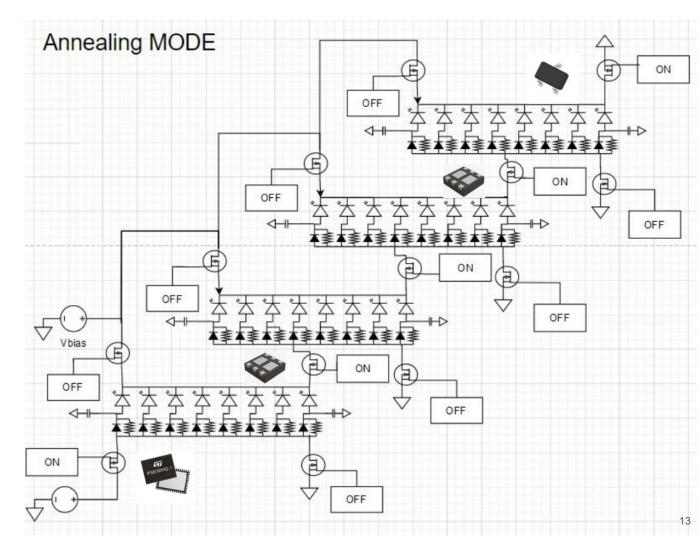

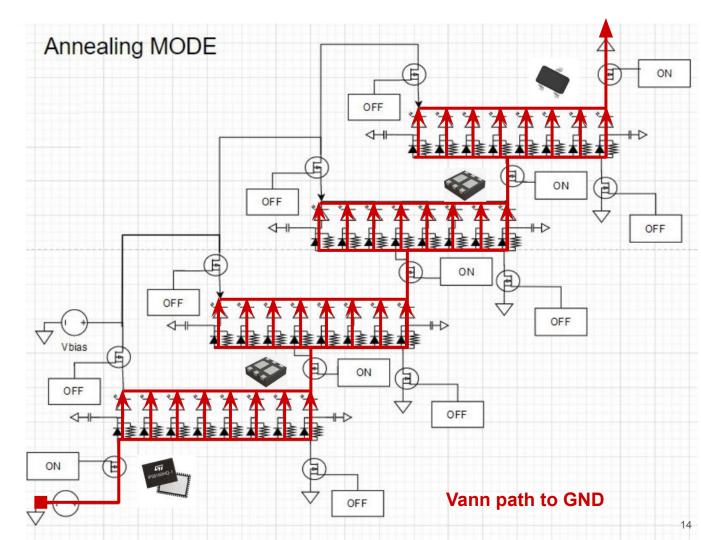

the circuit foreseen to allow both normal operation of SiPM (reverse bias) and self-annealing (forward bias) allows to inhibit the Vbias to a granularity of 8 SiPM.

might come at handy in case of troubles with Vbias distribution in a specific SiPM  $\rightarrow$  inhibit Vbias in a string of 8 SiPM sensors while the rest of the PDU can still be operated

digital switches (MOSFET) controlled by RDO

the circuit foreseen to allow both normal operation of SiPM (reverse bias) and self-annealing (forward bias) allows to inhibit the Vbias to a granularity of 8 SiPM.

might come at hany in case of troubles with Vbias distribution in a specific SiPM  $\rightarrow$  inhibit Vbias in a string of 8 SiPM sensors while the rest of the PDU can still be operated

the circuit foreseen to allow both normal operation of SiPM (reverse bias) and self-annealing (forward bias) allows to inhibit the Vbias to a granularity of 8 SiPM.

might come at handy in case of troubles with Vbias distribution in a specific SiPM  $\rightarrow$  inhibit Vbias in a string of 8 SiPM sensors while the rest of the PDU can still be operated

digital switches (MOSFET) controlled by RDO

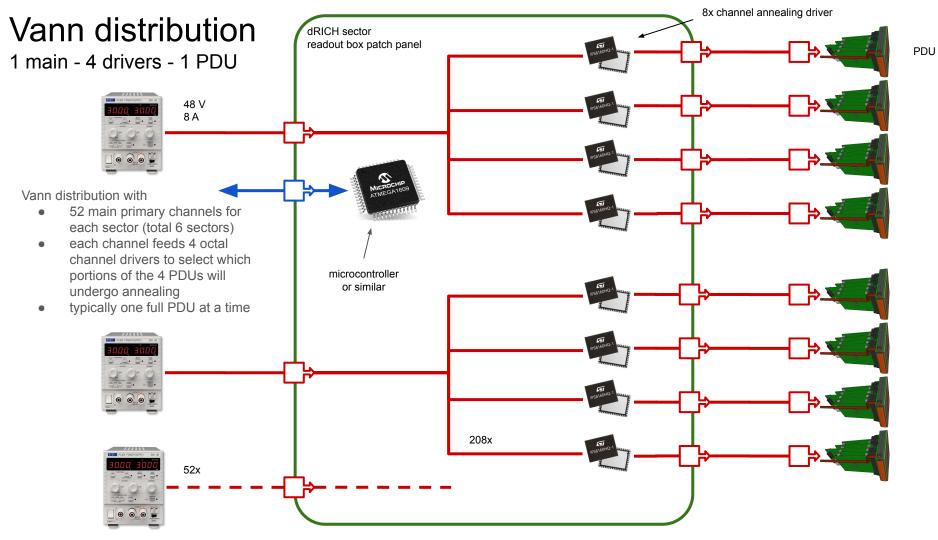

### Vann distribution

forward-bias annealing current for each sensor can reach up to 100 mA to keep annealing current low we foresee to forward-bias the SiPM in series of 4 SiPM strings

note: this approach should work but has to be tested to prove its performance

## Vann distribution

forward-bias annealing current for each sensor can reach up to 100 mA to keep annealing current low we foresee to forward-bias the SiPM in series of 4 SiPM strings

note: this approach should work but has to be tested to prove its performance

### Summary

|                                            | Vbias                             | Vann         |

|--------------------------------------------|-----------------------------------|--------------|

| N <sub>primary</sub>                       | 6 / 312                           | 312          |

| N <sub>primary</sub> / sector              | 1 / 52                            | 52           |

| V <sub>primary</sub>                       | 60 V                              | 48 V         |

| l<br>primary                               | 1 A / 1 mA                        | 8 A          |

| analog grouping<br>voltage regulation      | 256 / 1024                        | 1024         |

| digital grouping<br>capability to turn OFF | 8                                 | 32           |

| T dependence                               | <b>yes</b> measured and regulated | no           |

| stability                                  | < 20 mV                           | < 100 mA     |

| noise ripple                               | < 3 mVpp                          | not critical |

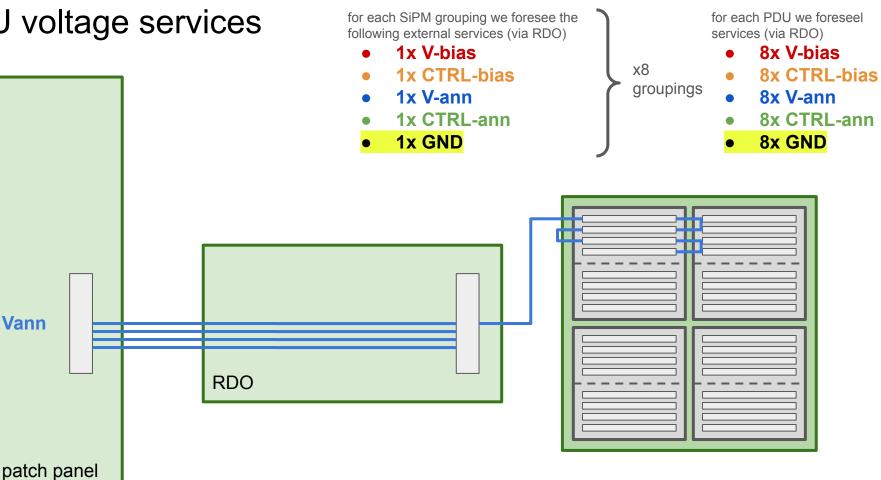

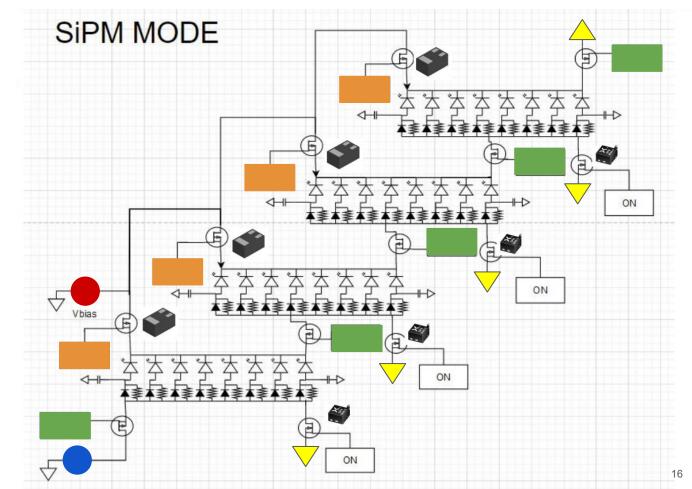

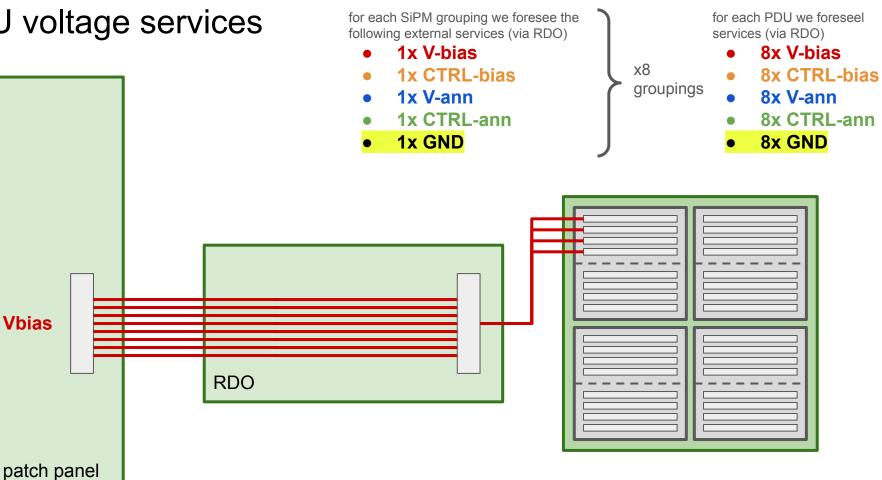

## PDU voltage services

the **<u>SiPM grouping</u>** is composed of 4 strings of 8 SiPM each

one <u>SiPM matrix</u> is composed of two SiPM groupings

the <u>dRICH PDU</u> is composed of four SiPM matrices

for each SiPM grouping we foresee the following external services (via RDO)

- 1 V-bias

- 1 CTRL-bias

- 1 V-ann

- 1 CTRL-ann

- 1 GND

This is a total of 5 wires for each SiPM grouping, namely a total of <u>40 wires for</u> <u>one PDU</u>. The 40 wires enter on the RDO from the readout box patch-panel.

#### PDU voltage services

#### PDU voltage services