### The electronics of the GEM- $\mu$ RWELL Endcap Tracker

#### Roberto Ammendola

INFN Roma Tor Vergata

Giornate Nazionali EIC\_NET - Bologna - 28/6/24

# Introduction to MPGDs electronic developments

- EndCap Tracker shares common electronics and data acquisition approach with other MPGDs detectors:

- development of various levels of electronics

- solutions for power distribution and dissipation

- strategy on cable media type and length and electronics placement

- Hot topics now on discussion (see DAQ meeting on 27/6)

- RM2 and GE personnel started connection in the last weeks with people already involved

- Most of the pictures and informations in these slides are from Saclay group, with permission and many thanks to Irakli M.

# Experiment requirements for MPGD Detectors

- Typical signal 1-1.5 keV resulting to 15-30 fC per channel

- Aimed dynamic range of 10 bits: Signal / noise of 60 dB

- Timing precision of O(10ns)

- $\bullet$  Channel occupancy of  ${\sim}10$  kHz: Including factor 5 of safety margin

- Streaming readout With support of in situ calibration and of on demand readout

- 1.8 T magnetic field

- Mild radiation environment

- ullet TID and neutron fluence after 10 years: 10 krad and  $10^{11} n_{eq}/cm^2$

- 20 MeV proton flux: 100 particle/cm²/s

- Stringent space for detector readout and services

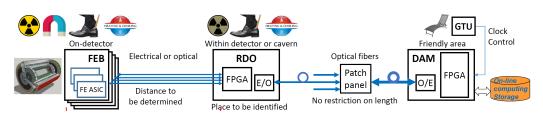

# General Readout Organization

- ullet FEB frontend board with readout ASICs o detector specific, common design among MPGDs detectors, different form factor

- ullet RDO readout module first stage of FEB data aggregation, last stage to dispatch clock & control ullet Mostly common design framework between sub detectors, different form factor

- ullet DAM data aggregation module interface with computing and global timing and control unit (GTU) o Common design for all sub detectors

- Downstream towards detector: clock, control, monitoring

- Upstream towards storage: physics, calibration, monitoring data

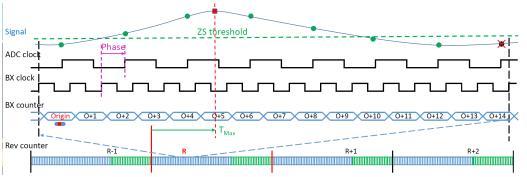

# Readout Strategies for MPGDs

- Signal is continuously sampled with an ADC

- Signal samples above threshold are retained

- ullet Nominal (physics data) readout: signal amplitude and timing is derived o Time of max (as on example) or time of arrival (fitting samples on rising edge)

- ullet On demand readout: signal shapes or raw non ZS data are provided o Calibration, detector studies

- ullet Guarantees best noise immunity and thus best S/N ratio ullet Allows on line common mode noise (CMN) subtraction before ZS

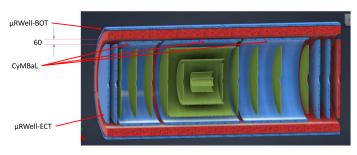

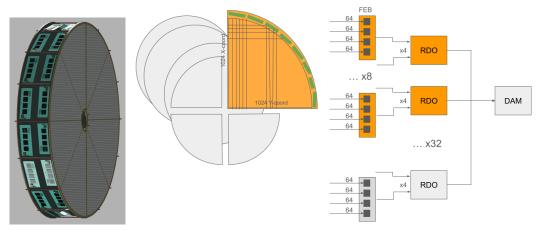

# **EndCap Tracker Figures**

- 4 disks each composed of 4 quadrants

- Each quadrant has 1024 X-strip and 1024 Y-strip (2048 channels)

- $\bullet$  Assuming FE ASIC is 64 channels, grouped in 4 chips FEB, 4 to 1 connection FEB-RDO

- Each quadrant will need 32 ASICs, 8 FEBs, 2 RDOs

- Total amount for ECT is 32k Channels, 512 ASICs, 128 FEBs, 32 RDOs

# EndCap Tracker Data Bandwidth Estimations

- Physics Data: support two zero suppression modes

- $\bullet$  Nominal: peak finding readout  $\rightarrow$  12 bit amplitude, 12 bit time of max, 8 bit ToT

- $\bullet$  On demand: full signal shape readout  $\to$  All samples (12 bit) above threshold (typically 15-25 samples)

- Estimated Physics data bandwidth per Salsa ASIC with channel rate 10 kHz:

- Peak finding 40 Mbit/s

- Signal shape 265 Mbit/s

- On line calibration: on demand readout

- Programmable number of non ZS samples

- ullet Estimated calibration data bandwidth per ASIC  $\sim$  6 Mbit/s

- $\bullet$  FEB RDO link occupancy:  $\sim$ 30 % of one 1 Gbit link

- Overall physics frontend data of ECT:

- ullet  $\sim$  130 Gbit/s for on demand mode

- ullet  $\sim$  37 Gbit/s for nominal mode

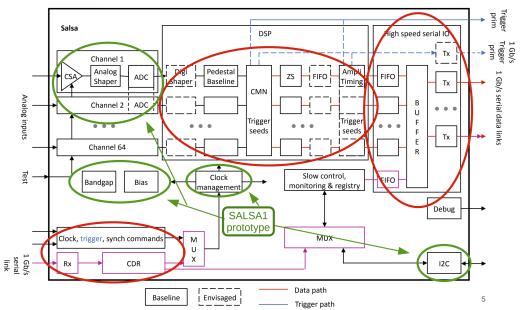

### SALSA ASIC Characteristics

- Versatile front-end characteristics

- Dedicated to MPGD detectors and beyond

- 64 channels

- Large range of peaking times: 50-500 ns

- $\bullet$  Large choice of gain ranges: 0-50, 0-250, 0-500 fC or 0-5 pC

- $\bullet$  Large range of input rates, up to 100 kHz/ch with fast CSA reset (limit assumed for EPIC: 25 kHz/ch)

- Front-end elements can be by-passed

- Digital stage

- $\bullet$  Fast sampling ADC for each channel on 12 bits (¿ 10 effective bits) at up to 50 MS/s

- Possibility under study to double rates by coupling pairs of channels

- Integrated DSP for internal data processing and size reduction, treatment processes to be selected according to user needs

- Continuous readout compatible with streaming DAQ foreseen at EIC, triggered mode also available

- Several 1 Gb/s output data links (will use one)

- General characteristics

- ullet  $\sim \! 1 \ \text{cm}^2$  die size, implemented on modern TSMC 65nm technology

- Low power consumption 15 mW/channel at 1.2V

- Radiation hardened (SEU, TID)

#### SALSA ASIC Characteristics

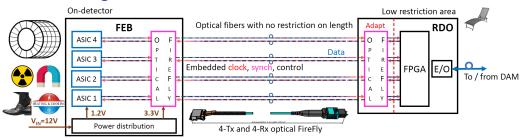

### Aimed FEB Design

- ASICs directly connected to 4 lane bidirectional parallel optic FireFly transceivers from Samtec

- $\bullet$  Single 1 Gbit /s Rx line encoding clock, sync run control and asynchronous slow control and monitoring commands

- Single 1 Gbit /s Tx line for physics, calibration, control and monitoring data

- Low active component count

- Easier to adapt to challenging on detector environment

- Samtec FireFly: reported to stand TID of 50-100 krad and neutron fluence of at least  $5\times 10^{11}n_{eq}/cm^2$

- RDO can be placed anywhere in experimental hall with no particular environmental restrictions

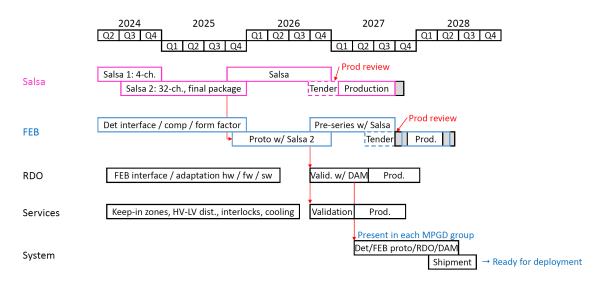

### developement planning

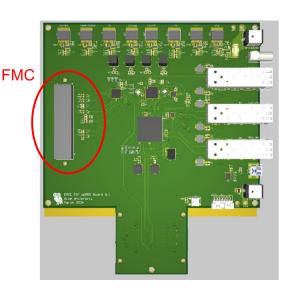

# RDO development via eRD109 (ppRDO)

- Aim is to produce a generalized RDO using the Xilinx Artix Ultrascale+ FPGA

- Used to finalize the timing distribution schemes

- It has an FMC connector and at least one 10gb connection (IpGBT to DAM)

- Allows flexibility with developing custom FMC daugher card for custom interconnections

- ppRDO is in the production stage

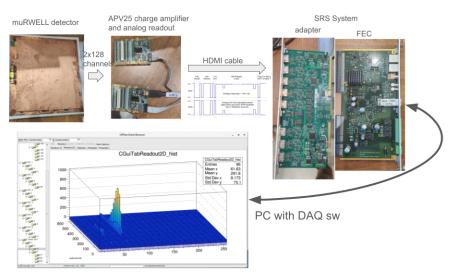

# **Experimental Setup**

Our Setup in LNF for preliminary development of muRWELL detector

Collected second-hand material from 2012

### Summary and Conclusions

- interaction with other MPGDs groups started

- a clear picture of the subsystem and how to fit it at global level is on the way

- we are driven by other groups timelines

- in charge of our group will be the form factor customization of FEB

- to evaluate a customization of RDO if needed

- need to find a way to start operate on other groups technology (SALSA, RDO) before it is already available

- emulate (part of) SALSA and RDO on COTS

- perform transition from actual experimental setup to production hardware