# Upgrade di Fase 2 dell'elettronica di readout ATLAS per il calorimetro ad Argon Liquido di ATLAS

Antonio CARBONE (Università degli Studi & INFN Milano) A nome del gruppo del calorimetro ad Argon Liquido di ATLAS

#### 1. Introduzione

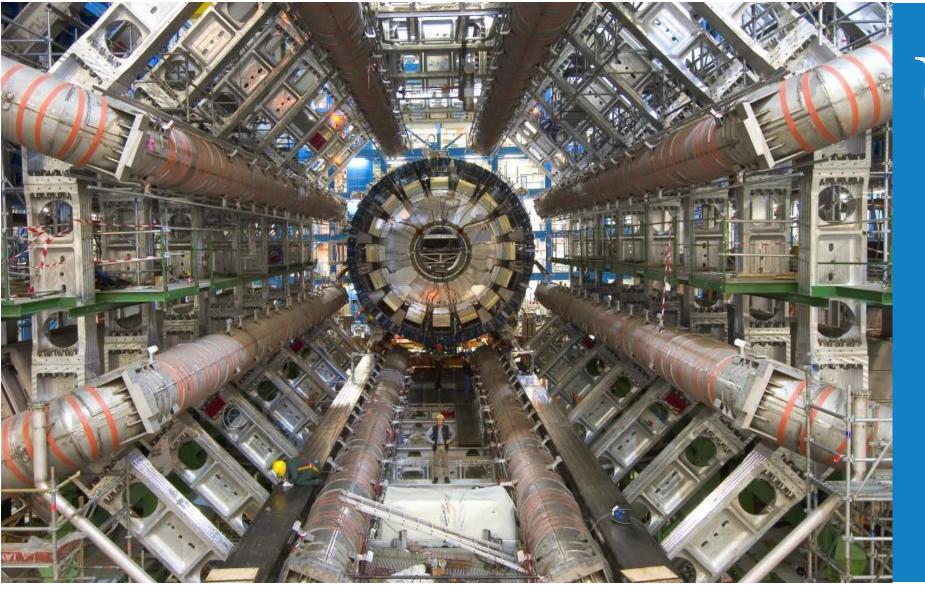

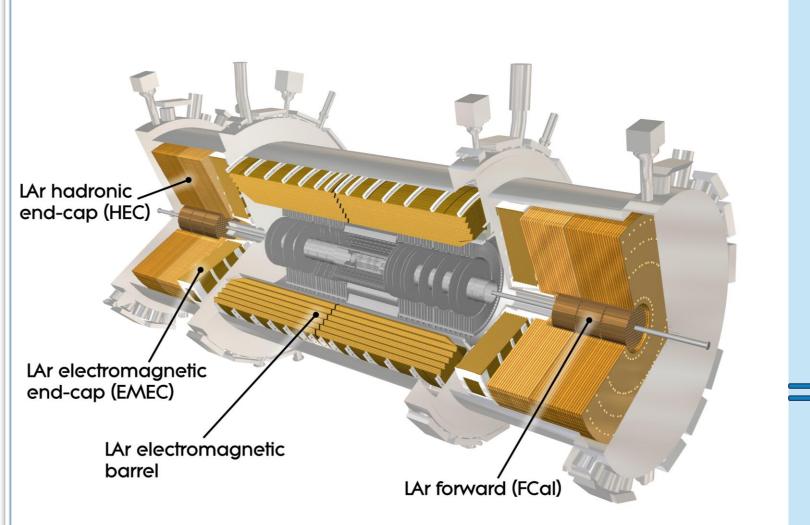

#### Calorimetro ad Argon Liquido (LAr) di ATLAS

- Calorimetro a campionamento basato su Argon Liquido come mezzo attivo.

- Misura energia, posizione e tempo dello sciame elettromagnetico (elettroni e fotoni) + getti adronici [1].

#### **Calorimetro EM** (barrel + endcap)

- Piombo + LAr

- 173,312 Canali di lettura

- Copertura:  $|\eta| < 3.2$

#### **Endcap Adronico** (HEC)

**Forward Calorimeter** (FCal)

- Rame/Tungsteno + LAr

- 3524 Canali di lettura

- Rame + LAr - 5632 Canali di lettura

- Copertura:  $1.5 < |\eta| < 3.2$

- Copertura:  $3.1 < |\eta| < 4.9$

- 182,468 celle!

COLUTAV4

Work in progress

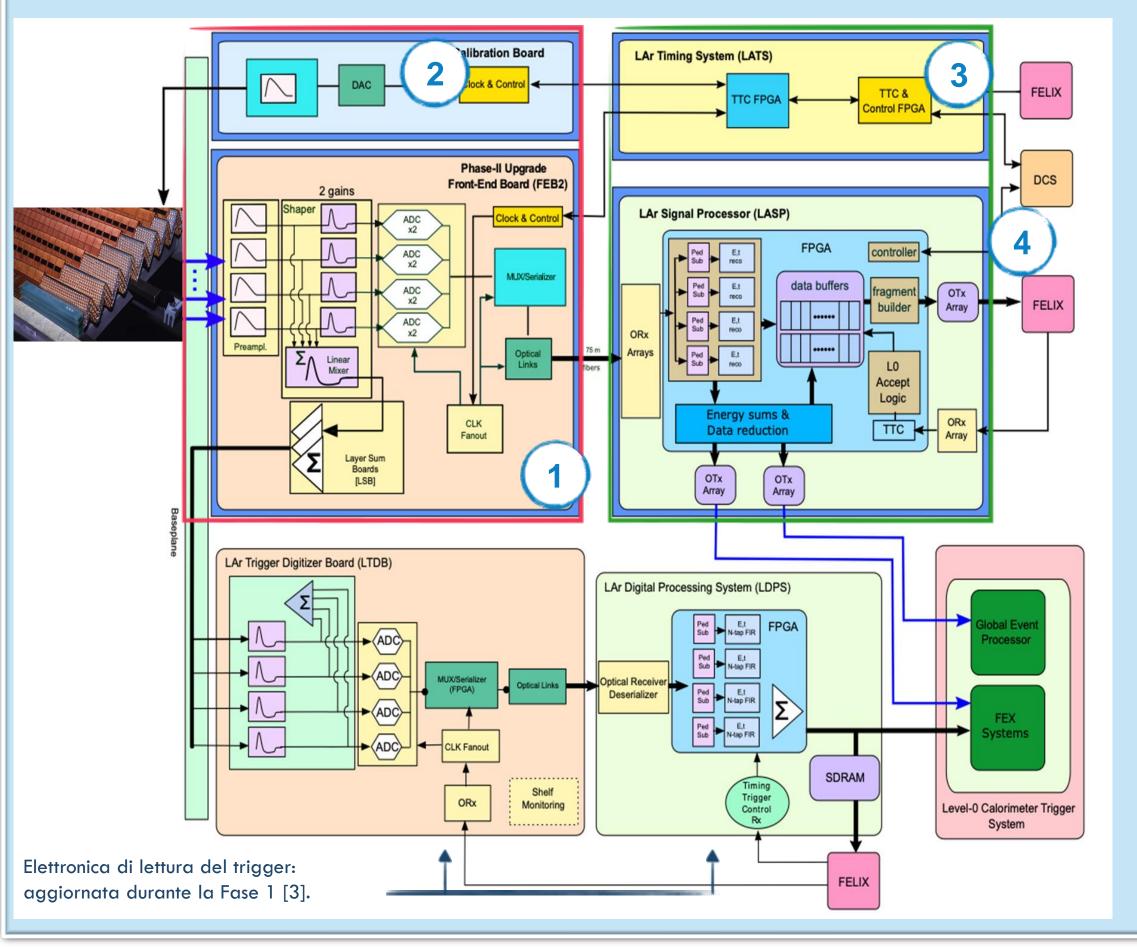

Elettronica di lettura Campiona a 40 MHz e invia I dati fuori dal rivelatore per analisi e trigger

#### Fase di alta luminosità di LHC (HL-LHC)

- Luminosità istantanea fino a  $7 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> = 7 × della luminosità attuale.

- Ambiente operativo molto impegnativo [1].

- Il Sistema ATLAS TDAQ deve gestire fino ~200 interazioni pp ( $\langle \mu \rangle$ ) simultaneamente.

- Maggiore tolleranza alle radiazioni per l'elettronica sul rilevatore.

#### DA LHC... A HL-LHC! LS 3 Run 2 Run 4 Run 3 **ATLAS ATLAS** • • • **(μ) ~ 200** (μ) ~ 34 Phase-1 **⟨μ⟩ ~ 60** Phase-2 2022 2015 2018 2026 2029 NOI SIAMO QUI

## 2. Aggiornamento di Fase 2 del LAr

- Per poter gestire il volume di dati di HL-LHC, è necessario riprogettare e sostituire l'elettronica on-detector e off-detector [2].

- Sarà installata durante il Long Shutdown (LS) 3.

# 3. Elettronica on detector (1)

# Scheda di Front-end (FEB2)

- Riceve il segnale dalle celle del calorimetro ed esegue l'elaborazione analogica.

- I segnali vengono digitalizzati, serializzati e trasmessi al di fuori del rilevatore tramite il protocollo IpGBT.

- 1524 FEB2s con 128 canali ciascuno.

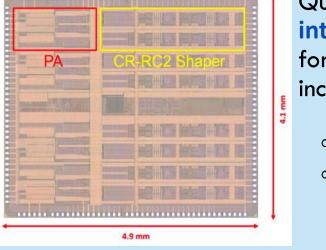

ASIC custom ALFE2: Preamplificatore/Shaper (PA/S)

Questo circuito integrato fornisce l'amplificazione di segnali con due intervalli di guadagno sovrapposti (alto e basso) utilizzando la formatura CR-(RC)<sup>2</sup>. Sarà fabbricato in tecnologia CMOS a 130 nm e incorpora una funzione di somma a 4 canali per il trigger.

- $_{\circ}$  Non linearità < 0.1% e rumore < 350 nA per i canali a 10 mA. o Resistenza alle radiazioni: funzionante dopo dosi di 12 kGy.

- **ALFE2 soddisfa le specifiche!**

ASIC custom COLUTAv4: Convertitore Anaogico-Digitale (ADC)

Converte le uscite PA/S in digitale a 40 MHz con una gamma dinamica di 16 bit e un numero effettivo di bit (ENOB) > 11, gestendo 8 canali (4 LAr x 2 guadagni) in tecnologia CMOS da 65 nm.

sinusoidale di 2 MHz.

Ottime prestazioni di uniformità con l'iniezione di un'onda

Basso rumore di piedistallo: RMS di 12 conteggi ADC.

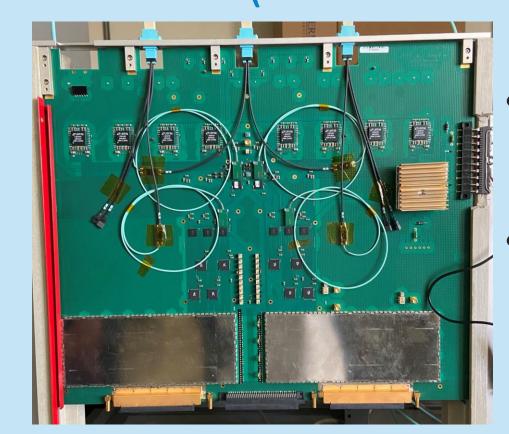

## FEB2 test (Slice Test Board)

- Sono state testate varie soluzioni, con

l'alimentazione sulla scheda da 48 V alle

l'aiuto di **mezzanine**, per **ridurre**

Distribuzione di potenza

Slice board con 32 canali (1 / 4 of FEB2) con la stessa densità della scheda finale FEB2.

Utilizzata per caratterizzare energia e tempo, linearità, e prestazioni multicanale.

tensioni necessarie per gli ASIC. Work in progress

Livello di rumore sotto controllo con soluzioni radiation-soft.

#### Prospettive

Risultati chiave

- Sono in corso test su una scheda totalmente popolata con soluzioni resistenti.

- alle radiazioni sviluppate dal CERN utilizzando bPOL48V + bPOL12V.

- Nuova versione della FEB2 con 128 canali completamente popolati sotto test.

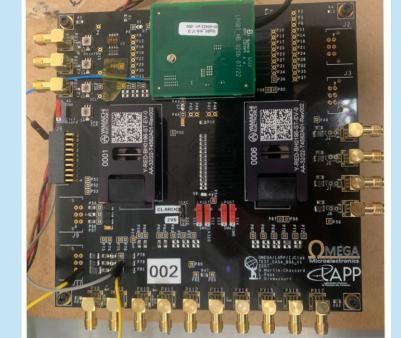

## Scheda di calibrazione (2)

- Inietta segnali noti per calibrare l'elettronica di lettura.

- Deve coprire l'intera gamma dinamica (320 mA, fino a 7,5 V in uscita): richiede la tecnologia HV-CMOS.

- Sono necessarie 122 schede con 128 canali per calibrare 182.468 celle!

ASIC custom CLAROCv4

Crea l'impulso aprendo un interruttore ad alta frequenza (HF) (basato sulla tecnologia XFAB a 180 nm).

ASIC custom LADOCv2

Convertitore digitale-analogico a 16 bit, comanda HF (basato sulla tecnologia TSMC a 130 nm).

Risultati chiave

- Entrambi gli ASIC soddisfano i requisiti di linearità (non linearità < 0.1% fino a 300 GeV). Sono sotto test i risultati dei test TID degli ASIC.

- LADOCv2b, versione finale: chip in produzione. CLAROCv4b sottomesso.

Prospettive

Scheda di calibrazione (CABANEv2): secondo prototipo in produzione.

### 4. Elettronica off detector

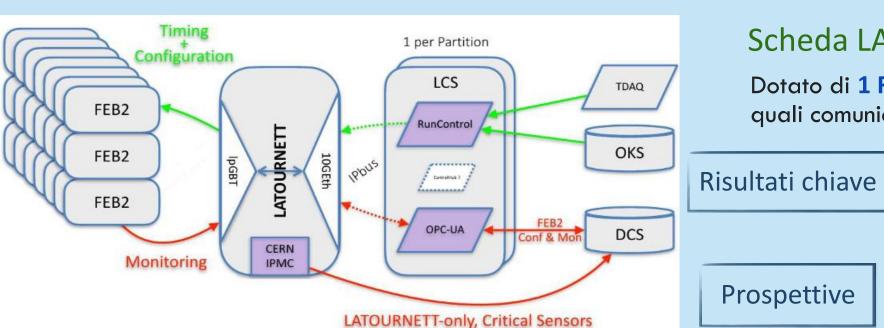

#### Sistema di temporizzazione LAr (LATS) (3)

Gestisce la distribuzione, la configurazione e il monitoraggio di Trigger, Timing e Control (TTC) delle schede FEB2 e Calibration, basandosi sul protocollo lpGBT.

Scheda LATOURNETT ATCA

Dotato di 1 FPGA centrale + 12 FPGA array AREA Cyclone 10, ciascuno dei quali comunica con 12 schede rivelatrici tramite collegamenti ottici.

Completata la progettazione della scheda di prova (V2) e preparazione del banco di prova. Test superato sul firmware FPGA e sull'infrastruttura di

sistema.

- La fabbricazione dei prototipi inizierà nel settembre 2024, quindi i test e l'integrazione del sistema.

# Elaboratore di segnale LAr (LASP) (4

Applica il filtraggio digitale alla forma d'onda del FEB2, calcola l'energia e il tempo e trasmette i dati ai sistemi TDAQ.

Scheda LASP ATCA (scheda principale) + sRTM

- Riceve dati da 6 FEB2.

- Calcola energia e tempo fino a 1,8 Tb/s

- Invia l'output al DAQ a 25 Gb/s alla ricezione di un segnale di accettazione del trigger.

- Implementato utilizzando due FPGA Stratix 10 (migrazione a Intel Agilex in corso).

- Risultati chiave

Prospettive

- Scheda di prova in continuo funzionamento grazie al monitoraggio regolare di temperatura, tensione e corrente.

- Alimentazione, sensori I2C e configurazione FPGA convalidati.

- In corso finalizzazione del **prototipo LASP** (giugno 2024)

- Firmware in via di sviluppo.

- Lunga serie di test previsti col prototipo (test stand-alone e system tests) per verificare le specifiche del TDR.

#### 5. Conclusioni

- L'elettronica on-detector e off-detector del calorimetro LAr è in fase di riprogettazione, per far fronte alle sfide di acquisizione dei dati a HL-LHC.

- Tutti i componenti elettronici saranno sostituiti entro il 2029 e sono progettati per funzionare per tutta la durata di HL-LHC (~ 2041).

Progressi principali dell'aggiornamento

di Fase2 :

- Gli ASIC custom hanno superato le specifiche e sono entrati nella fase di produzione.

- Promettenti risultati dei test sul preprototipo FEB2. Il primo prototipo col numero nominale di canali è in test ora.

- La progettazione del primo prototipo della scheda LASP è in fase avanzata (incluso il firmware).

- Grande importanza dei system tests previsti nei prossimi mesi.

In programma l'installazione nella caverna di ATLAS dopo la fine del Run 3!

#### Bibliografia

[1] ATLAS Collaboration. ATLAS liquid-argon calorimeter: Technical Design Report, CERN-LHCC-96-041.

- [2] ATLAS Collaboration. ATLAS LAr Calorimeter Phase-I Upgrade: Technical Design Report. CERN-LHCC-2013-017.

- [3] ATLAS Collaboration. ATLAS LAr Calorimeter Phase-II Upgrade: Technical Design Report. CERN-LHCC-2017-018.