# Il sensore monolotico HVCMOS ATLASPix3

R.Zanzottera, A.Andreazza, F.Sabatini

Università degli Studi di Milano e INFN Sezione di Milano

#### Introduzione

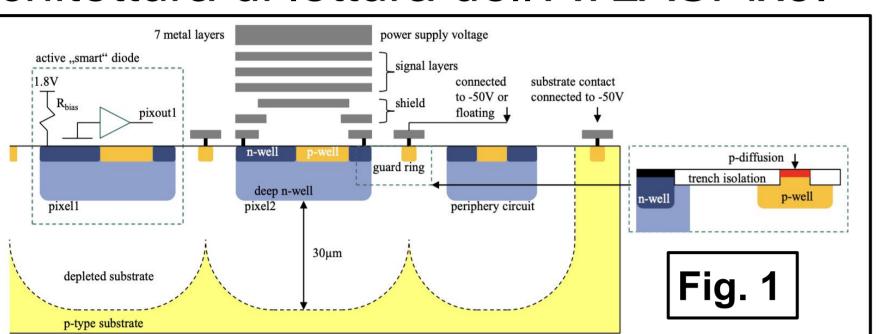

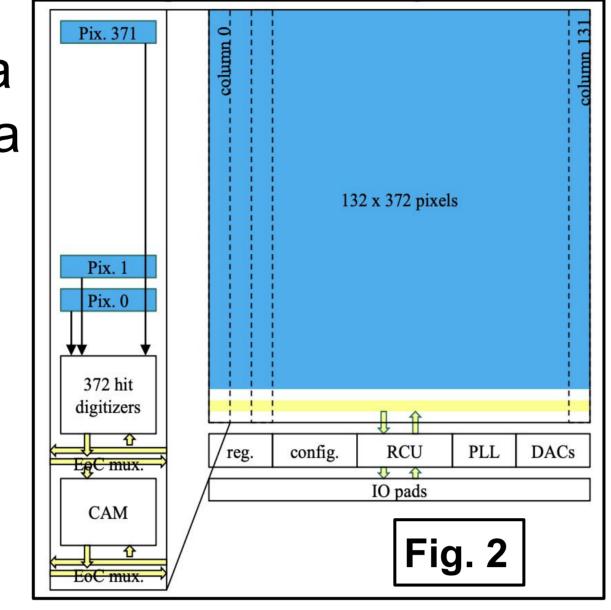

Il rivelatore a pixel monolitico ATLASPix3 è realizzato in tecnologia TSI 180nm HVCMOS. Ha dimensioni di 20x21 mm<sup>2</sup> ed è costituito da 132 colonne di 372 pixel, di 50x150µm². La tensione di svuotamento massima è -60V. Ha un timestamping a 25ns e una velocità massima di readout di 1.28Gbps, l'architettura supporta sia un readout triggered che triggerless.

Il serial powering è supportato grazie a regolatori shunt-LDO. La Fig. 1 mostra uno schema dei pixel, dove la buca *n* svolge un

doppio ruolo, elettrodo per la raccolta

della carica e isolamento dell'elettronica costruita al suo interno. La Fig. 2 mostra schematicamente il funzionamento dell' architettura di lettura dell'ATLASPix3.

## Testbeam del telescopio di ATLASPix3

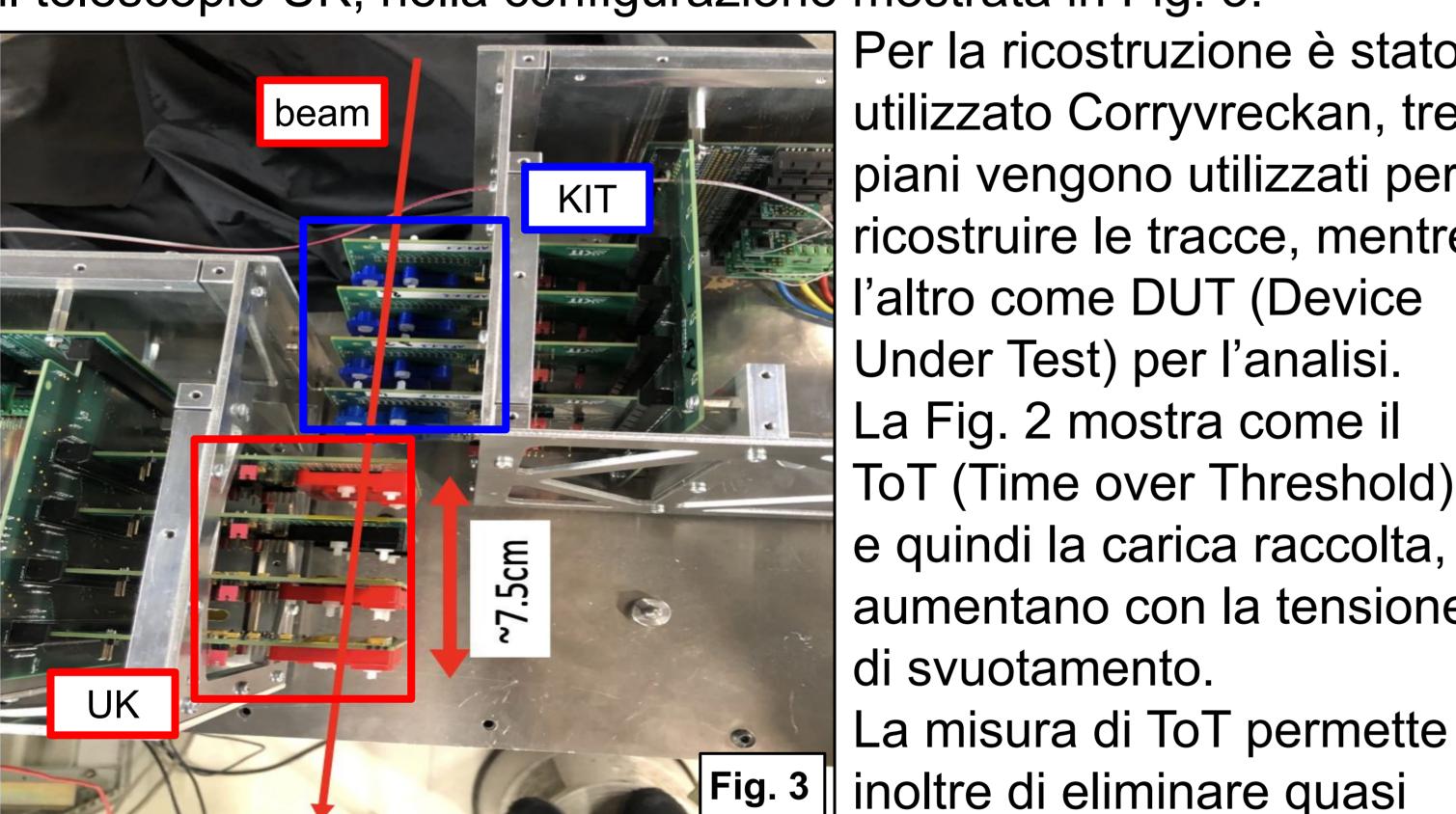

Ad aprile 2022 ATLASPix3 è stato testato a Desy con fasci di elettroni di energie fino a 6 GeV. In particolare sono stati testati due telescopi (UK e KIT), ciascuno con 4 piani di singoli chip. La presa dati è stata effettuata utilizzando una lettura hit-driven con soppressione degli zeri. Diverse configurazioni sono state testate ed i risultati qui presentati riguardano lo scan di alta tensione per il telescopio UK, nella configurazione mostrata in Fig. 3.

0.015

0.005

Per la ricostruzione è stato utilizzato Corryvreckan, tre piani vengono utilizzati per ricostruire le tracce, mentre l'altro come DUT (Device Under Test) per l'analisi. La Fig. 2 mostra come il ToT (Time over Threshold), e quindi la carica raccolta, aumentano con la tensione di svuotamento.

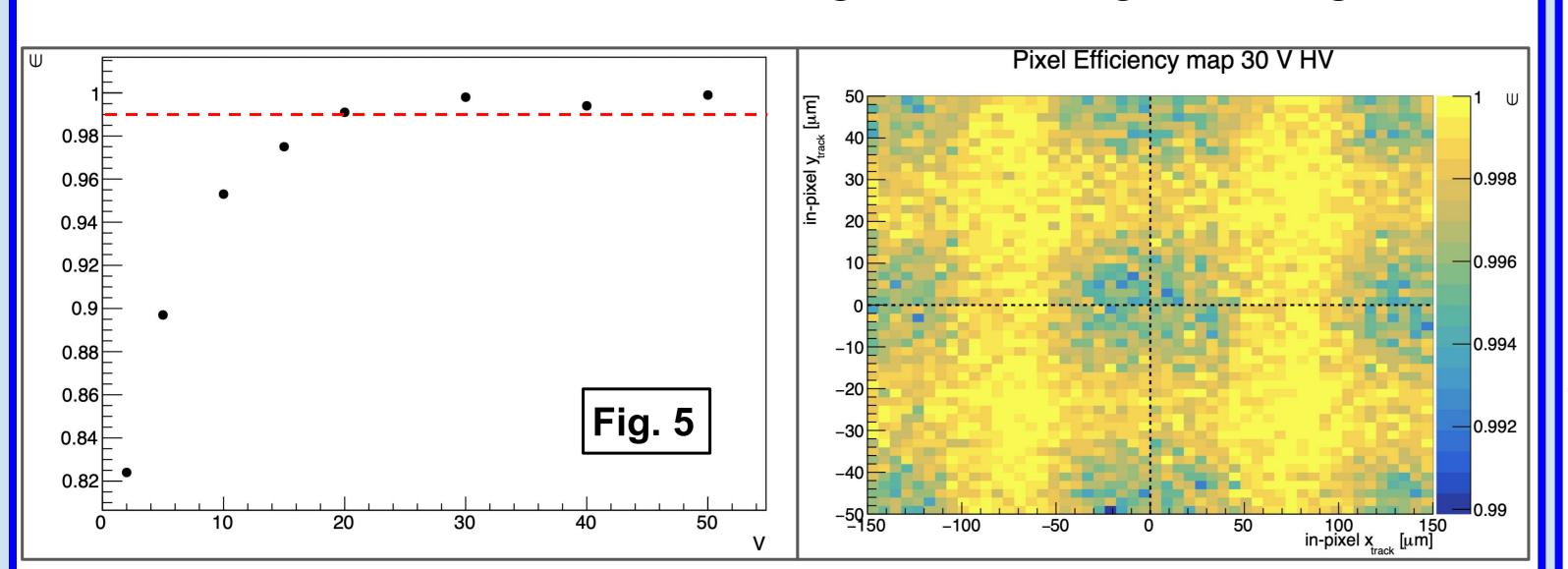

completamente la presenza di cross-talk, caratterizzato da ToT molto basso e dovuto all'accoppiamento capacitivo sulle linee tra la matrice e la logica end-of-column. L'efficienza raggiunge il 99% dopo i 20V, come mostrato in тот [тѕ] Fig. 4, a sinistra. Questo è

dovuto al fatto che per tensioni superiori a 20V l'intera regione del rivelatore è svuotata, come si può vedere dalla Fig. 5 destra, dove l'efficienza è inferiore nelle regioni di charge sharing.

Fig. 4

#### Test con fascio del CNAO

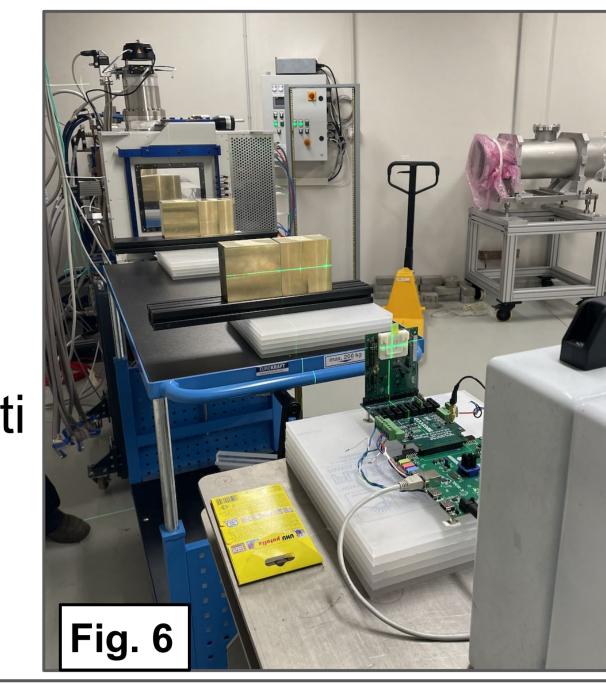

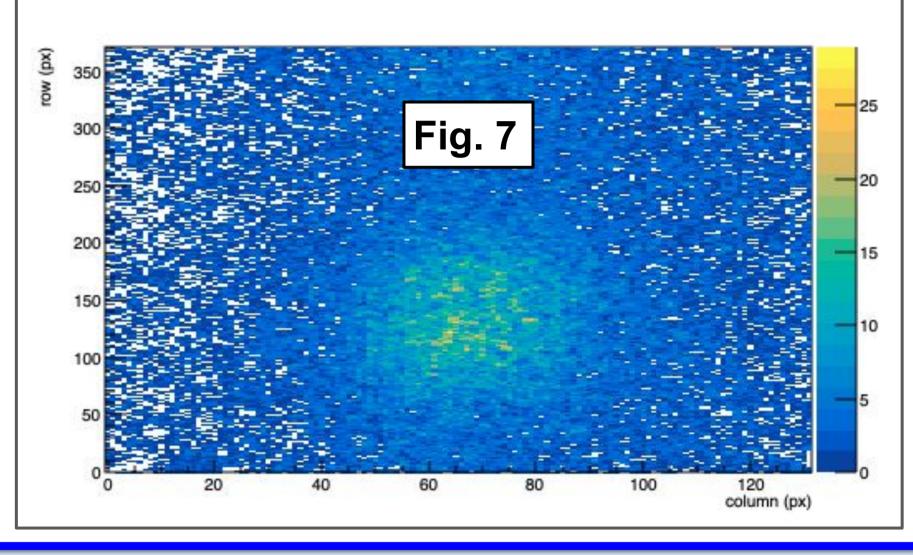

ATLASPix3, nella configurazione di singolo chip, è stato recentemente testato con i fasci del CNAO (Centro Nazionale di Adroterapia Oncologica) nell' ambito della collaborazione CREMA. In Fig. 6 è mostrato il setup per i test condotti. Durante la presa dati sono stati utilizzati fasci di protoni con energia di 227 MeV e fasci di ioni carbonio con energia di 400 MeV/u,

caso mostrato in Fig. 7. Per la presa dati il chip è stata utilizzato con una configurazione hit-driven con soppressione degli zeri. Non si osserva saturazione del segnale nonostante l'alto valore della carica rilasciata.

#### Moduli quad

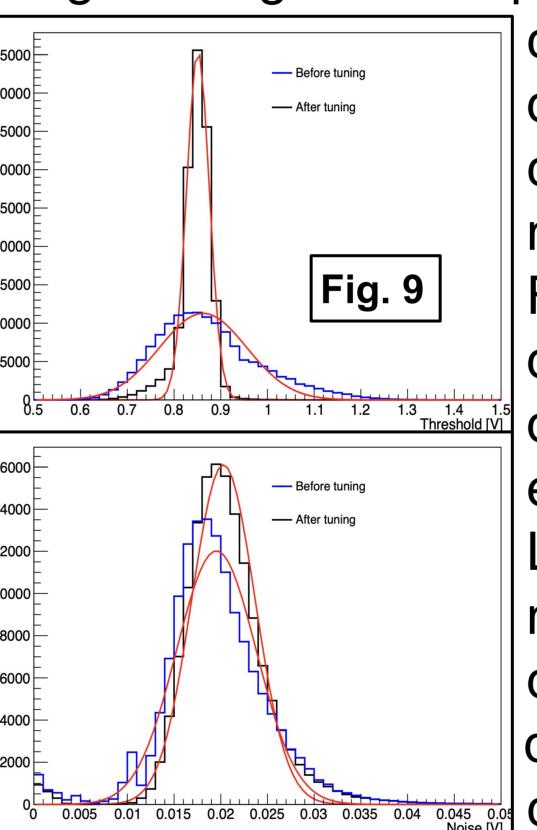

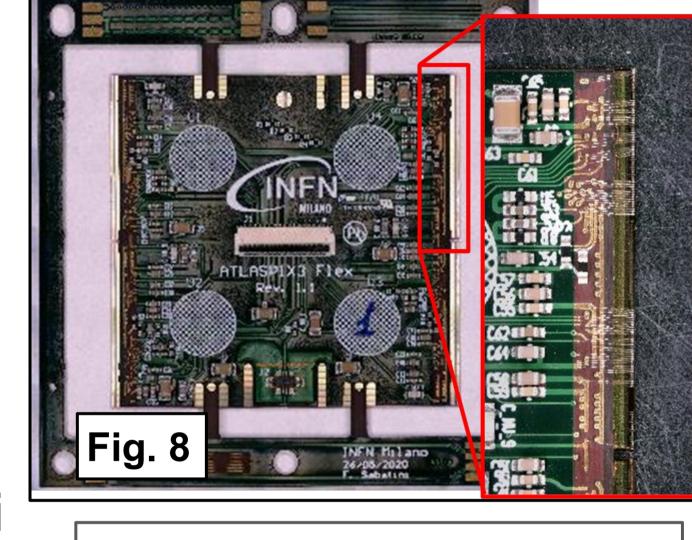

Moduli multi-chip, che integrano i servizi elettrici e linee dati per 4 chip, moduli Quad, sono stati assemblati. Il circuito stampato

flessibile in Fig. 8 è stato ispirato ai moduli\* ITk. Le prestazioni non vengono degradate rispetto alla

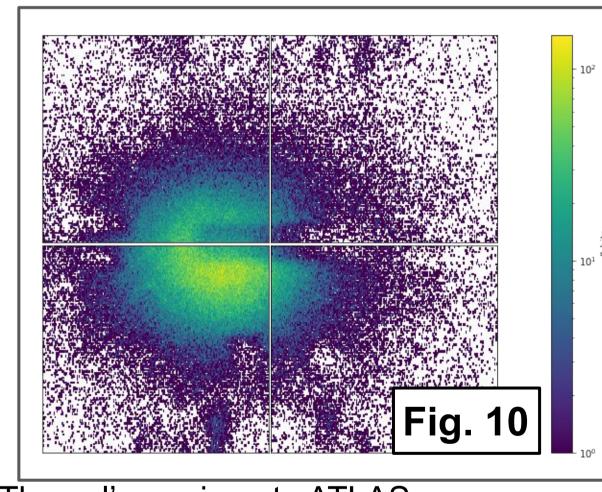

condizione di singolo chip, come mostrato in Fig. 9 dalle distribuzioni di soglia e rumore. La Fig. 10 mostra una dimostrazione di presa dati con sorgente.

\*si veda il poster di Sonia Carrà: Panoramica sul rivelatore ITk per l'esperimento ATLAS

### Serial Powering

Il chip ATLASPix3.1 permette l'alimentazione seriale tramite due regolatotori di tipo shunt-LDO (shunt-low dropout), uno per la

parte analogica del chip ed uno per la parte digitale del chip. La Fig. 11 mostra la schematica dei regolatori. La soglia e l'output dei regolatori viene regolata

Fig. 11

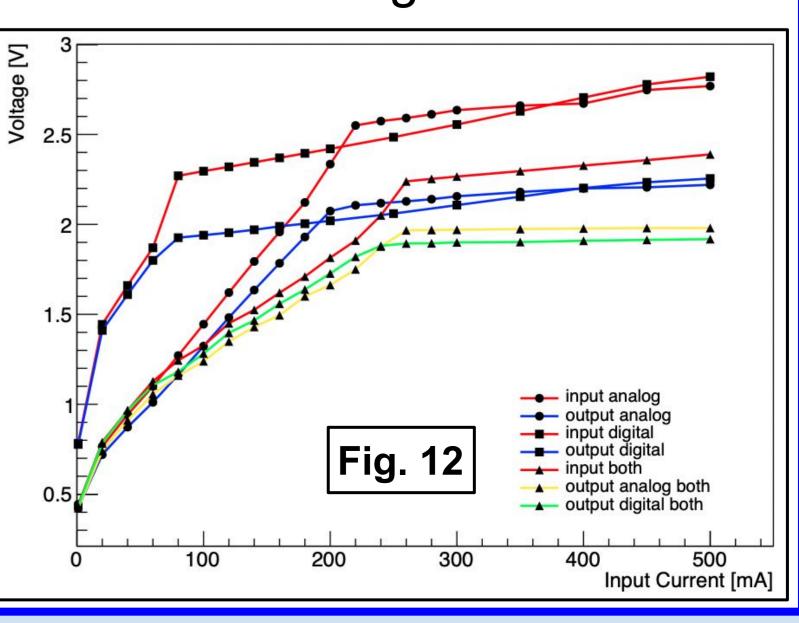

tramite DAC a 3-bit, con un range di qualche decina di mV. La Fig. 12 mostra le curve di accensione dei due regolari ed un

consumo di potenza di circa 175mW/cm<sup>2</sup>. Le performance rimangono stabili anche con questa configurazione. Moduli Quad che utilizzano questa alimentazione sono in fase di sviluppo, con l'obiettivo di creare in futuro catene di moduli alimentate in serie.