- 1. CGEM/BESIII

- 2. CGEM frontend electronics

- 3. CGEM readout

- 4. CGEM readout/BESIII DAQ

- 5. CGEM/BESIII Slow Control

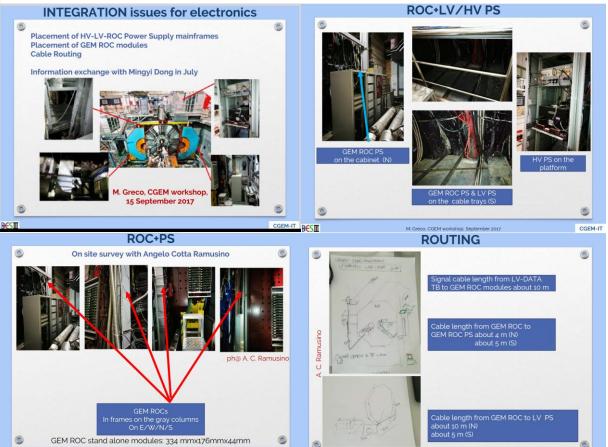

M: Greco, CGEM workshop, September 2017

2017/2023

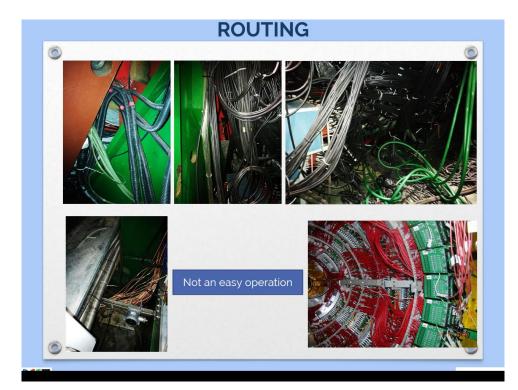

not an easy operation

## CGEM

### FRONT-END ELECTRONICS

#### TIGER

All chips have been encapsulated. Few losses. Monitoring since July

Further FEB spares: order ongoing

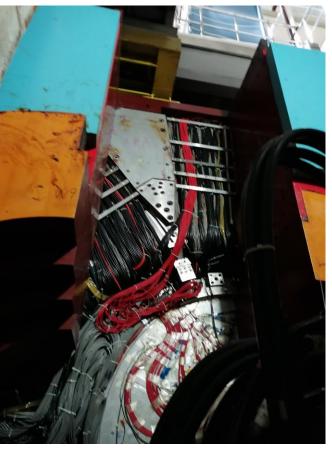

## CGEM READOUT ELECTRONICS: GEMROC

22 GEMROC needed

16 already used for L1/L2/half L3;

21 available at Beijing +1 «malfunctioning» @Beijing

2 already mounted by ACR( to be sent with GG &Riccardo)

-Spares:

4 to be mounted by ACR (or mounted in the meanwhile)

1 sent to Ferrara

>> talk by Ilaria Neri

Further developments

>> talk by Angelo

#

### GEMROC

Layer 3

Layer 1

Layer 2

**FEB**s

**FEB**s

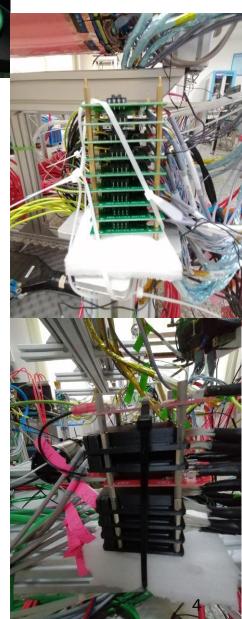

## CGEM READOUT ELECTRONICS: FANOUT

FCS: a modified GEMROC module which connects to the CLK, L1, L1\_CHK, FULL signals from the BESIII Fast Control System Fanout

FCS Local

4 groups of GEMROCs

FCS Local

FCS Local

FCS Local

FCS Local

FCS\_Local, fanout modules which connects to the CLK, L1, L1 CHK, FULL signals from FCS

>> talk by Angelo

FCS\_Local

FCS backplane: 5 available (4 needed)

FCS Flat Cable Ports: 5 available (4 needed)

FCS backplane interface: under check ->checked

FCS terminator: layout refined, under production

Modules will be mounted with the help of Nicholas

## READOUT ELECTRONICS: GEMROC<>GEMDC

GEM DC from LNF

Pawel @ Fe

End of March/April

Debugging by Angelo >> talk by Angelo

## CGEM READOUT/ SEST DAQ

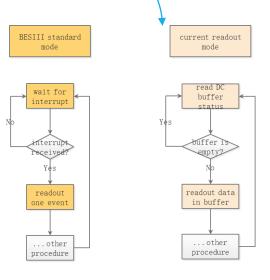

- Issue 1: lack document for Physics run mode data acquisition

- Issue 2: readout mode inconsistent with BESIII

- Issue 3: define different Run Modes for CGEM

|                      | ₩       |          |             |         |  |

|----------------------|---------|----------|-------------|---------|--|

| Run Mode<br>Detector | Physics | Pedestal | Calibration | Monitor |  |

| MDC                  | ٧       | ×        | ٧           | ×       |  |

| EMC                  | ٧       | ٧        | ٧           | ٧       |  |

| MUON                 | ٧       | ×        | ×           | ×       |  |

| TOF                  | ٧       | ×        | ×           | ٧       |  |

| TRG                  | ٧       | ×        | ×           | ×       |  |

| CGEM                 | ٧       | ?        | ?           | ?       |  |

Dedicated meeting(s)

## CGEM READOUT/

#### **CGEM-IT** electronics procedures

#### Before run

- GEMROC/TIGER configuration:

- TIGER settings:

- Load default settings (all the same)

- Load specific TIGER settings

- Load threshold settings (by channel)

- Disable listed channels

- GEMROC settings:

- Load default settings

- Set "pause mode"

- 8b/10b error status check

#### During run

- IVT status check

- 8b/10b error status check

#### Periodic procedures /on demand

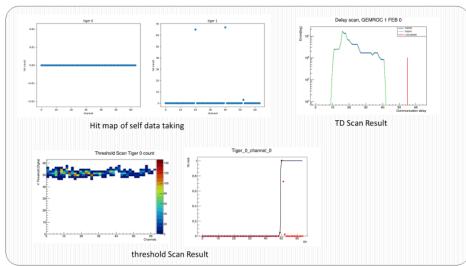

- Threshold scan

- TD scan

#### Expert debug procedures

· GUFI controlled?

**Documentation** provided or underway

#### **CGEM DAQ discuss**

#### Documentation

My Thesis -> Overview of the chain and details about GEMROC's and GUFI

Fabio Cossio's Thesis -> details about TIGER

The CGEM readout chain -> JINST article about the whole electronic chain

Fabio's presentation about TIGER pass: Cgem2023

UDP format file -> GEMROC packet format pass: Cgem2023

We are working on a complete wiki, expecially for GEMROCs, I will keep you updated.

- 1. what is the config process before physics data taking mode? Can you provide me a document about this topic?

- o I will provide a specific document for it.

- 2. what config variable and command is used by DAQ?

- 3. what is the meaning of each config varible?

- You can find TIGER variables in Fabio's thesis, yo we are working on

- 4. what is the meaning of each config command?

- o TIGER codes:

| code | name        | action                                                         |

|------|-------------|----------------------------------------------------------------|

| 0x0  | CMD_WRCHCFG | Write the<br>global<br>configuration<br>into TIGER<br>register |

#### Quick guide for a simulated triggers noise acquisition (with double threshold)

#### Preliminary: about voltages and currents

Analog Voltage: between 3.2 and 3.

Mar

14 views 🎤

Ferrara 15/09/2023 Stefano Chiozzi, Angelo Cotta Ramusino, INFN-Ferrara Alberto Bortone, Università' / INFN-Torino

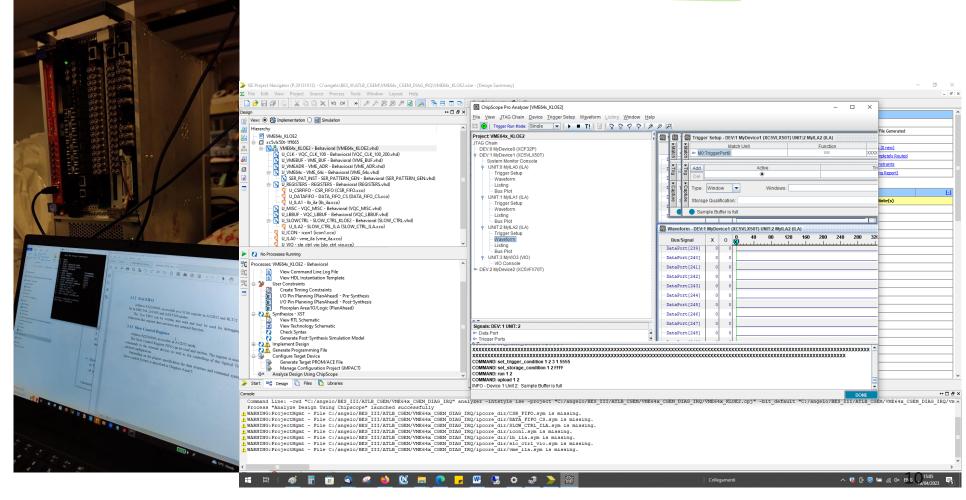

#### Notes on GEMROC Ethernet controller

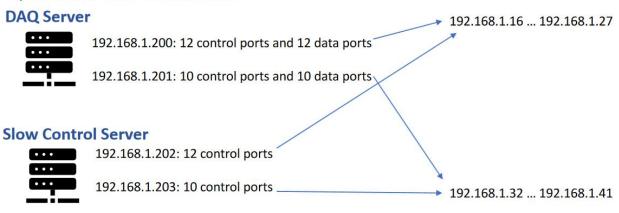

The GEMROC module exploits an Ethernet Controller IP (Intellectual Property) developed by Stefano Chiozzi of INFN-Ferrara to allow the GEMROC module's FPGA to efficiently packets over an Ethernet To achieve the optimization of the EC some constraints have been necessarily introduced by the designer on its network connections features, mainly in order to minimize the FPGA resources needed to generate UDP packets yet achieving a data throughput close to the maximum theoretical data transfer rate of a GbE link.

For the above reason, the following rules apply for the private Ethernet network connecting the GEMROC modules and the server PC(s) running the Slow Control / DAQ tasks:

- 1. the network prefix formed by the 3 most significant octets of the IP address may be freely chosen. A good idea is to use a prefix belonging to the range 192.168.0.0 -192.168.255.255 assigned by the Internet Assigned Numbers Authority (IANA) to private networks. The usual choice of network prefix is 192.168.1.

- 2. the "Host ID" octect range 1 to 254 (Host ID 0 and 255 are reserved) is divided

a. the range of IP addresses 192.68.1.1 - 192.168.1.191 is reserved to GEM

## CGEM READOUT

### Firmware update

- UDP packets format

>> Alberto

New packet format needed to decouple DAQ and Slow Control registers write operation Already implemented in GUFI and DAQ test software

@CGEM workshop

#### Now

| DAQ                 | Operations (e.g.)    | Command   | Effect                       | DAQ                    | Operations (e.g.)    | Command        | Effect                    |

|---------------------|----------------------|-----------|------------------------------|------------------------|----------------------|----------------|---------------------------|

| Server              | Thr scan counter set | LV_CFG_WR | Overwrite FEB power settings | Server                 | Thr scan counter set | LV_COUNTER_SET | No SC register overwrite  |

| Slow Control Server | Power ON FEBs        | LV_CFG_WR | Overwrite scan settings      | Slow Control<br>Server | Power ON FEBs        | LV_CFG_WR      | No DAQ register overwrite |

### **CGEM READOUT**

#### Firmware update

- GEMROC addresses

New address/port structure in order to connect 22 GEMROCs with a simple structure.

- IP addresses from 192.168.1.16 to 192.168.1.47 (determined by GEMROC ID number)

- A range of 16 ports for every operation (data, configuration ecc.), due to GEMROC Ethernet controller structure

- Two destination IP needed on the control PC in order to manage all the GEMROC.

- GUFI and DAQ test software already compatible with this patch

#### A possible network structure:

L1, L2 GEMROCs

L3 GEMROCs

>> Alberto

@CGEM workshop

## INFN

### CGEM READOUT

### Firmware update

New Current (I), Voltage (V) and Temperature (T) log mode:

>> Damiano

```

switch(cmd code 4bit)

// #define CMD GEMROC NONE 0x0

case CMD GEMROC LV CFG WR:

Update GEMROC CFG LV(Number of packet words);

break; // defined 0)

Read GEMROC CFG LV(Number of packet words);

break; // defined 0x

8 s

case CMD GEMROC LV IVT UPDATE: Perform IVT update(Number of packet words);

break: // defined 0x

Perform IVT read(Number of packet words);

case CMD GEMROC LV IVT READ:

break; // defined 0x

case CMD GEMROC LV TIMING DELAYS UPDATE: GEMROC update timing delays(Number of packet words); break;

case CMD GEMROC LV REMOTE HARD RESET: Perform GEMROC HARD RST(Number of packet words); break; // def

default: break;

void Perform IVT read(int Num of packet words) // last update: cab 2023-06-06

int i:

Perform IVT read and Check Interlock(); // cab 2023-06-06

30 s

// acr 2018-01-07 BEGIN adding a set of control to separate Analog/Digital V and I

U32 command words array[Num of packet words-11] = 0;

GEMROC

void Perform IVT read and Check Interlock()

// cab 2023-06-06 BEGIN

time(&T CONTROL);

Read_IVT_ADC(); // cab 2023-05-31

if (difftime(T_CONTROL,T_LAST_CHECK)>INTERLOCK_CHECK_DELAY)

Interlock_PIN_Check(); // cab 2023-05-

Perform IVT read and Check Interlock();

time(&T LAST CHECK);

D 2023-06-06 END

```

## • CGEM /BESI SC

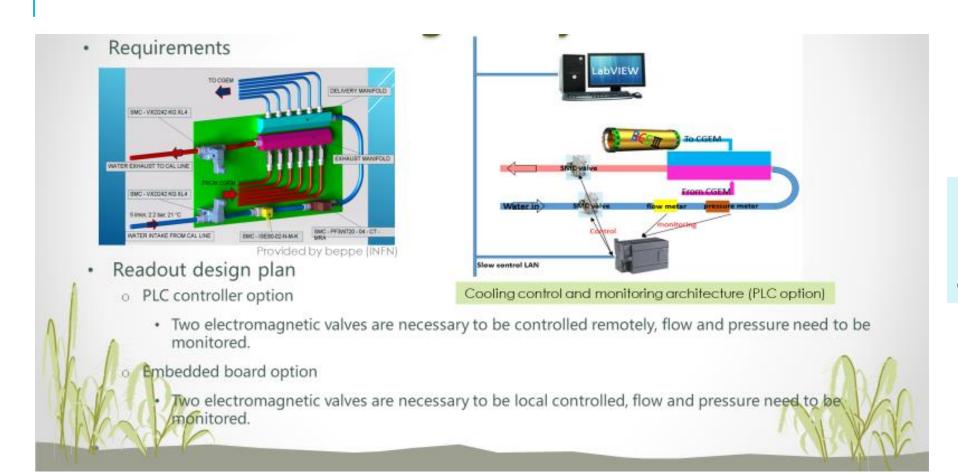

The Status of CGEM Slow Control System Speaker: Si Ma On behalf of IHEP DAQ Group 2019.06.29 The subsystems of CGEM DCS > High voltage control & monitoring system > Low voltage control & monitoring system > GEMROC control & monitoring > GEMROC and TIGER power supply control & monitoring > VME control & monitoring system > Gas control & monitoring system > Cooling control & monitoring system VME subsystem Requirements · Control power switch Monitoring voltage, current, temperature and fan Software development progress Reuse of other VME software design and implementation of BESIII VME commissioning status Stable operation in the laboratory for nearly one

Embedded board option

2019

The CGEM DCS is divided into three

Local control layer (LCL)

Global control layer (GCL)

layers the same as other detectors of BESIII

- Convert signals such as temperature and pressure into digital information

- To acquire data from the FEL and offer

supervisory and control functions

— Software based on BESIII DCS framework

- Including a GCS, a database server and a web

hardware platform has just been set up in our lab,

debugging of the LabVIEW library with GEMROC is in

- Execute control commands sent from the LCS

## INFN O.

## \*CGEM COOLING

**Documentation checked**

Paolo Mereu onsite at the end of November

INTEGRATION Working Group @IHEP, end of November Angelo, Damiano, Fabio, Giulio, GG, Manuel, Matias, Michela, Paolo

NEED TO FILL THE GAP in DAQ &SC activities asap

PERFORMANCE REVIEW......COMING!