## UNIVERSITĂ DEGLI STUDI DI BARI ALDO MORO

# **Characterization of Monolithic Active Pixel Sensors** for future collider Experiment

Angelo Colelli<sup>a,b,\*</sup>, Francesco Barile<sup>a,b</sup>, Shyam Kumar<sup>b</sup>, Triloki Triloki<sup>b</sup>, Rajendra Nath Patra<sup>b,c</sup>, Giuseppe Eugenio Bruno<sup>a,b</sup>, Domenico Di Bari<sup>a,b</sup>, Cosimo Pastore<sup>b</sup>, Antonio Franco<sup>b</sup>

<sup>a</sup>Università degli Studi di Bari Aldo Moro, Italy, <sup>b</sup>INFN Sez. di Bari, Italy, Department of Physics, <sup>c</sup>University of Jammu, Jammu, India \*angelo.colelli@ba.infn.it

## Abstract

In high-energy physics experiments, Monolithic Active Pixel Sensors (MAPS) have become crucial components of vertex and tracking detectors over the past decade due to the integration of readout circuitry with the detection volume in a single chip. The low material budget requirement to achieve precise tracking and vertexing capabilities for upgrade of HEP experiments, such as ALICE at LHC and future experimental facilities like ePIC at EIC, leads to a direct attention towards an ultra-thin (a few tens of µm), bent, wafer-scale silicon sensors produced with stitching technology.

Recent ongoing activities performed at the INFN and UniBa Laboratory in Bari will be described. The characterization of analogue silicon pixel sensors of 65 nm CMOS technology using electrical test pulsing and <sup>55</sup>Fe as a soft X-ray source will be discussed. Furthermore, a study on timing performance will be presented.

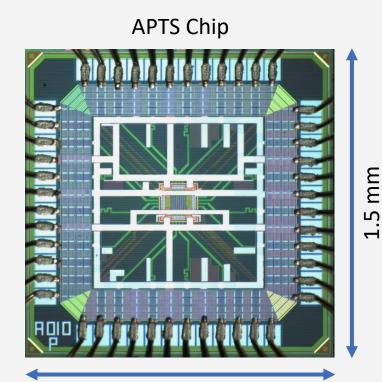

## The 65 nm CMOS Analogue Pixel Test Structure

The APTS is a prototype test structure based on TPSCo CMOS 65 nm ISC technology. CMOS pixels sensors with small collection electrode are characterized by a small sensor capacitance and consequently a high signal-to-noise ratio. From the monolithic design itself, a low material budget is reached allowing to a better resolution at low transverse momentum.

## Laboratory Measurements The chip testing is performed as follow: **Electronic calibration** Best Working point **Radioactive measurements with** <sup>55</sup>**Fe X-rays source**

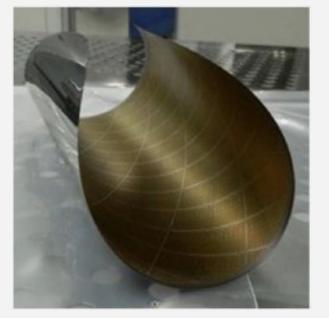

#### Bent wafer-scale sensor

#### **Chip Characteristics:**

- matrix sizes: 6×6 pixels

- **pixel pitch:** 10, 15, 20, 25 μm

- Output drivers: Operational Amplifier

- **Readout**: direct analogue of the 4x4 central submatrix<sup>1</sup>

- **Coupling**: DC/AC

- **Biasing**: 0 ÷ -5V (DC) 0 ÷ 50V (AC)

<sup>1</sup>The others 20 are dummy pixels allowing to minimize the distorsion of the electric field.

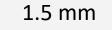

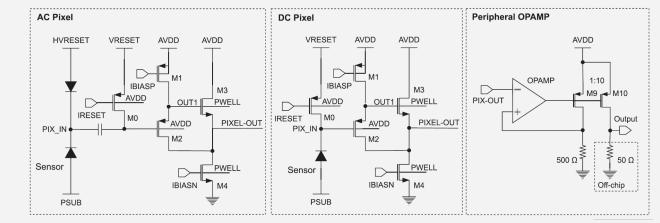

**Pixel designs**<sup>1</sup>:

- Standard:

- n-well collection electrode on a low resistivity p-type substrate.

- In-pixel circuits placed outside the collection electrode and inside a deep p-well: full CMOS circutry enabled.

- Balloon-shaped depletion zone.

- Modified:

- A deep low-dose n-type implant under the full pixel area creates a planar junction.

- With some substrate reverse bias applied, a full depletion of the epitaxial layer is achieved allowing charge collection by drift.

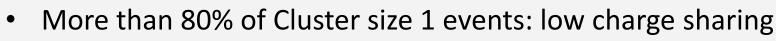

- Modified with gap (MwG):

- A gap of 2.5 µm has been created at the pixel boundaries.

- Reduction of the charge sharing among neighbouring pixels is

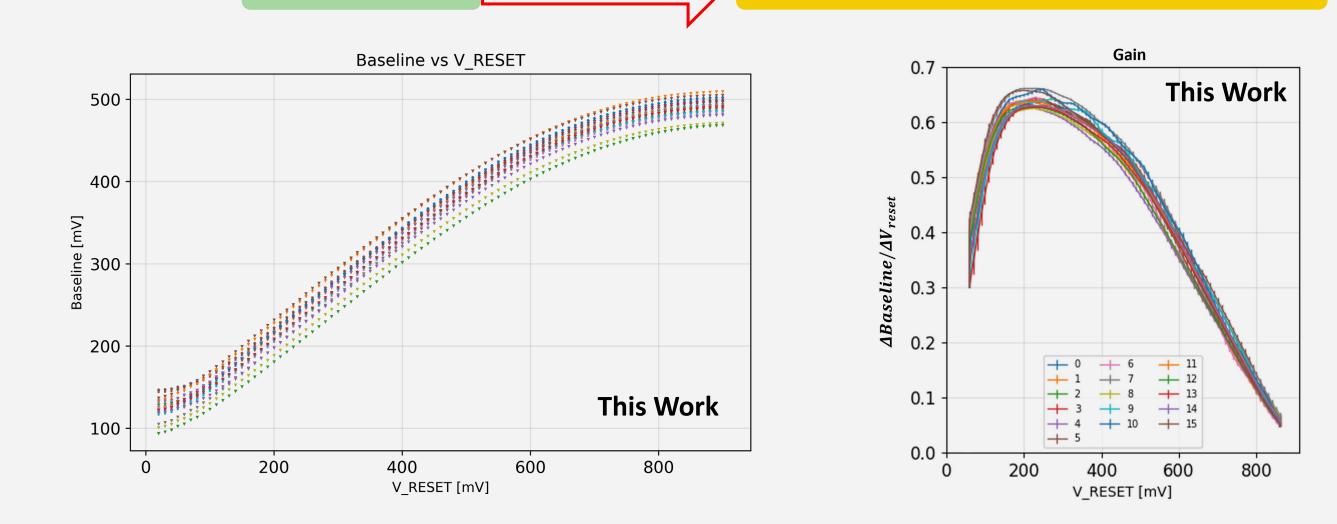

- Stable values of  $\Delta Baseline/\Delta V_{reset}$  represent the best circuitry response.

- Pulsing by electronic charge injection into the circuitry to simulate diode data collection.

X-Ray emission close to MIP for direct chip characterization in terms of best amplitude signal and minimum fall time.

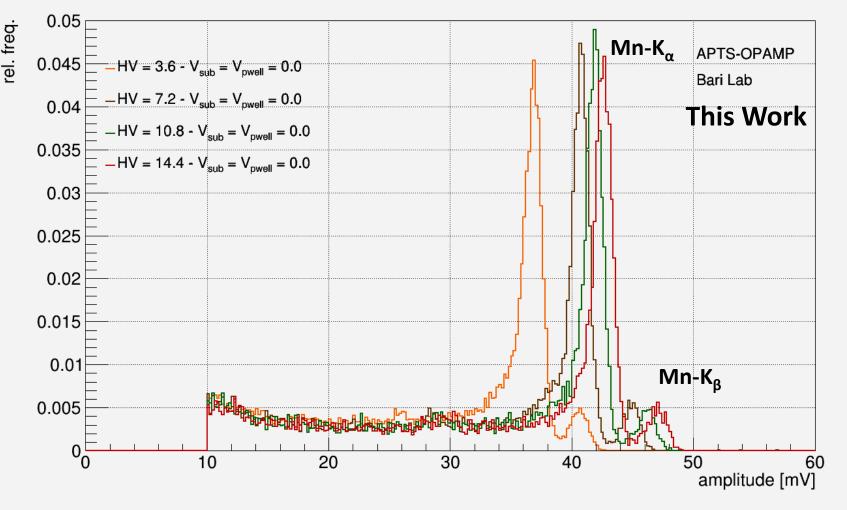

• Mn-K<sub> $\alpha$ </sub> (5.9 keV) and Mn-K<sub> $\beta$ </sub> (6.5 keV) peaks used as absolute energy calibration.

<sup>55</sup>Fe Energy Spectrum Cluster size 1 measured with a MwG AC coupled sensor at different bias level

**Cluster Size 1**

< 2 m\

< 2 mV

expected due to an enhanced lateral electric field.

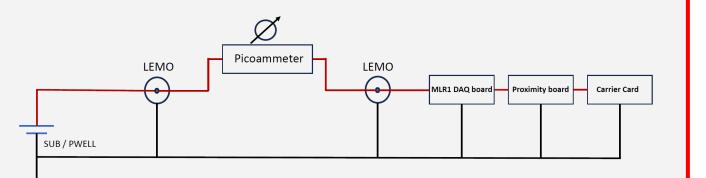

#### **Readout chain<sup>2</sup>:**

- AC coupling:

- A capacitor is introduced between the sensing node and input transistor gate.

- The sensing node is reset via a diode.

- Substrate tied to the ground.

- DC coupling:

- The sensing node is directly connected to the input transistor gate.

- The sensing node is reset by a PMOS transistor.

- A negative bias is applied to the substrate and to the bulk of NMOS transistors.

Schematics of the pixel design

Schematics of the readout chain

Operational Amplifier (OpAmp): maximize speed capability to characterize charge collection time in the sub-nanosecond range.

- High statistics for Cluster size 1 events

- Slow events are suppressed

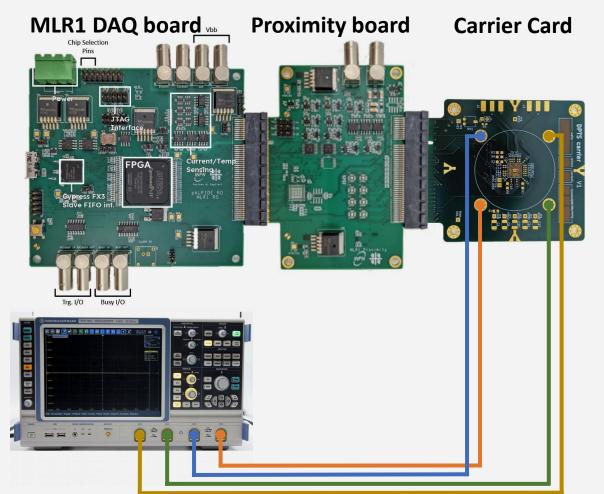

## **Experimental Setup at INFN and UniBa Laboratory - Bari**

Multi Layer Reticle MLR1 First sensor prototypes in 65 nm process used to validate the technology in collaboration with CERN EP R&D.

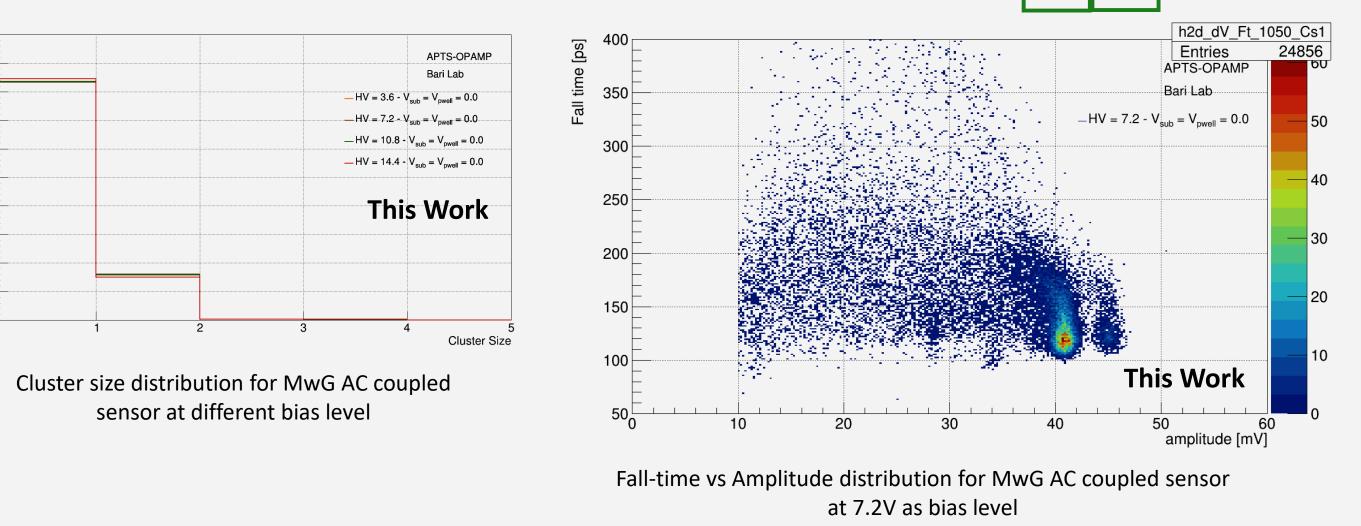

#### MLR1 DAQ board (FPGA-based):

- Powering and biasing the chip.

- Hosting the ADCs that sample the 16 pixels at 4MSa/s.

**Proximity and carried card:**

• Designed specifically for each chip flavour.

## **Experimental facilities for outgassing studies in vacuum**

Future vertex detectors will be mounted close to the beampipe where the order of vacuum will be about 10<sup>-10</sup> mbar. Thus, it is very important to study the outgassing properties of the vertex detectors components.

Three ways to perform outgassing measurement:

- Comparing the vacuum level with and without sample

- Comparing residual atmosphere of vacuum chamber with and without sample using Residual Gas Analyzer (RGA)

- Comparing the Total Mass Loss (TML) of sample before

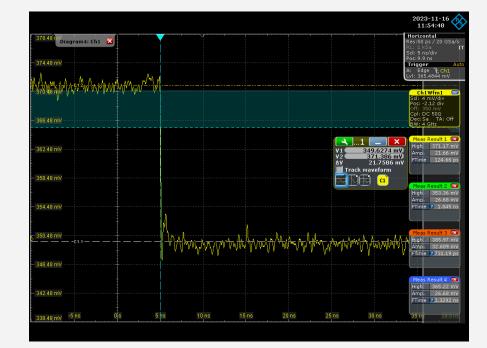

**Oscilloscope Rohde & Schwarz RTO RTO 1044:**

- Bandwidth: 4GHz Sampling Rate: 20GSa/s

- Sampling the 2x2 inner pixel matrix for timing studies

**Picoammeter Keithley 6487:**

• VI measurement of leakage currents in the substrate

Schematics of the experimental setup

Schematics of the leakage currents measurement

Waveform at 20GSa/s. Time window 50 ns

#### and after pumping

#### Samples to test:

- 3D printed aluminium nitride (AIN) samples disks

- Al<sub>2</sub>O<sub>3</sub> samples disk: 3D printed alumina samples disks

- 3D printed AlSi samples disks

- Carbon (LAYPUS) Substrate of the cold plate

- Carbon Fleece of the cold plate

- Carbon foam All comp high density

Particular of the setup for sample transportation under vacuum

Experimental Setup for outgassing studies @

University of Bari and INFN

- Carbon foam All comp low density

- Carbon foam ERG duocel

- Optical Fiber with connector

- NASA Epoxy

- Si wafer

- Wire bonded Si wafer

- FPC

#### References

- [1] Rinella et Al., Characterisation of analogue Monolithic Active Pixel Sensor test structures implemented in a 65 nm CMOS imaging process, arXiv, Instrumentation and Detectors, (2024) 2403.08952

- [2] W. Deng et Al., Design of an analog monolithic pixel sensor prototype in TPSCo 65 nm CMOS imaging technology, Journal of *Instrumentation*, 18 (2023) C01065