# The Upgrade of the CMS Tracker for the High Luminosity LHC

Anna Macchiolo University of Zurich on behalf of the CMS Tracker group

16th Pisa Meeting on Advanced Detectors, Elba, 27 May 2024

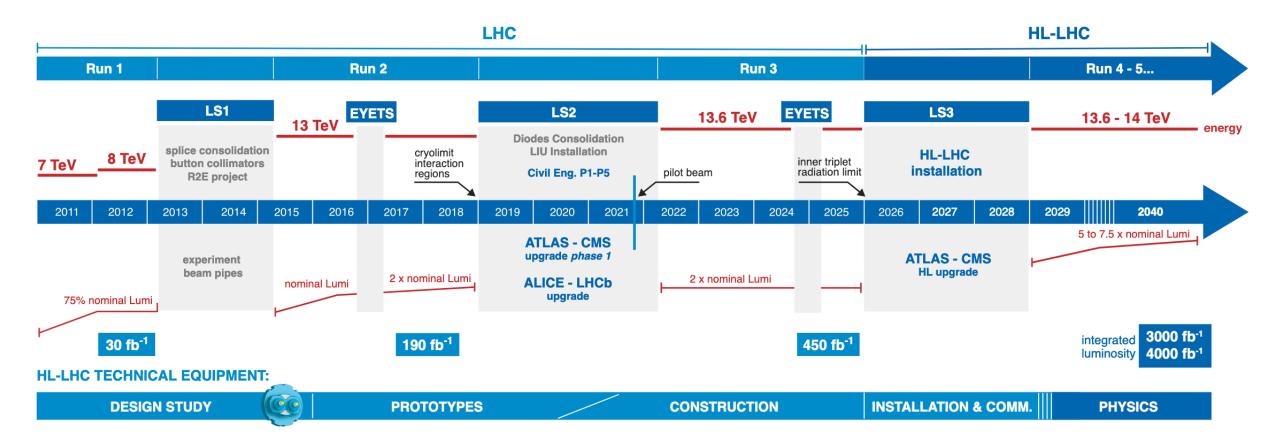

### LHC / HL-LHC Plan

# The roadmap for the CMS Tracker at HL-LHC

The new HL-LHC upgrade environment:

- Luminosity @ 5-7 x 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Pile-up to  $\langle \mu \rangle$  = **200** (4x times more than Phase 1)

- Integrated luminosity  $\geq 3000 \text{ fb}^{-1}$  (~10x times more than Phase 1)

### The present CMS Tracker

- StripTracker

- $\simeq 9.3 \times 10^6$  strip channels (198 m<sup>2</sup>), Mono-phase cooling

- Pixel system

- $\simeq 125 \times 10^6$  pixels (~1.9m<sup>2</sup>), Bi-phase CO<sub>2</sub> cooling

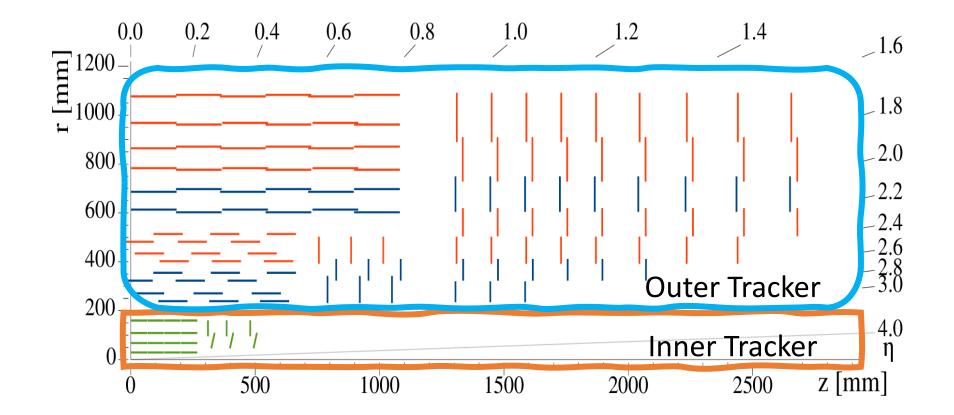

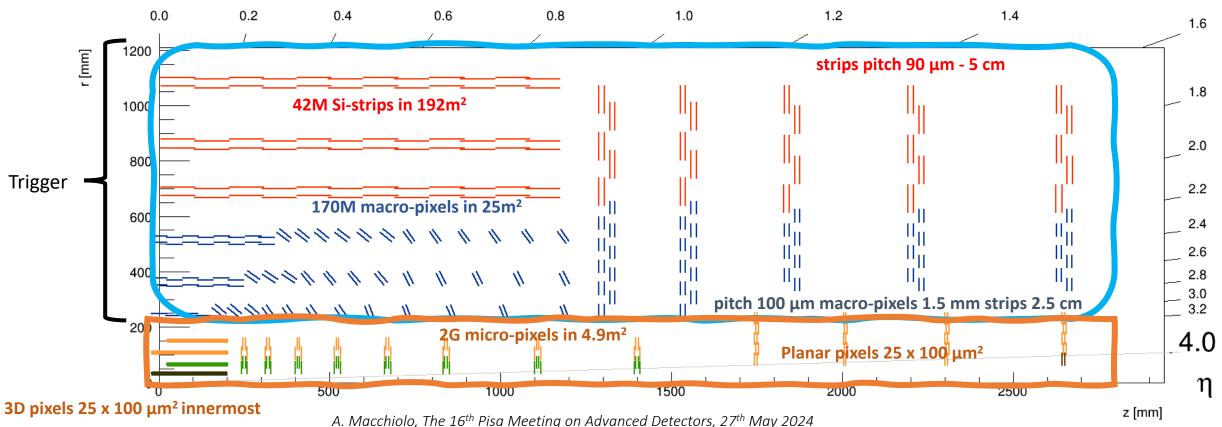

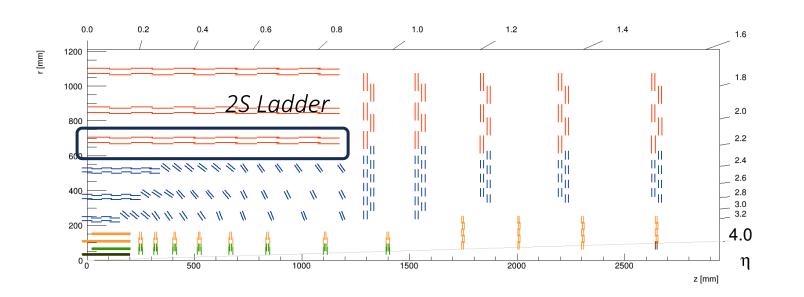

### Phase-2 Tracker

#### Outer Tracker design driven by ability to provide tracks at 40 MHz to L1 trigger

- $\simeq 200 \text{ m}^2 200 \text{x} 10^6 \text{ channels}$

- Track stub / double sided p<sub>T</sub> module @ bunch crossing rate of 40 MHz

- Track finding for L1 implemented in FPGAs

- Tilted geometry

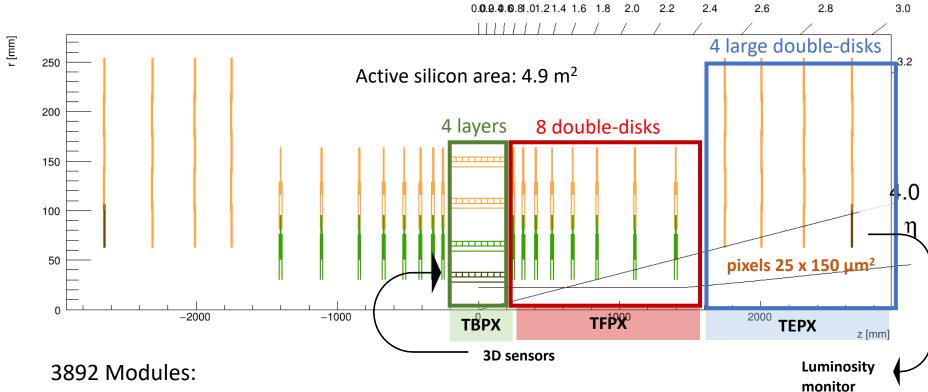

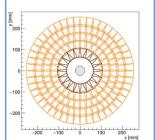

- Inner tracker with extended coverage in pseudo-rapidity

- $\simeq 4.9 \text{ m}^2 2 \times 10^9 \text{ channels}$

- Innermost layer at 2.8 cm (2.9 cm in Phase-1) from beam pipe but same occupancy as in Phase-1 (~2x10<sup>-3</sup>)

- - One replacement foreseen for innermost layer in the barrel and first ring in the disks of the forward system at a fluence of 1-1.5 x10<sup>16</sup> n<sub>eq</sub>/cm<sup>2</sup>

5

## The Outer Tracker

1 1

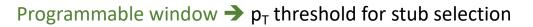

### Outer Tracker module concepts

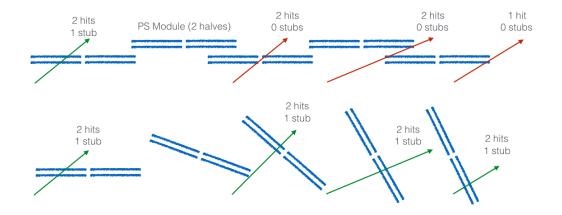

*Modules provide p<sub>T</sub> discrimination in front-end electronics*

#### New concept

- Tag high p<sub>T</sub> segments locally on the same module

- Contains ALL electronics = full system

- Effective way to have 2 space points in single mechanics – lightweight

- Frontend electronics gives Level-1 track finder 'vectors' instead of points

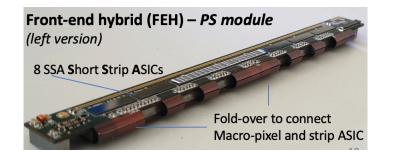

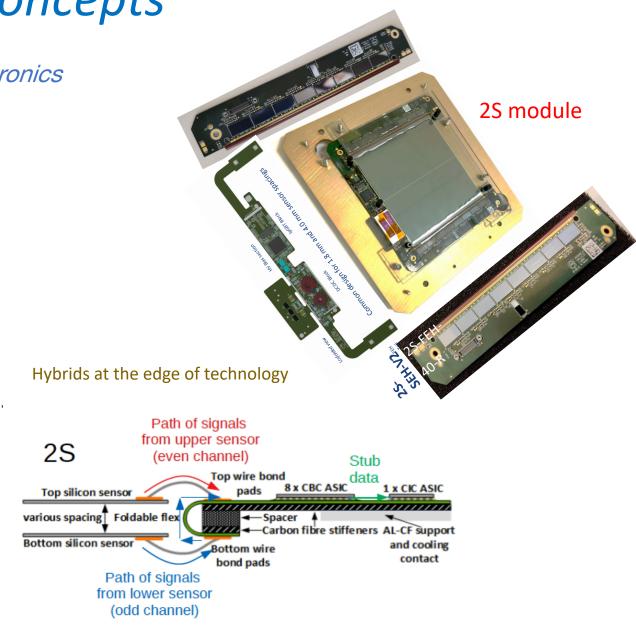

#### Hybrids with fold-over:

- Allow to wire-bond both sensors to the same hybrid

- Provide adequate stiffness for wire bonding

- Minimize material

- Complicated fabrication and delicate part!

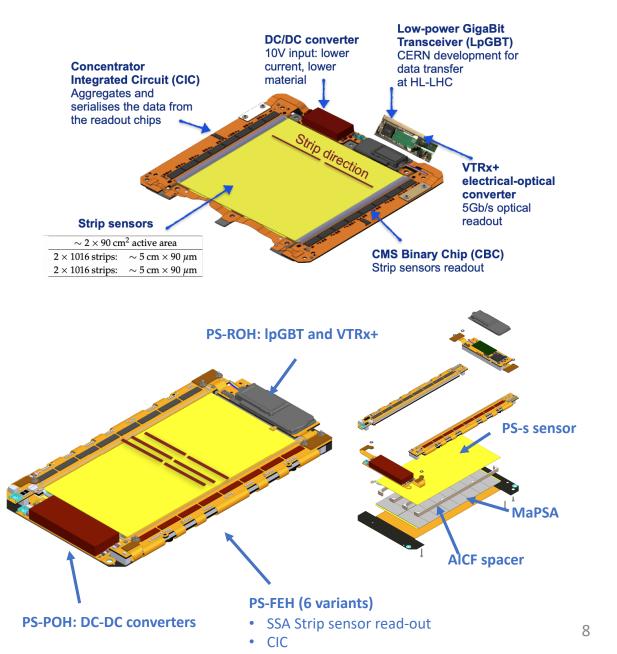

### 2S and PS modules: design and production

#### Strip-strip (2S) module

- 2 AC-coupled strip sensors

- 10cm x 10cm (5cm long strips, 90µm pitch)

- 2 sensor spacings: 1.8mm\* and 4.0mm

- R> 60 cm

#### Pixel-strip (PS) module

- AC-coupled strip sensor

- 5cm x 10cm (2.5cm long strips, 100µm pitch)

- Macro-Pixel Subassembly (MaPSA)

- DC-coupled pixel sensor (1.4mm long macro-pixels, 100µm pitch) bump bonded to 16 MPA chips

- 3 sensor spacings: 1.6mm, 2.6mm\* and 4.0mm

- R< 60 cm

- Good noise performance found with pre-series PS and 2S modules

- Almost all components are in pre-production or production

- Module design is final

See Poster by I. Margjeka: Noise and performance tests results of the PS modules for the phase-2 CMS outer tracker

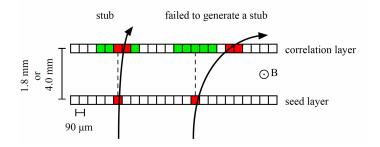

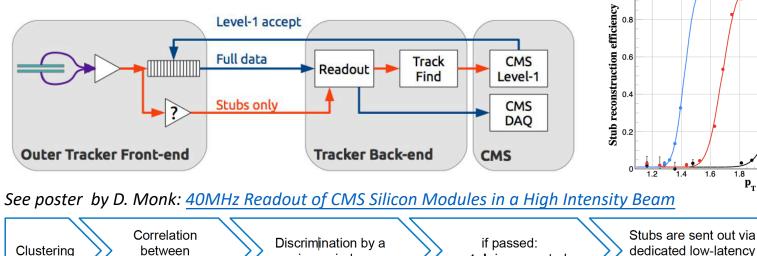

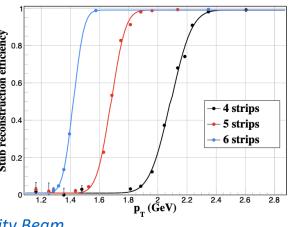

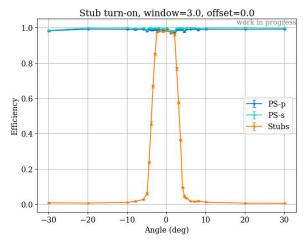

## OT modules for the L1 Track Trigger

a stub is generated

Two simultaneous data-streams

two planes

- Stub read-out at the full 40MHz rate

- Full data read-out at up to 750kHz

given window

I. Zoi, https://doi.org/10.22323/1.448.0021

Stub efficiency for 2S prototypes

data path

D. Rastorguev, BTTB12 20024

Stub efficiency for PS prototypes

$\mathcal{E}(\text{Stub}) = \mathcal{E}(\text{PS-p}) \cdot \mathcal{E}(\text{PS-s}) \cdot \mathcal{E}(\text{Acceptance})$

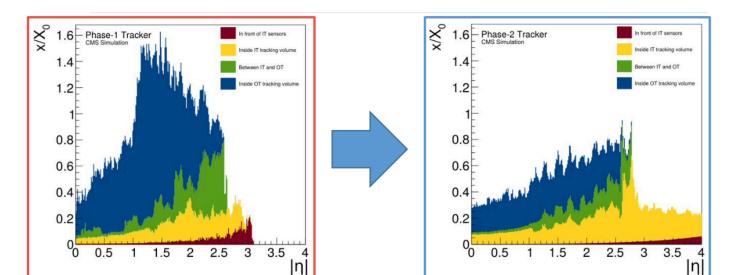

### Material budget and mechanics

#### • DC-DC converters – fewer cables

- Fewer layers

- Lighter materials

- Optimized service routing 3D modelling

- $CO_2$  bi-phase cooling thin pipes

- Inclined geometry

CMS Tracker TDR, CERN-LHCC-2017-009

#### 2S ladder

#### PS module on TBPS plank

#### OT tilted rings

OT endcap dee

Carbon foam layer 3 end ring pieces

All OT mechanical support structures in pre-production or production

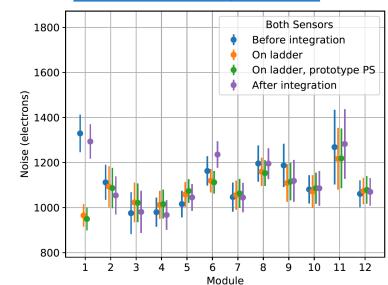

### OT System tests – 2S ladders

- 12 2S modules on a ladder with prototypes of electrical and optical services:

- Prototype power supply for the Phase-2 Tracker with 60 m long cable

- Module noise shows no significant increase on the ladder compared to the measurement before integration

- No noise degradation throughout integration test

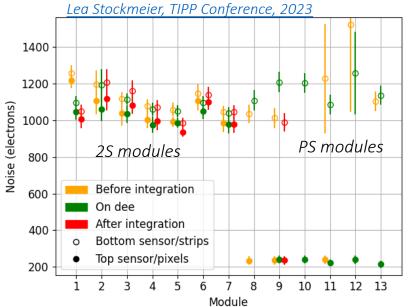

#### Lea Stockmeier, TIPP Conference, 2023

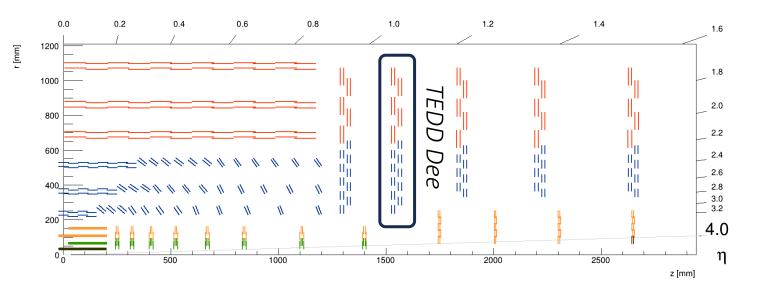

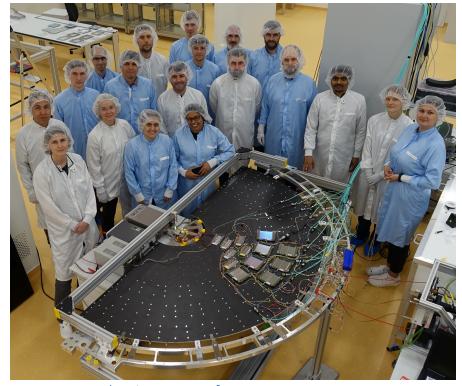

### OT System tests – TEDD Dee

- 13 2S and PS modules on a TEDD half disk:

- PS module noise different in some cases, due to prototype-specific known issues

- 2S module noise shows no significant increase on the dee compared to the measurement before integration

- Outlook

- Further integration tests planned

- With final modules

- With final support structures

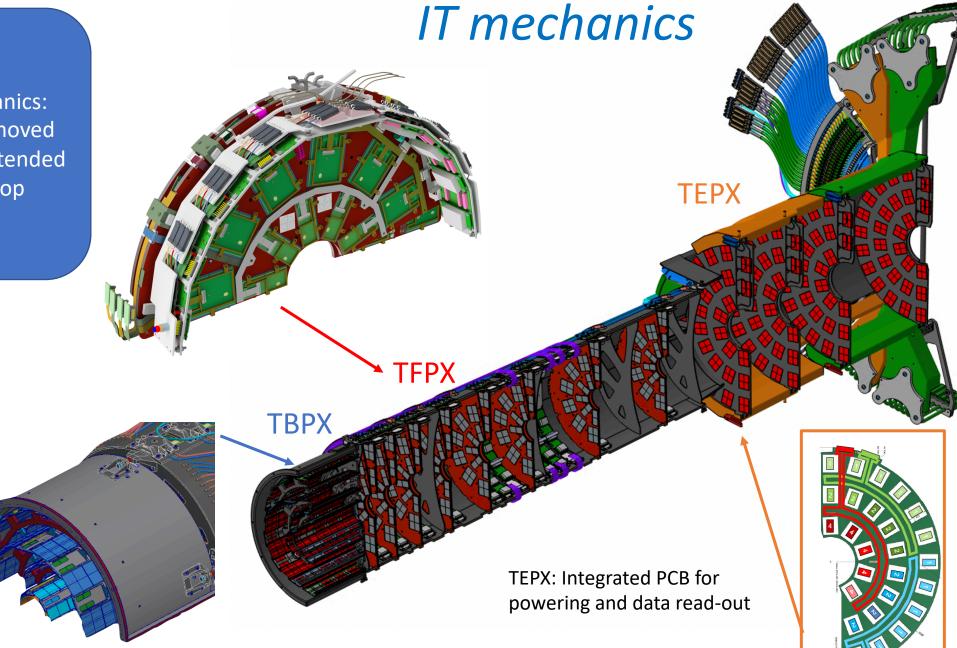

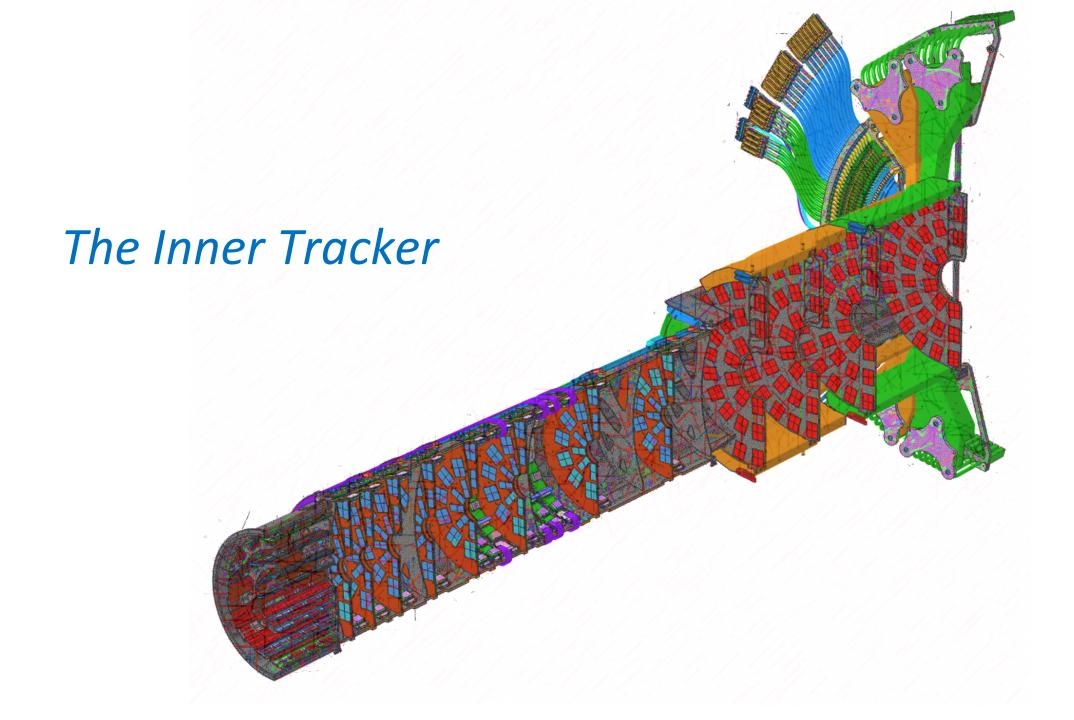

### Inner Tracker for Phase-2

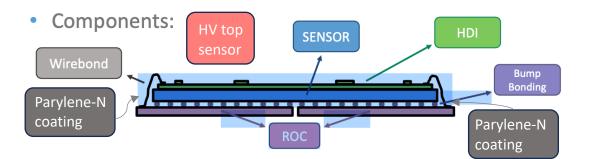

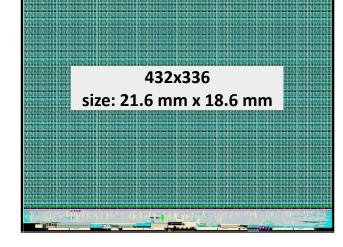

- Read Out Chip (ROC) only active element on module

- (1156) 1x2 ROC module and (2736) 2x2 ROC module

A. Macchiolo, The 16<sup>th</sup> Pisa Meeting on Advanced Detectors, 27<sup>th</sup> May 2024

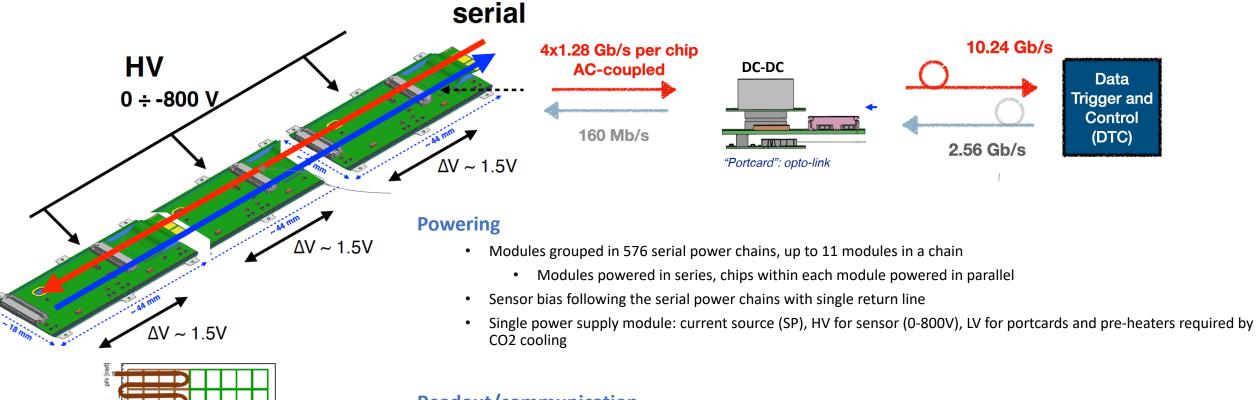

### IT Electronics system architecture

Innovation - new technology 65 nm TSMC ASIC enabling 50(25) x 50(100)  $\mu$ m<sup>2</sup> pitch at  $\simeq$  3 GHz/cm<sup>2</sup> (inner layer) Innovation - *serial powering* - only way to power 50 kW detector with reasonable material budget

#### Readout/communication

TBPX L1

- Hit rate ~ 3 GHz/cm<sup>2</sup> (inner layer), trigger latency 12.8  $\mu$ s  $\rightarrow$  ASIC buffer length

- Modules to LpGBT Up to 6 electrical up-links at 1.28 Gb/s

- LpGBT to Module One electrical down-link at 160 Mb/s

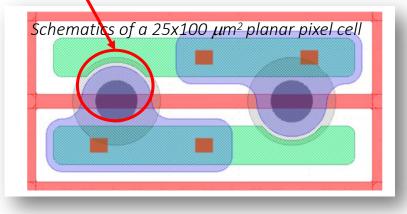

- = 150  $\mu$ m bulk thickness, 25x100  $\mu$ m<sup>2</sup> pixels cells everywhere

- Planar n-in-p sensors:

- Bias up to 600V and spark protection between ROC and sensors

- $\hfill Bump bonding pattern is 50x50 \,\mu m^2$

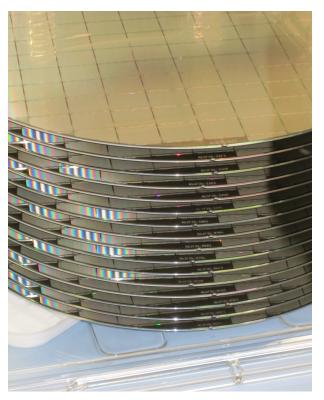

- Production started at HPK

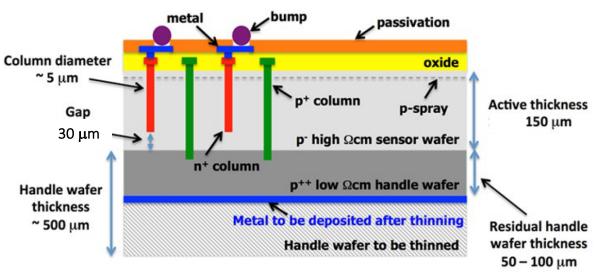

- 3D sensors for barrel L1

- Short drift distance ~50  $\mu$ m (3D) vs 150  $\mu$ m (Planar)

- Slim edges (150  $\mu m$  ) vs planar (~450  $\mu m$  )  $\rightarrow$  smaller dead zone

- Sensors pre-production well under way at FBK on 6" wafers

See characterization results before and after irradiation in the posters by <u>D. Zuolo (3D</u> <u>Sensors)</u> and <u>B. Raciti (planar sensors)</u> No n<sup>+</sup> implant under metal to reduce x-talk

# Pixel sensors

Structure of a 3D sensor – FBK process

### The CMS IT read-out chip

Designed by the RD53 collaboration

- 65 nm CMOS technology (current detector 250 nm)

- Radiation hard at least up to 0.5 Grad

- 50 x 50  $\mu$ m<sup>2</sup> pixel size  $\rightarrow$  compatible with 25 x 100  $\mu$ m<sup>2</sup> pixel size on sensors

- A shunt-LDO (SLDO) on each chip provides voltage regulation for each chip while maintaining a constant current

- 4 data links per chip at 1.28 Gb/s using Aurora encoding

- Data merging: read-out of up to three secondary chips through a primary one in the same module → reduction of data lines in low-occupancy layers

First engineering run delivered in January with a preliminary estimation of the yield at 77%

See poster of M. Grippo: <u>First results on the final readout chip for the</u> <u>High-Luminosity LHC upgrade of the CMS Inner Tracker</u>

- Test of the CROCv2 chips is on-going with digital (no-sensor) modules while waiting for the pre-production modules (~ August 2024):

- Good performance observed up to now (bugs on data merging affecting CROCv1 have been fixed)

- More detailed characterization after irradiation will follow

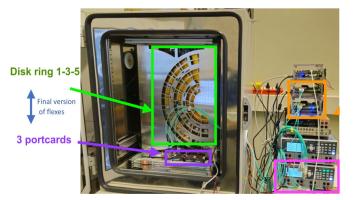

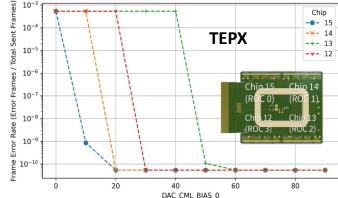

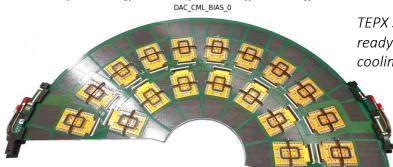

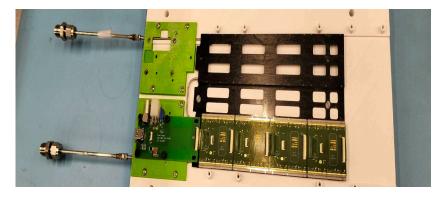

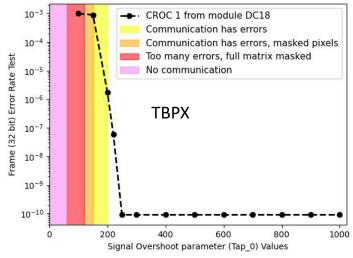

# System tests – Data integrity

TEPX Disk PCB with digital quad modules

Bit Error Rate vs Signal overshoot

- Test of the data transmission through the electrical and optical stages with modules powered in serial mode for the three subsystems

- Data integrity (Bit error rate) is studied as a function of a programmable overshoot to compensate for the signal attenuation in the transmission line

### Target values of the Bit Error Rate achieved

TEPX system test with half-disk ready to be connected to CO2 cooling system for thermal tests TBPX system test with modules mounted on L4 ladder

Bit Error Rate vs Signal overshoot

#### G. Bardelli, IFAE 2024

Under planning: tests of substructures with final components to ultimately validate the electronics and thermal performance

# Conclusions

- Design of the new CMS Tracker for Phase-2 driven by the inclusion of the Outer Tracker in the decision forming process for the L1 Trigger

- Highlight of the Inner Tracker is increased granularity and extended acceptance in the forward region from  $|\eta|{<}3$  to 4

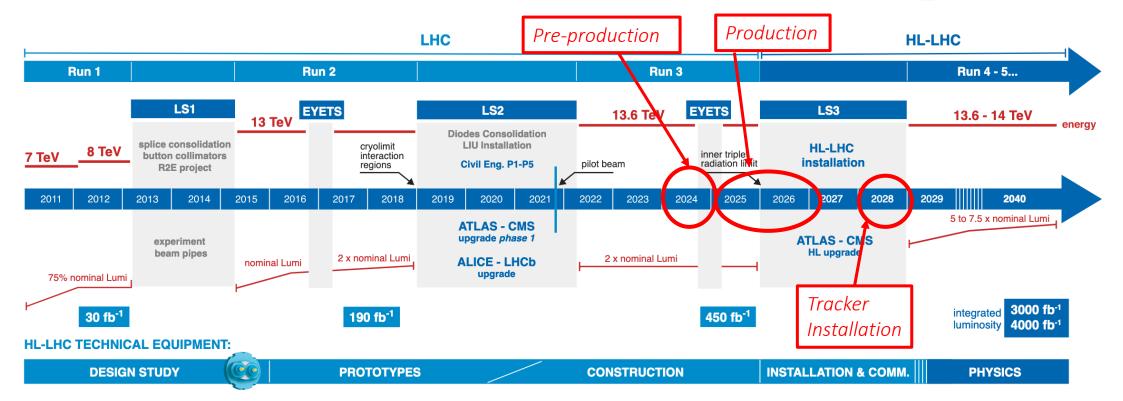

- Most of the components for Inner and Outer Tracking are in production or preproduction phase

- With the delivery and testing of the final version of the CROC ASIC for the Inner Tracker, all the Tracker ASICs have been validated and have entered production

- System tests being conducted to validate all the components, powering, read-out and thermal performance of the sub-detectors

- Still many challenges ahead of us for the timely accomplishment of the production and integration steps and the achievement of the design performance

# Additional slides

Light and simple mechanics: Inner Tracker can be removed for maintenance in an extended Year End Technical Stop

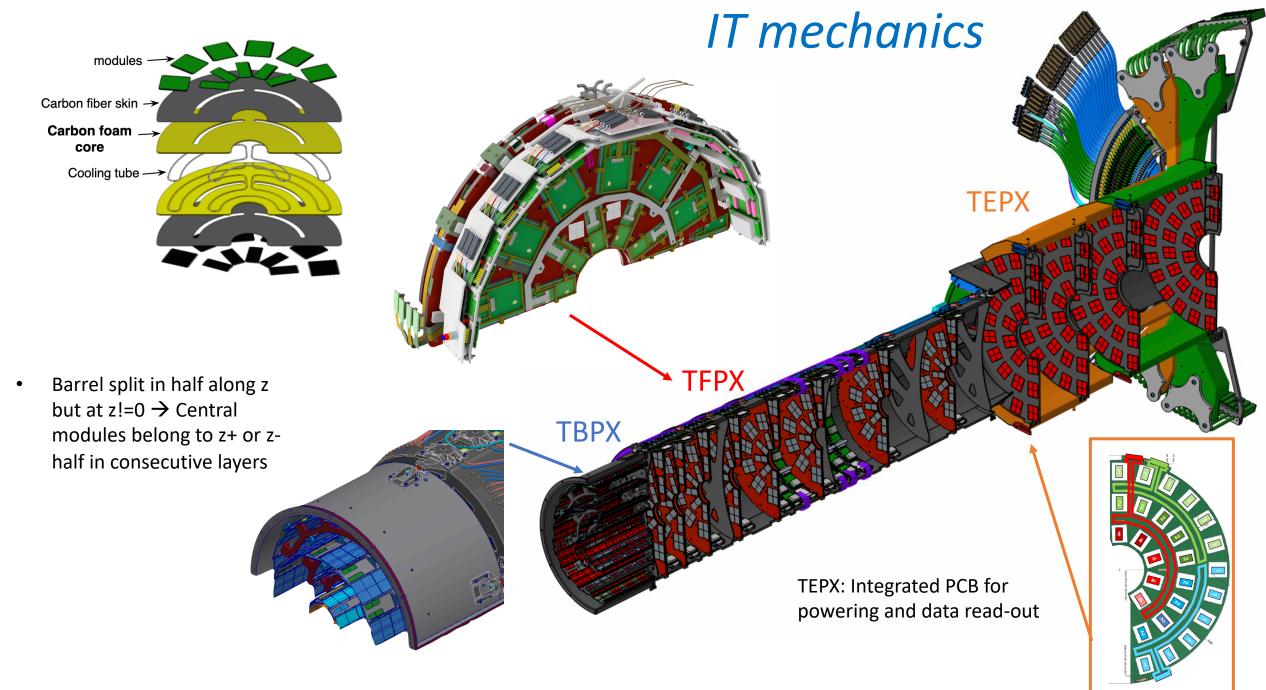

Barrel split in half along z but at z!=0 → Central modules belong to z+ or zhalf in consecutive layers