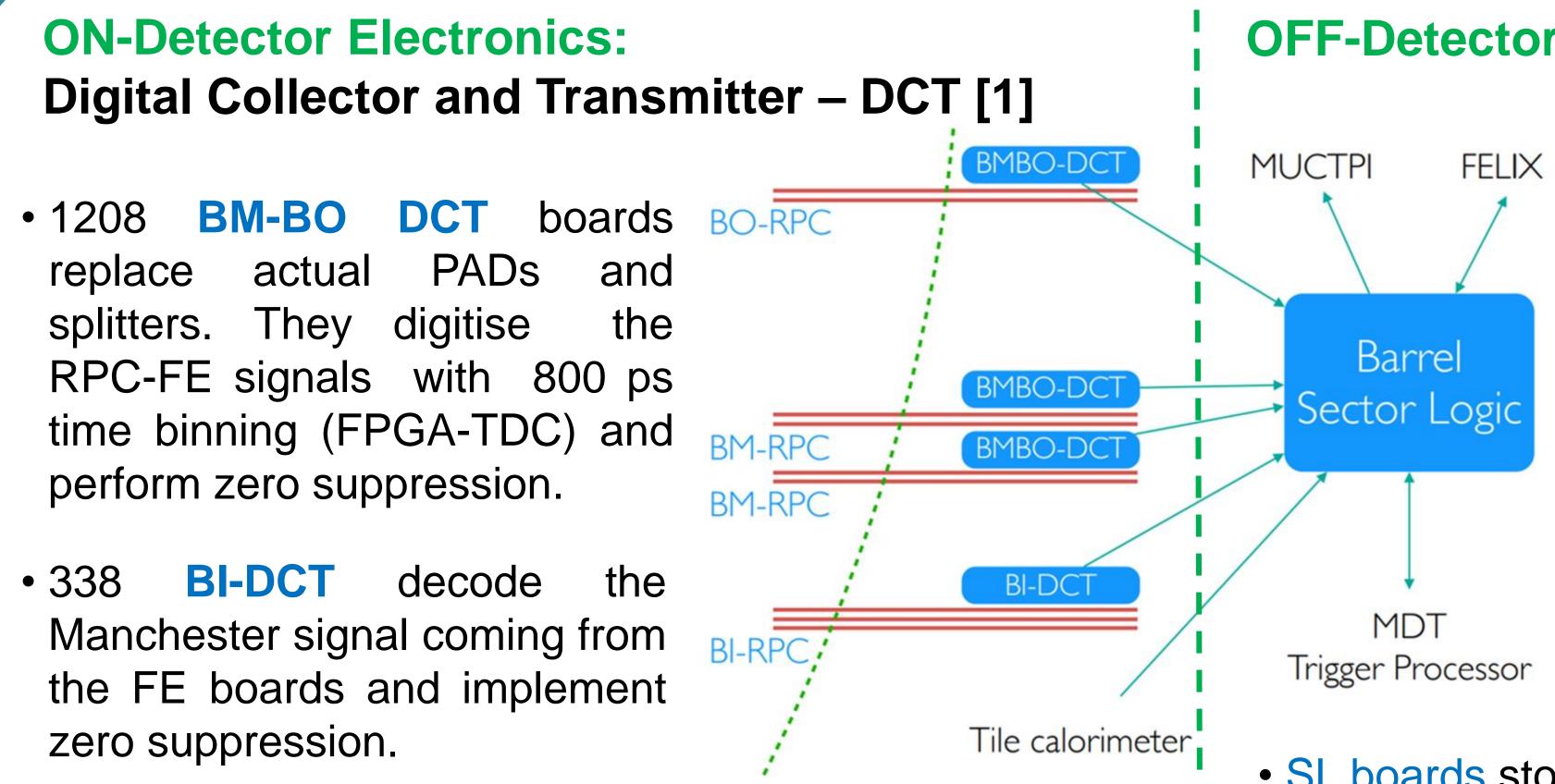

#### **OFF-Detector Electronics:** Sector Logic – SL [2]

- 32 barrel SL boards receive all the RPC data and control from the DCTs.

- Each SL board is connected with up to 50 DCTs through optical fibres.

• DCTs send zero suppressed data to barrel Sector Logic (SL) in counting room (USA15).

- SL boards produce trigger candidates based on RPC and Tile Calorimeter data and interface with the Monitored Drift Tubes (MDT) Trigger Processor (for further refinements).

- Final muon L0 trigger candidates sent to ATLAS central trigger through Muon Central Trigger Processor Interface (MUCTPI) board.

- SL boards store readout data into local memories during Level-0 trigger latency.

- Muon hit data is transmitted to High Level Trigger and readout system via FELIX modules when an LO-Accept signal is received.

# **BMBO-DCT and SL Hardware & Firmware Status**

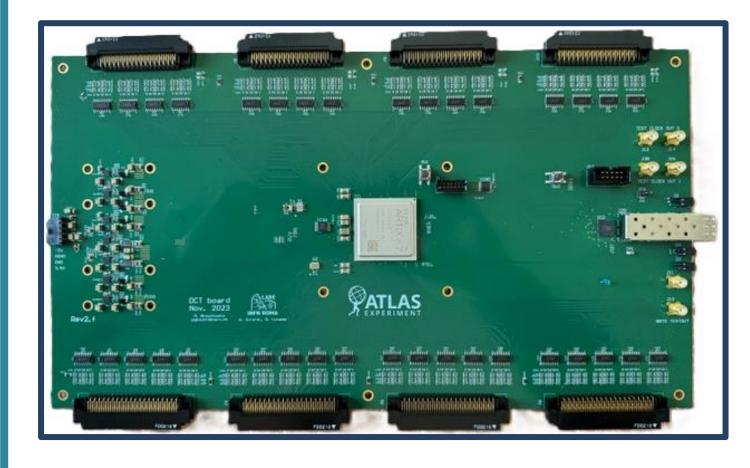

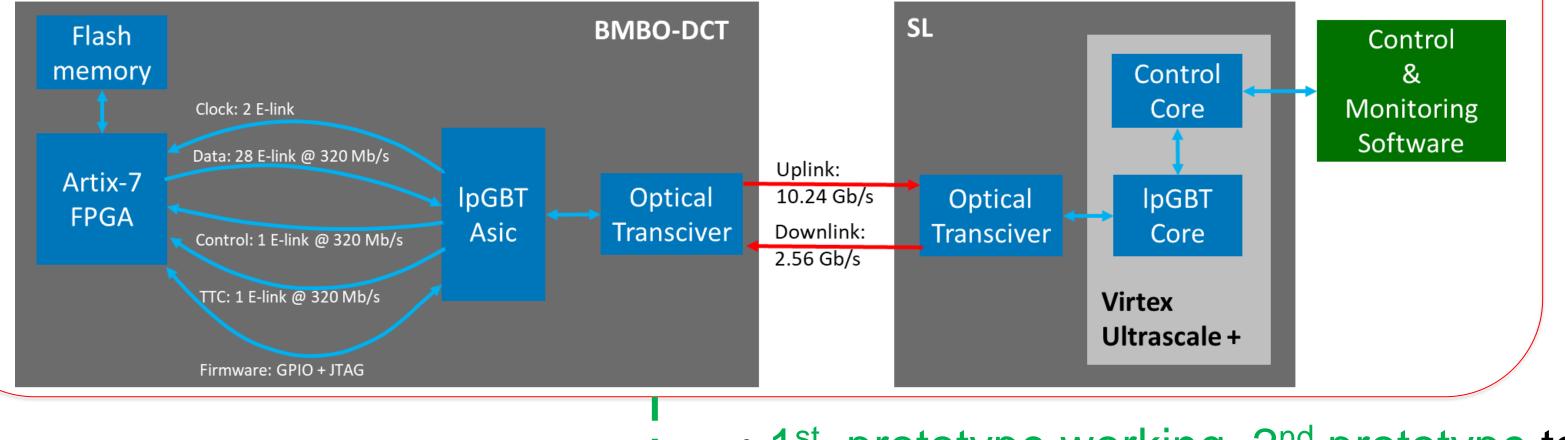

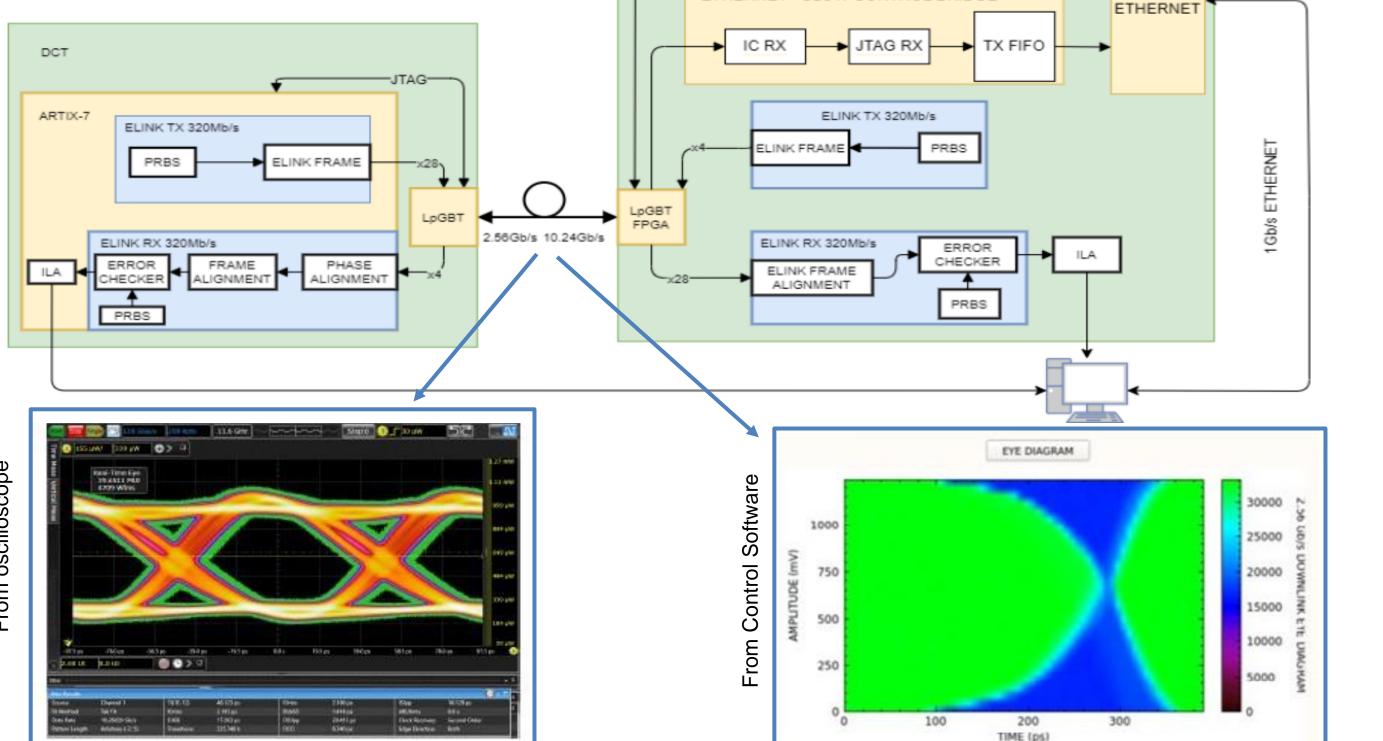

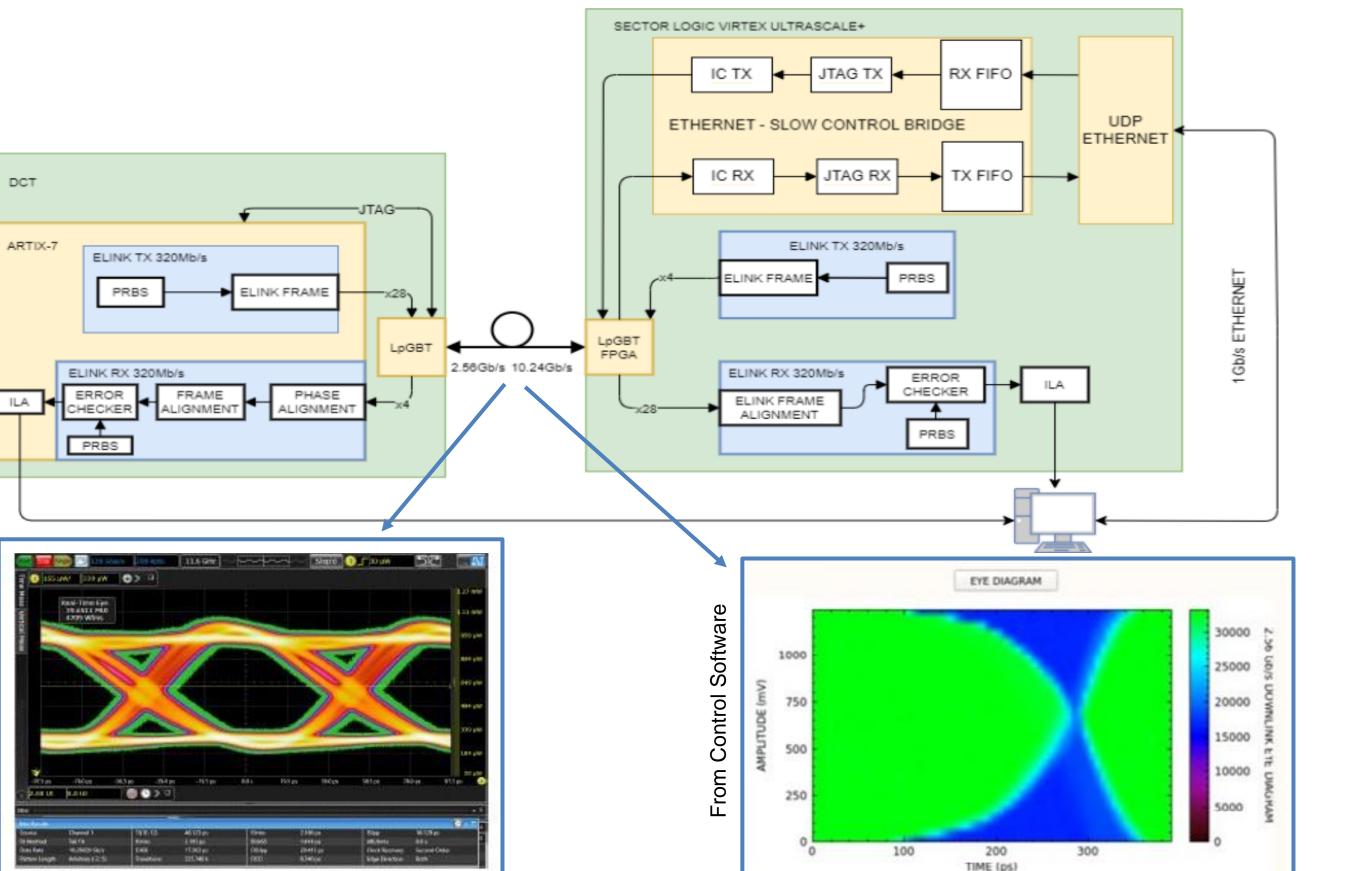

- BMBO-DCT FPGA-based on Artix-7 (XC7A200)

- **IpGBT ASIC** used to handle the serial data transmission between DCT and SL.

- Optical transmission with SFP+ optical module.

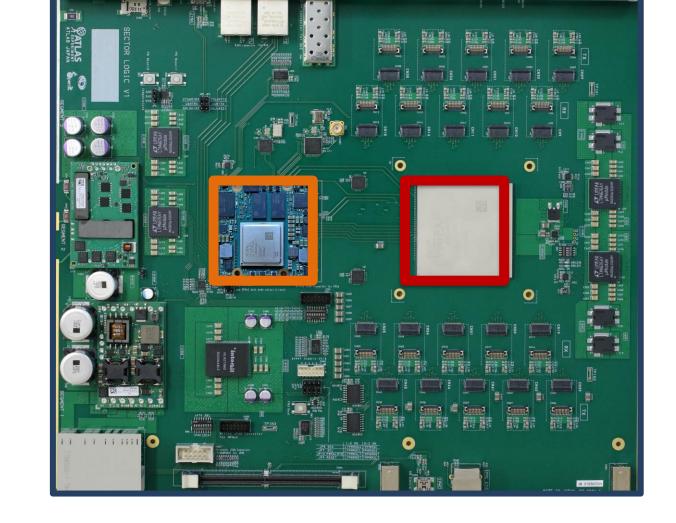

- SL FPGA-based on Virtex Ultrascale + (XCVU13P)

- **IpGBT interface** implemented on FPGA to handle the serial data transmission between DCT and SL.

- Optical transmission using Firefly optical modules.

#### **DCT-SL Interface**

• 1<sup>st</sup> prototype working.

- 2<sup>nd</sup> prototype recently produced, currently being tested.

- Firmware ready and tested in lab and on RPC detector.

- Rad-hard tests to be completed on 2024.

DCT to SL: 256bit @ 40MHz (10.24 Gb/s bandwidth, 8.96 Gb/s user data) SL to DCT: 32bit @ 80MHz (2.56 Gb/s bandwidth, 1.28 Gb/s user data)

- 1<sup>st</sup> prototype working, 2<sup>nd</sup> prototype to be delivered soon.

- Firmware ready, hardware tests ongoing.

- Different trigger algorithm approaches under investigation: spatial coincidences (roads), pattern matching, NN.

## Test communication between BMBO-DCT and SL in the L0 Muon test stand

### **Configuration & monitoring**

- Control software used for DCT/SL configuration, monitoring through ethernet connection.

- DCT FPGA, flash, and lpGBT configured via SL.

• DCT monitoring: reading voltages and temperatures from decoded IpGBT data.

**Data communication test**

- IBERT test @ 10.24 Gb/s.

- BER test: send packets with PRBS7 data using a delimiter (automatic phase and packet alignment). A logic block deserialises the frame and aligns them using a custom header.

- All Elinks tested both in uplink and downlink @ 320 Mb/s.

- **ILA** used to monitor transmission errors.

- No transmission errors found for a 24h test.

SAPIENZA Università di Roma Istituto Nazionale di Fisica Nucleare

1 ATLAS Collaboration. Technical Design Report for the Phase-II Upgrade of the ATLAS Muon Spectrometer. CERN-LHCC-2017-017. 2 ATLAS Collaboration. Technical Design Report for the Phase-II Upgrade of the ATLAS TDAQ System. CERN-LHCC-2017-020.