## ALICE Silicon Tracker Upgrades for LHC RUN4 and Beyond

Luca Aglietta on behalf of the ALICE collaboration

16th Pisa Meeting on Advanced detectors, La Biodola, 27/05/2024

Forward Calorimeter LOI: <u>CERN-LHCC-2020-009</u> TDR: <u>CERN-LHCC-2024-004</u> Not in this talk: →See *M. Inaba* poster in Calorimetry session!

ECAL

- RICH

Forward Calorimeter LOI: CERN-LHCC-2020-009 **TDR:** CERN-LHCC-2024-004 Not in this talk: →See M. Inaba poster in Calorimetry session!

Luca Aglietta (UniTO, INFN) | 27/05/2024 | 16th Pisa Meeting on Advanced Detectors

- Tracker

Vertex detector

TOF

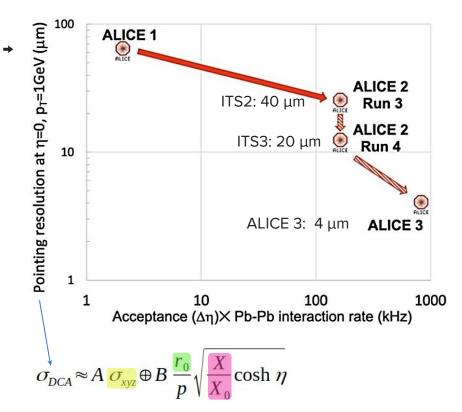

## **Upgrades motivations and requirements**

#### **Physics Motivations:**

Study of QGP in ultra-relativistic heavy-ions collisions search for rare, low momentum probes, reconstruction of displaced decay topologies:

- Heavy flavour hadrons at low  $p_{T}$

- Thermal dieleptons

- Precision measurements of light (hyper)nuclei and searches for charmed hypernuclei

#### Tracker upgrade requirements:

- Increase of effective acceptance (acceptance x readout rate)

- Improve tracking and vertexing performance low  $p\tau$  for combinatorial background suppression

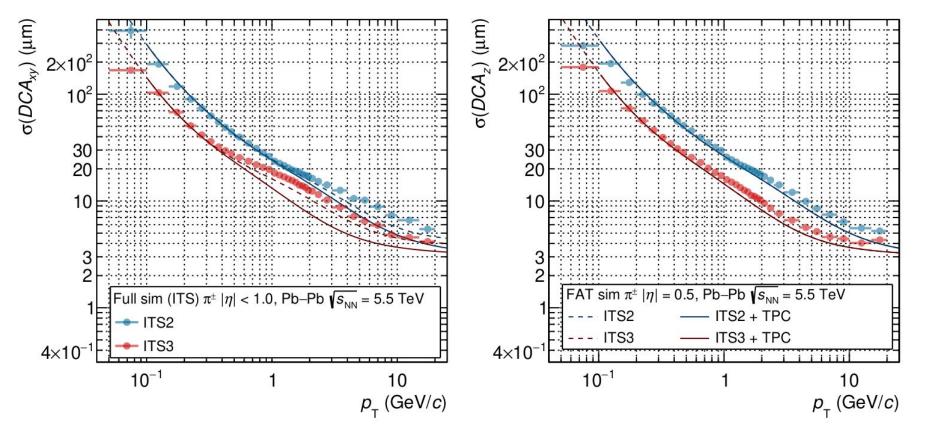

- → Excellent spatial resolution, minimal inner radius and low material budget are needed

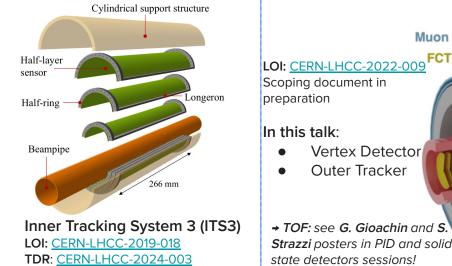

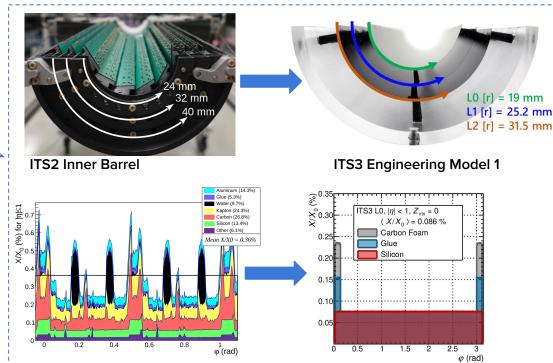

## The ITS3 Upgrade

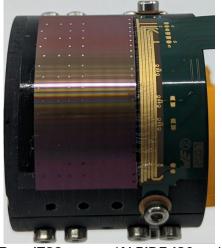

- Replacement of the Inner Barrel of the ITS2 with 3 layers of curved, 50 μm thick, wafer-scale MAPS in 65nm CMOS process

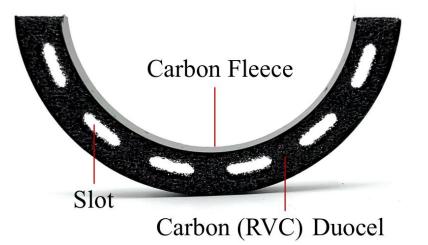

- Air cooling and ultra-light mechanical supports (carbon foam)

- Reduction of L<sub>0</sub> radius:

from 24 mm to 19 mm

- Reduction of material budget per layer:

- → from 0.36% X/X<sub>0</sub> to 0.09% X/X<sub>0</sub>

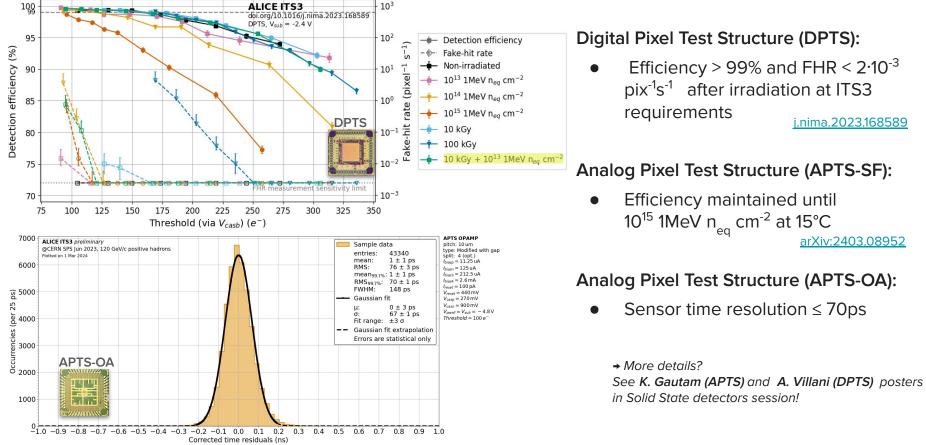

## Technology qualification: MLR1

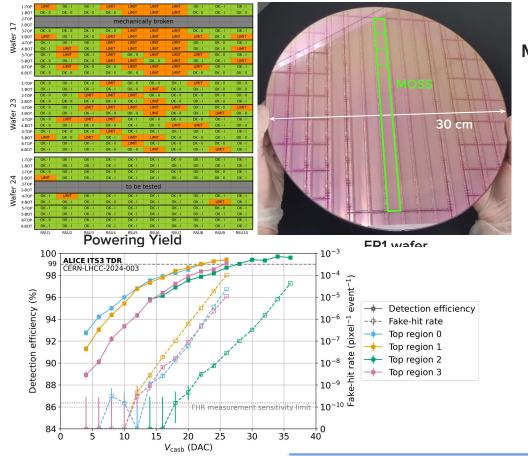

## Stitched MAPS: ER1

#### MOnolithic Stitched Sensor (MOSS):

- 10 Repeated Sensor Units stitched together: 259 mm x 14 mm per sensor

- 2 pixel pitches (18 μm and 22.5 μm) and 5 front-end variants

- Chip is **operational** and reaches **full efficiency**

- Yield: currently under study with extensive characterization campaign with wafer prober. Target < 2% dead pixels per layer</li>

## Performance of bent MAPS

Inefficiency associated tracks / total tracks)

10

10 of

-uou

(number

= 30 mm

= 24 mm

R = 18 mm

100

ALICE ITS3 beam test preliminar @DESY 5.4 GeV/c electrons Plotted on 29 Sept 2022

300

99% efficient

99.9% efficient

99.99% efficient

400

500

ALPIDE, Vhh = 0 V

200 Threshold (e<sup>-</sup>)

Working

Point

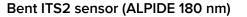

Bent 65 nm wafer bonded to FPC

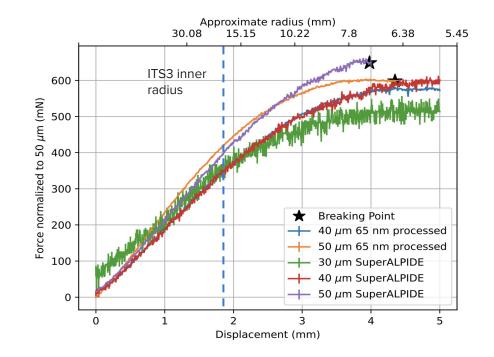

- 50 µm thick silicon sensors can be be bent to ITS3 target radius without breaking

- Test on bent ALPIDE chips show performance is unaffected  $\rightarrow$  No efficiency loss

- Results validated on bent 65 nm pixel test structures

- Electrical interconnections to FPC after bending through wire bonding

First results on bent MAPS: j.nima.2021.166280

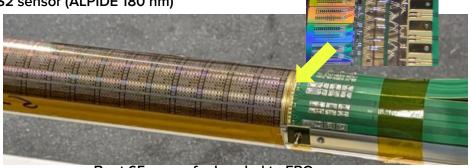

## **Thermo-mechanical characteristization**

Baseline cooling solution → air cooling.

- Tests in wind tunnel on breadboard model: dummy silicon sensor with copper serpentine heater

- Temperature differences in the sensor below 5°C with of 8 m/s airflow. (Thermal load: 25 mW cm<sup>-2</sup> in matrix, 1000 mW cm<sup>-2</sup> in end-caps)

- Mechanical assembly with carbon foam half rings keeps vibrations within ± 0.5 µm with 8 m/s airflow

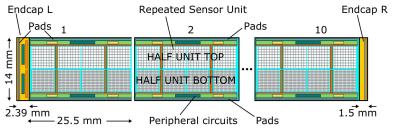

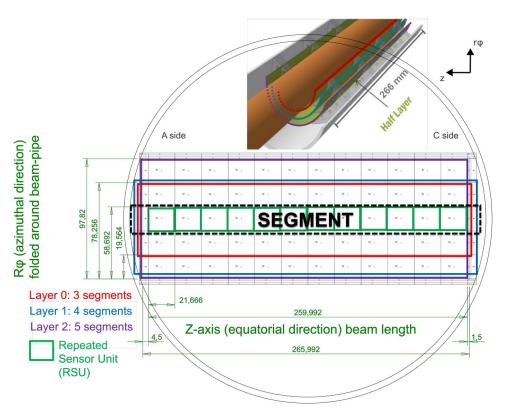

## **ITS3 Final Sensor Design: ER2 submission**

Design of **full-size** and **full-functionality** prototypes of the final sensor is being finalised incorporating learnings from MOSS testing:

- Modular design: each sensor is divided into 3, 4, or 5 segments with 12 RSUs.

- Each RSU is divided in turn in 12 fully independent tiles (powering, control and readout)

- Left end cap acts as a separate readout circuit on the same silicon wafer → interface with off detector electronics

- Submission to the foundry in fall 2024

11

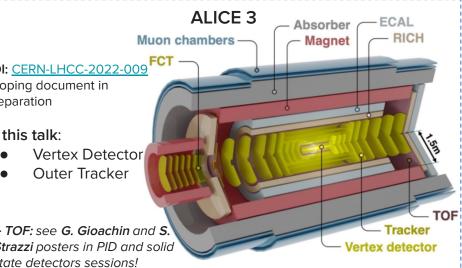

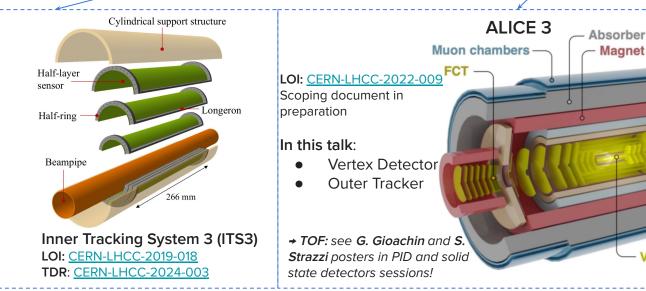

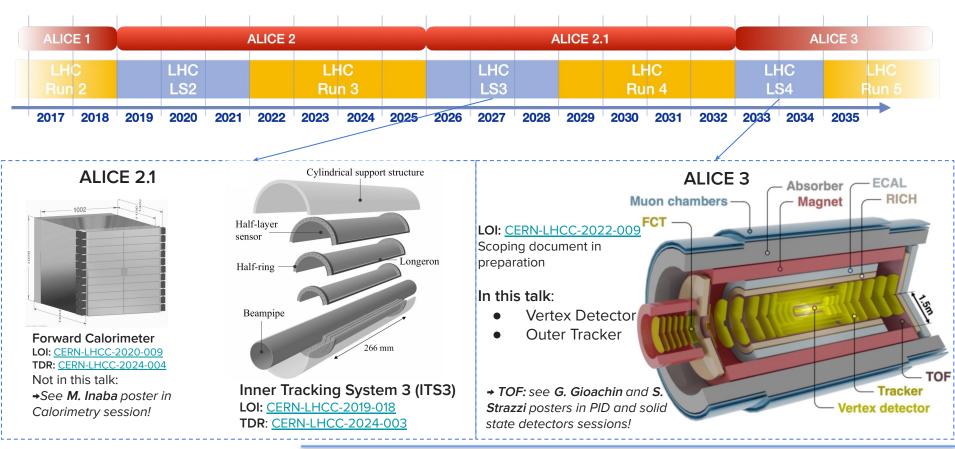

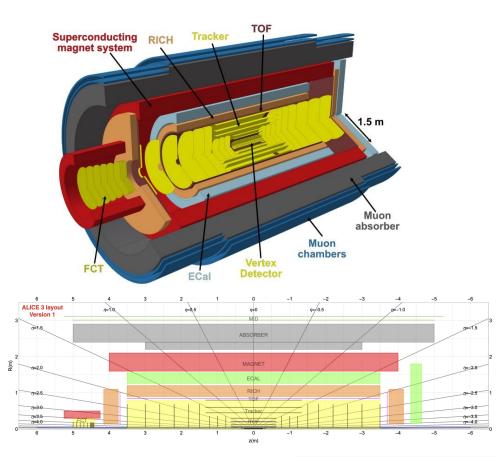

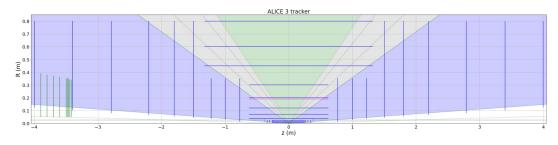

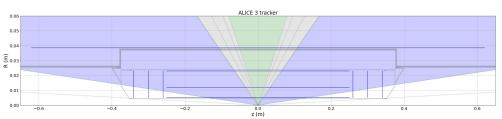

## ALICE 3 (LS4: 2033-2034)

Next generation compact experiment based on advanced silicon detectors

- Centered around a 60m<sup>2</sup> low-mass silicon tracker fully made of MAPS

- Retractable vertex detector for unprecedented pointing resolution

- Excellent PID capabilities thanks to TOF and RICH detectors

- Superconducting magnet (2T)

- Large acceptance:  $-4 < \eta < 4$

- Continuous readout and online data processing to access rare signals

- Muon Identification system, large acceptance Ecal and Forward Conversion Tracker for ultra-soft photons

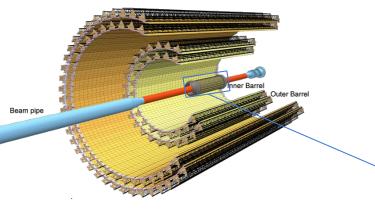

## **ALICE 3 Outer Tracker**

ALICE

- 8 barrel layers (3.5 cm < R < 80 cm) and 2 x 9 end-cap disks

- Material budget: 1% X/X₀ per layer

→ < 10% X/X₀ for entire tracker</li>

- Space resolution: 10  $\mu$ m  $\rightarrow$  50  $\mu$ m pixel pitch

- Low power consumption: 20 mW/cm<sup>2</sup>

- **100 ns** time resolution to mitigate pileup

#### Main R&D challenges:

- Modules integration for mass industrialization

- Power consumption while preserving timing performance

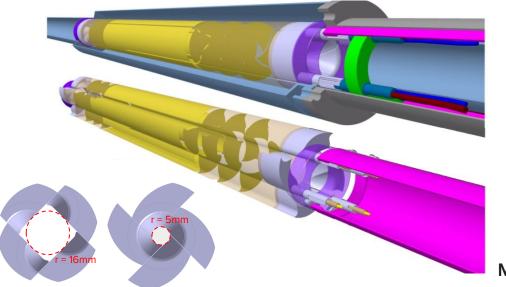

## **ALICE 3 Vertex Detector**

- 3 barrel layers and 2 x 3 end-cap disks of ultra-thin, curved, wafer-scale MAPS

- Retractable structure inside the beam pipe in secondary vacuum: Iris Tracker

- First detection layer at **5 mm** from the interaction point

- Unprecedented spatial resolution: 2.5 μm

- Extremely low material budget: 0.1% X/X<sub>0</sub>

- Hit rate: **35 MHz cm**<sup>-2</sup>

#### Main R&D challenges:

- Radiation hardness: 10<sup>16</sup> 1MeV n<sub>eq</sub> cm<sup>-2</sup> + 300 Mrad (LOI values)

- Mechanics and cooling

- 10 µm pixel pitch

- Data and power distribution

- → R&D will build up on ITS3 experience

## Summary and Outlook

ALICE ITS3 project is on track for being installed in LS3 :

- bent MAPS performance demonstrated in beam

- 65 nm process qualified with MLR1 pixel structures

- stitched design exercised, testing is ongoing

- assembly procedure with curved wafer-scale sensors defined

- air cooling solution validated

- TDR reviewed by LHCC and approved by Research Board: <u>CERN-LHCC-2024-003</u>

ALICE 3, proposed for LHC run 5, will further push the limits of MAPS technology:

- LOI: <u>CERN-LHCC-2022-009</u>

- large-scale integration (60 m<sup>2</sup> outer tracker)

- increased spatial resolution, radiation hardness and rate capabilities + in-vacuum operation (vertex detector)

- Scoping document is being redacted: submission to the LHCC in fall 2024

# Thank you for your attention!

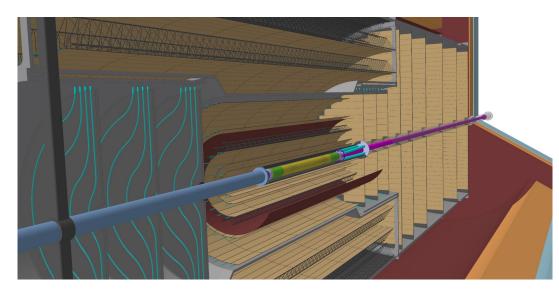

*In the background:* Render of the full ITS3 geometry implemented in ALICE simulation and reconstruction software (O2)

16th Pisa Meeting on Advanced detectors, La Biodola, 27/05/2024

## Backup

16th Pisa Meeting on Advanced detectors, La Biodola, 27/05/2024

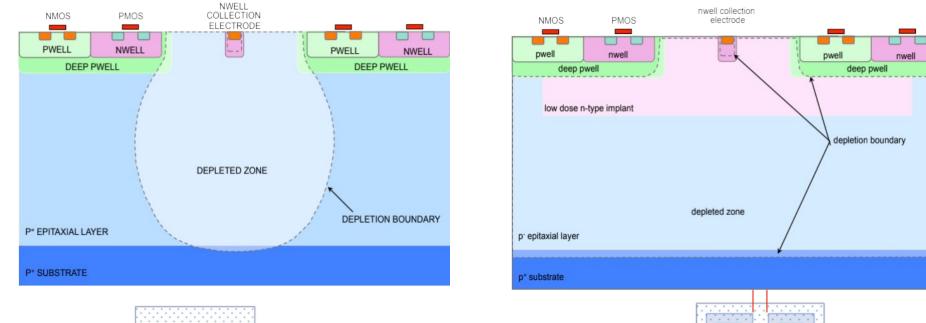

## **Modified MAPS production process**

Snoeys, W., et al. "Optimization of a 65 nm CMOS imaging process for monolithic CMOS sensors for high energy physics." *PIXEL 2022.*

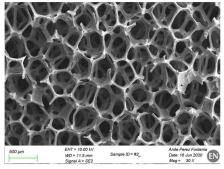

### **Ultra-light detector mechanics**

with the second seco

(a) Carbon (RVC)  $Duocel^{\textcircled{R}}$

## **Bending Force**

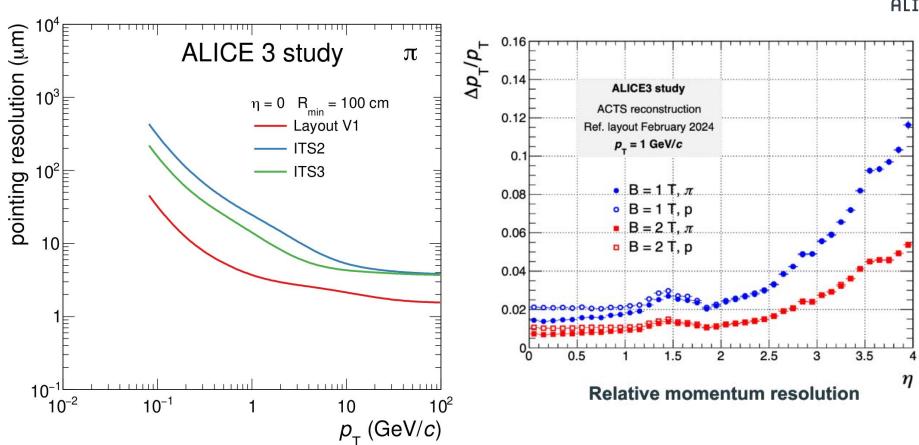

## **ITS3** Pointing resolution

## **ALICE 3 Tracking performance**