# HASPIDE WP2

### Valentino Liberali, INFN Milano

June 14, 2023

HASPIDE WP2

June 14, 2023 1 / 11

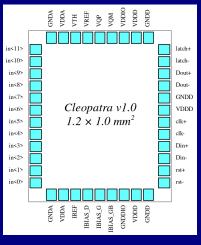

### Cleopatra v1.0

Test ASIC pinout

- Technology : CMOS 28 nm

- 12 channels recycling integrator

- Simple serial interface

- Submitted on April 26<sup>th</sup> 2023

- Expected back on August 2023

- Board design ongoing

HASPIDE WP2 status

HASPIDE WP2

June 13<sup>th</sup> 2023

June 14, 2023 2 /

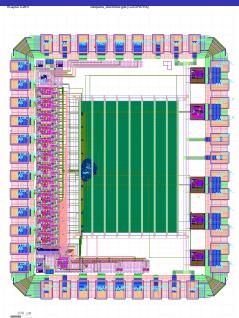

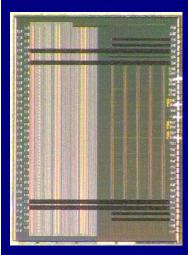

# cleopatra1 - layout

- Layout submitted to IMEC on May 2, 2023

- PAD ring designed using the rad-hard library provided by CERN

Image: A math a math

HASPIDE WP2

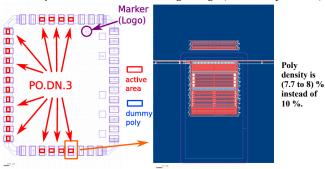

# cleopatra1 - waived DRC error

### Device name: INFN\_Cleopatra

□ Violated rule: PO.DN.3

Failed coordinates: left: (67.325, 167.325) to (67.325, 1147.325); bottom: (367.325, 67.325) to (637.325, 67.325); top: (367.325, 1247.325) to (637.325, 1147.325) - 20 violations in total.

Customer comment: Radiation-hard pads have large diodes and we cannot draw poly over active area.

Whole chip

ß

### Enlarge image (shows why violate)

Image: A math the second se

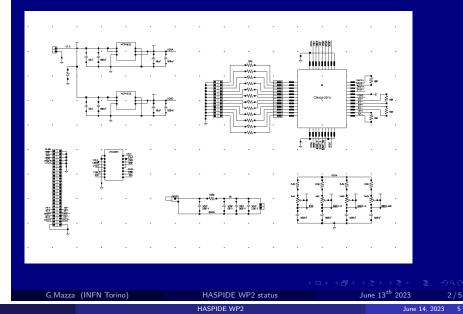

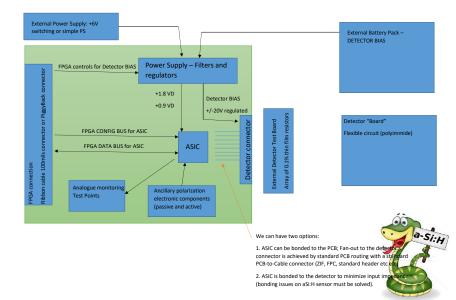

# Test board schematic ( $\alpha$ release)

5 / 11

## Test board - requirements from UoW

イロト イヨト イヨト イヨ

### Cleopatra v2.0

- Based on v1.0, 32 or 64 channels

- 32 channels

- Estimated size :  $1.5 \times 2 \text{ mm}^2$

- Possible package : QFN64 9×9 mm<sup>2</sup> €163/pkg

- 64 channels

- Estimated size : 2.8×2 mm<sup>2</sup>

- Possible package : CERQUAD FP 128, 11.6×11.6 mm<sup>2</sup>, €194/pkg

- Submission in 2Q2024

G.Mazza (INFN Torino)

HASPIDE WP2 status

2020

HASPIDE WP2

- for MPW: must ask IMEC

- for miniASIC: 8229  $\in$  / 1 mm² (min area) + 788  $\in$  / 0.1 mm² (additional area) + VAT

- 3 mm<sup>2</sup>: ≈ 30 k€

- 5.6 mm<sup>2</sup>: ≈ 55 k€

Image: A match a ma

# Chip for single particle detection

- Designed for the PANDA MVD

- 64 channels ASIC for strip readout

- Detector capacitance 2÷17 pF

- ToA and ToT measurement

- Input charge up to 50 fC

- Reference clock 160 MHz

- Die size  $3.24 \times 4.41 \text{ mm}^2$

- Time resolution (rms) 1.8 ns

- CMOS UMC 0.11  $\mu$ m technology

G.Mazza (INFN Torino)

HASPIDE WP2 status

HASPIDE WP2

June 14, 2023 9 / 1

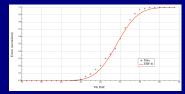

### Test results

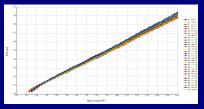

### Linearity after calibration (Gain 60ns/fC)

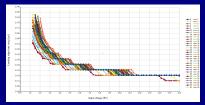

#### Time resolution (before ToT correction)

#### Beam test scheduled for August 2023 at Cosy

G.Mazza (INFN Torino)

HASPIDE WP2 status

### Noise (without sensor) $\approx$ 300 e<sup>-</sup>

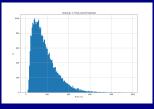

# ToT distribution connected to a strip sensor and exposed to a $\mathrm{Sr}^{90}$ source

June 13th 2023

#### June 14, 2023 10 / 11

5/5

HASPIDE WP2

- in 2023: 1 Assegno di Ricerca "junior" Milano

- in 2024:

- fabrication of the second prototype: depends on area

- test board for the second prototype: 2 k  $\in$

- travel ?

Image: A match a ma