# Development of monolithic sensors for high energy physics in TPSCo 65nm ISC technology

CERN EP R&D

WP1.2 Monolithic Pixel Detectors

Many contributors, see next page

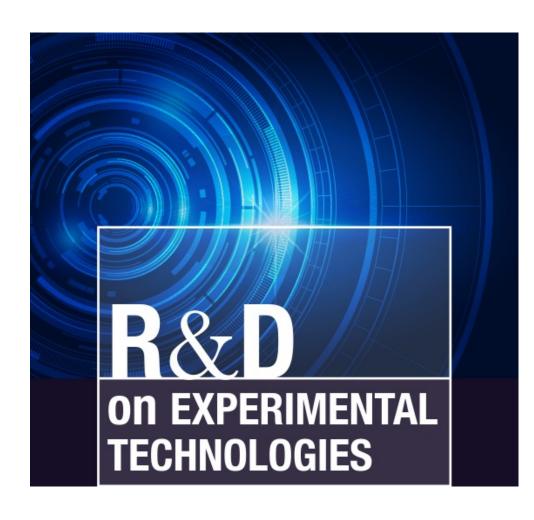

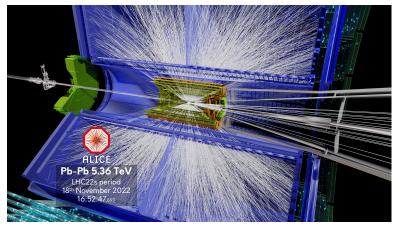

Strong synergy with ALICE ITS3 upgrade

# Development of monolithic sensors for high energy physics in TPSCo 65nm ISC technology

on experimental

**TECHNOLOGIES**

University and INFN Torino: F. Benotto, S. Beole, C. Ferrero U. Savino, S.

Perciballi, F. Prino, A. Turcato

University and INFN Bari: G. De Robertis, F. Loddo University and INFN Catania: P. La Rocca, A. Triffiro

University and INFN Cagliari: D. Marras, , V. Sarritzu, G. Usai

University of Salerno and Bologna: R. Ricci

University and INFN Trieste: M. Antonelli, R. Baccomi, M. Buckland, P.

Camerini, G. Contin, S. Rashevski A. Villani

CPPM: P. Barrillon, M. Barbero, D. Fougeron, A. Habib, P. Pangaud

IPHC: J. Baudot, G. Bertolone, A. Besson, S. Bugiel, C. Colledani, A.

Dorokhov, Z. El Bitar, X. Fang, M. Goffe, C. Hu, K. Jaaskelainen, F. Morel, H.

Pham, S. Senyukov, J. Soudier, I. Valin, Y. Wu (also with USTC)

**NIKHEF**: R. Russo, V. Gromov, D. Gajanana, A. Yelkenci, A. Grelli, R. Kluit, J.

Sonneveld, A. Vitkovskiy

Heidelberg University: P. Becht, S. Masciocchi, M.W. Menzel, H.K. Soltveit, A.

Yuncu, J. Stachel

Munster University: A. Andronic, N. Tiltmann

**Prague University**: A. Isakov, A. Kotliarov, F. Krizek

STFC (RAL): S. Matthew, I. Sedgwick

Birmingham University: L. Gonella

Technical University Munich: L. Lautner, I. Sanna (also with CERN), L. Fabiette

**Technical University Vienna**: J. Hasenbichler (also with CERN)

DESY: K. Hansen, C. Reckleben, S. Spannagel

Yonsei University: Y. Kwon, G.H. Hong CCNU: Wenjing Deng (also with CERN) EPFL: E. Charbon, F.Piro (also with CERN)

SLAC & Stanford U: M.D. Vassilev, C. Vernieri

CERN:, G. Aglieri Rinella, W. Bialas, G. Borghello, R. Ballabriga, J. Braach,

**CERN:**, G. Aglieri Rinella, W. Bialas, G. Borghello, R. Ballabriga, J. Braach, E. Buschmann, M. Campbell, F. Carnesecchi, L. Cecconi, D. Dannheim, K. Dort, Joao de Melo, W. Deng (also with CCNU), A. Di Mauro, A. Dorda Martin, P. Dorosz, J. Hasenbichler (also with TU Vienna), H. Hillemans, A. Junique, I. Kremastiotis, A. Kluge, G. Kucharska, T. Kugathasan, P. Leitao, M. Mager, P. Martinengo, M. Munker, L. Musa, F. Piro, K. Rebane, F. Reidt, I. Sanna (also with TU Munich), <u>W. Snoeys</u>, P. Svihra, M. Suljic, G. Termo, J. B. Van Beelen

Foundry support: TPSCo: M. Suzuki, Tower Semiconductor: A. Fenigstein,

and Etesian Semiconductor: A. Haim, E. Toledano

#### EP RD WP1.2 on monolithic CMOS sensors

#### Long term goal: develop CMOS sensors in sub 100nm technologies

Synergy with development of the stitched sensor in the ALICE ITS3 upgrade

#### First technology selected: TPSCo 65 nm CMOS imaging technology

- TPSCo (joint venture TJ & Panasonic): several 65 nm flavors: high density logic, RF, and imaging (ISC)

- ISC preferred: 2D stitching experience, special sensor features, different starting materials, lower defect densities, etc

- Initially 5 metal layers, now 7 metals

First submission: MLR1 December 2020

**Second submission: ER1 November 2022**

65 nm development profited significantly from 10 years of experience in TowerJazz 180 nm.

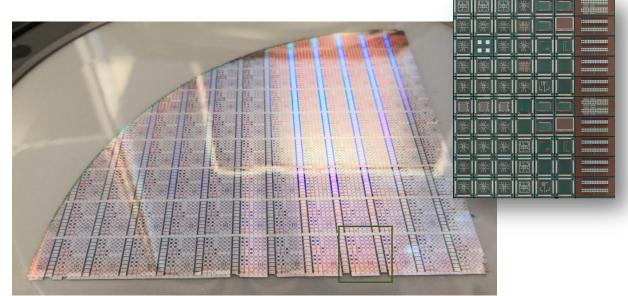

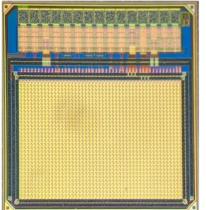

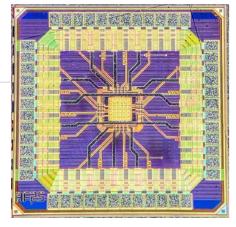

# MLR1 Submission – December 2020

- First submission in TPSCo 65 nm CMOS Imaging

- Learn technology features

- Characterize devices

- Prototype circuits, blocks and pixel structures

•  $1.5 \times 1.5 \text{ mm}^2 \text{ test chips}$

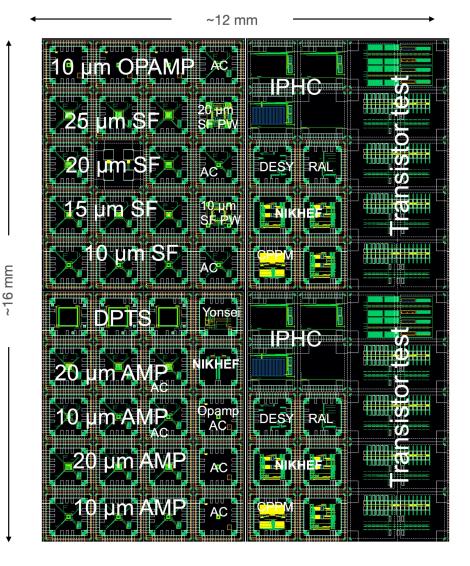

# MLR1 Chips and Features

- Transistor Test Structures

- Building blocks

Bandgap, DACs, Temperature sensor, VCO, drivers ...

NIKHEF, IPHC, STFC, DESY, CPPM

- Pixel Prototypes APTS, DPTS, CE65

Other pixel prototypes from DESY, Yonsei

- Process Optimisation

- Increase margins on sensing performance

#### **APTS**

4x4 pixel matrix 10, 15, 20, 25 μm pitches Pixel variants Direct analogue readout

#### **DPTS**

$32 \times 32$  pixels  $15 \mu m$  pitch Asynchronous digital readout ToT information

#### **CE65**

64 × 32 pixels 15 μm pitch Rolling shutter analog readout 3 pixel architectures

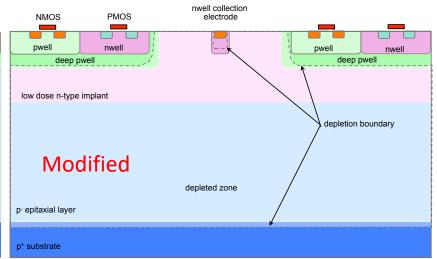

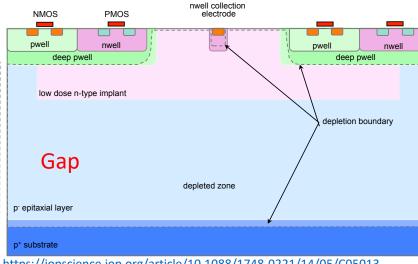

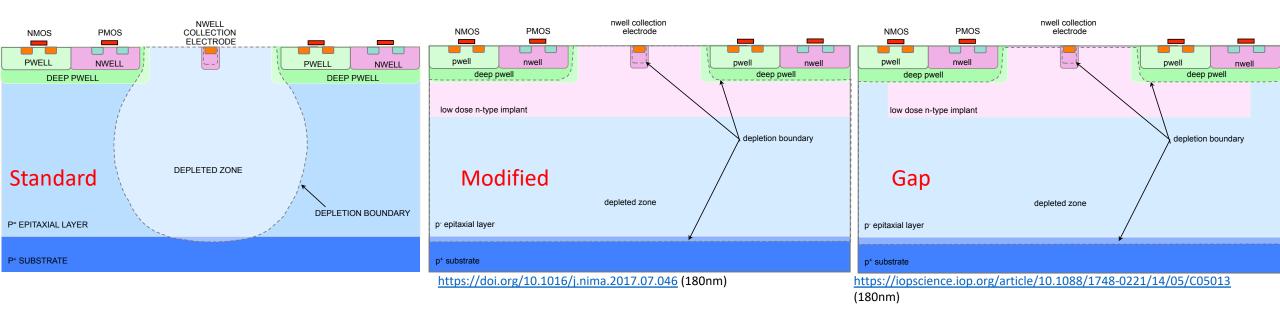

# Pixel optimization in 180 nm (started in 2012)

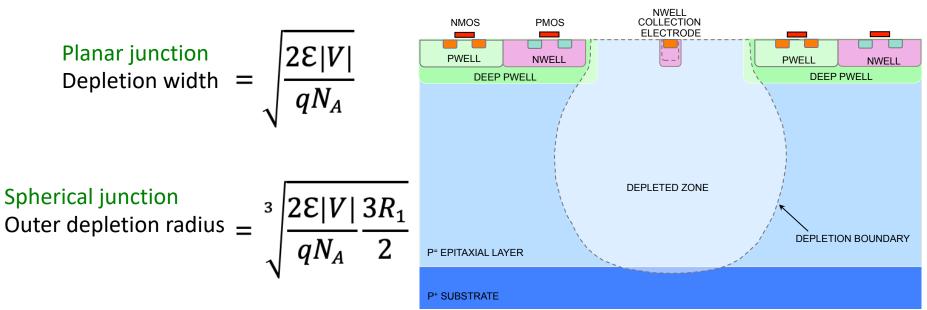

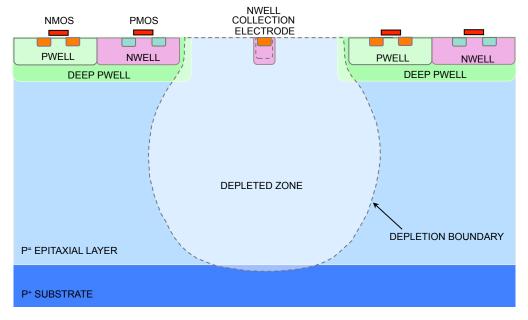

# ALPIDE and ITS2 in ALICE (10 m²) NMOS PMOS COLLECTION ELECTRODE PWELL NWELL DEEP PWELL DEEP PWELL DEPLETED ZONE DEPLETION BOUNDARY

efficiency loss at  $\sim 10^{15}$  1 MeV  $n_{eq}/cm^2$

E. Schioppa et al, VCI 2019

https://doi.org/10.1016/j.nima.2017.07.046 (180nm)

H. Pernegger et al., Hiroshima 2019, M. Dyndal et al 2020 JINST 15 P0200

https://iopscience.iop.org/article/10.1088/1748-0221/14/05/C05013

Charge collection speed

P\* EPITAXIAL LAYER

P+ SUBSTRATE

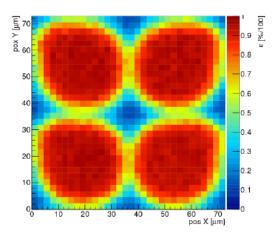

# Process optimization: 65 nm very similar

Charge collection speed

Charge sharing

"10th International Workshop on Semiconductor Pixel Detectors for Particles and Imaging" PoS(Pixel2022)001, DOI: <a href="https://doi.org/10.22323/1.420.0001">https://doi.org/10.22323/1.420.0001</a>

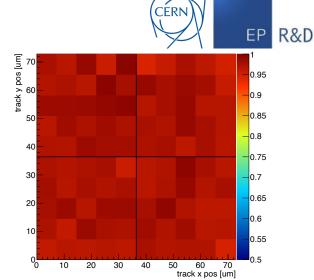

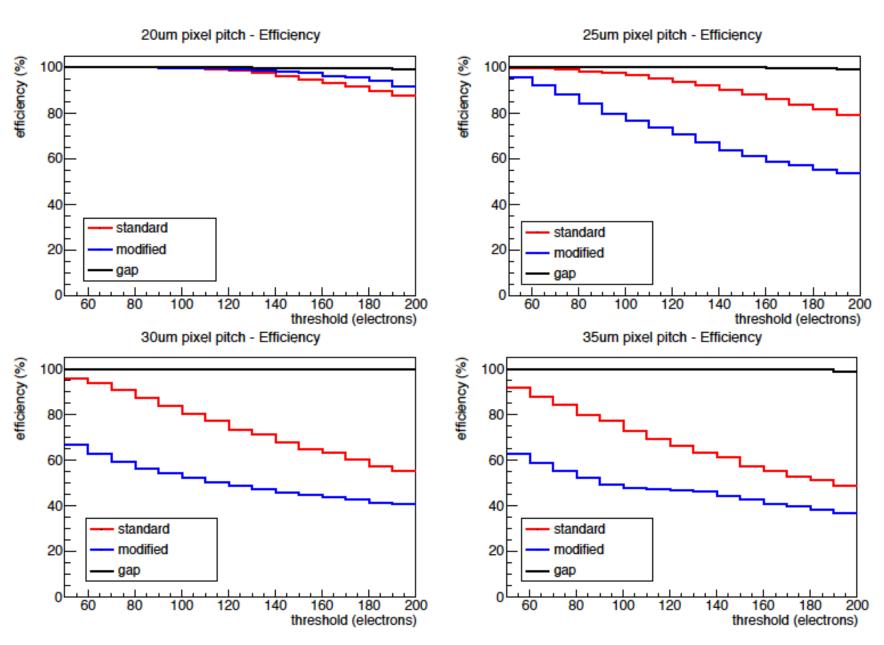

# Different pixel flavors at larger pixel pitches

Simulations by J. Hasenbichler for MIPS

Charge sharing reduces the signal in a single pixel and reduces efficiency especially for larger thresholds.

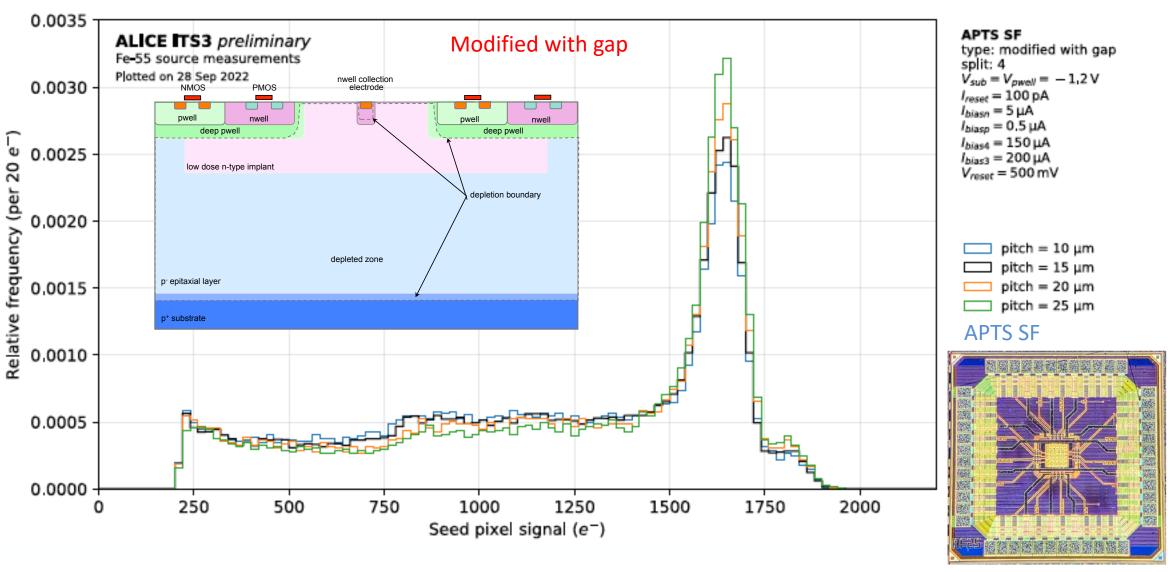

Only the gap concentrates charge sufficiently to remain efficient for large pixel pitches

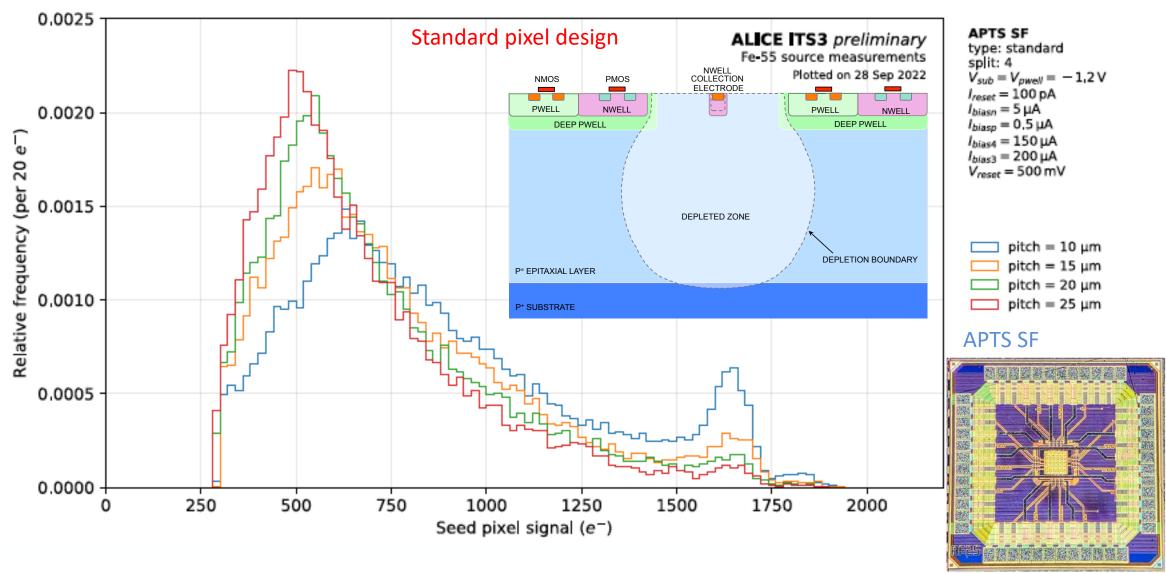

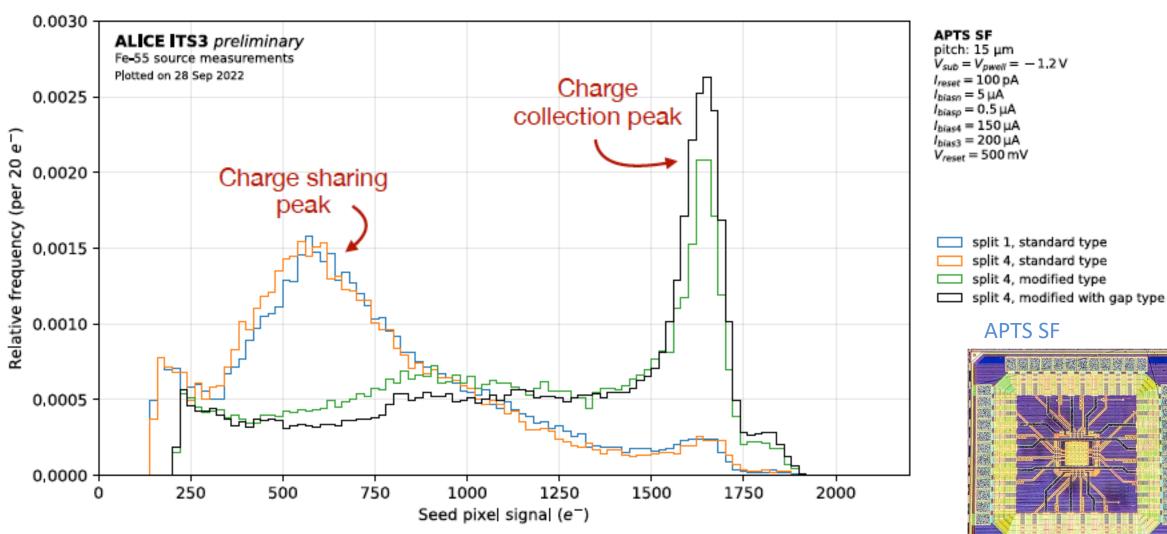

# Pitch dependence for different variants <sup>55</sup>Fe

See also: I. Sanna IEEE NSS 2022

## Pitch dependence for different variants <sup>55</sup>Fe

See also: I. Sanna IEEE NSS 2022

#### Remarkable result!

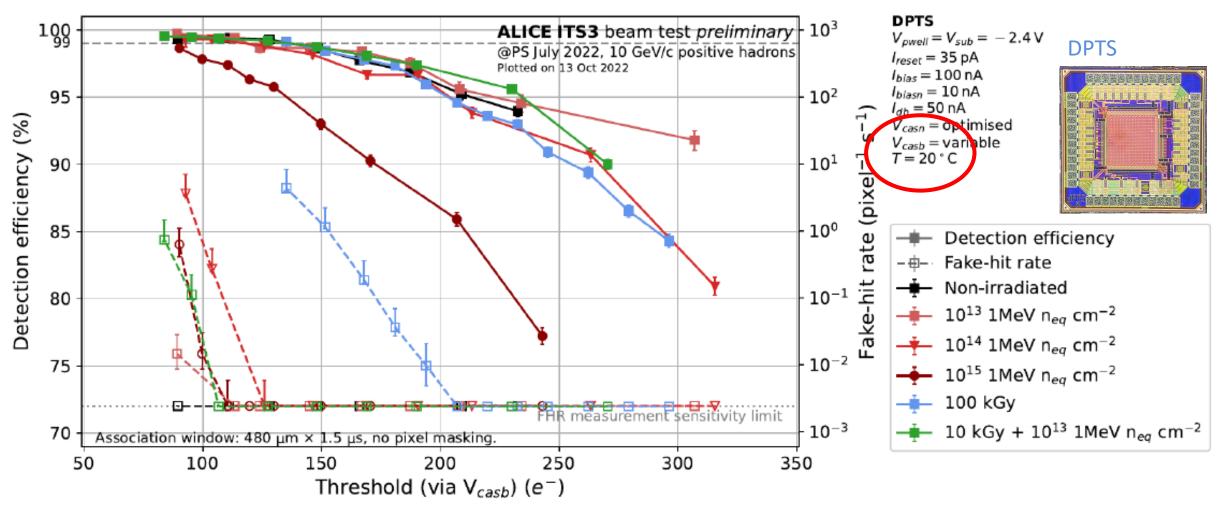

# $\sim$ 99 % efficiency at $10^{15}$ $n_{eq}/cm^2$ ... at room temperature

#### **ADD REFERENCE**

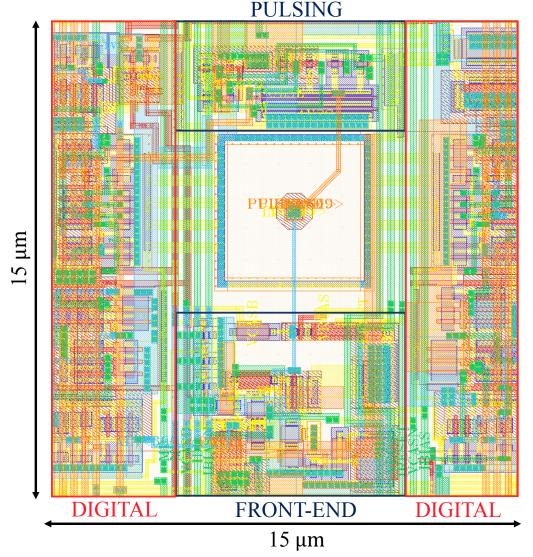

• Fully efficient sensor, analog front end, digital readout chain in 15 x 15 μm² pixel (DPTS) including sensor optimization

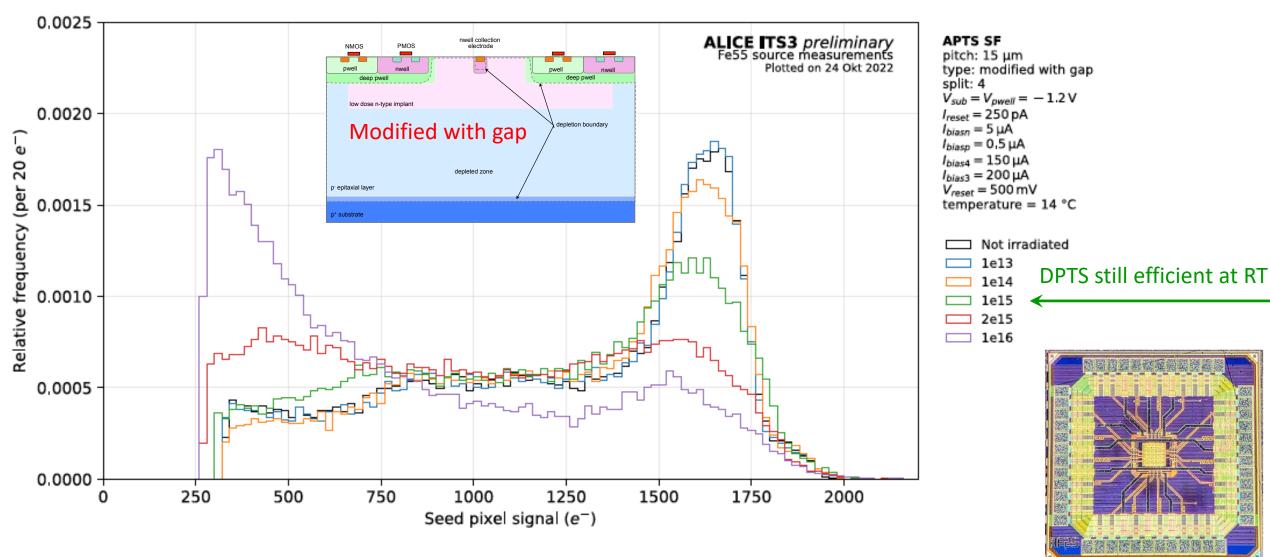

# Irradiation results: exploring paths to higher fluences

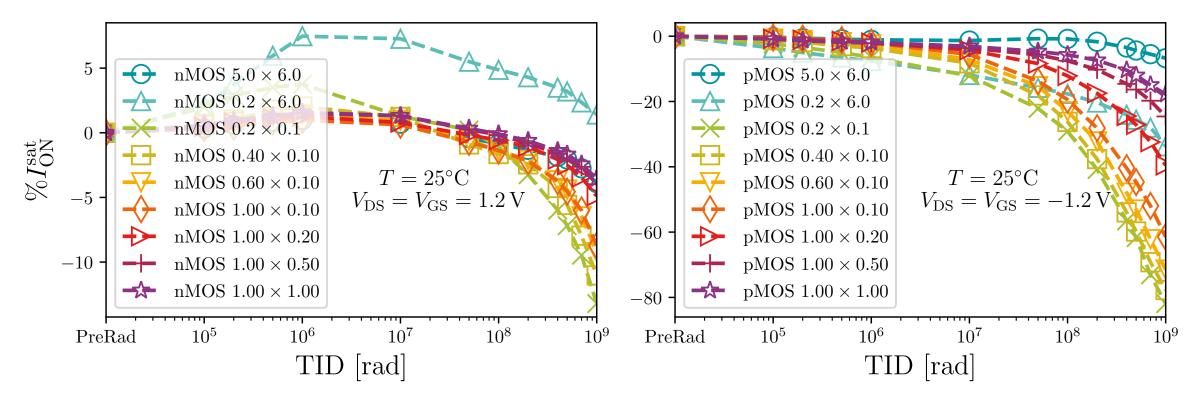

#### Transistor radiation tolerance

In line with other 65 nm technologies, no showstoppers.

Small size PMOS transistors degrade significantly after several hundred Mrad.

#### Caveat: modeling of transistors with significant reverse bias

A. Dorda Martin et al. "Measurements of total ionizing dose effects in TPSCo 65 nm and influence of NMOS bulk bias". doi: 10.1088/1748-0221/18/02/C02036

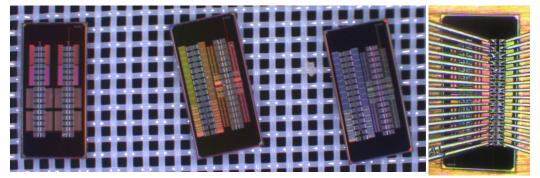

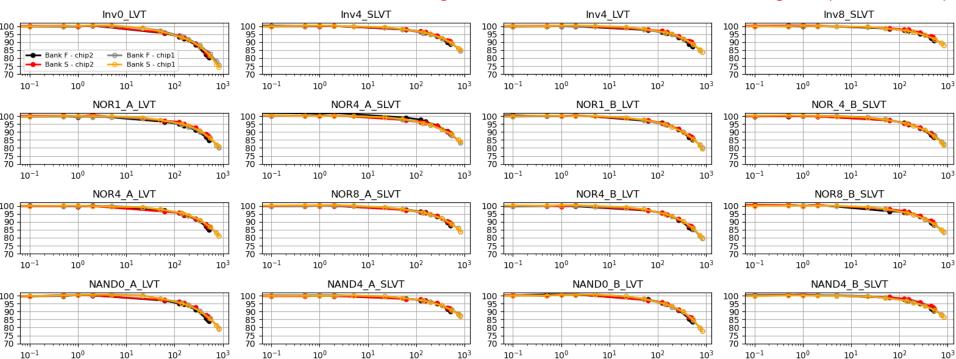

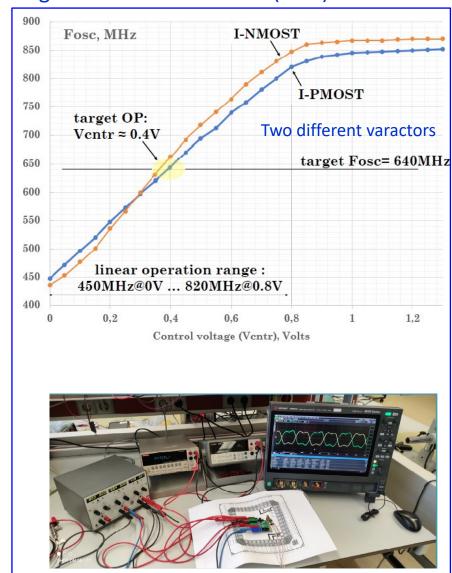

## Ringoscillator test chip

CPPM: Pierre Barrillon, Marlon Barbero, Denis Fougeron, Alexandre Habib and Patrick Pangaud (TWEPP 2022)

- CPPM contributed to MLR1 with a Ring Oscillator test chip to characterize the standard cells of the TJ 65 nm technology.

- The chip contains 48 ring oscillator based on different standard cells.

- 2 banks of 24 Rows each with the purpose of testing two approaches while irradiating:

- · Functional: the oscillation is enabled

- Static: the oscillation is disabled

- Oscillation frequency drops by 12-25 % after 830 Mrad. Degradation more pronounced for smaller cells.

- Also several analog designs radiation tolerant up to several 100 Mrad, eg DACs (IPHC), VCO, bandgap (NIKHEF)...

### Key achievement after MLR1: TPSCo 65 nm qualified for HEP

- Chain of sensor with process modifications, analog front end, and digital readout fully efficient in test bear process modifications and pixel designs.

- Pixel pitch

DPTS 15 μm pixel pitch, stitched devices in ER1 18 μm and 22.5 μm (180 nm: ALPIDE ~ 28 μm)

Sensor variant with gap conserves efficiency at larger pixel pitches.

Radiation tolerance

NIEL: DPTS  $10^{15}$   $n_{eq}$ /cm<sup>2</sup> at room temperature,  $10^{16}$   $n_{eq}$ /cm<sup>2</sup> will need cooling (needed for  $10^{15}$  for 180 nm)

TID: transistors in line with other 65 nm CMOS technologies, leads to tested tolerance beyond 100 Mrad for several circuits (ringoscillators, VCO, DAC, bandgap, etc)

SEU: cross-sections in line with other 65 nm CMOS technologies

Timing (only established really for the sensor now);

APTS\_OA ~ 80 ps requires further study, no timewalk correction yet etc (180 nm: FASTPIX ~ 100 ps) see backup

Many features in the technology still unexplored: special imaging devices, wafer stacking, ....

EP R&D Open day 2023, WP1.2 Summary:

https://indico.cern.ch/event/1233482/contributions/5264293/attachments/2596131/4482445/EP RandD Days WP1.2 2023 02 20.pdf

Proceedings on process optimization: https://pos.sissa.it/420/083

Article on DPTS chip (under review at NIMA): <a href="https://doi.org/10.48550/arXiv.2212.08621">https://doi.org/10.48550/arXiv.2212.08621</a>

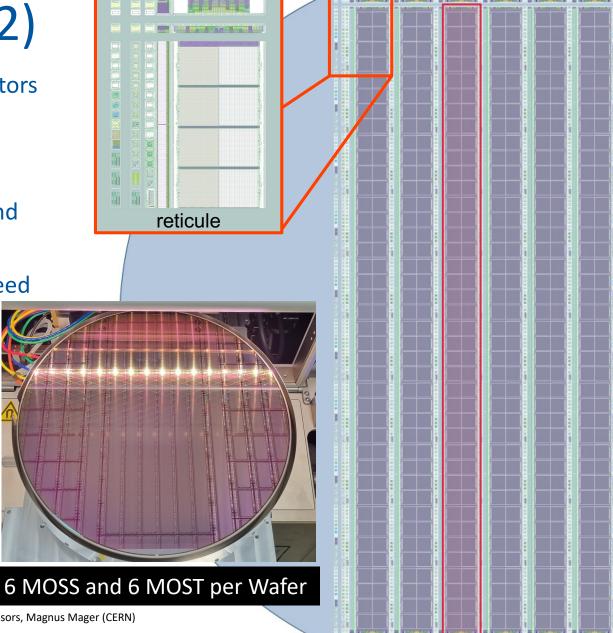

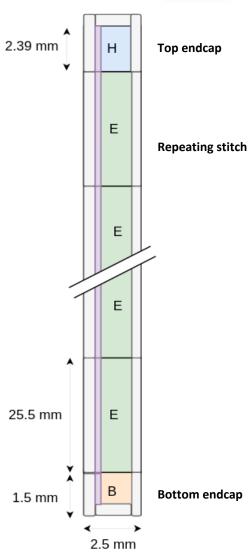

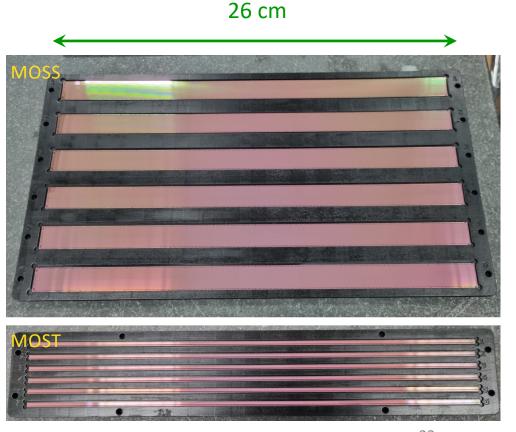

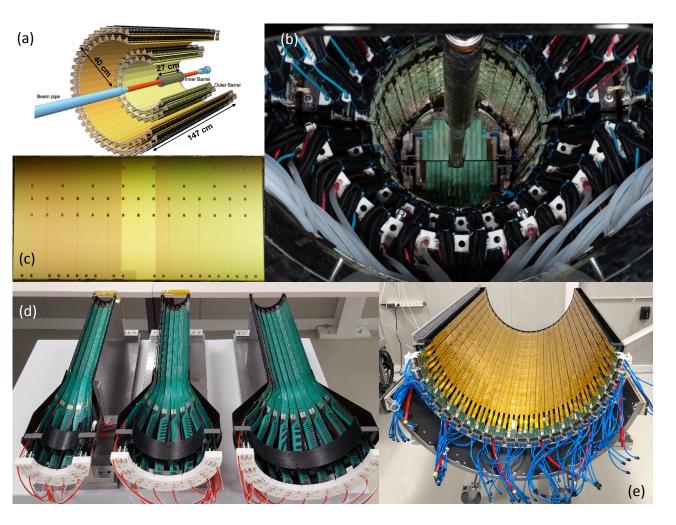

# ER1 submission (Nov 2022)

Objective: prove that we can design wafer scale pixel detectors

- Learn stitching techniques

- Stitching interconnects

- Learn about yield, design for manufacturing (DFM) and defects masking

- Study power schemes, leakage, spread, noise and speed

- Develop wafer assembly and stitching methodology

- Practical application: Alice ITS3 upgrade<sup>1</sup>

12" wafer (30cm)

26cm length single silicon object

(1) https://indico.cern.ch/event/1071914, ALICE ITS3 – a next generation vertex detector based on bent, wafer-scale CMOS sensors, Magnus Mager (CERN) (1) https://cds.cern.ch/record/2703140/files/LHCC-I-034.pdf - Letter of Intent for an ALICE ITS Upgrade in LS3

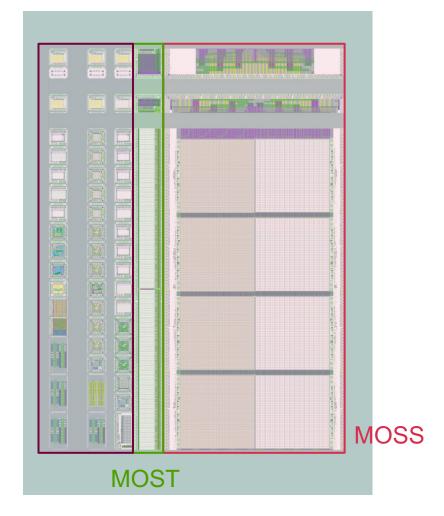

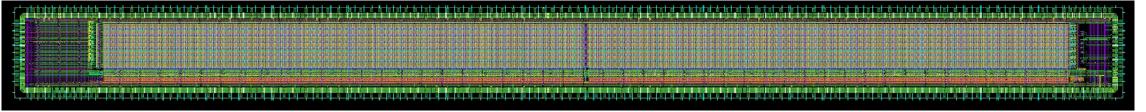

## ER1 submission

- Features two stitched sensor chips, 6 of each per wafer

- MOSS chip (1.4 x 26 cm)

- Conservative layout (DFM rules), Alpide-like readout scheme and 1/20 power segmentation

- MOST chip (0.25 x 26 cm)

- High local density with high power gating granularity to mitigate faults, async hit driven readout

- Features 51 chiplets for prototyping blocks and pixel chips

- PLL, pixel prototypes, fast serial links, SEU test chips, ...

- IPHC, NIKHEF, STFC, DESY, SLAC, INFN, CERN...

- Technology and support development

- New metal stack: new I/Os, PDK, DDK, DRC rules

- Custom DRC and LVS rule deck implemented

- Custom DFM standard cell library implemented

- Setup legal and contractual framework

- Develop know-how on stitching, wafer assembly & signoff

Test chips

#### reticule

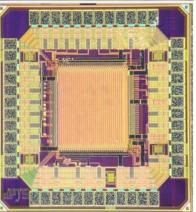

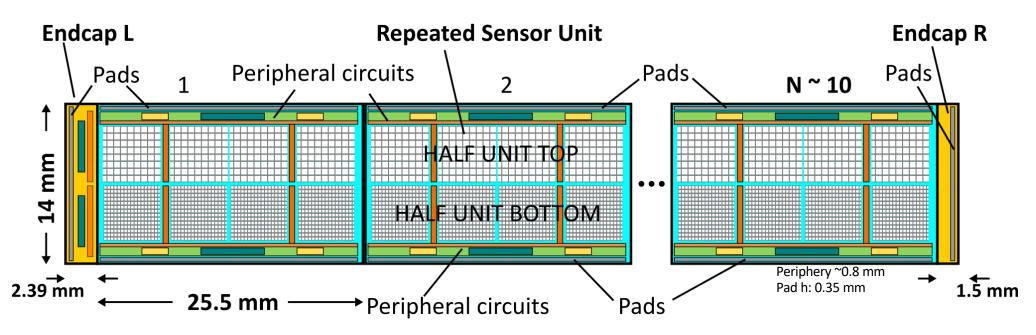

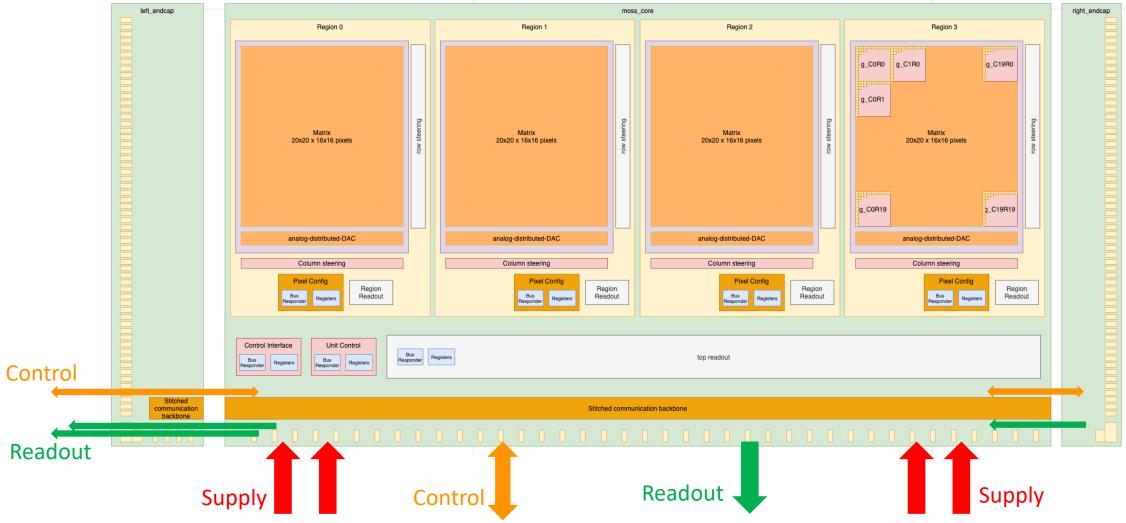

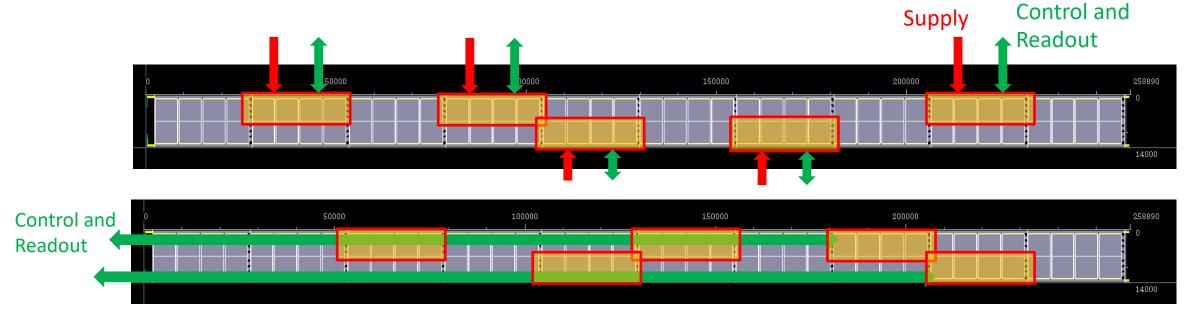

# MOSS Monolithic Stitched Sensor Prototype

#### **Primary Goals**

Learn Stitching technique to make a particle detector

Interconnect power and signals on wafer scale chip

Learn about yield and DFM

Study power, leakage, spread, noise, speed

#### Repeated units abutting on short edges

Repeated Sensor Unit, Endcap Left, Endcap Right

Functionally independent

Stitching used to connect metal traces for **power** distribution and long range on-chip interconnect busses for control and data readout

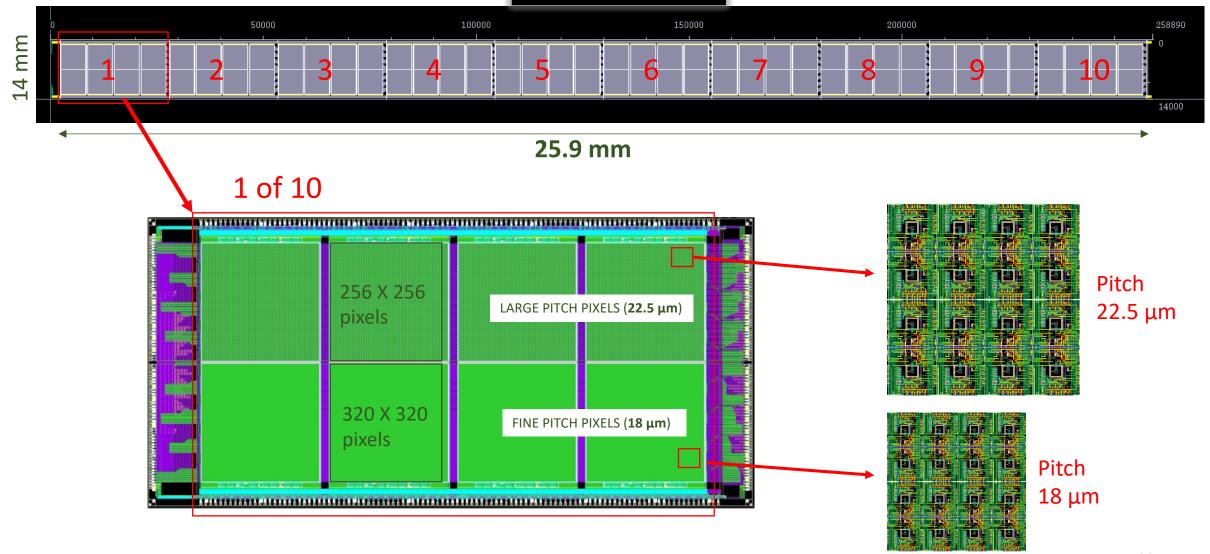

# MOSS Layout

#### 6.72 Mpixels

# MOSS - Half Unit

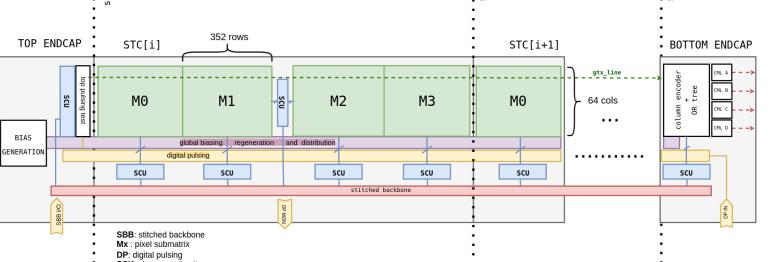

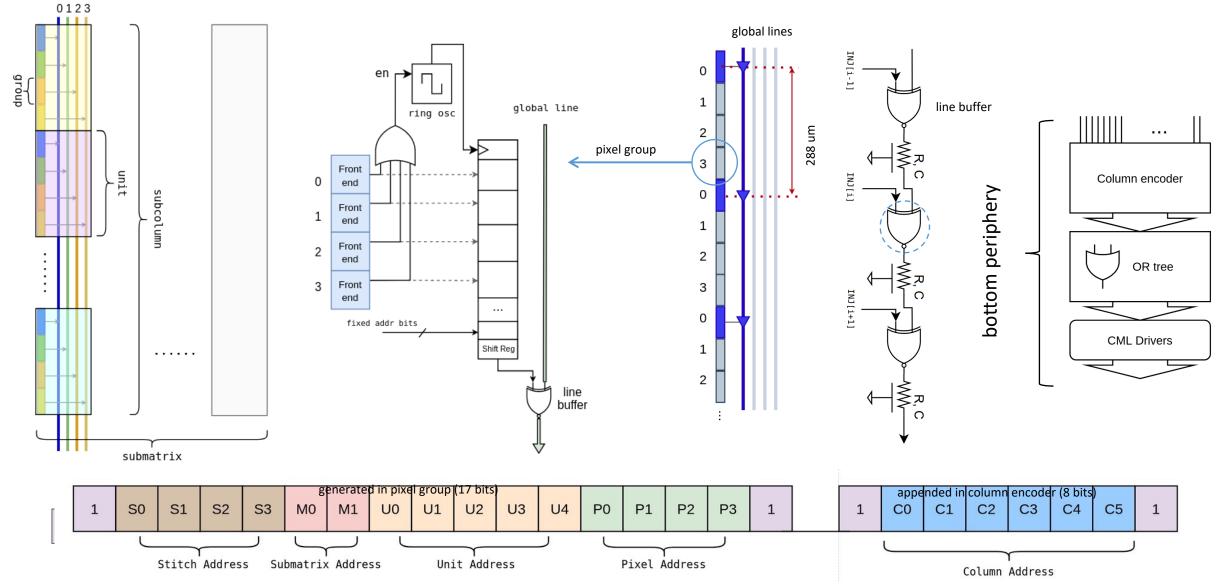

# MOST Chip

- Investigate **yield** when local density is preserved

- Global power domains over full chip (Digital/Analog)

- Higher granularity in power gating in case of a defect of

- analog (rows of 4 pixels)

- digital (half columns)

- PWELL tied to ground

- reverse sensor biasing achieved by higher power supply

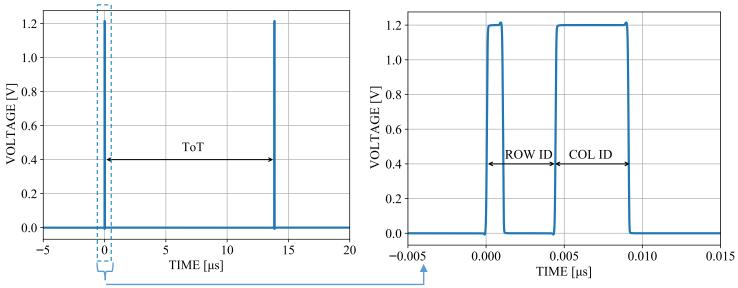

- Immediate transfer of hit data to the periphery (bottom endcap, 4 CML outputs)

- event-driven asynchronous readout (no strobing) over long distance

- serial binary address transmission for this implementation (more robust encoding than DPTS) TOP ENDCAP STC[i] STC[i+1] BOTTOM ENDCAP gtx\_line

# MOST Chip: more detail

Single stitch assembly: (1 middle stitch + endcaps)

First mounting of (dummy from pad wafer) MOST on test card

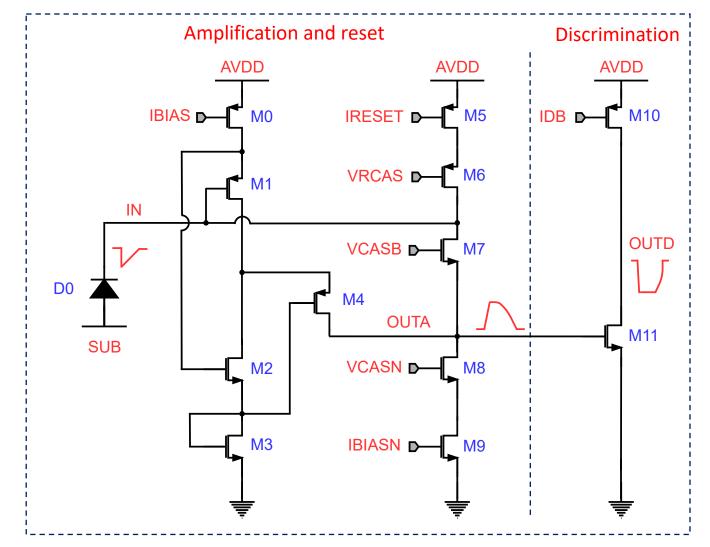

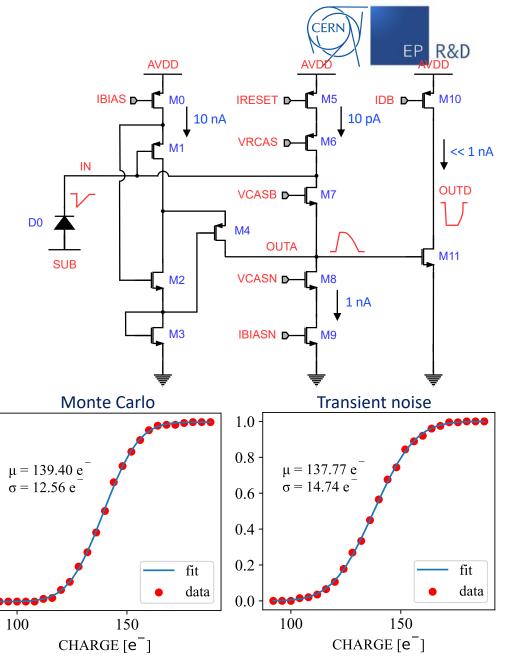

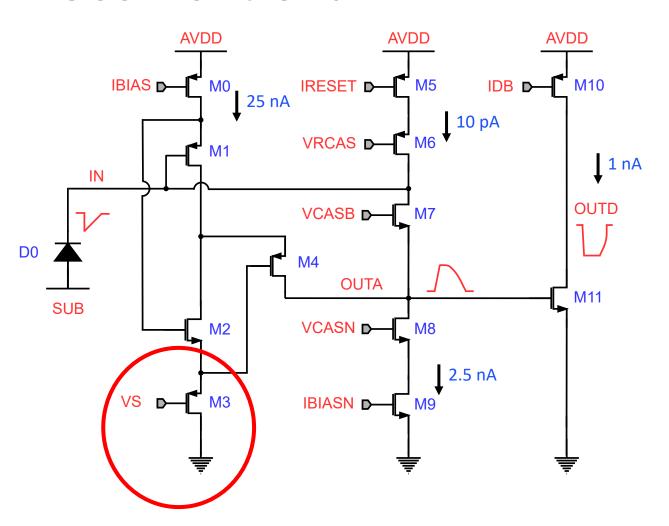

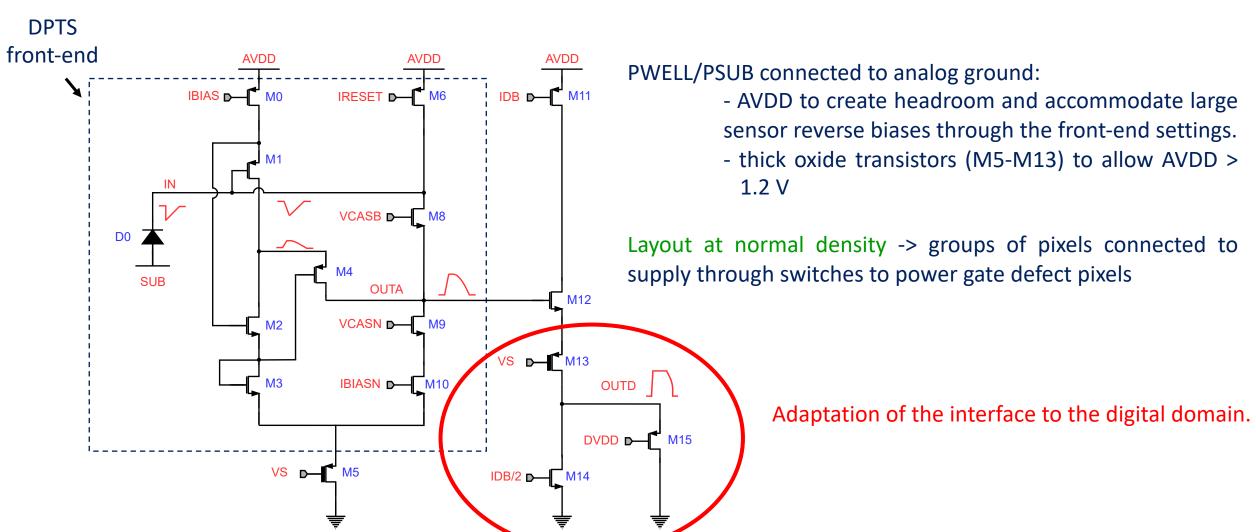

# DPTS Analog front-end

see also: F. Piro IEEE NSS 2022

Benefits from low sensor capacitance (< 5fF).

- Source follower (M1) to compensate C<sub>GS</sub> capacitance.

- M2, DC coupled to the source of M1, contributes to the gain using the same current.

- Cascode transistors M4 and M8 provide high gain on OUTA.

- DC coupling requires feedback to input through M7. Current provided by M5-M6.

- M10-M11 form a simple discriminator with threshold set by the IDB current source.

Tunable IBIAS-IBIASN (IBIAS = 10 x IBIASN) currents to set lower power consumption or faster timing response.

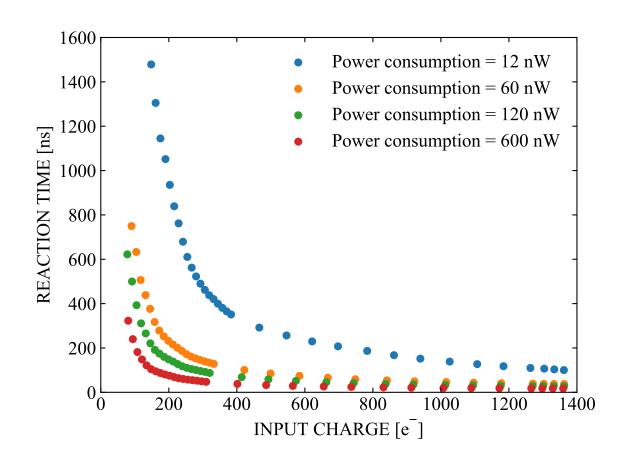

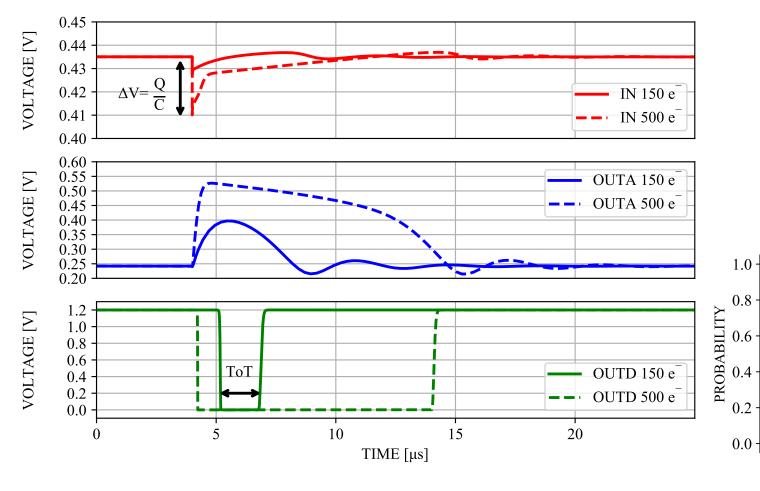

# **DPTS Front-end simulations**

Simulation results with  $\approx 12$  nW power consumption – lowest power mode.

Gain @ threshold  $\approx 1 \text{ mV/e}^-$ , 1 µs peaking time.

1.0

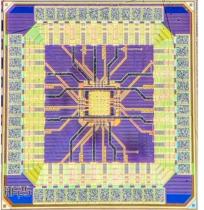

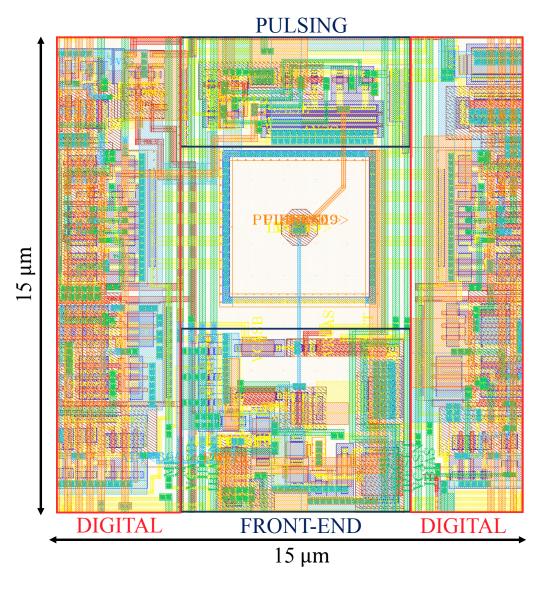

# DPTS Pixel layout and measurements

#### In-pixel circuitry:

- front-end amplifier and discriminator (42  $\mu$ m<sup>2</sup>).

- test pulse injection circuitry (17  $\mu$ m<sup>2</sup>).

- digital gates for asynchronous transmission of the timeencoded pixel address (140  $\mu m^2$ ).

Analog power density over the matrix as low as  $\sim 5 \text{ mWcm}^{-2}$ .

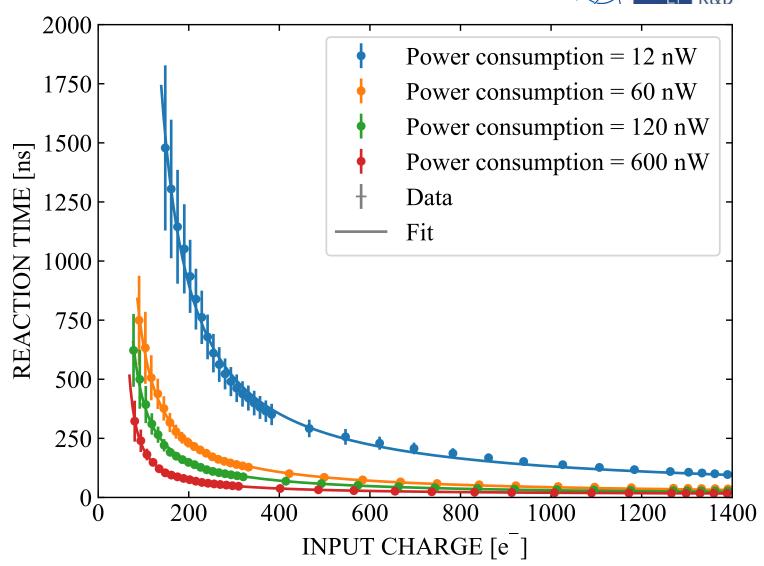

# Measurements - front-end time walk

For a power consumption of 12 nW, with charges  $> 200 e^-$  (35% of a MIP charge):

- time response  $< 1 \,\mu s$

- jitter < 150 ns

For a power consumption of 600 nW, with charges  $> 350 e^-$ :

- time response < 25 ns

- jitter < 1.2 ns

Can go up to a few  $\mu$ W. Power increased by increasing IBIAS = 10 IBIASN.

# MOSS front-end

Conservative layout to respect DFM rules.

PWELL/PSUB to be kept at ground for high yield:

- Transistor M3 converted to a PMOS to be able to shift up the collection electrode voltage through front-end settings and increase sensor reverse bias.

Higher current for more margin

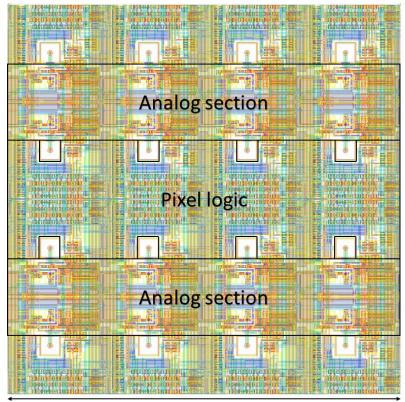

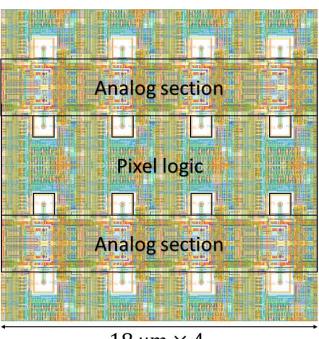

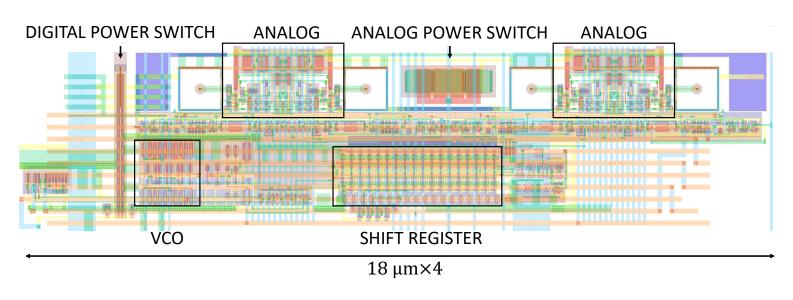

# MOSS pixel layout

$18 \, \mu m \times 4$

Performance obtained with PEX simulations

| Parameter       | Value                 |

|-----------------|-----------------------|

| Area            | 60 μm²                |

| Power           | 36 nW                 |

| Gain            | 0.5 mV/e <sup>-</sup> |

| Threshold       | 150 e <sup>-</sup>    |

| Peaking Time    | 1 μs                  |

| Phase Margin    | 60°                   |

| Thr. Dispertion | 11.5 e <sup>-</sup>   |

| ENC             | 12 e <sup>-</sup>     |

$22.5 \mu m \times 4$

Power density  $\approx 7.11 \, \text{mWcm}^{-2}$

Power density  $\approx 11.11 \text{ mWcm}^{-2}$

# MOST front-end

# MOST pixel layout

Power density  $\approx 11.11 \text{ mWcm}^{-2}$

#### Performance obtained with PEX simulations

| Parameter       | Value               |

|-----------------|---------------------|

| Area            | $45 \mu m^2$        |

| Power           | 36 nW               |

| Gain            | 1 mV/e <sup>-</sup> |

| Threshold       | 150 e <sup>-</sup>  |

| Peaking time    | 1 μs                |

| Phase Margin    | 55°                 |

| Thr. Dispertion | 15 e <sup>-</sup>   |

| ENC             | 10.5 e <sup>-</sup> |

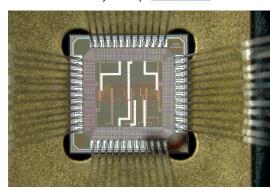

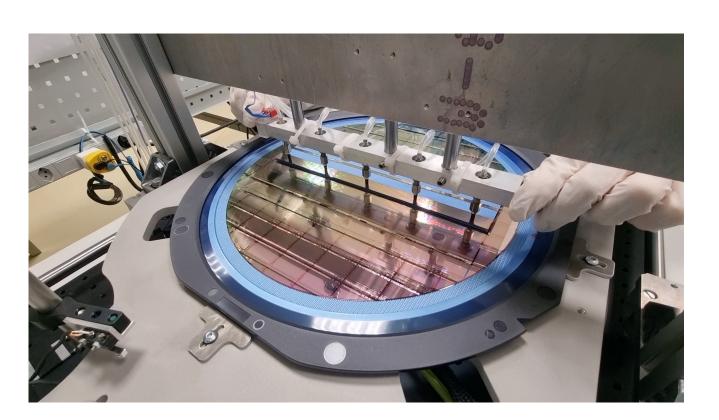

# Thinning/Dicing/Picking tests

- Wafers thinned and diced (50 μm)

- Chips picked using dedicated tooling at CERN, similar setup prepared at NIKHEF

- Works!

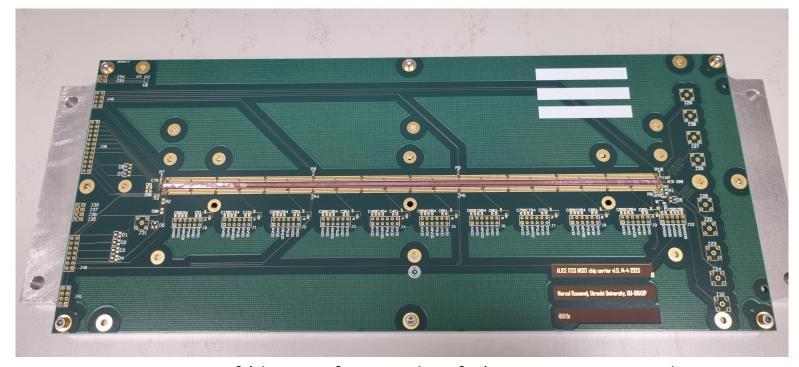

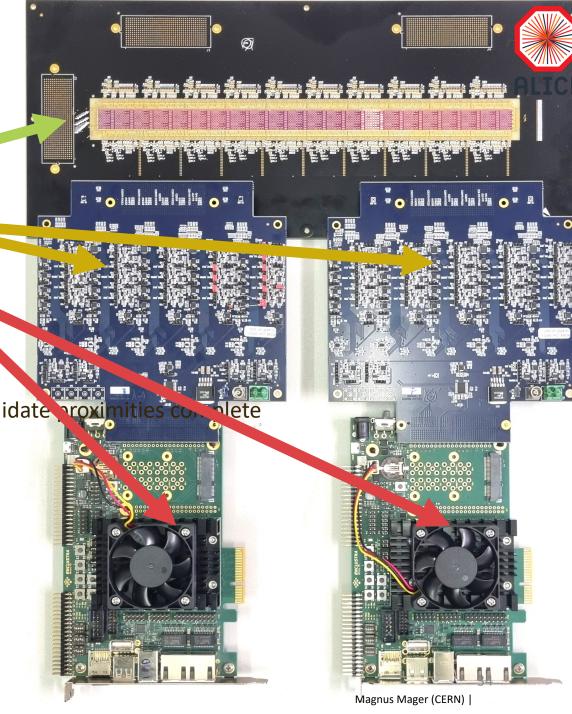

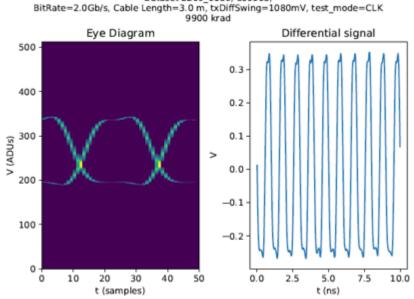

# ER1 (MOSS) test system

- Based on:

- carrier card (passive; custom made)

- 5x proximity card (active; custom made)

- 5x FPGA board (commercial: enclustra Mercury+ AA1+PLL)

- Status:

- carrier: V2 (cosmetic changes) in production

- proximity: V2 (minor bug fixes) in production

- FPGA boards: delivered (12 units)

- Soft- and firmware: under development, functionality to validate proxi

- Complex system:

- NB: picture on the right shows only 2/5 parts

- important to start early, no criticalities

- Very first tests indicate life in the chip

#### SUMMARY and OUTLOOK

# CERN EP R&D

#### After MLR1: 65 nm ISC qualified for HEP:

- Building knowledge about this technology for general interest

- Results fully in line with ECFA roadmap

- Very significant effort with synergy with the ALICE ITS3 upgrade project without which this progress could not have been made.

#### ER1: exploration of stitched sensors

Back from foundry, significant testing effort ahead

#### ER2: focused on large stitched sensor MOSS2 for ITS3 upgrade

- MOSS2 will need to satisfy ITS3 requirements

- Less chiplets

- Tapeout spring 2024

MLR2...4: Organizing access for wider HEP community and continuing R&D for experiments (ALICE 3, ....)

See next page

#### SUMMARY and OUTLOOK

also in testing (!), in synergy with the experiments (ALICE3, ...) and other R&D projects

As part of CERN EP R&D WP1.2 on monolithic sensors and DRD7. 6 on complex imaging ASICs and technologies, aligned with ECFA roadmap

- Set up joint access for TPSCo 65 nm technology (and possibly others like TJ 180 nm, Lfoundry supported by other institutes, ...)

- Engineering runs MLR2-4 with <u>small chiplets, reticle scale and wafer scale stitched sensors</u> on single wafer

- Common framework with frame contract, PDK, libraries, ...

- IP blocks (standard pixels, pad rings, ADCs ...)

- Shared access to 3 D technologies

- Common QA/ASIC development framework

- Designer's fora

| 2024  |         |       |  |  |  | 2025 |       |          |        |  |      | 2026   |    |  |  |  |  | 2027 |    |         |    |  |  | 2028 |  |  |  |    |           |

|-------|---------|-------|--|--|--|------|-------|----------|--------|--|------|--------|----|--|--|--|--|------|----|---------|----|--|--|------|--|--|--|----|-----------|

| Deliv | erable  | s:    |  |  |  |      |       |          |        |  |      |        |    |  |  |  |  |      |    |         |    |  |  |      |  |  |  |    |           |

|       |         |       |  |  |  |      | Des.K | it & Lil | raries |  | Re   | port E | R2 |  |  |  |  |      | Re | port ML | R2 |  |  |      |  |  |  | Re | eport MLR |

|       |         |       |  |  |  |      |       |          |        |  |      |        |    |  |  |  |  |      |    |         |    |  |  |      |  |  |  |    |           |

| Tape  | -out da | ates: |  |  |  |      |       |          |        |  |      |        |    |  |  |  |  |      |    |         |    |  |  |      |  |  |  |    |           |

|       |         | ER2   |  |  |  |      |       |          |        |  | MLR2 |        |    |  |  |  |  |      |    | MLR3    |    |  |  |      |  |  |  |    | MLR4      |

|       |         |       |  |  |  |      |       |          |        |  |      |        |    |  |  |  |  |      |    |         |    |  |  |      |  |  |  |    |           |

- Standardized test setups and readout, MASSIVE testing effort

- See call for proposals for DRD 7 (please express your interest before June 30<sup>th</sup> 2023)

- See also last general WP1.2 general reporting meeting: https://indico.cern.ch/event/1280150/

# THANK YOU TO ALL CONTRIBUTING PEOPLE, GROUPS AND INSITUTES

# **SPARE**

## ECFA Detector R&D in Electronics: DRD7. Call for projects

#### Dear Colleagues

You receive this message because you registered to the ECFA DRD7 interest group.

In view of drafting its Letter of Intent, DRD7 is now calling for projects in electronics, following the priorities established in the ECFA Detector R&D roadmap document.

Interested scientists, groups or collaborations are invited to express their interest by contacting the relevant DRD7 WG conveners with their project intentions.

Conveners will collect the community feedback and aggregate it into a portfolio of projects in each WG. These preliminary project intentions will form the basis of the Letter of Intent, due to be submitted in July 2023.

The two attached documents give all necessary information on the call for projects itself, and on the DRD7 future organization.

Please express your interest before 30 June 2023.

Francois Vasey, on behalf of the steering and technical committees.

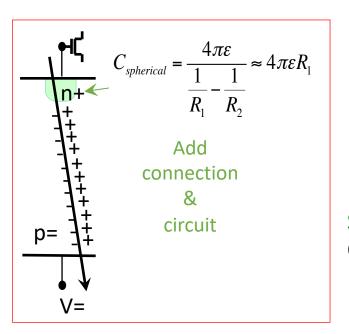

## The need for sensor optimization to obtain full depletion

Signal charge is collected from the non-depleted layer, diffusion dominated and prone to trapping after irradiation

#### Planar vs spherical junction

- Planar junction: depletion thickness proportional to square root of reverse bias.

- Spherical junction: depletion thickness proportional only to *cubic root* of reverse bias, inner radius R1 to be kept small for low capacitance

- Deep pwell and substrate limit extension of the depletion layer -> see next slide

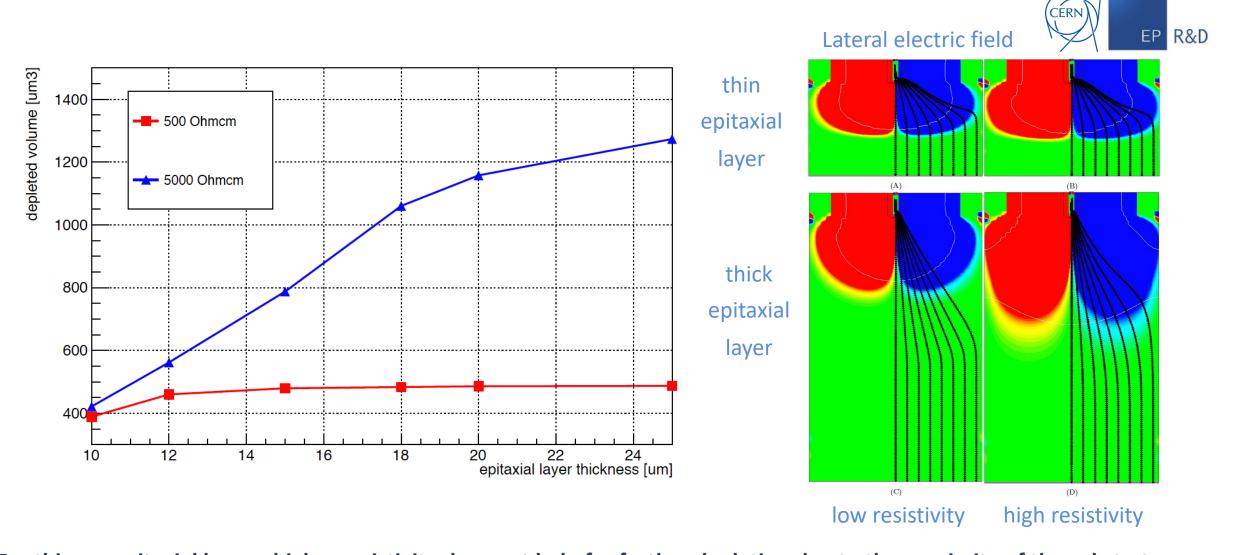

Sensor optimization: influence of the resistivity of the epitaxial layer

For thinner epitaxial layers, higher resistivity does not help for further depletion due to the proximity of the substrate

Depletion constrained by the substrate and surrounding pwells

# State of the art: ALICE Inner Tracking System 2: 10 m<sup>2</sup> with 3x1.5 cm<sup>2</sup> ALPIDE chips

TowerJazz 180 nm imaging CMOS technology, development 2012-2016

#### **ALPIDE CHIP**

- 512 x 1024 pixels of 28 x 28 μm<sup>2</sup>

- Full CMOS in the pixel (deep pwell)

- 40 nW front end, sparse readout

- Matrix 6 mW/cm<sup>2</sup>, up to 40 mW/cm<sup>2</sup> including periphery

- Standard process: sensitive epitaxial layer not depleted

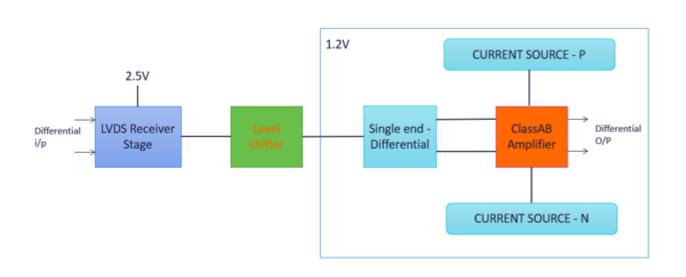

#### STFC

RAL: S. Mathew, Iain Sedgwick

MLR1 submission with CML driver:

Dataset 2209\_0136, L00003;

• Several other institutes have submitted test chips: Yonsei and SLAC (pixel test matrix), DESY (test pixels and Krummenacher feedback amplifier)

# <sup>55</sup>Fe measurements confirm influence on charge sharing

See also: I. Sanna IEEE NSS 2022

No experimental comparison between split 3 and split 4 available yet.

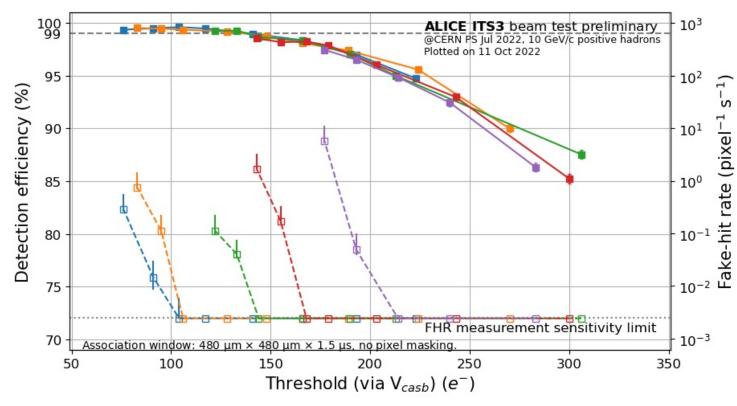

## Detection efficiency/Fake hits/Sensor radiation tolerance

**DPTS**

DPTSOW22B3 TID + NIEL.  $10 \text{ kGy} + 10^{13} \text{ 1MeV n}_{eq} \text{ cm}^{-2}$ version: O split: 4 (opt.)  $I_{reset} = 35 pA$  $I_{bias} = 100 \, \text{nA}$  $I_{biasn} = 10 \text{ nA}$ db = 50 nA $V_{casn} = variable$  $V_{casb} = variable$  $V_{pwell} = V_{sub} = variable$  $T = 20 \,^{\circ} \text{C}$ Detection efficiency −⊕− Fake-hit rate V<sub>sub</sub>=-3.0 V  $V_{sub}$ =-2.4 V  $V_{sub} = -1.8 \text{ V}$

$V_{sub}=-1.2 V$

$V_{sub}=-0.6 V$

- Fully efficient sensor, analog front end, digital readout chain in

15 x 15 μm<sup>2</sup> pixel (DPTS) including sensor optimization

- Large operating margin before irradiation

- After 1E15  $n_{eq}/cm^2$  efficiency > 99% maintained at room temperature

- Higher fluencies under investigation

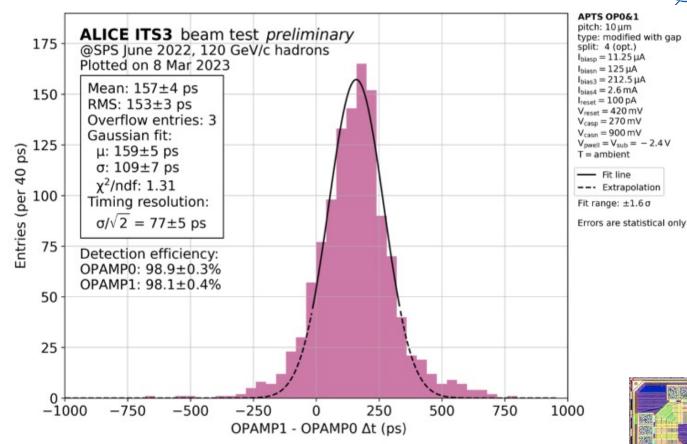

### Time resolution of the sensor

#### (U. Savino et al. ULITIMA 2023)

- Two chips with 4 x 4 matrix at 10 μm pitch put into coincidence (!)

- Measured sigma of the time difference = 109 +- 7 ps, per plane 77 ps

- No timewalk correction yet.

- In 180 nm ~100 ps with timewalk and cluster size correction (J. Braach et al. ULITIMA 2023)

**APTS**

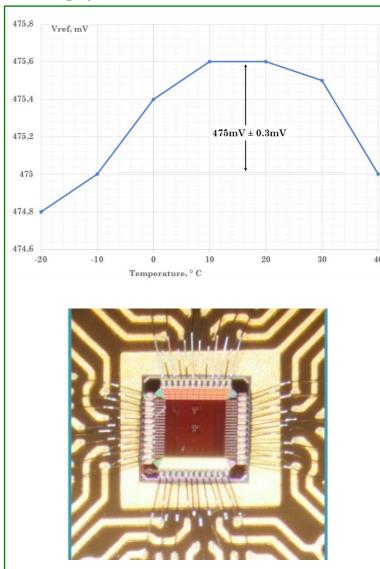

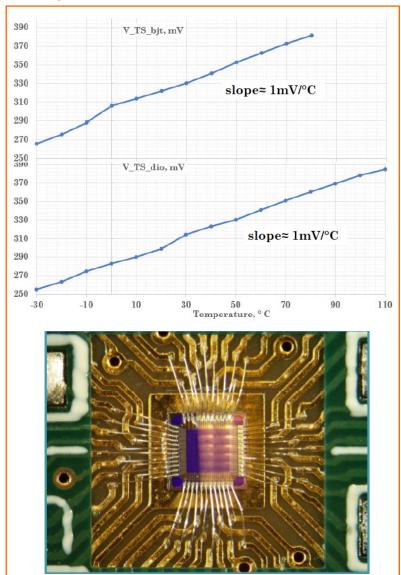

IP Block measurements bandgap, T-sensor, VCO: all functional and tolerant to 100 Mrad or beyond

NIKHEF: V. Gromov, D. Gajanana, A. Yelkenci, A. Grelli, R. Kluit, M. Rossewij (TWEPP 2022)

#### Bandgap

#### Temperature sensor

#### Voltage Controlled Oscillator (VCO)

EP R&D

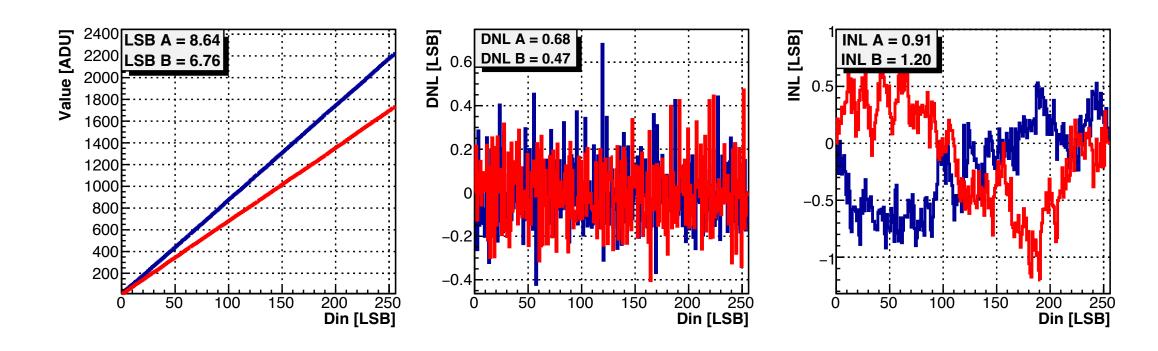

### IP Block measurements DAC

IPHC: I. Valin, S. Bugiel, A. Dorokhov, C. Colledani, C. Hu et al.

| CERN | EP | R&D |  |

|------|----|-----|--|

| /    | 1  |     |  |

|                        | DAC A   | DAC B   |

|------------------------|---------|---------|

| Resolution             | 8 bit   | 8 bit   |

| LSB [nA]               | 40      | 40      |

| Reference current [uA] | -0.8    | -10.72  |

| Power [uW] (*)         | 13      | 13      |

| Area [um x um]         | 133x253 | 143x253 |

Both DACs remain functional after 500 Mrad irradiation with DNL < 1 LSB, INL < 2 LSB

10 keV X-rays 6.5 Mrad/hour

## **MOSS TESTING SCENARIOS - EXAMPLES**

Test the sub-units independently

Study manufacturing yield

Functional yield at half unit, block, column/row/pixel level granularity

Possible dependence on pixel pitch and layout density?

Study noise, threshold, position resolution vs pixel variants

# DPTS Pixel layout

#### In-pixel circuitry:

- front-end amplifier and discriminator (42  $\mu$ m<sup>2</sup>).

- test pulse injection circuitry (17  $\mu$ m<sup>2</sup>).

- digital gates for asynchronous transmission of the timeencoded pixel address (140  $\mu m^2$ ).

Analog power density over the matrix as low as  $\sim 5 \text{ mWcm}^{-2}$ .

L. Cecconi, et al., "Design and readout architecture of a monolithic binary active pixel sensor in TPSCo 65 nm CMOS imaging technology", TWEPP 2022.

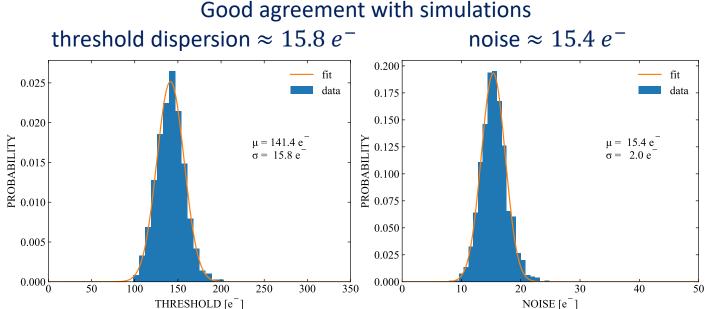

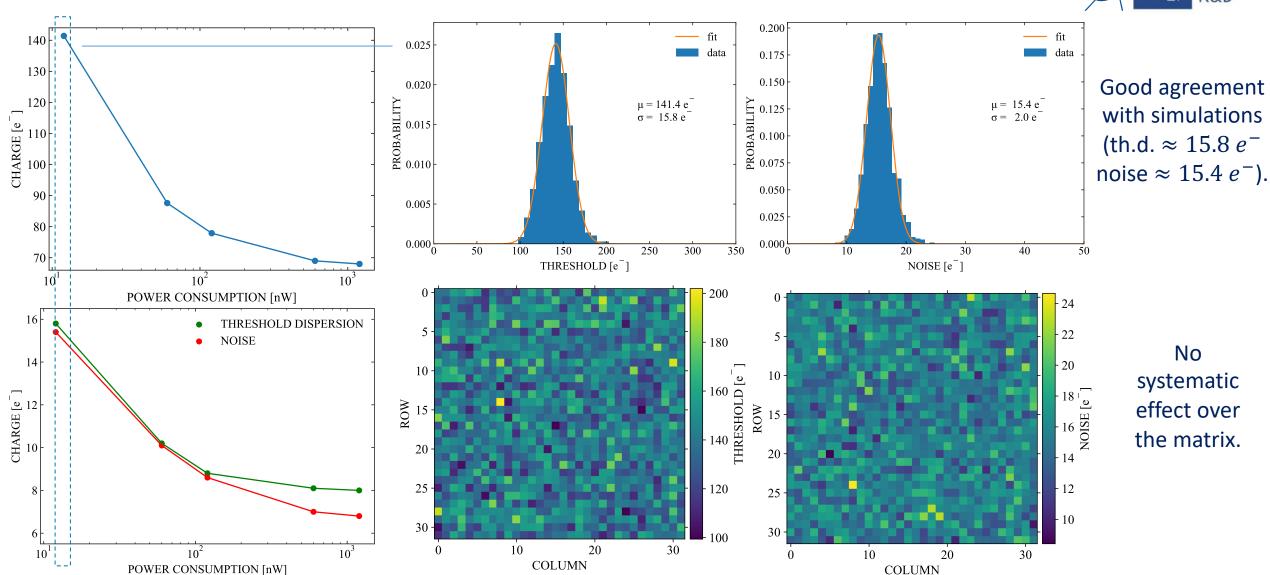

# Measurements - threshold dispersion and noise

# Timing measurements